Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением.

Известны устройства для цикловой синхронизации [1-3], содержащие: опознаватель синхрокомбинации, блоки удержания и поиска синхронизма, генераторное оборудование, элементы И, ИЛИ, входы и выходы устройства, соединенные определенным образом.

Основным недостатком этих устройств является невозможность одним и тем же устройством осуществить синхронизацию различных цифровых передач информации с временным уплотнением.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для цикловой синхронизации [4], содержащее оперативное запоминающее устройство, устройство настройки и диагностики, дешифратор синхрокомбинации, фазирующее устройство, генераторное оборудование, устройства хранения критериев входа и выхода из синхронизма, входы и выходы устройства, соединенные соответствующим образом.

Приведенное устройство позволяет осуществлять одним и тем же устройством синхронизацию различных цифровых передач информации с временным уплотнением. Однако оно не обеспечивает цикловую синхронизацию группы одинаковых по структуре передач с помощью одного устройства.

Технической задачей изобретения является расширение функциональных возможностей, позволяющих осуществить одним устройством цикловую синхронизацию группы цифровых передач одинаковой структуры с одновременным сокращением аппаратурных затрат, энергопотребления и повышения надежности и помехоустойчивости.

Указанная задача решается тем, что в устройство для групповой цикловой синхронизации, содержащее оперативное запоминающее устройство (ОЗУ), устройство настройки (УН), дешифратор синхрокомбинации (ДС), фазирующее устройство (ФУ), генераторное оборудование (ГО), причем вход выбора ОЗУ соединен с земляной шиной, а входы записи и чтения - с соответствующими выходами УН, входы выбора режима, нового адреса, установки в ноль, записи, чтения, выбора настройки ОЗУ или регистра запоминания и информационные 0,... ,N входы-выходы которого являются соответствующими входами устройства для групповой цикловой синхронизации (ГЦС), входы-выходы значения синхрокомбинации, позиции синхрокомбинации, конца синхрокомбинации ОЗУ соединены с соответствующими входами-выходами УН и с соответствующими входами ДС, выход отклика которого соединен с соответствующим входом ФУ, вход конца синхрокомбинации которого соединен с соответствующим выходом ОЗУ, вход-выход конца цикла которого соединен с соответствующим входом-выходом УН, вторые 02,... ,N2 задающие выходы которого соединены соответственно с задающими 0,... ,N входами ГО, вход установки в ноль которого соединен с соответствующим выходом УН, выходы концов циклов ГО являются соответствующими выходами устройства для ГЦС, согласно изобретению введены первый, второй и третий коммутаторы, распределитель сигналов (PC), временной анализатор (ВА) и удалитель сигналов (УС), причем тактовые входы и информационные входы устройства для ГЦС соединены с соответствующими входами первого коммутатора, тактовый выход которого соединен с соответствующими входами ДС, УС и третьего коммутатора, информационный выход первого коммутатора соединен с соответствующим входом ДС, выход сигнала конца цикла ОЗУ соединен с соответствующим входом ВА, 0,... ,N задающие входы которого соединены с 02,... ,N2 задающими выходами УН, первые 01,... ,N1 задающие выходы которого соединены с 0,... N задающими входами PC, тактовый выход ВА соединен с соответствующим входом PC, 1,... ,M разрешающие выходы которого соединены с соответствующими входами первого, второго и третьего коммутаторов и входами УС, 0,... ,N адресные выходы второго коммутатора соединены с соответствующими входами ОЗУ, выход наличия синхронизации ФУ соединен с соответствующими входами третьего коммутатора и ВА, выход управления которого соединен с соответствующим входом УС, тактовые выходы которого соединены с соответствующими входами ГО, входы выбора режима PC и УС соединены с соответствующим входом устройства для ГЦС, вход нового адреса которого соединен с соответствующим входом УС, вход конца синхрокомбинации которого соединен с соответствующим выходом ОЗУ, выход нулевого состояния ФУ соединен с соответствующим входом УС, тактовые входы которого соединены с соответствующими входами устройства для ГЦС, адресные выходы ГО соединены с соответствующими входами второго коммутатора, выходы наличия синхронизации третьего коммутатора являются соответствующими выходами устройства для ГЦС.

Временной анализатор содержит первый, второй и третий счетчики, первый и второй триггеры, первый и второй инверторы, первый, второй и третий элементы ИЛИ, первый, второй, третий и четвертый элементы И, вход наличия синхронизации, вход конца цикла, задающие входы, выход управления и тактовый выход, причем вход наличия синхронизации соединен с вторым входом второго элемента ИЛИ и вторыми входами первого и второго элементов И, вход конца цикла соединен с тактовыми входами первого, второго и третьего счетчиков и второго триггера, а также с входом первого инвертора, третьим входом первого элемента И и вторым входом третьего элемента И, выход первого счетчика соединен с тактовым входом первого триггера, информационный вход которого соединен с шиной питания, входы установки в ноль первого счетчика и первого триггера соединены с выходом первого элемента ИЛИ, первый вход которого и третий вход второго элемента ИЛИ соединены с выходом четвертого элемента И, выход первого триггера является выходом управления временного анализатора, а также соединен с входом второго инвертора и с первыми входами первого и второго элементов И, выход второго инвертора соединен с первым входом второго элемента ИЛИ, выход которого соединен с входами установки в ноль второго, третьего счетчиков и второго триггера, задающие входы второго счетчика являются задающими входами временного анализатора, выход второго счетчика соединен с разрешающим входом второго триггера, выход которого соединен с разрешающим входом третьего счетчика, выход третьего счетчика соединен с первыми входами третьего и четвертого элементов И, выход первого инвертора соединен с вторым входом четвертого элемента И и с третьим входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выходы первого и третьего элементов И соединены с входами третьего элемента ИЛИ, выход которого является тактовым выходом временного анализатора, информационный вход второго триггера соединен с шиной питания.

Новизна технического решения заключается в наличии в заявленном устройстве новых схемных элементов: первого, второго и третьего коммутаторов, распределителя сигналов, временного анализатора и удалителя сигналов.

Таким образом, изобретение соответствует критерию “Новизна”.

Анализ известных технических решений в исследуемой и смежной областях позволяет сделать вывод, что введенные функциональные узлы известны. Однако введение их в устройство для групповой цикловой синхронизации с указанными связями придает ему новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют расширить его функциональные возможности, обеспечивая одним устройством синхронизацию группы цифровых передач с одинаковой структурой, сократить аппаратурные затраты и связанное с этим энергопотребление, повысить надежность и помехоустойчивость устройства, связанные с тем, что применение одного запоминающего устройства при синхронизации группы цифровых потоков позволяет резко сократить количество печатных проводников, увеличить их ширину, тем самым уменьшить удельное сопротивление и вероятность нарушения соединения между элементами устройства.

Таким образом, изобретение соответствует критерию “Изобретательский уровень”, так как оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передачи информации с асинхронным объединением цифровых потоков.

Таким образом, изобретение соответствует критерию “Промышленная применимость”.

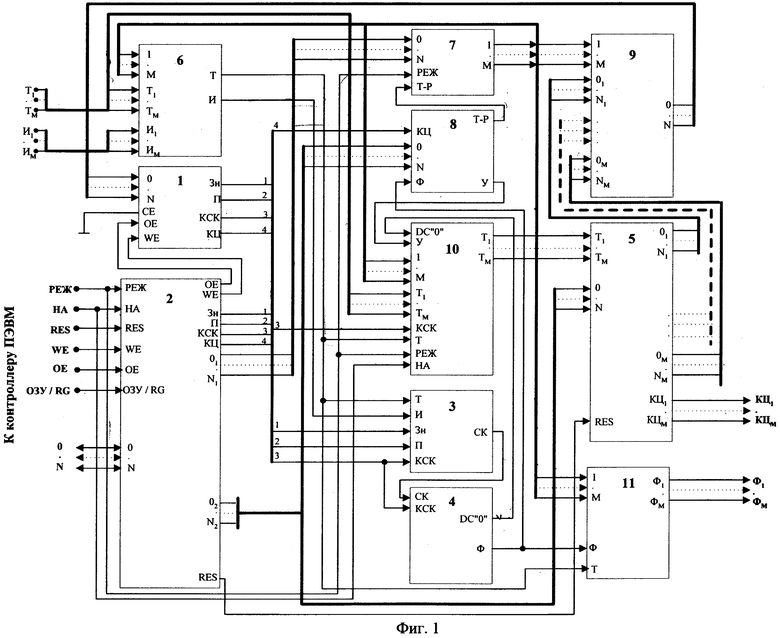

На фиг.1 представлена структурная электрическая схема предлагаемого устройства для групповой цикловой синхронизации, на фиг.2 - структурная электрическая схема временного анализатора, на фиг.3 - электрическая принципиальная схема удалителя сигналов.

Устройство для групповой цикловой синхронизации (фиг.1) содержит оперативное запоминающее устройство 1 (ОЗУ), устройство настройки 2 (УН), дешифратор синхрокомбинации 3 (ДС), фазирующее устройство 4 (ФУ), генераторное оборудование 5 (ГО), первый коммутатор 6, распределитель сигналов 7 (PC), временной анализатор 8 (ВА), второй коммутатор 9, удалитель сигналов 10 (УС), третий коммутатор 11, причем вход выбора (вход СЕ) ОЗУ соединен с земляной шиной, а входы записи (вход WE) и чтения (вход ОЕ) - с соответствующими выходами УН 2, входы выбора режима (вход РЕЖ), нового адреса (вход НА), установки в ноль (вход RES), записи (вход WE), чтения (вход ОЕ), выбора настройки ОЗУ или регистра запоминания (вход ОЗУ/RG) и информационные 0,... ,N входы-выходы которого являются соответствующими входами устройства для групповой цикловой синхронизации (ГЦС), входы-выходы значения синхрокомбинации (вход-выход Зн), позиции синхрокомбинации (вход-выход П), конца синхрокомбинации (вход-выход КСК) ОЗУ 1 соединены с соответствующими входами-выходами УН 2 и с соответствующими входами ДС 3, выход отклика (выход СК) которого соединен с соответствующим входом ФУ 4, вход конца синхрокомбинации (вход КСК) которого соединен с соответствующим выходом ОЗУ 1, вход-выход конца цикла (вход-выход КЦ) которого соединен с соответствующим входом-выходом УН 2, вторые 02,... ,N2 задающие выходы которого соединены соответственно с задающими 0,... ,N входами ГО 5, вход установки в ноль (вход RES) которого соединен с соответствующим выходом УН 2, выходы концов циклов (выходы КЦ1,... ,КЦМ) являются соответствующими выходами устройства для ГЦС, тактовые входы (входы Т1,... ,ТМ) и информационные входы (входы И1,... ,ИМ) устройства для ГЦС соединены с соответствующими входами первого коммутатора 6, тактовый выход (выход Т) которого соединен с соответствующими входами ДС 3, УС 10 и третьего коммутатора 11, информационный выход (выход И) первого коммутатора 6 соединен с соответствующим входом ДС 3, выход сигнала конца цикла (выход КЦ) ОЗУ 1 соединен с соответствующим входом ВА 8, 0,... ,N задающие входы которого соединены с вторыми 02,... ,N2 выходами УН 2, первые 01,... ,N1 задающие выходы которого соединены с 0,... ,N задающими входами PC 7, тактовый выход (выход Т-Р) ВА 8 соединен с соответствующим входом PC 7, разрешающие выходы которого соединены с соответствующими входами первого 6, второго 9, третьего 11 коммутаторов и входами УС 10, 0,... ,N адресные выходы второго коммутатора 9 соединены с соответствующими входами ОЗУ 1, выход наличия синхронизации (выход Ф) ФУ 4 соединен с соответствующими входами третьего коммутатора 11 и ВА 8, выход управления (выход У) которого соединен с соответствующим входом УС 10, тактовые выходы (выходы Т1,... ,ТМ) которого соединены с соответствующими входами ГО 5, входы выбора режима (вход РЕЖ) PC 7 и УС 10 соединены с соответствующим входом устройства для ГЦС, вход нового адреса (вход НА) которого соединен с соответствующим входом УС 10, вход конца синхрокомбинации (вход КСК) которого соединен с соответствующим выходом ОЗУ 1, выход нулевого состояния (выход ДС“0”) ФУ 4 соединен с соответствующим входом УС 10, тактовые входы (Т1,... ,ТМ) которого соединены с соответствующими входами устройства для ГЦС, адресные выходы (выходы 01,... ,N1 – 0М,... ,NМ) ГО 5 соединены с соответствующими входами второго коммутатора 9, выходы наличия синхронизации (выходы Ф1,... ,ФМ) третьего коммутатора 11 являются соответствующими выходами устройства для ГЦС.

Временной анализатор (фиг.2) содержит первый 12, второй 13 и третий 14 счетчики, первый 15 и второй 16 триггеры, первый 17 и второй 18 инверторы, первый 19, второй 20 и третий 21 элементы ИЛИ, первый 22, второй 23, третий 24 и четвертый 25 элементы И, вход наличия синхронизации (вход Ф), вход конца цикла (вход КЦ), задающие входы (входы 0,... ,N), выход управления (выход У) и тактовый выход (выход Т-Р), причем вход наличия синхронизации соединен с вторым входом второго элемента ИЛИ 20 и вторыми входами первого 22 и второго 23 элементов И, вход конца цикла соединен с тактовыми входами (входы К) первого 12, второго 13, третьего 14 счетчиков и второго триггера 16, а также с входом первого инвертора 17, третьим входом первого элемента И 22 и вторым входом третьего элемента И 24, выход первого счетчика 12 соединен с тактовым входом (вход К) первого триггера 15, информационный вход (вход D) которого соединен с шиной питания, входы установки в ноль (входы R) первого счетчика 12 и первого триггера 15 соединены с выходом первого элемента ИЛИ 19, первый вход которого и третий вход второго элемента ИЛИ 20 соединены с выходом четвертого элемента И 25, выход первого триггера 15 является выходом управления временного анализатора, а также соединен с входом второго инвертора 18 и с первыми входами первого 22 и второго 23 элементов И, выход второго инвертора 18 соединен с первым входом второго элемента ИЛИ 20, выход которого соединен с входами установки в ноль (входы R) второго 13, третьего 14 счетчиков и второго триггера 16, задающие входы (входы 0,... ,N) второго счетчика 13 являются задающими входами временного анализатора, выход второго счетчика 13 соединен с разрешающим входом (вход ЕС) второго триггера 16, выход которого соединен с разрешающим входом (вход ЕС) третьего счетчика 14, выход третьего счетчика 14 соединен с первыми входами третьего 24 и четвертого 25 элементов И, выход первого инвертора 17 соединен с вторым входом четвертого элемента И 25 и с третьим входом второго элемента И 23, выход которого соединен с вторым входом первого элемента ИЛИ 19, выходы первого 22 и третьего 24 элементов И соединены с входами третьего элемента ИЛИ 21, выход которого является тактовым выходом (выход Т-Р) временного анализатора, информационный вход (вход D) второго триггера 16 соединен с шиной питания.

Удалитель сигналов (фиг.3) содержит триггеры 26, 27, 28, 29, инверторы 30, 31, 321,... ,32М, элементы И 33, 34, 35, 361,... ,36М, 371,... ,37M, элемент ИЛИ 38, причем вход нового адреса (вход НА) удалителя сигналов (УС) соединен с первым входом элемента И 34, второй вход которого соединен с выходом инвертора 31, вход которого, а также первый вход элемента И 35 являются входом выбора режима (вход РЕЖ) УС, тактовые входы (входы Т1,... ,ТМ) УС соединены соответственно с первыми входами элементов И 371,... ,37М, вторые входы которых соединены с выходами соответствующих инверторов 321,... ,32М, входы последних соединены соответственно с выходами соответствующих элементов И 361,... ,36М, первые входы которых соединены соответственно с разрешающими входами (входы 1,... ,М) УС, вход управления (вход У) УС соединен с первым входом элемента И 33, выход которого соединен со вторыми входами элементов И 361,... ,36М, вход нулевого состояния (вход DC“0”) УС соединен со вторым входом элемента И 33, третий вход которого соединен с выходом триггера 27, вход конца синхрокомбинации (вход КСК) УС соединен с тактовым входом (вход К) триггера 26, информационный вход (вход D) которого соединен с шиной питания, а вход установки в ноль (вход R) - с выходом триггера 29, выход триггера 26 соединен с информационным входом (вход D) триггера 27 и с входом инвертора 30, выход которого соединен с входами установки в ноль (входы R) триггеров 27, 28, 29, выход триггера 27 соединен с информационным входом (вход D) триггера 28, выход триггера 28 соединен с информационным входом (вход D) триггера 29, тактовый вход (вход Т) УС соединен с тактовыми входами (входы К) триггеров 27, 28, 29, выход элемента И 371 соединен с вторым входом элемента И 35, выход которого соединен с вторым входом элемента ИЛИ 38, первый вход последнего соединен с выходом элемента И 34, выход элемента ИЛИ 38, а также выходы элементов И 372,... ,37М являются тактовыми выходами (выходы Т1,... ,ТМ) УС.

Устройство для ГЦС работает следующим образом. Устройство для ГЦС имеет два режима работы. Первый - режим настройки и диагностики, второй - режим работы.

В первом режиме на входы устройства для ГЦС и далее на входы УН 2 с контроллера, работающего совместно с персональной электронной вычислительной машиной (ПЭВМ), поступают следующие сигналы: выбора режима (вход РЕЖ), равный “Лог.0”, нового адреса (вход НА), установки в ноль (вход RES), записи (вход WE), чтения (вход ОЕ), выбора настройки ОЗУ или регистра (вход ОЗУ/RG), информационные (входы-выходы 0,... ,N). Сигнал выбора режима также поступает на соответствующие входы PC 7 и УС 10. Сигнал нового адреса также поступает на соответствующий вход УС 10.

При настройке ОЗУ на вход ОЗУ/RG УН 2 поступает сигнал “Лог.1”.

Применяемое в устройстве для ГЦС ОЗУ имеет 0,... ,N адресные входы, вход выбора (вход СЕ), вход записи (вход WE), вход чтения (вход ОЕ) и информационные входы-выходы. Разрешение работы ОЗУ осуществляется при наличии сигнала низкого уровня на его СЕ входе. В устройстве для ГЦС вход СЕ ОЗУ соединен с земляной шиной. Запись информации, поступившей на информационные входы-выходы ОЗУ, осуществляется при наличии на его WE входе сигнала “Лог.0”, а на ОЕ входе - сигнала “Лог.1”. Чтение информации, запомненной в ОЗУ, осуществляется при наличии на его ОЕ входе сигнала “Лог.0”, а на WE входе - сигнала “Лог.1”.

В ОЗУ запоминаются следующие параметры цифровой передачи:

- значение синхрокомбинации (вход-выход Зн);

- позиции синхрокомбинации (вход-выход П);

- конец синхрокомбинации (вход-выход КСК);

- конец цикла (вход-выход КЦ).

Перед настройкой ОЗУ на вход RES УН 2 поступает сигнал установки в ноль. При этом сигналом установки в ноль, поступившим с выхода УН 2 (выход RES) на соответствующий вход ГО 5, счетчики позиций последнего устанавливаются в нулевое состояние. Количество счетчиков позиций в ГО 5 определяется количеством синхронизируемых цифровых потоков. 0,... ,N выходы разрядов 1,... ,М счетчиков позиций ГО 5 соединены соответственно с 01,... ,N1,... ,0М,... ,NМ адресными выходами ГО 5.

В режиме настройки сигналом “РЕЖ”, поступающим на соответствующий вход PC 7, последний удерживается в первом состоянии. При этом сигналом первого состояния, поступающим с выхода 1 PC 7 на соответствующий вход второго коммутатора 9, осуществляется коммутация сигналов, поступающих с 01,... ,N1 выходов разрядов ГО 5 через соответствующие входы второго коммутатора 9 на выходы последнего и далее на адресные входы ОЗУ 1. Таким образом, в режиме настройки, на адресные входы ОЗУ 1 поступают сигналы с адресных выходов первого счетчика позиций ГО 5.

Также сигналом “РЕЖ”, поступающим на соответствующий вход удалителя сигналов 10, последний коммутирует сигналы нового адреса (вход НА) УС 10 на T1 выход последнего. Сигналы с T1 выхода УС 10 поступают на T1 вход ГО 5, являясь тактовыми сигналами первого счетчика позиций последнего.

При настройке ОЗУ 1 на информационные 0,... ,N входы-выходы УН 2 поступают информационные сигналы настройки. При этом сигналы Зн, П, КСК, КЦ с входов-выходов УН 2 поступают на соответствующие входы-выходы ОЗУ 1. Далее по сигналу записи, поступившему на WE вход ОЗУ 1, в последнем по адресу, соответствующему нулевому состоянию первого счетчика позиций ГО 5, запоминается информация, поступившая на входы-выходы ОЗУ 1. После этого по сигналу нового адреса, поступившему на вход НА устройства для ГЦС и далее через УС 10 на T1 вход ГО 5, первый счетчик позиций последнего изменяет свое состояние на единицу. Далее запись данных в ОЗУ 1 осуществляется так же, как описано выше.

Для проверки правильности настройки ОЗУ 1 сигналом установки в ноль, поступившим с RES выхода на соответствующий вход ГО 5, первый счетчик позиций последнего устанавливается в нулевое состояние. После этого сигналом “Лог.1”, поступившим на вход записи (вход WE) УН 2 и далее с WE выхода УН 2 на соответствующий вход ОЗУ 1, последнее переводится в режим чтения. Затем сигналом “Лог.0”, поступившим на вход чтения (вход ОЕ) УН 2 и далее с ОЕ выхода УН 2 на соответствующий вход ОЗУ 1, осуществляется считывание информации из ОЗУ 1 по нулевому адресу последнего. При этом сигналы Зн, П, КСК, КЦ с входов-выходов ОЗУ 1 поступают на соответствующие входы-выходы УН 2 и далее в контроллер ПЭВМ для их сравнения с исходными. Затем по сигналу нового адреса осуществляется смена адреса ОЗУ 1 и считывание данных по новому адресу так же, как было описано ранее.

После настройки и проверки правильности настройки ОЗУ 1 осуществляется настройка регистров запоминания, расположенных в УН 2. Настройка регистров запоминания разрешается сигналом “Лог.0”, поступающим на вход ОЗУ/RG УН 2.

В регистре запоминания в двоичном коде хранятся следующие параметры:

- количество синхронизируемых передач;

- длина цикла передач (в позициях).

При этом порядок настройки и проверки ее правильности такой же, как для ОЗУ. С выходов регистра запоминания УН 2 сигналы, задающие количество синхронизируемых передач и длину цикла передач, поступают соответственно на первые 01,... ,N1 и вторые 02,... ,N2 задающие выходы УН 2.

Перевод устройства для ГЦС в режим работы осуществляется сигналом “Лог.1”, поступающим на вход РЕЖ УН 2. При этом сигналами “Лог.1” и “Лог.0”, поступающими соответственно с выхода WE записи и выхода ОЕ чтения УН 2 на соответствующие входы ОЗУ 1, последнее переводится в режим считывания данных.

Работа устройства для ГЦС осуществляется следующим образом. Сигналы с тактовых Т1,... ,ТМ и информационных И1,... ,ИМ входов устройства для ГЦС поступают на соответствующие входы первого коммутатора 6. Сигналы с тактовых Тi,... ,ТМ входов устройства для ГЦС также поступают на соответствующие входы УС 10. Тактовые сигналы с Т1,... ,ТМ выходов УС 10 поступают на соответствующие входы ГО 5 и далее на тактовые входы счетчиков позиций последнего. Количество тактовых и информационных входов устройства для ГЦС определяется количеством синхронизируемых цифровых передач, задаваемым в двоичном коде сигналами с 01,... ,N1 задающих выходов УН 2. Эти сигналы поступают на соответствующие входы PC 7. Тактовые сигналы на Т-Р вход PC 7 поступают с соответствующего выхода ВА 8. Сигналом на одном из разрешающих 1,... ,М выходов PC 7, поступившим на соответствующие входы первого 6, второго 9, третьего 11 коммутаторов и УС 10, разрешается:

- коммутация информационного и тактового сигналов соответствующей цифровой передачи с соответствующих входов первого коммутатора 6 на его информационный и тактовый выходы;

- коммутация сигналов с адресных выходов соответствующего счетчика позиций ГО 5, поступивших на соответствующие адресные выходы ГО 5 и далее на соответствующие адресные входы второго коммутатора 9, на адресные выходы последнего;

- коммутация сигнала наличия синхронизации, поступившего с Ф выхода ФУ 4 на соответствующий вход третьего коммутатора 11, на выход наличия синхронизации устройства для ГЦС для соответствующей цифровой передачи;

- с помощью УС 10 осуществлять удаление тактового сигнала соответствующей цифровой передачи, поступившего с определенного входа устройства для ГЦС на соответствующий вход УС 10, в режиме поиска синхронизма этой передачи.

Адресные выходы второго коммутатора 9 соединены с адресными входами ОЗУ 1. Таким образом на адресные входы ОЗУ 1 поступают адресные сигналы с выходов разрядов соответствующего счетчика позиций ГО 5. Тактовые и информационные сигналы определенной цифровой передачи с информационного и тактового выходов первого коммутатора 6 поступают на соответствующие входы ДС 3. Тактовые сигналы с выхода первого коммутатора 6 также поступают на соответствующий тактовый вход УС 10 и тактовый вход третьего коммутатора 11.

В исходном состоянии сигналом с разрешающего выхода 1 PC 10 адресные входы ОЗУ 1 через второй коммутатор 9 и адресные 01,... ,N1 выходы ГО 5 подключены к первому счетчику позиций ГО 5. Сигнал наличия синхронизации, поступающий с Ф выхода ФУ 4 на соответствующий вход третьего коммутатора 11, коммутируется последним на выход наличия синхронизации первой цифровой передачи (выход F1 устройства для ГЦС). Удалитель сигналов 10 находится в режиме удаления тактовых сигналов, поступающих на его T1 вход с соответствующего входа устройства для ГЦС. Тактовые сигналы первой цифровой передачи коммутируются первым коммутатором 6 с входа T1 устройства для ГЦС на тактовые" входы (входы Т) УС 10, ДС 3 и третьего коммутатора 11. Информационные сигналы первой цифровой передачи коммутируются первым коммутатором 6 с входа И1 устройства для ГЦС на информационный вход (вход И) ДС 3.

Работа устройства для ГЦС начинается с проверки наличия синхронизации скоммутированной цифровой передачи. Максимальный период проверки наличия синхронизации равен произведению длины цикла передачи и удвоенного значения критерия выхода из синхронизма. Если за период проверки устройство для ГЦС не вышло из синхронизма, то в ВА 8 формируется тактовый сигнал, который с Т-Р выхода последнего поступает на соответствующий вход PC 7, изменяя его состояние. После этого осуществляется проверка наличия синхронизации следующей цифровой передачи. Если же за период проверки наличия синхронизации был зафиксирован выход из синхронизма, то устройство для ГЦС переходит в режим поиска синхронизма подключенной цифровой передачи. Максимальный период поиска синхронизма равен сумме двух величин:

1) длина цикла цифровой передачи, возведенная в квадрат;

2) произведение длины цикла на удвоенное значение критерия выхода из синхронизма.

Если за период поиска синхронизма синхронизация не найдена, то в ВА 8 формируется тактовый сигнал, по которому, как было описано ранее, PC 7 устанавливается в следующее состояние, подключая для анализа следующую цифровую передачу. Во втором положении PC 7 сигналом с его разрешающего выхода 2 адресные входы ОЗУ 1 подключаются к адресным выходам второго счетчика позиций ГО 5, сигнал наличия синхронизации подключается к выходу Ф2 устройства для ГЦС, УС 10 устанавливается в режим удаления тактовых сигналов, поступающих на его T2 вход, информационные и тактовые сигналы второй цифровой передачи (входы И2 и Т2) устройства для ГЦС коммутируются на информационный и тактовый выходы первого коммутатора 6. В дальнейшем устройство для ГЦС работает так же, как было описано выше. После анализа последней цифровой передачи PC 7 вновь устанавливается в первое состояние и цикл проверки наличия и поиска синхронизации цифровых передач осуществляется как было описано ранее.

Работа устройства для ГЦС при поиске синхронизации цифровых передач осуществляется следующим образом. Сигналы с выходов значения синхрокомбинации (выход Зн), позиции синхрокомбинации (выход П) и конца синхрокомбинации (выход КСК) ОЗУ 1, а также тактовые и информационные сигналы поступают на соответствующие входы ДС 3. ДС 3 осуществляет поэлементное сравнение информационных сигналов на позициях синхрокомбинации с ее значениями, заданными в ОЗУ 1, и формирование результата сравнения на выходе отклика (выход СК). В случае совпадения сигналов значения синхрокомбинации на ее позициях, заданных в ОЗУ 1, с входной информационной последовательностью на выходе отклика (выход СК) ДС 3 формируется сигнал “Лог.1”, а при несовпадении - сигнал “Лог.0”. Сигналы с выхода отклика ДС 3 и с выхода конца синхрокомбинации (выход КСК) ОЗУ 1 поступают на соответствующие входы ФУ 4.

Фазирующее устройство работает следующим образом. При отсутствии на его входе отклика сигнала “Лог.1”, т.е. положительного отклика наличия синхрокомбинации, реверсивный счетчик ФУ 4 находится в нулевом состоянии. Сигналом с выхода нулевого состояния (выход DC“0”) ФУ 4 разрешается работа УС 10. При поступлении на входы ФУ 4 положительного отклика и конца синхрокомбинации с соответствующих выходов ДС 3 и ОЗУ1 реверсивный счетчик ФУ 4 устанавливается в режим положительного счета и увеличивает свое состояние на единицу. При этом сигналом с выхода нулевого состояния ФУ 4 запрещается работа УС 10. Таким образом, при наличии сигнала дешифрации синхрокомбинации, реверсивный счетчик ФУ4 увеличивает свое состояние на единицу, а при отсутствии - уменьшает свое состояние на единицу. Когда разность сигналов наличия и отсутствия синхрокомбинации достигает значения входа в синхронизм, реверсивный счетчик ФУ 4 устанавливается в максимальное состояние. Таким образом, устройство для ГЦС переходит в режим синхронизма, о чем свидетельствует сигнал “Лог.1” на выходе наличия синхронизации (выход Ф) ФУ 4. В этом режиме устройство для ГЦС находится до тех пор, пока разность сигналов отсутствия и наличия синхрокомбинации не достигнет значения критерия выхода из синхронизма. При этом ФУ 4 устанавливается в нулевое состояние и устройство для ГЦС переходит в режим поиска синхронизма, как было описано выше.

Проведенные эксперименты показали, что для устройств цикловой синхронизации оптимальное значение критерия входа в синхронизм равно 4, а значение критерия выхода из синхронизма равно 8.

Генераторное оборудование 5 содержит счетчики позиций и дешифраторы концов циклов. Количество счетчиков позиций и дешифраторов концов циклов равно количеству синхронизируемых цифровых передач. Длина цикла передач задается сигналами в двоичном коде, поступающими с вторых 02,... ,N2 задающих выходов УН 2 на 0,... ,N задающие входы ГО 5.

Временной анализатор (фиг.2) работает следующим образом. Первоначально проверяется наличие синхронизации соответствующей цифровой передачи. При этом сигнал конца цикла с входа КЦ временного анализатора поступает на тактовый вход (вход К) первого счетчика 12. После поступления на тактовый вход первого счетчика 12 количества сигналов, равного удвоенному критерию выхода из синхронизма, на выходе первого счетчика 12 формируется сигнал, который, поступая на тактовый вход (вход К) первого триггера 15, устанавливает его в единичное состояние. При этом сигнал с выхода первого триггера 15 поступает на выход управления (выход У) ВА, на вход первого инвертора 18 и на первые разрешающие входы первого 22 и второго 23 элементов И. Сигнал “Лог.0” с выхода второго инвертора 18 поступает на первый вход второго элемента ИЛИ 20. Если при проверке наличия синхронизации соответствующей цифровой передачи устройство для ГЦС не вышло из синхронизма, то на вход наличия синхронизма (вход Ф) ВА и далее на вторые разрешающие входы первого 22, второго 23 элементов И и на второй вход второго элемента ИЛИ 20 поступает сигнал “Лог.1”. При этом, сигналом с выхода второго элемента ИЛИ 20, поступающим на входы установки в ноль (входы R) второго 13, третьего 14 счетчиков и второго триггера 16, последние устанавливаются в нулевое состояние. Сигнал конца цикла через открытый первый элемент И 22 и третий элемент ИЛИ 21 поступает на тактовый выход (выход Т-Р) ВА. После этого сигналом, поступающим с выхода инвертора 17 через открытый по первому и второму входу второй элемент И 23 и первый элемент ИЛИ 19, на входы установки в ноль (входы R) первого счетчика 12 и первого триггера 15, последние устанавливаются в нулевое состояние. Тактовый сигнал, поступая с выхода ВА на вход распределителя сигналов, изменяет его состояние, тем самым подключая для проверки синхронизации следующую цифровую передачу. В случае, если при проверке наличия синхронизации соответствующей цифровой передачи устройство для ГЦС вышло из синхронизма, то оно переходит в режим поиска синхронизма. При этом на первый и второй входы второго элемента ИЛИ 20 поступают сигналы “Лог.0” соответственно с выхода второго инвертора 18 и Ф входа ВА.

Выходным сигналом “Лог.0”, поступающим с выхода второго элемента ИЛИ 20 на входы установки в ноль второго 13, третьего 14 счетчиков и второго триггера 16, разрешается работа последних.

Второй счетчик 13 подсчитывает количество сигналов конца цикла, поступивших на его тактовый вход (вход К) с КЦ входа ВА. При достижении вторым счетчиком 13 числа равного количеству позиций в цикле цифровой передачи, заданному в двоичном коде сигналами, поступающими с 0,... ,N задающих входов ВА на соответствующие входы второго счетчика 13, на выходе последнего формируется сигнал, который поступает на разрешающий вход (вход ЕС) триггера 16. Далее по сигналу конца цикла, поступившему на тактовый вход (вход К) триггера 16, последний устанавливается в единичное состояние, и своим выходным сигналом, поступившим на разрешающий вход (вход ЕС) третьего счетчика 14, разрешает его работу. После поступления на тактовый вход (вход К) третьего счетчика 14 количества сигналов конца циклов, равного удвоенному значению критерия входа в синхронизм, на выходе третьего счетчика 14 формируется сигнал, который указывает на то, что синхронизация не найдена. При этом сигнал с выхода третьего счетчика 14 поступает на первые входы третьего 24 и четвертого 25 элементов И, разрешая их работу. Сигнал конца цикла через открытый третий элемент И 24 и третий элемент ИЛИ 21 поступает на тактовый выход ВА и далее на соответствующий вход PC, изменяя его состояние, тем самым разрешая проверку наличия синхронизации и поиск синхронизма следующей по порядку цифровой передачи. После этого сигналом, поступившим с выхода инвертора 17, через открытый четвертый элемент И 25 и второй элемент ИЛИ 20 на входы установки в ноль второго 13 и третьего 14 счетчиков, а также второго триггера 16, последние устанавливаются в нулевое состояние. Этим же сигналом, поступившим через элемент ИЛИ 19 на входы установки в ноль первого счетчика 12 и первого триггера 15, последние также устанавливаются в нулевое состояние.

Если в процессе поиска синхронизма на Ф входе ВА появился сигнал наличия синхронизма, то, как было описано ранее, первый 12, второй 13 и третий 14 счетчики, первый 15 и второй 16 триггеры устанавливаются в нулевое состояние, а на выходе третьего элемента ИЛИ 21 формируется тактовый сигнал, который с Т-Р выхода ВА поступает на соответствующий вход PC, устанавливая его в следующее состояние, разрешая проверку наличия синхронизации и поиск синхронизма следующей по порядку цифровой передачи.

Удалитель сигналов (фиг.3) работает следующим образом. Если при проверке цифровой передачи на наличие синхронизации последняя не будет подтверждена, то устройство для ГЦС переходит в режим поиска синхронизма соответствующей цифровой передачи. Поиск синхронизма осуществляется следующим образом. На каждом цикле цифровой передачи осуществляется запись информационных сигналов на позициях синхрокомбинации и сравнение их с заданными в ОЗУ. Позиции синхрокомбинации конкретной цифровой передачи определяются состоянием соответствующего счетчика позиций ГО, адресные выходы которого подключены к адресным входам ОЗУ. Если в течение цикла цифровой передачи синхрокомбинация не найдена, то с помощью удалителя сигналов осуществляется пропуск одного тактового сигнала, поступающего на соответствующий тактовый вход счетчика позиций ГО, и указанный счетчик изменяет свою фазу работы по отношению к фазе цифровой передачи. Указанный порядок работы происходит до тех пор, пока не будет найдена первая синхрокомбинация. После чего запрещается удаление тактовых сигналов и осуществляется проверка наличия синхрокомбинации на соответствующих позициях цифровой передачи. В случае выполнения критерия входа в синхронизм устройство для ГЦС переходит в режим синхронизма, что указывает на соответствие фазы работы счетчика позиций ГО с фазой определенной цифровой передачи.

При поиске синхронизма на вход управления (вход У) УС с соответствующего выхода ВА поступает сигнал “Лог.1”, а на вход начального состояния (вход DC“0”) УС с соответствующего выхода ФУ также поступает сигнал “Лог.1”. Сигналы с входов У и DC“0” удалителя сигналов поступают соответственно на первый и второй входы элемента И33, разрешая его работу. На один из разрешающих входов (входы 1,... ,М) УС с соответствующего выхода PC поступает сигнал “Лог.1”. Этот сигнал, поступая на первый вход одного из элементов И 361,... ,И 36М, разрешает его работу. На тактовые входы (входы Т1,... ,ТМ) УС поступают сигналы с соответствующих входов устройства для ГЦС. На вход конца синхрокомбинации (вход КСК) УС поступает сигнал с соответствующего выхода ОЗУ. Этот сигнал, поступая с КСК входа УС на тактовый вход (вход К) триггера 26, устанавливает его в единичное состояние. Сигнал единичного уровня с выхода триггера 26 поступает на информационный вход (вход D) триггера 27 и через инвертор 30 - на входы установки в ноль (входы R) триггеров 27, 28, 29, разрешая их работу. На тактовые входы (входы К) триггеров 27, 28, 29 поступают сигналы с тактового входа (вход Т) УС, соединенного с соответствующим выходом первого коммутатора. Триггеры 27, 28 отрицательным фронтом тактовых сигналов устанавливаются последовательно в единичное состояние, а затем, положительным фронтом тактового сигнала в единичное состояние устанавливается триггер 29. После чего сигналом с выхода триггера 29 устанавливается в нулевое состояние триггер 26, который выходным сигналом через инвертор 30 устанавливает в начальное состояние триггеры 27, 28, 29. После установки триггера 27 в единичное состояние на третий вход элемента И 33 поступает сигнал “Лог.1”, который с выхода последнего поступает на вторые входы элементов И 361,... ,И 36м. С выхода разрешенного по первому входу соответствующего элемента И 361...,И 36м сигнал логической единицы поступает на вход соответствующего инвертора 321,... ,32м, на выходе которого формируется сигнал “Лог.0”, запрещающий по второму входу работу соответствующего элемента И 371,... ,И 37м, тем самым запрещая прохождение через этот элемент тактового сигнала соответствующей цифровой передачи с одного из тактовых Т1,... ,ТМ входов УС на соответствующий его выход. При этом при работе сигналом “Лог.1” с входа РЕЖ УС разрешается работа элемента И 35, тем самым разрешается прохождение тактового сигнала первой цифровой передачи с выхода элемента И 371 через элемент И 35 и элемент ИЛИ 38 на тактовый T1 выход УС. При настройке сигналом “Лог.0” с входа РЕЖ УС через инвертор 31 разрешается работа элемента И 34, тем самым разрешается прохождение сигнала с входа нового адреса (вход НА) УС через элемент И 34 и элемент ИЛИ 38 на тактовый T1, выход УС.

Для технической реализации устройства для ГЦС использовано статическое оперативное запоминающее устройство импортного производства типа KM68257CJ-15 фирмы SEC и перепрограммируемая логическая интегральная схема XC4020XLA фирмы XILINX.

Предлагаемое изобретение позволяет осуществить одним устройством цикловую синхронизацию группы цифровых передач одинаковой структуры с одновременным сокращением аппаратурных затрат, энергопотребления и повышением надежности и помехоустойчивости, т.к. для цикловой синхронизации группы цифровых передач используется одно ОЗУ вместо N аналогичных ОЗУ. Применение одного ОЗУ также позволяет сократить количество печатных проводников и увеличить их полезную площадь, тем самым уменьшить удельное сопротивление и вероятность нарушения соединений между элементами устройства.

Источники информации

1. Патент РФ №2019046, H 04 L 7/08.

2. Патент РФ №2136111, H 04 L 7/08.

3. Левин Л.С., Плоткин М.А. Цифровые системы передачи информации. М.: Радио и связь. С.101-102, рис.4.4.

4. Патент РФ №2187210, H 04 L 7/08.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2256295C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2286020C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302084C2 |

| УСТРОЙСТВО ДЕСКРЕМБЛИРОВАНИЯ | 2006 |

|

RU2310991C2 |

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2005 |

|

RU2296431C2 |

Изобретение относится к технике цифровой связи и может использоваться для цикловой синхронизации цифровых систем передачи информации с временным уплотнением. Достигаемый технический результат - сокращение аппаратурных затрат, энергопотребления и повышение надежности и помехоустойчивости. Устройство для групповой цикловой синхронизации содержит оперативное запоминающее устройство, устройство настройки, дешифратор синхрокомбинации, фазирующее устройство, генераторное оборудование, три коммутатора, распределитель сигналов, временной анализатор и удалитель сигналов. 1 з.п. ф-лы, 3 ил.

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1998 |

|

RU2136111C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| US 5710774 А, 20.01.1998 | |||

| US 5862143 А, 19.01.1999 | |||

| Коммутационная матрица с гезаконами | 1982 |

|

SU1292063A1 |

Авторы

Даты

2005-03-20—Публикация

2003-06-23—Подача