(Изобретение относится к вычислитель- ной|технике и предназначено для контроля логических узлов.

Цель изобретения - увеличение производительности устройства за счет увеличения частоты подачи входных воздействий на объект контроля, сокращения объема памяти, необходимой для хранения программ те- контроля.

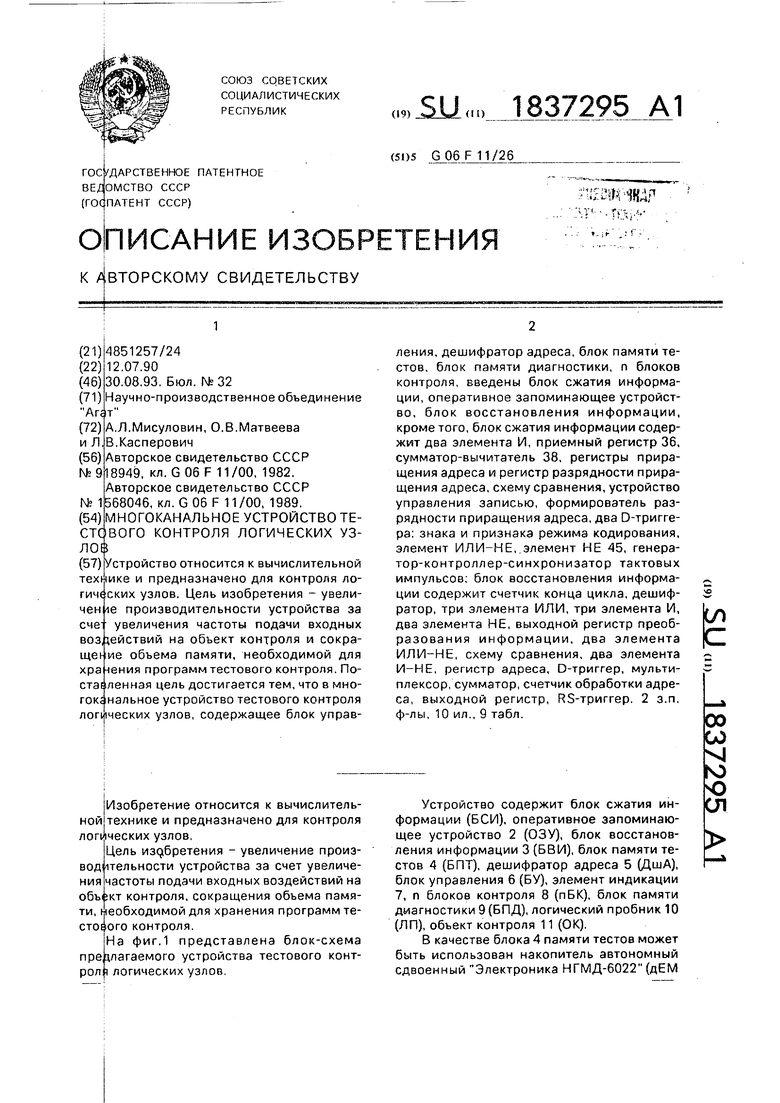

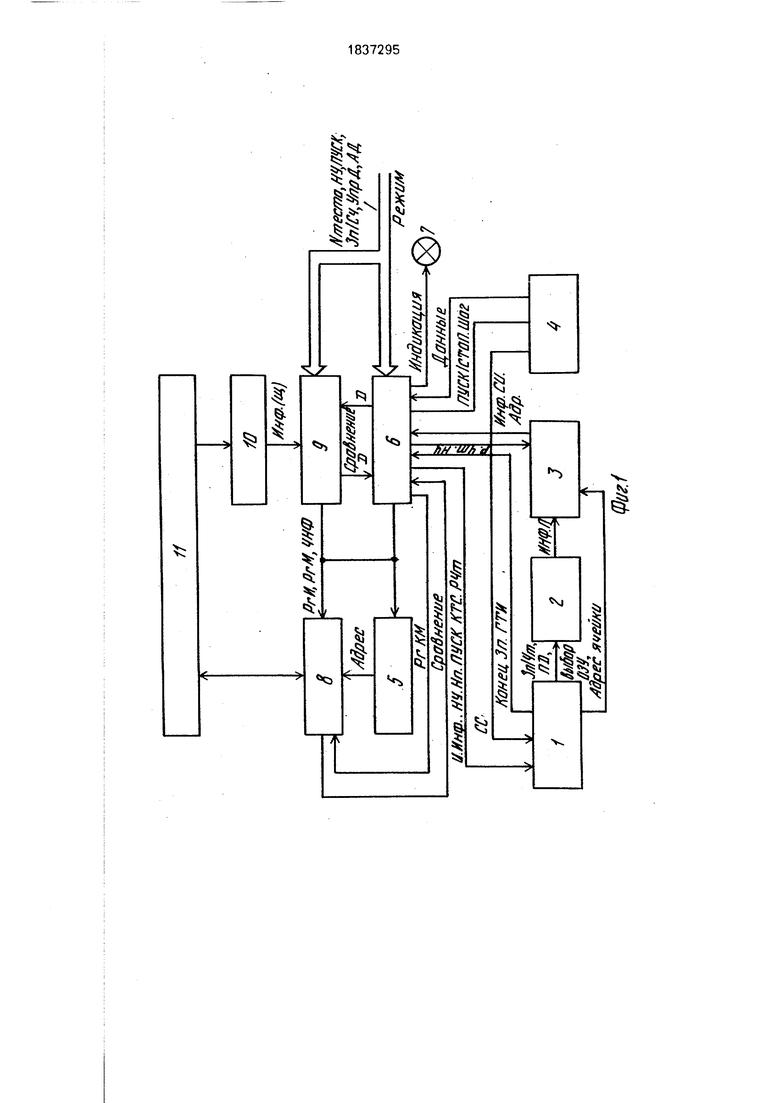

На фиг.1 представлена блок-схема предлагаемого устройства тестового контроля логических узлов.

Устройство содержит блок сжатия информации (БСИ), оперативное запоминающее устройство 2 (ОЗУ), блок восстановления информации 3 (БВИ), блок памяти тестов 4 (БПТ), дешифратор адреса 5 (ДшА), блок управления 6 (БУ), элемент индикации 7, п блоков контроля 8 (пБК), блок памяти диагностики 9 (БПД), логический пробник 10 (ЛП), объект контроля 11 (ОК).

В качестве блока 4 памяти тестов может быть использован накопитель автономный сдвоенный Электроника НГМД-6022 (дЕМ

3,853.123-01 ТО). Блок ОЗУ 2 представляет собой однотипные ячейки ОЗУ, в качестве которых могут быть использованы микросхемы 537 РУ 2А. ОЗУ 2 имеет гарантированное питание. ДшА 5 представляет собой n-разрядный двоичный дешифратор, где п log2 N, при этом N - количество проверяемых каналов ОК 11.

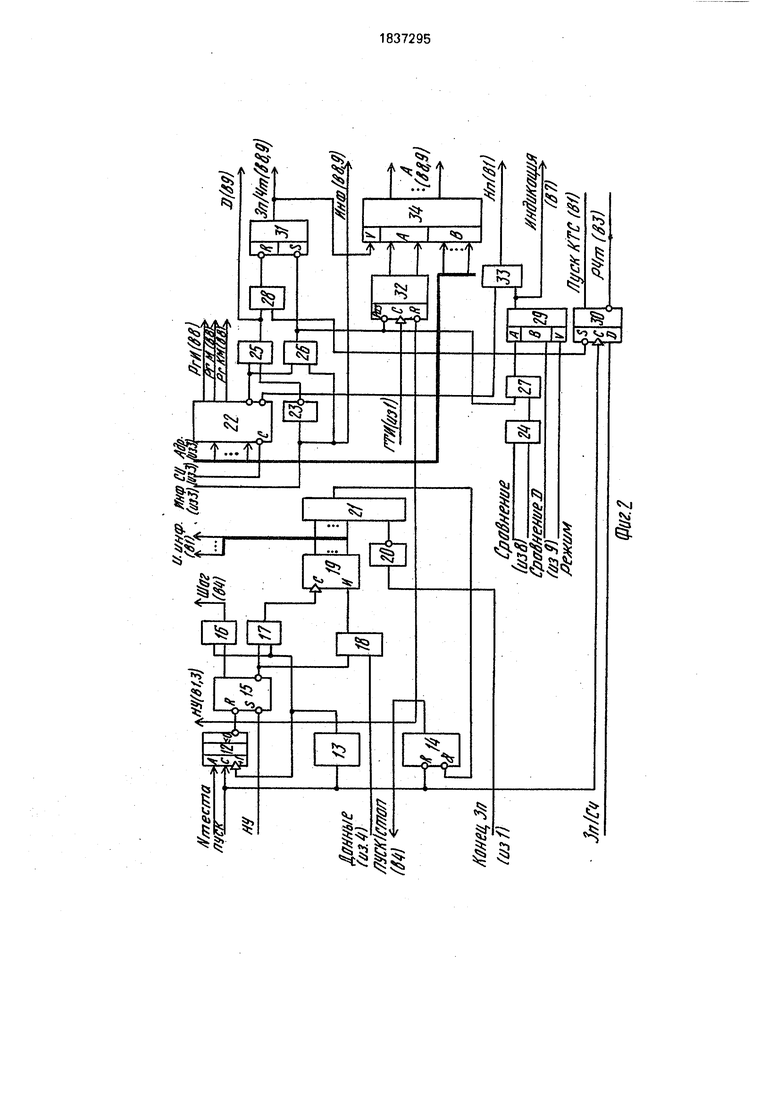

На фиг.2 представлена блок-схема БУ 6, который содержит счетчик 12 номера теста (СчТ), генератор-контроллер-синхронизатор 13 тактовых импульсов (G), триггеры 14, 15, элементы 16-18 И, сдвиговый регистр 19 (Рг), элемент НЕ 20, элемент И 21, дешифратор 22 маркера, элемент НЕ 2, элемент И 24. элементы 25, 26, 27 ИЛИ, элемент И 28. мультиплексор 29 неисправности Мх Ни, D- триггерЗО, Н8-триггер31, счетчик адреса 32 (Сч А), элемент И 33, мультиплексор 34 адреса (МХА).

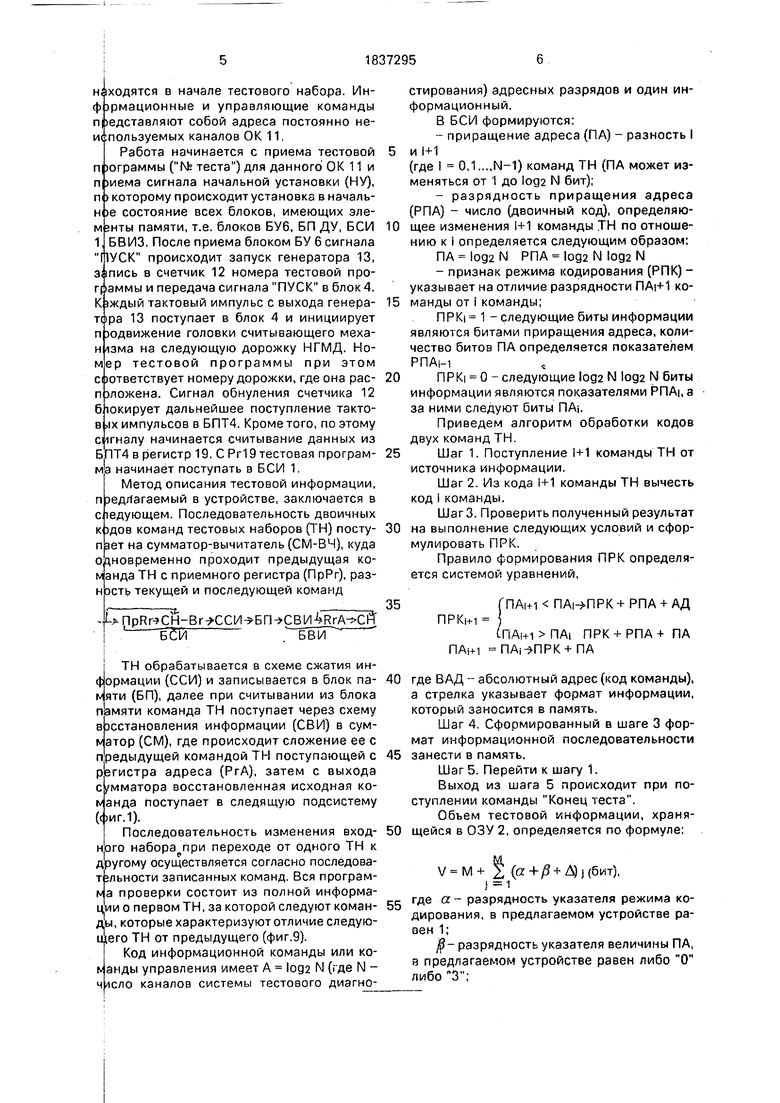

На фиг.З представлена блок-схема предлагаемого блока сжатия информации, который содержит элемент 35 И, приемный регистр 36 (прРг), триггер 37, сумматор-вы- читатель 38 (СМ-В), элемент 39 И, контрол- л ер-синхронизатор-генератор тактовых импульсов G 40, D-триггер 41 знака (ТгЗн), регистр 42 прира,щения адреса (РгПА), элемент ИЛИ 43, формирователь разрядности приращения адреса 44, (ФРПА), элемент НЕ 45, регистр 46 разрядности приращения адреса (РгРПА), RS-триггер 47, схему сравнения 48(СС), DC-триггер 49 признака режима кодирования (ТгПРК), устройство 50 управления записью (УУЗ).

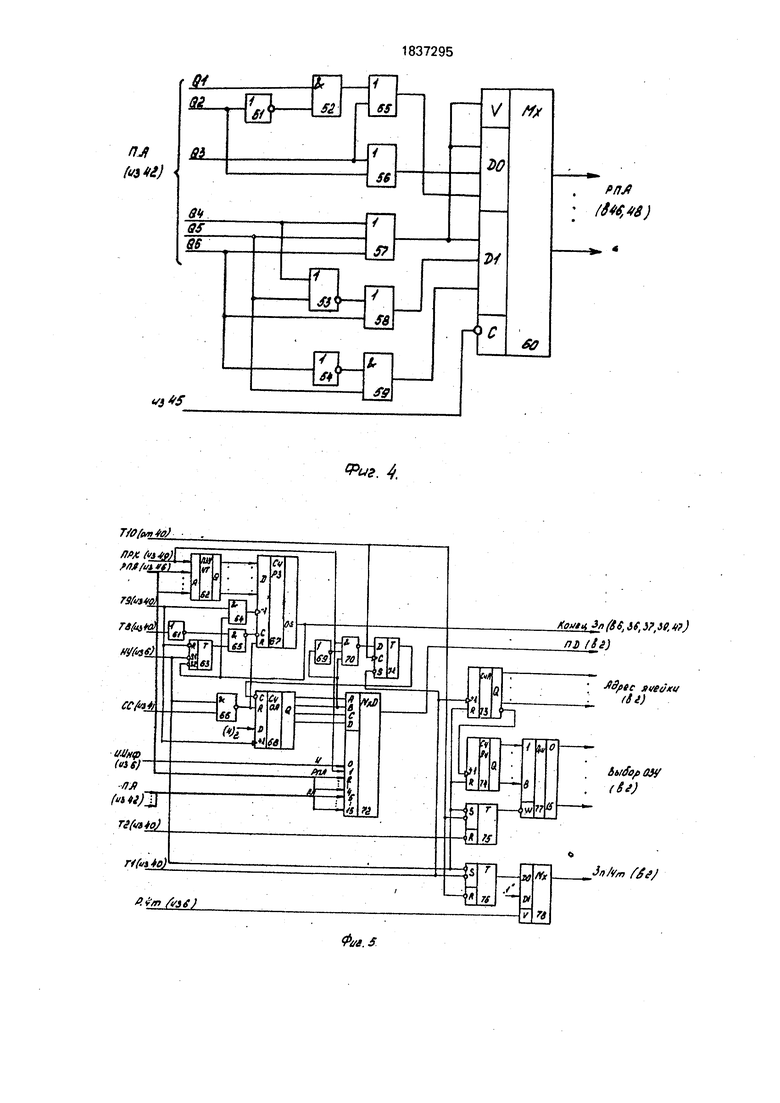

На фиг.4 представлена блок-схема ФРПА 44, состоящего из элемента 51 НЕ, элемента И 52, элемента ИЛИ-НЕ 53, элемента НЕ 54, элементов ИЛИ 55, 56, 57, 58 элемента И 59. мультиплексора 60.

На фиг.5 представлен пример выполнения УУЗ 50, который содержит элемент 61 НЕ, ПЗУ 62 числа тактов (ПЗУ, ЧТ), RS-триггер 63, элемент И 64, элемент И-НЕ 65, 66 счетчик 67 разрешения записи (Сч РЗ), счет- чик 68 обработки адреса (СчОА), элемент 69 НЕ, элемент И-НЕ 70, мультиплексор 72 данных (МхД), D-триггер 71, счетчик 73 адреса, счетчик 74 ячеек ОЗУ, RS-триггеры 75, 76, дешифратор 77, мультиплексор 78.

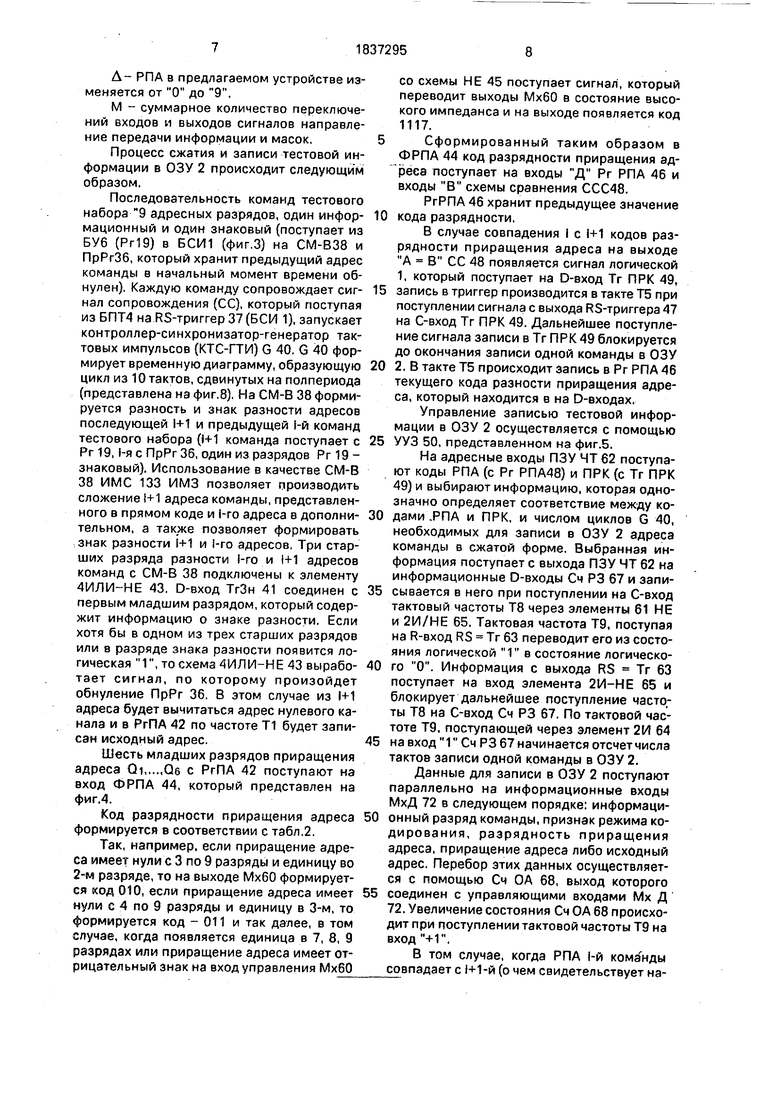

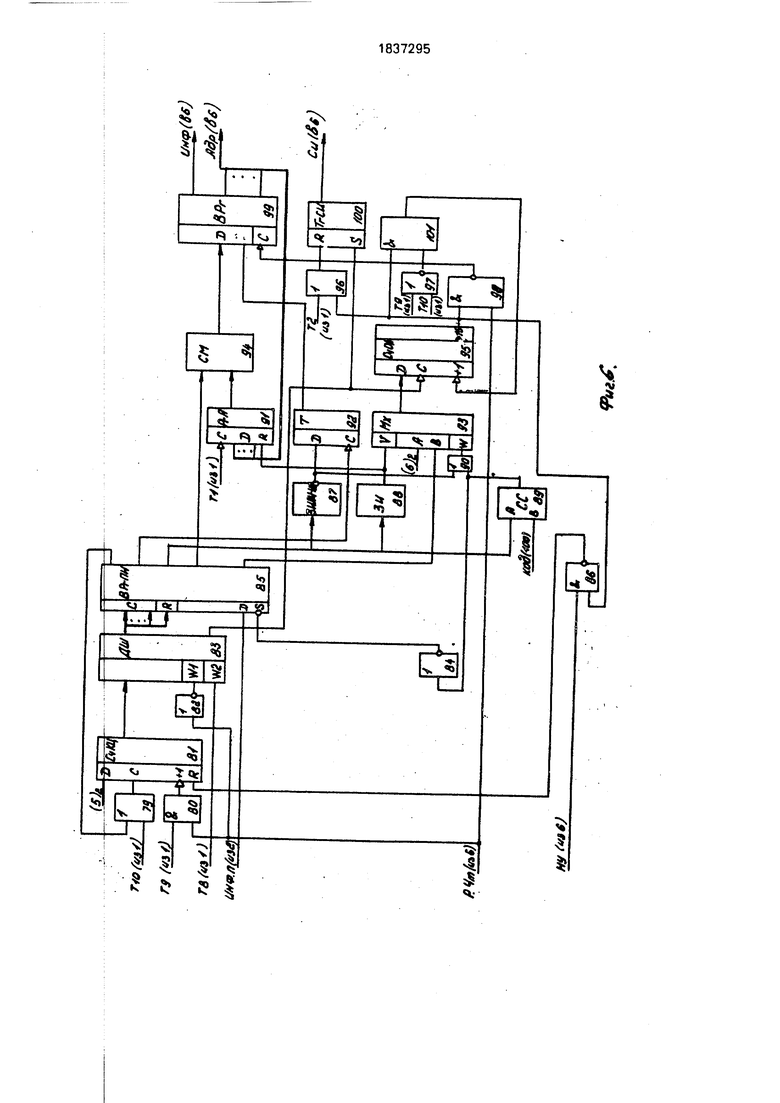

На фиг.6 представлена блок-схема предлагаемого блока восстановления информации БВИ 3, который состоит из элемента ИЛИ 79, элемента И 80, счетчика 81 конца цикла (СчУЦ), элемента НЕ 82, дешиф- ратора 83, элемента НЕ 84, выходного регистра 85 преобразования информации (ВРгПИ), элемента И-НЕ 86, элемента 3 ИЛИ-НЕ 87, элемента 3 И 88, схемы сравнения 89 (СС), элемента ИЛИ 90, регистра 91

адреса (РгА), D-триггера 92, мультиплексора 93, сумматора 94, счетчика 95 обработки адреса (СчОА), элемента ИЛИ 96, элемента ИЛИ-НЕ 97, элемента И-НЕ 98, выходного регистра 99 (ВРг), RS-триггера 100 синхроимпульсов (ТгСИ), элемента И 101.

На фиг.7 представлена блок-схема выходного регистра преобразования информации, входящего в состав БВИ.

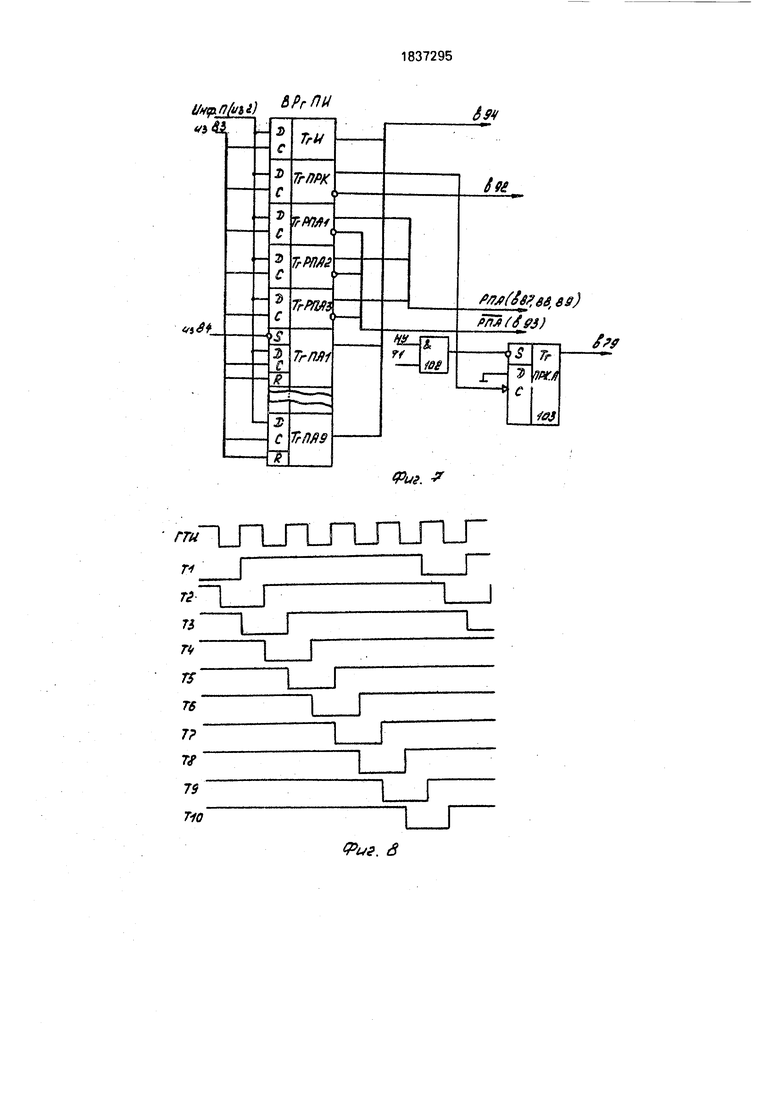

На фиг,8 представлена временная диаграмма работы контроллера-синхронизатора-генератора.

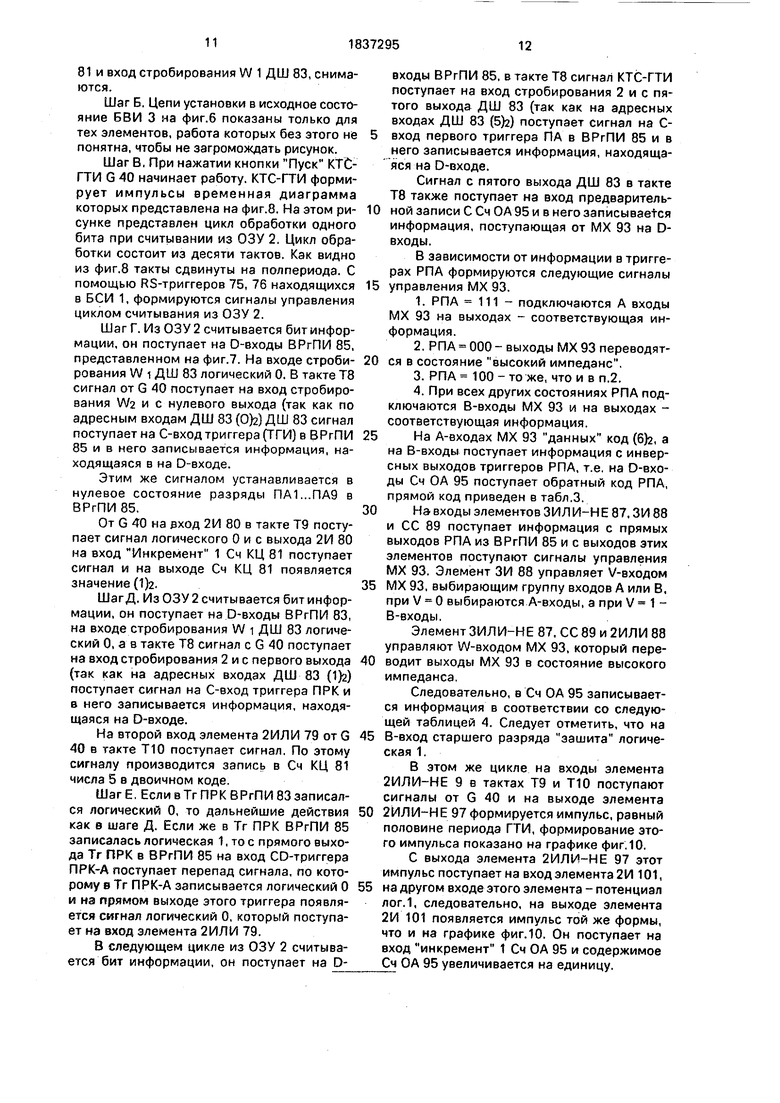

На фиг.9 представлен порядок расположения данных в тестовой программе.

При работе в режиме проверки многоканальное устройство тестового контроля логических узлов подает на внешние контакты ОК 11 входные воздействия и снимает ответные реакции с них, а затем сравнивает с эталонными. Входные воздействия и ожидаемые эталонные реакции ОК 11 определены тестовой программой.

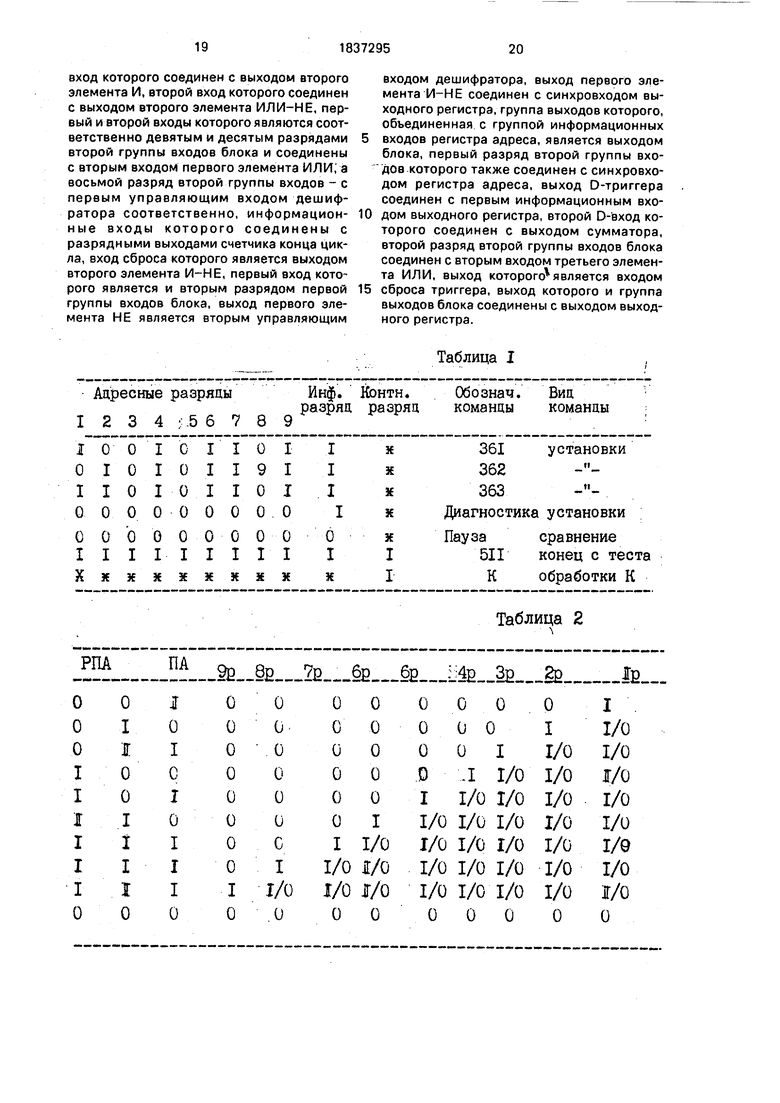

Тестовая программа представляет собой последовательность тестовых наборов, которые состоят из информационных команд и команд управления (фиг.9). Вся тестовая программа состоит из полной информации о первом тестовом наборе, за которой следуют команды, которые характеризуют отличие следующего тестового набора от предыдущего. Назначение входов-выходов ОК 11 происходит по адресам каналов (номера контактов подключения ОК 11 к многоканальному устройству тестового контроля логических узлов), следующим после команды управления окоммутация, входные воздействия и выходные реакции ОК 11 (информационные команды) также списываются состоянием канала по его адресу и располагаются в тестовом наборе после команды управления информация. Аналогично, по команде управления маска происходит объявление об установке и снятии маски. Командой сравнения и обработки К (пауза и К), записанной в конце каждого тестового набора, включается микропрограмма сравнения выходной реакции ОК 11 с эталонной. По команде конца теста (511), записанной в конце тестовой программы, происходит ее останов и фиксация результата проверки. Для выделения диагностической части программы служит команда диагностика. Команды управления приведены в табл. 1.

В предлагаемом устройстве количество каналов ОК 1.1 описывается 9-ти разрядным двоичным адресом. Наличие контрольного разряда означает начало нового тестового набора. В командах установки контрольный разряд присутствует в том случае, когда они

находятся в начале тестового набора. Информационные и управляющие команды представляют собой адреса постоянно неиспользуемых каналов ОК 11,

Работа начинается с приема тестовой программы (№ теста) для данного ОК 11 и приема сигнала начальной установки (НУ), по которому происходит установка в начальное состояние всех блоков, имеющих эле- мзнты памяти, т.е. блоков БУ6, БП ДУ, БСИ 1, БВИЗ, После приема блоком БУ 6 сигнала ПУСК происходит запуск генератора 13, запись в счетчик 12 номера тестовой программы и передача сигнала ПУСК в блок 4. Каждый тактовый импульс с выхода генератора 13 поступает в блок 4 и инициирует продвижение головки считывающего меха- н 1зма на следующую дорожку НГМД. Номер тестовой программы при этом соответствует номеру дорожки, где она расположена. Сигнал обнуления счетчика 12 блокирует дальнейшее поступление такто- в мх импульсов в БПТ4. Кроме того, по этому сигналу начинается считывание данных из БЛТ4 в регистр 19, С Рг19 тестовая программа начинает поступать в БСИ 1.

Метод описания тестовой информации, пэедЛагаемый в устройстве, заключается в следующем. Последовательность двоичных кодов команд тестовых наборов (ТН) поступает на сумматор-вычитатель (СМ-ВЧ), куда одновременно проходит предыдущая команда ТН с приемного регистра (ПрРг), раз- нэсть текущей и последующей команд

-U ПрНг4СЙ-Вг ССИ- БП- СВИ4ЯгА СН .

ТН обрабатывается в схеме сжатия информации (ССИ) и записывается в блок памяти (БП), далее при считывании из блока памяти команда ТН поступает через схему вэсстановления информации (СВИ) в сумматор (СМ), где происходит сложение ее с предыдущей командой ТЫ поступающей с регистра адреса (РгА), затем с выхода с/мматора восстановленная исходная команда поступает в следящую подсистему (оиг.1).

Последовательность изменения входного набора при переходе от одного ТН к другому осуществляется согласно последовательности записанных команд. Вся программа проверки состоит из полной информации о первом ТН, за которой следуют коман ды, которые характеризуют отличие следующего ТН от предыдущего (фиг.9).

Код информационной команды или ко- ы анды управления имеет А Iog2 N (где N - члсло каналов системы тестового диагно-

стирования) адресных разрядов и один информационный.

В БСИ формируются:

-приращение адреса (ПА) - разность I и 1+1

(где I 0,1...,М-1) команд ТН (ПА может изменяться от 1 до log,2 N бит);

-разрядность приращения адреса (РПА) - число (двоичный код), определяющее изменения 1+1 команды ТН по отношению к i определяется следующим образом: nA log2N РПА од2 N logaN

-признак режима кодирования (РПК) - указывает на отличие разрядности ПА|+1 команды от i команды;

ПРК| 1 - следующие биты информации являются битами приращения адреса, количество битов ПА определяется показателем РПАы

ПРК| 0 - следующие Iog2 N Iog2 N биты

информации являются показателями РПА|, а за ними следуют биты ПА|,

Приведем алгоритм обработки кодов двух команд ТН.

Шаг 1. Поступление 1+1 команды ТН от

источника информации.

Шаг 2. Из кода 1+1 команды ТН вычесть код I команды.

Шаг 3. Проверить полученный результат на выполнение следующих условий и сформулировать ПРК.

Правило формирования ПРК определяется системой уравнений,

ГПАц-1 ПА|- ПРК+РПА + АД

ПРКн-1

1ПА|+1 ПА| ПРК + РПА + ПА ПАн-1 ПА(- ПРК+ПА

где ВАД -- абсолютный адрес (код команды), а стрелка указывает формат информации, который заносится в память,

Шаг 4, Сформированный в шаге 3 формат информационной последовательности занести в память.

Шаг 5. Перейти к шагу 1. Выход из шага 5 происходит при поступлении команды Конец теста.

Объем тестовой информации, храня- щейся в ОЗУ 2, определяется по формуле:

55

V M+ Ј (« +/ + Д) | (бит),

1 1

где а. - разрядность указателя режима кодирования, в предлагаемом устройстве ра- аен 1;

$- разрядность указателя величины ПА, в предлагаемом устройстве равен либо О либо

А- РПА в предлагаемом устройстве изменяется от О до 9,

М - суммарное количество переключений входов и выходов сигналов направление передачи информации и масок.

Процесс сжатия и записи тестовой информации в ОЗУ 2 происходит следующим образом.

Последовательность команд тестового набора 9 адресных разрядов, один информационный и один знаковый (поступает из БУ6 (Рг19) в БСИ1 (фиг.З) на СМ-В38 и ПрРгЗб, который хранит предыдущий адрес команды в начальный момент времени обнулен). Каждую команду сопровождает сигнал сопровождения (СС), который поступая из БПТ4 на RS-триггер 37 (БСИ 1), запускает контроллер-синхронизатор-генератор тактовых импульсов {КТС-ГТИ) G 40. G 40 формирует временную диаграмму, образующую цикл из 10 тактов, сдвинутых на полпериода (представлена на фиг.З). На СМ-В 38 формируется разность и знак разности адресов последующей 1+1 и предыдущей 1-й команд тестового набора 0+1 команда поступает с Рг 19, i-я с ПрРг 36, один из разрядов Рг 19 - знаковый). Использование в качестве СМ-В 38 ИМС 133 ИМЗ позволяет производить сложение 1+1 адреса команды, представленного в прямом коде и i-ro адреса в дополнительном, а также позволяет формировать знак разности 1+1 и 1-го адресов, Три старших разряда разности 1-го и 1+1 адресов команд с СМ-В 38 подключены к элементу 4ИЛИ-НЕ 43. D-вход ТгЗн 41 соединен с первым младшим разрядом, который содержит информацию о знаке разности. Если хотя бы в одном из трех старших разрядов или в разряде знака разности появится логическая 1, то схема 4ИЛИ-НЕ 43 выработает сигнал, по которому произойдет обнуление ПрРг 36. В этом случае из 1+1 адреса будет вычитаться адрес нулевого канала и в РгПА 42 по частоте Т1 будет записан исходный адрес.

Шесть младших разрядов приращения

адреса QiQe с РгПА 42 поступают на

вход ФРПА 44, который представлен на фиг.4.

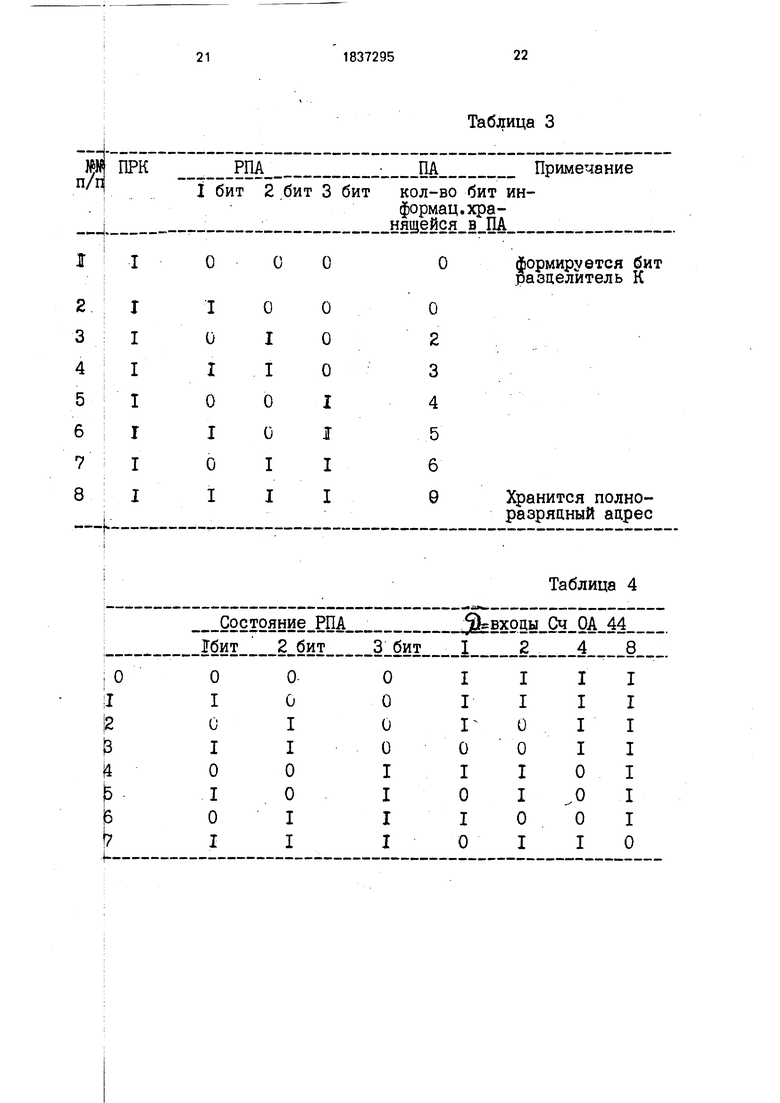

Код разрядности приращения адреса формируется в соответствии с табл,2.

Так, например, если приращение адреса имеет нули с 3 по 9 разряды и единицу во 2-м разряде, то на выходе МхбО формируется код 010, если приращение адреса имеет нули с 4 по 9 разряды и единицу в 3-м, то формируется код - 011 и так далее, в том случае, когда появляется единица в 7, 8, 9 разрядах или приращение адреса имеет отрицательный знак на вход управления МхбО

со схемы НЕ 45 поступает сигнал, который переводит выходы МхбО в состояние высокого импеданса и на выходе появляется код 1117.

Сформированный таким образом в

ФРПА 44 код разрядности приращения эд- рееа поступает на входы Д Рг РПА 46 и входы В схемы сравнения ССС48.

РгРПА 46 хранит предыдущее значение

0 кода разрядности,

В случае совпадения i с 1+1 кодов разрядности приращения адреса на выходе А В СС 48 появляется сигнал логической 1, который поступает на D-вход Тг ПРК 49,

5 запись в триггер производится в такте Т5 при поступлении сигнала с выхода RS-триггера 47 на С-вход Тг ПРК 49. Дальнейшее поступление сигнала записи в Тг ПРК 49 блокируется до окончания записи одной команды в ОЗУ

0 2. В такте Т5 происходит запись в Рг РПА 46 текущего кода разности приращения адреса, который находится в на D-входах.

Управление записью тестовой информации в ОЗУ 2 осуществляется с помощью

5 УУЗ 50, представленном на фиг.5.

На адресные входы ПЗУ ЧТ 62 поступают коды РПА (с Рг РПА48) и ПРК (с Тг ПРК 49) и выбирают информацию, которая однозначно определяет соответствие между ко0 дами ,РПА и ПРК, и числом циклов G 40, необходимых для записи в ОЗУ 2 адреса команды в сжатой форме. Выбранная информация поступает с выхода ПЗУ ЧТ 62 на информационные D-входы Сч РЗ 67 и запи5 сывается в него при поступлении на С-вход тактовый частоты Т8 через элементы 61 НЕ и 2И/НЕ 65. Тактовая частота Т9, поступая на R-вход RS Тг 63 переводит его из состояния логической 1 в состояние логическо0 го О. Информация с выхода RS Тг 63 поступает на вход элемента 2И-НЕ 65 и блокирует дальнейшее поступление частоты Т8 на С-вход Сч РЗ 67. По тактовой частоте Т9, поступающей через элемент 2И 64

5 на вход 1 Сч РЗ 67 начинается отсчет числа тактов записи одной команды в ОЗУ 2.

Данные для записи в ОЗУ 2 поступают параллельно на информационные входы МхД 72 в следующем порядке: информаци0 онный разряд команды, признак режима кодирования, разрядность приращения адреса, приращение адреса либо исходный адрес. Перебор этих данных осуществляется с помощью Сч ОА 68, выход которого

5 соединен с управляющими входами Мх Д 72. Увеличение состояния Сч ОА 68 происходит при поступлении тактовой частоты Т9 на .

В том случае, когда РПА 1-й кома нды совпадает с 1+1-й (о чем свидетельствует наличие сигнала логической 1 на выходе гПРК 49). то запись в ОЗУ 2 значения РПА не производится. Следовательно, после записи через Мх Д 72 в ОЗУ 2 информационного разряда команды и значения ПРК должно быть сразу записано ПА. Анализ состояний Сч ОА 68 и Тг ПРК 49 осуществляется элементами НЕ 69 и ЗИ-НЕ 70. Когда состояние Сч ОА 68 соответствует (1)ю, и ПРК - 1), элементом ЗИ-НЕ 70 вырабатывается сигнал логического О, который поступая на D-вход D-Tr 71 переводит его по тактовой частоте Т10 в нулевое состояние. 5ыход D-Tr 71 соединен с С-входом Сч ОА 68. Таким образом, на С-вход ОА 68 поступает сигнал разрешения записи информации, находящейся на его D-входах. Снятие Сигнала разрешения происходит по тактовой частоте Т1, которая поступает на S-вход )-Тг 71, Так как на D-входах Сч ОА 68 посто- j нно записано число 4 в двоичном коде, то по частоте Т9, поступающей на вход +1 Сч ОА 68, после записи ПРК в ОЗУ 2 начинает считываться первый разряд ПА.

Управление записью информации, поступающей в ОЗУ 2 с Мх Д 72, осуществляется следующим образом. По сигналу НУ в / сходное состояние устанавливаются Сч А 73, Сч Яч 74, RS-Tr 75, 76. По тактовой частоте Т1, которая поступает на счетный ЕХОД Сч А 73, начинается перебор адресов для записи информации в ОЗУ 2. которое состоит из 16 однотипных ячеек. Выбор ячеек происходит последовательно с помощью Сч Яч 74, RS-Tr 75 и Дш 77. По тактовым частотам Т2 и Т10, поступающим соответственно на R- и S-входы триггера 75, происходит формирование импульса стробирования, который поступает на W- вход Дш 77. На выходе Дш 77 формируется сигнал выборки одной из ячеек ОЗУ 2. По тактовым частотам Т1 и Т10, поступающим соответственно на S- и R-входы RS-Tr 76, Формируются импульсы записи информа- иии в ОЗУ 2. Так как на V-вход Мх 78 поступает внешний сигнал Разрешение записи соответствует логическому О, то прохождение импульсов записи в ОЗУ 2 разрешено. При считывании информации на ОЗУ 2 на V-входе Мх 78 сигнал лог.1 и в ОЗУ 2 поступает константа, соответствующая

ЮГ.1.

Конец записи одной команды происходит при переполнении Сч РЗ 67. Сигнал с выхода 0 Сч РЗ 67 блокирует поступление через элемент 2И 64 тактовой частоты Т9 на вход -1 Сч РЗ 67; переводит в единичное состояние RS-триггер 63; Тг Зн 41 и RS-триггер 47 переводятся в нулевое состоящие; происходит останов КТС-ГТИ 40.

Происходит опрос элемента И 21 в БУ 6 и в случае наличия на его входах команды Конец теста происходит выработка сигнала Стоп БПТ. Запуск G 40 для записи по- следующих команд тестового набора в сжатой форме происходит по сигналу сопро- вождения команды, поступающему из БПТ4.

Процедура формирования адреса при 0 считывании информации из ОЗУ 2 сводится к следующему (см. фиг.6).

Шаг А. Принятие внешнего сигнала Чтение тестовой информации (режим тестового диагностирования). 5 Шаг Б. Установка в исходное состояние всех элементов с памятью в многоканальном устройстве тестового контроля.

Шаг В. После принятия сигнала Пуск устройство начинает работу. 0Шаг Г. Считывание из ОЗУ 2 бита информации - являющегося информацией о состоянии канала ОК 11.

Шаг Д. Считывание из ОЗУ 2 второго бита информации - являющегося призна- 5 ком режима кодирования (ПРК).

Шаг Е. Анализ информации, полученной в шаг Д.

Так как это первый цикл формирования адреса, то ПРК1 является логическим 0. 0Если же это i-цикл формирования адреса, то формирование следующих шагов проводится по следующему правилу:

nPKj 1 - следующие биты информации являются битами приращения адреса, коли- 5 чество битов приращения адреса определяется показателем РПА|-1 (разрядность приращения адреса).

ПРК( 0 - следующие три бита информации являются показателем РПА, значе- 0 ние показателя РПА и ПА приведены в табл.З.

Шаг Ж. Считывание из ОЗУ 2 информации в соответствии со значением РПА,

Шаг 3. Формирование адреса обраще- 5 ния кОК 11 (Бу 6).

Шаг И. Формирование сигнала СС сигнала сопровождения для передачи адреса, сформированного в шаге 2.

Шаг К. Переход к шагу Г.

0Останов данной процедуры может произойти при выполнении одного из двух условий - поступления сигнала конец с теста или сигнала прерывание из БУ 6.

Опишем как осуществляется работа 5 БВИ 3 в соответствии с выше описанной процедурой.

. Шаг А. С БУ 6 сигнал логическая 1 поступает на входы элементов 98 2И-НЕ, 80 2И и НЕ 82, при этом сигналы запрета, поступающие на входы инкремент 1 Сч КЦ

81 и вход стробирования W 1 ДШ 83, снимаются.

Шаг Б. Цепи установки в исходное состояние БВИ 3 на фиг.6 показаны только для тех элементов, работа которых без этого не понятна, чтобы не загромождать рисунок.

Шаг В. При нажатии кнопки Пуск КТС- ГТИ G 40 начинает работу. КТС-ГТИ формирует импульсы временная диаграмма которых представлена на фиг.8. На этом рисунке представлен цикл обработки одного бита при считывании из ОЗУ 2. Цикл обработки состоит из десяти тактов. Как видно из фиг.8 такты сдвинуты на полпериода. С помощью RS-триггеров 75, 76 находящихся в БСИ 1, формируются сигналы управления циклом считывания из ОЗУ 2.

Шаг Г. Из ОЗУ 2 считывается бит информации, он поступает на D-входы ВРгПИ 85, представленном на фиг.7. На входе стробирования W 1 ДШ 83 логический 0. В такте Т8 сигнал от G 40 поступает на вход стробирования Л/2 и с нулевого выхода (так как по адресным входам ДШ 83 (0)2) ДШ 83 сигнал поступает на С-вхрд триггера (ТГИ) в ВРгПИ 85 и в него записывается информация, находящаяся в на D-входе.

Этим же сигналом устанавливается в нулевое состояние разряды ПА1...ПА9 в ВРгПИ 85.

От G 40 на яход 2И 80 в такте Т9 поступает сигнал логического 0 и с выхода 2И 80 на вход Инкремент 1 Сч КЦ 81 поступает сигнал и на выходе Сч КЦ 81 появляется значение (1)2.

Шаг Д. Из ОЗУ 2 считывается бит информации, он поступает наО-входы ВРгПИ 83, на входе стробирования W 1 ДШ 83 логический 0, а в такте Т8 сигнал с G 40 поступает на вход стробирования 2 и с первого выхода (так как на адресных входах ДШ 83 (1)а) поступает сигнал на С-вход триггера ПРК и в него записывается информация, находящаяся на D-входе.

На второй вход элемента 2ИЛИ 79 от G 40 в такте Т10 поступает сигнал. По этому сигналу производится запись в Сч КЦ 81 числа 5 в двоичном коде.

ШагЕ, Если в Тг ПРК ВРгПИ 83 записался логический 0, то дальнейшие действия как в шаге Д. Если же в Тг ПРК ВРгПИ 85 записалась логическая 1, то с прямого выхода Тг ПРК в ВРгПИ 85 на вход CD-триггера ПРК-А поступает перепад сигнала, по которому в Тг ПРК-А записывается логический О и на прямом выходе этого триггера появляется сигнал логический 0, который поступает на вход элемента 2ИЛИ 79.

В следующем цикле из ОЗУ 2 считывается бит информации, он поступает на Dвходы ВРгПИ 85, в такте Т8 сигнал КТС-ГТИ поступает на вход стробирования 2 и с пятого выхода ДШ 83 (так как на адресных входах ДШ 83 (5)2) поступает сигнал на Свход первого триггера ПА в ВРгПИ 85 и в него записывается информация, находящаяся на D-входе.

Сигнал с пятого выхода ДШ 83 в такте Т8 также поступает на вход предваритель0 ной записи ССч ОА95и в него записывается информация, поступающая от MX 93 на D- входы.

В зависимости от информации в триггерах РПА формируются следующие сигналы

5 управления MX 93.

1.РПА 111 - подключаются А входы MX 93 на выходах - соответствующая информация.

2.РПА 000 - выходы MX 93 переводят- 0 ся в состояние высокий импеданс.

3.РПА 100 - то же, что и в п.2.

4.При всех других состояниях РПА подключаются В-входы MX 93 и на выходах - соответствующая информация.

5 На А-входах MX 93 данных код (6)2, a на В-входы поступает информация с инверсных выходов триггеров РПА, т.е. на D-входы Сч ОА 95 поступает обратный код РПА, прямой код приведен в табл.3.

0Нэ входы элементов ЗИЛ И-НЕ 87. ЗИ 88

и СС 89 поступает информация с прямых выходов РПА из ВРгПИ 85 и с выходов этих элементов поступают сигналы управления MX 93. Элемент ЗИ 88 управляет V-входом

5 MX 93, выбирающим группу входов А или В, при V 0 выбираются А-входы, а при V 1 - В-входы.

Элемент ЗИЛИ-НЕ 87, СС 89 и 2ИЛИ 88 управляют W-входом MX 93, который пере0 водит выходы MX 93 в состояние высокого импеданса.

Следовательно, в Сч ОА 95 записывается информация в соответствии со следующей таблицей 4. Следует отметить, что на

5 В-вход старшего разряда зашита логическая 1.

В этом же цикле на входы элемента 2ИЛИ-НЕ 9 в тактах Т9 и Т10 поступают сигналы от G 40 и на выходе элемента

0 2ИЛИ-НЕ 97 формируется импульс, равный половине периода ГТИ, формирование этого импульса показано на графике фиг. 10.

С выхода элемента 2ИЛИ-НЕ 97 этот импульс поступает на вход элемента 2И 101,

5 на другом входе этого элемента - потенциал лог.1, следовательно, на выходе элемента 2И 101 появляется импульс той же формы, что и на графике фиг. 10. Он поступает на вход инкремент 1 Сч ОА 95 и содержимое Сч ОА 95 увеличивается на единицу.

Шаг Ж. Обработка остальных битов приращения адреса (вплоть до последнего) не личается от шага Г, единственное, что не- Абходимо отметить запись информации в Тг ПА осуществляется поступлением сигна- /а с .соответствующего выхода ДШ 83 в кте Т8, а выход определяется двоичной юмбинацией, поступающей с выходов Сч f Ц 81 на входы ДШ 83, Увеличение на 1 двоичного веса Сч КЦ 81 осуществляется в 9, Увеличение на 1 двоичного веса Сч ОА 5 происходит так, как описано в следующем шаге.

Шаг 3. Рассмотрим обработку последнего бита приращения адреса. Из ОЗУ 2

итывается бит информации, он поступает на D-входы ВРгПИ 85, в такте Т8 сигнал с G О поступает на вход стробирования W 2 Ш 83 и с 1-выхода (так как на адресных одах ДШ 83 (i)2) ДШ 83 сигнал поступает на С-вход 1-го триггера ПА и в него записы- в зется информация, находящаяся на D-вхоВ тактах Т9 и Т10 сигнал поступает (так- е как в шаге Е) на вход инкремент 1 Сч А 95 (двоичный вес счетчика равен (14)г) и юичный вес счетчика становится равным (15)2. На выходе прямой перенос Сч ОА 95 Ш)является сигнал лог,0. Этот сигнал пост упает на входы элементов 21/1 101, 2И-НЕ 8i

б

ил вход Инкремент 1 Сч ОА 95, до поступлю ния импульса на вход предварительной установки С Сч ОА 95 и пятого выхода ДШ 8с в такте Т8.

Элемент 2И-НЕ 86 выходом соединен с входом начальной установки R Сч КЦ 81 и, следовательно, устанавливается Сч КЦ 81 в нулевое состояние (0)2.

Элемент2И-НЕ 98 выходом соединен с входом записи регистра ВРг 99 и перепад уровня сигнала из лог.О в лог.1 производит за тись информации, находящейся на D-вхо- дах ВРг99. Информация на D-входэх ВРг 99 формируется суммированием в СМ 94 информации, записанной в Рг 91 и Тг ПА в ВргПИ85.

Как формируется информация в ТгПА бы

2ИЛИ 96 и 2И-НЕ 98. Элемент 2И 101 окирует поступление импульсов от G 40

ло описано выше.

В регистр РгА 91 информация поступает

на D-входы с выходов ВРг 99, а запись ее

производится в такте Т1 при поступлении

си нала от G 40,

Первый адрес всегда формируется сум-

миЬованием информации, поступающей с

1А ТЗРПИ 85 с (0)2, так как ВРг 99 и РгА установлены в нулевое состояние в шаге Три РПА 111 с выхода элемента ЗИ 88 нал поступает на вход R РгА 91 и устанав0

5

0

5 0

5

0

5

0

5

ливает его в нулевое состояние, так как в ТгПА в ВРгПИ 85 формируется абсолютный адрес.

Шаг И. Сигнал лог.О с выхода прямой перенос Сч ОА 95 поступив на вход элемента 2ИЛИ 96 разрешает формирование сигнала СИ. В следующем цикле после обработки последнего бита ПА в такте Т2 сигнал поступает от G 40 на второй вход элемента 2ИЛИ 96 и на его выходе появляется уровень лог.О, который поступает на R вход ТгСИ 100 и он его перебрасывает в нулевое состояние, т.е. на его выходе появляется перепад из лог.1 в лог.О, возвращается ТгСИ 100 в исходное состояние при поступлении сигнала с пятого выхода ДШ 83 в такте Т8.

Шаг К. Переход к шагу Г.

Следует отметить, что при РПА 100 в ОЗУ 2 этот разряд в ТгПА не хранится, т.к. он всегда равен 1, поэтому как только СС 89 обнаруживает, что код, поступивший от РПА в ВРгПИ 85 на его входы А совпал с кодом, зашитым на его входах В (100), на выходе появляется сигнал лог.1, который поступает на вход элемента 2ИЛИ 98 (как было описано выше) и на вход элемента НЕ 84, выход этого элемента соединен с входом установки в единичное состояние ТгПА 1 в ВРгПИ 85 и переводит прямой выход ТгПА 1 в состояние лог, 1.

Еще одна особенность, которая не была описана выше, это формирование признака К (контроль или начало следующего слова). Как только элемент ЗИЛИ-НЕ 87 обнаруживает, что, код, поступивший от РПА в ВРгПИ 85 на его входы, равен (000) на выходе появляется сигнал лог.1, который поступает на D-вход Тг 92, а запись лог.1 происходит при появлении сигнала с инверсного выхода ТгПРК ВРгПИ 85 на вход С Тг 92. На его выходе появляется лог.1, которая поступает на соответствующий D-вход ВРг 99.

В заключении приведем форматы, хранящиеся в ОЗУ 2,

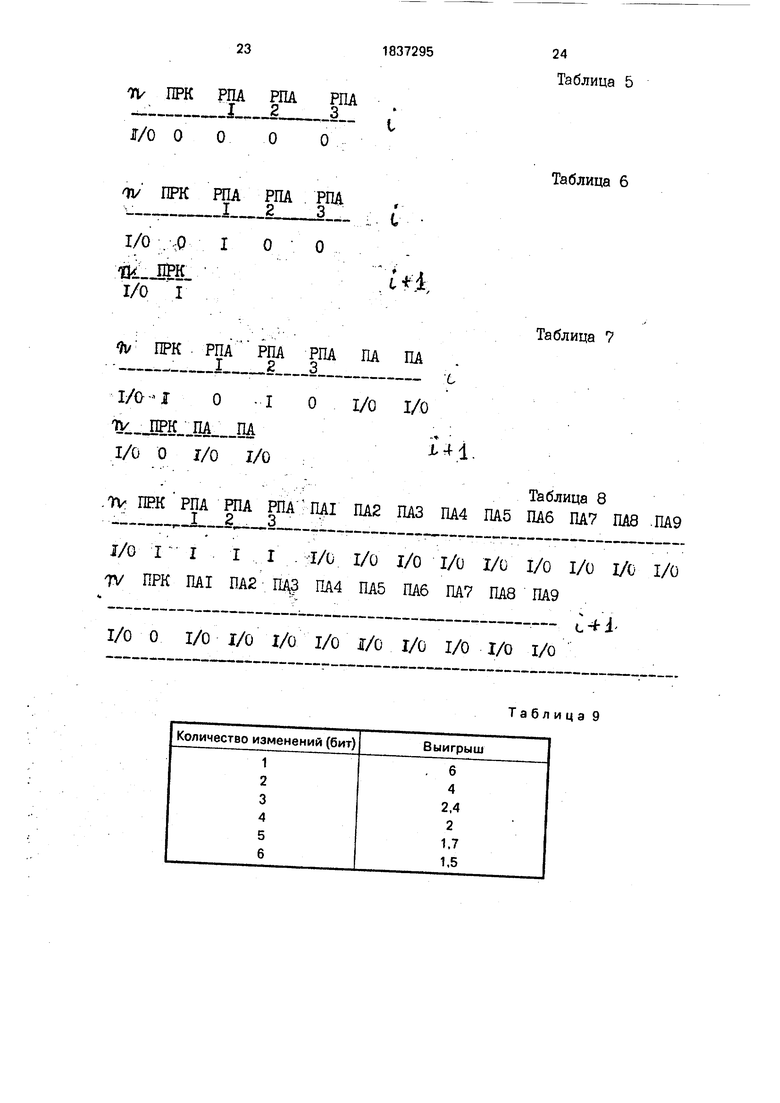

В таблице 5 приведен формат для формирования признака К в таблице 6 - формат с ПА 1, в таблице 7 - формат ПА 2 и в таблице 8 - формат ПА 9.

Объем тестовой информации в предлагаемом методе определяется как

V3-M + 2, () Кбит).

J 1

где а - разрядность указателя режима кодирования, в предлагаемом устройстве равен 1;

разрядность указателя величины ПА, в предлагаемом устройстве равен либо О, либо

А- РПА, в предлагаемом устройстве из- меняется от О до

М - суммарное количество переключений входов и выходов сигналов, направление передачи информации иммасок.

Таким образом, предложенная на фиг.1 блок-схема позволяет уменьшить объем памяти, необходимый для хранения тестовых программ, за счет кодирования исходной информации. Максимальный выигрыш в уменьшении объема памяти при использовании предлагаемого устройства по отношению к объему памяти в устройстве (2) достигается при упорядочении изменения тестовой информации: например, при проверке логических модулей, содержащих 256 контролируемых каналов, зависимость получаемого выигрыша от количества изменений в разрядах последующего тестового набора по отношению к предыдущему показана в табл.9.

Формула изобретения 1. Многоканальное устройство тестового контроля логических узлов, содержащее блок управления, дешифратор адреса, блок памяти тестов, блок памяти диагностики, n-блоков контроля, причем первая группа логических входов блока управления соединена с первой.группой выходов п блоков контроля, первая группа входов которых является первой группой входов устройства, группа выходов устройства для подключения к контролируемому логическому узлу является второй группой выходов п-блоков контроля, группа адреса входов которого соединена с группой выходов дешифратора адреса, группа адресных входов которого, объединенная с группой адресных входов блока памяти диагностики и второй группой входов n-блоков контроля, является первой группой выходов блока управления, первый выход которого соединен с управляющим входом n-блоков контроля, первый вход логического условия блока управления является первым выходом блока памяти диагностики, первый информационный вход которого является управляющим входом устройства для подключения через логический пробник к внутренней точке контролируемого логического узла, входы начальной загрузки устройства соединены с входами начальной загрузки блока памяти диагностики и блока управления, вторая группа выходов блока управления которого соединена с группой управляющих входов блока памяти тестов, группа выходов которого соединена с группой входов загрузки блока управления, второй выход блока управления соединен с элементом индикации, а третий выход блока управления является вторым информационным входом блока памяти диагностики, отличающееся тем, что, с целью увеличения производительности устройства, за счет увеличения частоты подачи входных воздействий на объект контроля, сокращения объема памяти, необходимой

0 для хранения программ тестового контроля, введены блок сжатия информации, оперативное запоминающее устройство (ОЗУ), блок восстановления информации, группа выходов которого соединена с вторым вхо5 дом логического условия блока управления, третья группа выходов блока управления которого соединена с первой группой входов блока восстановления информации, первый вход которого соединен с выходом ОЗУ,

0 группа управляющих входов которого соединена с первой группой выходов блока сжатия информации, вторая группа выходов которого соединена с второй группой логических входов блока управления, четвертая

5 группа выходов блока управления которого соединена с группой входов блока сжатия информации, вход которого соединен с вторым выходом блока памяти тестов, третья группа выходов блока сжатия информации

0 соединена с второй группой входов блока восстановления информации.

2, Устройство поп.1,отличающее- с я тем, что блок сжатия информации содержит два элемента И, приемный регистр, сум5 матор-вычитатель, регистры приращения адреса и регистр разрядности приращения адреса, схему сравнения, устройство управления записью, формирователь разрядности приращения адреса, два триггера,

0 D-триггер знака и D-триггер признака режима кодирования, элемент ИЛИ-НЕ, элемент НЕ, генератор тактовых импульсов, причем группа информационных входов приемного регистра, объединенная с пер5 выми входами сумматора-вычитателя и первой группой входов устройства управления записью, является группой входов блока, вход начальной установки которого объединен с первым входом первого эле0 мента И, входами сбросов регистра приращения адреса и регистра разрядности приращения адреса, вторым входом сброса второго триггера и входом сброса D-тригге- ра признака режима кодирования и вторым

5 входом устройства управления записью и является первым входом установки первого триггера, второй вход установки которого объединен с входом синхронизации приемного регистра, первым входом второго элемента И, первым входом сброса второго

триггера и первым выходом устройства управления записью и является выходом второй группы выходов блока, третья группа выходов которого объединена с третьей группой входов устройства управления записью и является первой группой выходов генератора тактовых импульсов, второй выход которого объединен с входом установки второго триггера и входом синхронизации регистра приращения адреса, группа выходов которого объединена с первыми входами схемы сравнения и является четвертой группой входов устройства управления записью, пятый вход которого объединен с первым входом сброса первого триггера и является входом блока сжатия информации, вход первого разряда группы входов которого является третьим входом установки первого триггера, выход которого является входом пуска генератора тактовых импульсов, третий выход которого является С-входом D-триггера знака, вход сброса которого соединен с выходом второго элемента И, второй вход которого объединен с выходом элемента ИЛИ-НЕ, входом элемента НЕ, вторым входом первого элемента И, выход которого соединен с входом сброса приемного регистра, группа выходов которого соединена с вторыми входами сумматора-вычитателя, группа выходов которого, объединенная с соответствующим разрядом с D-входом D-триггера знака и группой входов элемента ИЛИ-НЕ, соединена с информационными входами регистра приращения адреса, группа выходов которого, объединенная с шестой группой входов устройства управления записью, является первой группой входов формирователя разрядности приращения адреса, группа выходов которого, объединенная с информационными входами регистра разрядности приращения адреса, является вторыми входами схемы сравнения, выход которой является D-входом D-триггера признака режима кодирования, С-вход которого соединен с выходом второго триггера, второй вход сброса первого триггера является входом второго разряда группы входов блока, первая группа выходов которого является выходом устройства управления записью, выход элемента НЕ является вторым входом формирователя разрядности приращения адреса, четвертый выход генератора тактовых импульсов соединен с синхровходом регистра приращения адреса, выход D-триггера признака режима кодирования является седьмым входом устройства управления записью, выход триггера знака соединен с входом элемента ИЛИ-НЕ.

3. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок восстановления информации содержит счетчик конца цикла, дешифратор, три элемента ИЛИ, три элемента И, два элемента НЕ, выходной регистр преобразования информации, два элемента ИЛИ-НЕ, схему сравнения, два элемента И-НЕ, регистр адреса, D-триггер, мультиплексор, сумматор, счетчик обработки адре0 са, выходной регистр, триггер, первый вход первого элемента И, объединенный с входом первого элемента НЕ и первым входом первого элемента И-НЕ, является первым разрядом первой группы входов, второй

5 вход первого элемента И-НЕ, объединенный с вторым входом второго элемента И- НЕ, первым входом второго элемента И, первым входом третьего элемента ИЛИ, соединен с выходом счетчика обработки адре0 са, синхровход которого, объединенный с входом установки триггера синхроимпульсов, является первым выходом дешифратора, вторая группа выходов которого соединена с входами синхронизации и

5 сброса выходного регистра преобразования информации, первый выход которого является первым входом первого элемента ИЛИ, выход которого соединен с синхровходом счетчика конца цикла, суммирующий вход

0 которого является выходом первого элемента И, второй вход которого является девятым разрядом второй группы входов блока, первый вход которого соединен с информационным входом выходного реги5 стра преобразования информации, вход установки соединен с выходом второго элемента НЕ, вход которого соединен с первым входом второго элемента ИЛИ и соединен с выходом схемы сравнения, пер0 вая группа входов которой, объединенная с входами третьего элемента И, входами элемента ИЛИ-НЕ, соединена с второй группой выходов выходного регистра преобразования информации, выходы третьей группы

5 которого соединены с синхровходом D- триггера, D-вход которого, объединенный с выходом первого элемента ИЛИ-НЕ, соединен с вторым входом второго элемента ИЛИ, выход которого является управляю0 щим входом мультиплексора, информационный вход которого является четвертым выходом выходного регистра преобразования информации, пятый выход которого является первым входом сумматора, второй

5 вход которого является выходом регистра адреса, вход сброса которого соединен с выходом элемента И и является управляющим входом мультиплексора, выход которого соединен с информационным входом счетчика обработки адреса, суммирующий

вход которого соединен с выходом второговходом дешифратора, выход первого эле- элемента И, второй вход которого соединенмента И-НЕ соединен с синхровходом вы- с выходом второго элемента ИЛИ-НЕ, пер-ходного регистра, группа выходов которого, вый и второй входы которого являются соот-объединенная с группой информационных ветственно девятым и десятым разрядами5 входов регистра адреса, является выходом второй группы входов блока и соединеныблока, первый разряд второй группы вхо- с вторым входом первого элемента ИЛИ, которого также соединен с синхровхо- восьмой разряд второй группы входов - сдом регистра адреса, выход D-триггера первым управляющим входом дешиф-соединен с первым информационным вхо- ратора соответственно, информацией-10 дом выходного регистра, второй D-вход ко- ные входы которого соединены сторого соединен с выходом сумматора, разрядными выходами счетчика конца цик-второй разряд второй группы входов блока ла, вход сброса которого является выходомсоединен с вторым входом третьего элемен- второго элемента И-НЕ, первый вход кото-та ИЛИ, выход которого является входом рого является и вторым разрядом первой15 сброса триггера, выход которого и группа группы входов блока, выход первого эле-выходов блока соединены с выходом выход- мента НЕ является вторым управляющимного регистра.

Таблица I

Таблица 3

23

1837295

24

Таблица 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

TV ПРК РПА РПА РПА

:Л -Ј-2-

1/00 О О О

П/ ПРК РПА РПА . РПА I23 „

I/O .,0 I

tfeL JS&- 1/0 I

о

V ПРК РПА РПА РПА ПА ПА --.--I-- 3 г

.

I/0-J О -I O.I/0 I/O

I/O О I/O I/O

Таблица 8 TV ПРК РПА РПА РПА ПАГ ПА2 ПАЗ ПА4 ПА5 ПАб ПА7 ПА8 -ПА9

:......„

I/O I I I I . I/O I/O I/O I/O I/O I/O I/O I/O I/O

7V ПРК ПА1 ПА2 ПДЗ ПА4 ПАб ПАб ПА7 ПА8 ПА9 .

....„...-

I/O 0 I/O I/O I/O I/O J/0 I/O I/O I/O I/O

Таблица б

с

ct i.

Таблица 7

.

Таблица 9

| |I

IS

.

t

I

I

fe

I

r

2

4j

.

I

«

%

ч

If

b

лн -и/л

I

SsJ

I

3

I

f

4J

I

fc t

1

-а. Ч

«-Hi

I

ПЛ MM)

T/fffomta}

flfljt №4)

rsfo4 &

rafori f/i/fotL

РПЛ ()

Фиг. 4.

КонцЗл (SS, if, 37, if, 17) ЛЈ ttS)

Адрес я /еохц

tH)

bbt&fOW

(6 г)

Jri/Vm fЈfj

ю

05

см гCD

со

(ff/пэ

(Wetr

(УЗ)™

frtyou

ПО

Фиг. 6

Фиг.

Донные о коммутации

- J tO /nfcmo&istt

#0(fy

/ анн#ё о jMffvfHtsi/ 1

&nuty fffvpfQXyvis j

rfawtve ff trocxox .

- - -

HOjbf

Данн&в о хопггу- I mayvu

4вннь/е о зноченм опнпу0о8 и/оевкунй

Данные о пасхах , .в „

- - - - - - тесто&/У

Htxfyo

команда лоузо

команда х

хононоо S-f-f конец mecrvo

Донные о коммутации

П

- J

&& /0fcnx &/f WOAOSWW Япро/у.

Фиг, 9

| 4851257/24 12.07.90 30.08.93 | |||

| Бюл | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР Me 1568046, кл.СОбР 11/00, 1989. | |||

Авторы

Даты

1993-08-30—Публикация

1990-07-12—Подача