Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностирования цифровых узлов, имеющих выходы с тремя состояниями.

Известен сигнатурный анализатор [1], содержащий два блока свертывания, блок распределения данных, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вход данных, две группы выходов номера искаженного участка, синхровход, вход смены участка последовательности, входы "Старт" и "Стоп". Он позволяет определить номер искаженного участка входной информационной последовательности при его единственности.

Недостатками данного анализатора являются невозможность определения наличия ошибки до окончания периода формирования сигнатуры, невозможность определения местоположения нескольких искаженных участков, а также характера происшедших искажений - четнократная ошибка, ошибка связанная с переходами в третье состояние.

Наиболее близким к предлагаемому по технической сущности является сигнатурный анализатор [2] , содержащий формирователь временных сигналов, два формирователя сигнатур, два компаратора, элемент НЕ и два элемента И, причем выход пуска формирователя временных сигналов является управляющим входом "Старт-стоп" анализатора, входы первого и второго компараторов объединены и подключены к информационному входу анализатора, выход первого компаратора соединен с входом элемента НЕ и первым входом первого элемента И, выход второго компаратора соединен с вторым входом первого элемента И и первым входом второго элемента И, выход элемента НЕ соединен с вторым входом второго элемента И, а выходы формирователей сигнатуры являются выходами сигнатурного анализатора. Анализатор содержит также второй элемент НЕ, третий элемент И и элемент ИЛИ, причем информационный вход первого формирователя сигнатур подключен к информационному входу анализатора, выход второго компаратора соединен с входом второго элемента НЕ и информационным входом второго формирователя сигнатур, выход второго элемента НЕ соединен с первым входом третьего элемента И, второй вход которого соединен с выходом первого элемента НЕ, третьи и четвертые входы с первого по третий элементов И объединены между собой и подключены соответственно к синхровходу анализатора и выходу формирователя временных сигналов, выходы первого и третьего элементов И соединены с выходами элемента ИЛИ, синхровходы первого и второго формирователей сигнатур подключены соответственно к выходам элемента ИЛИ и второго элемента И. Известный сигнатурный анализатор обеспечивает формирование сигнатур в отдельности по уровням "0" и "1" и по уровню Z (третье состояние).

Однако данный анализатор не позволяет определить местоположение и характер возникающих искажений (четнократные и нечетнократные), а также сам факт возникновения искажений до окончания периода формирования структур.

Целью изобретения является расширение функциональных возможностей анализатора за счет определения номера искаженного участка в кодовой последовательности, а также характера искажений: четнократные или нечетнократные ошибки, ошибки при переходе в Z-состояние, а также определения факта возникновения искажений непосредственно в процессе формирования сигнатуры.

Для достижения цели в анализатор, содержащий формирователь временных сигналов, два компаратора, два формирователя сигнатур, два элемента НЕ, три элемента И, элемент ИЛИ, причем вход пуска формирователя временных сигналов является управляющим входом "Старт-стоп" анализатора, входы первого и второго компараторов объединены и подключены к информационному входу анализатора, выход первого компаратора соединен с входом первого элемента НЕ и первым входом первого элемента И, выход второго компаратора соединен с вторым входом первого элемента И и первым входом второго элемента И, выход первого элемента НЕ соединен с вторым входом второго элемента И, информационный вход первого формирователя сигнатур подключен к информационному входу анализатора, выход второго компаратора соединен с входом второго элемента НЕ и информационным входом второго формирователя сигнатур, выход второго элемента НЕ соединен с первым входом третьего элемента И, второй вход которого соединен с выходом первого элемента НЕ, третьи и четвертые входы с первого по третий элементов И объединены между собой и подключены к синхровходу анализатора и выходу формирователя временных сигналов, выходы первого и третьего элементов И соединены с входами элемента ИЛИ, синхровходы первого и второго формирователей сигнатур подключены соответственно к выходам элемента ИЛИ и второго элемента И, вход начальной установки анализатора подключен к соответствующим входам первого и второго формирователей сигнатур, введены сдвиговый регистр, два блока контроля четности, блок управления, три блока памяти, блок обнаружения третьего состояния, первый и второй триггеры, элемент ИЛИ-НЕ, при этом входы начальной установки формирователя временных сигналов, сдвигового регистра, блока управления, блока обнаружения третьего состояния, первого и второго триггеров объединены и соединены с входом начальной установки анализатора, информационный вход сдвигового регистра соединен с информационным входом анализатора, выходы сдвигового регистра и первого формирователя сигнатур соединены соответственно с группами входов первого и второго блоков контроля четности, синхровходы сдвигового регистра и блока управления соединены с выходом элемента ИЛИ, управляющий вход блока управления является входом анализатора "Чтение-запись", группы адресных и управляющих выходов блока управления соединены по шине адреса и шине сигналов управления с соответствующими группами входов первого, второго и третьего блоков памяти, информационные выходы которых соединены соответственно с единичными входами первого и второго блоков контроля четности и информационным входом блока обнаружения третьего состояния, вход контроля которого соединен с выходом второго элемента И, синхровходы блока обнаружения третьего состояния, первого и второго триггеров объединены и соединены с синхровыходом блока управления, информационные входы первого и второго триггеров соединены соответственно с выходами первого и второго блоков контроля четности, выходы первого и второго триггеров и информационный выход блока обнаружения третьего состояния соединены соответственно с информационными входами первого, второго и третьего блоков памяти и входами элемента ИЛИ-НЕ, выход которого соединен с первым управляющим входом формирователя временных сигналов, второй управляющий вход которого соединен с вторым входом "Чтение-запись" анализатора.

Блок управления содержит два счетчика, дешифратор и формирователь импульса, причем объединенные входы начальной установки первого и второго счетчиков формирователя импульса образуют вход начальной установки блока управления, подключенный к входу начальной установки анализатора, синхровход первого счетчика является синхровходом блока управления, который подключен к выходу элемента ИЛИ, выходы первого счетчика соединены с входами дешифратора, вход выбора режима которого является управляющим входом блока управления, и подключен к входу управления "Чтение-запись" анализатора, первый и второй выходы дешифратора являются управляющими выходами блока, третий выход дешифратора соединен с синхровходом второго счетчика, выходы которого являются группой адресных выходов блока, вход запуска формирователя импульса соединен с выходом окончания счета первого счетчика, выход формирователя импульса, являющийся синхровходом блока управления, подключен к синхровходам обоих триггеров и блока обнаружения третьего состояния.

Блок обнаружения третьего состояния содержит два триггера, схему сравнения, элемент И и формирователь импульса, причем синхровход первого триггера является входом контроля блока обнаружения третьего состояния и подключен к выходу элемента И, выход первого триггера соединен с первым входом схемы сравнения, второй вход которой является информационным входом блока и соединен с выходом третьего блока памяти, выход схемы сравнения соединен с информационным входом второго триггера, выход которого является информационным выходом анализатора, вход начальной установки первого триггера соединен с выходом элемента И, первый вход которого объединен с входами начальной установки второго триггера и формирователя импульса, является входом начальной установки блока и подключен к входу начальной установки анализатора, второй вход элемента И соединен с выходом формирователя импульса, синхровход которого объединен с синхровходом второго триггера и является синхровходом блока и подключен к синхровходу блока управления.

Суть изобретения заключается в следующем. Входной информационный поток разбивают на отрезки длиной 16 битов, которые фиксируют в сдвиговом регистре. Любая нечетнократная ошибка, возникающая за 16 тактов синхронизации, изменяет четность отрезка информационной последовательности и первый блок контроля четности вырабатывает сигнал ошибки. Таким образом, все нечетнократные ошибки обнаруживаются непосредственно в процессе формирования сигнатур. Контроль четности содержимого первого формирователя сигнатур позволяет обнаружить половину четнократных искажений входной последовательности. Так как формирователь сигнатур - линейное устройство, то для него справедлив принцип суперпозиции истинной входной последовательности и последовательности ошибок. Таким образом сигнатура искаженной последовательности есть сумма по модулю два сигнатур истинной последовательности и последовательности ошибок. Текущая сигнатура изменяет четность, если к сигнатуре истинной последовательности прибавлена сигнатура последовательности ошибок, которая является нечетной.

Рассмотрим данную ситуацию.

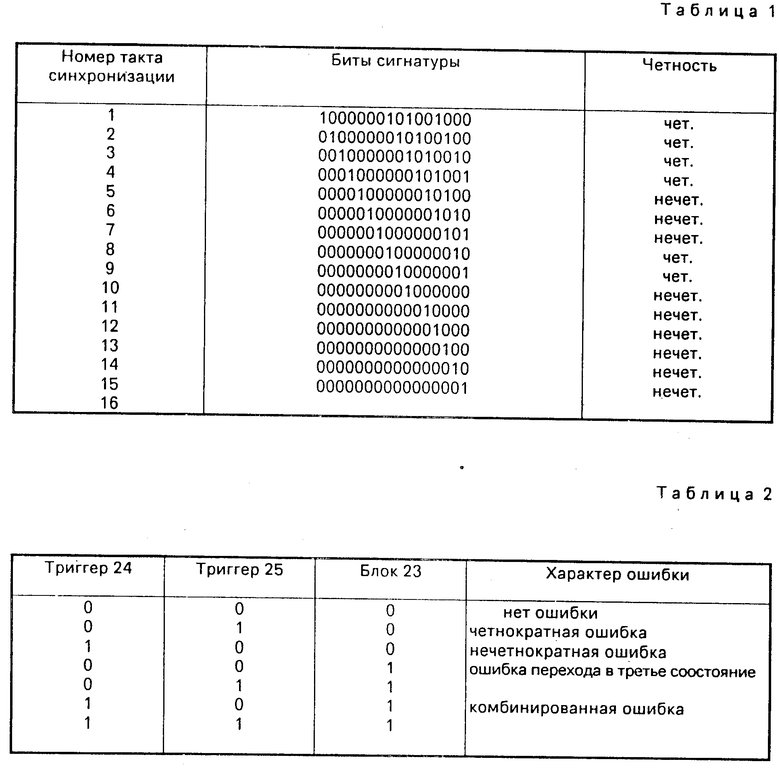

В табл. 1 приведены сигнатуры единичной ошибки, возникающей в одном из 16 тактов синхронизации.

Так как контроль четности осуществляется каждые 16 тактов синхронизации, то ряд кратных ошибок такой: 2, 4, 6, 8, 10, 12, 14, 16. Вероятность того, что сигнатура последовательности ошибок нечетная, вычисляется по формуле

Р(К) = М(К)/N(K), где К - число из ряда кратных ошибок;

М - количество комбинаций, приводящих к нечетногй сигнатуре;

N - общее количество комбинаций ошибок К-го порядка.

Рассчитывают вероятность для последовательности, состоящей из двух ошибок:

N(2)=  =

=  =

=  = 120,, где C

= 120,, где C - количество сочетаний из n по m;

- количество сочетаний из n по m;

М(2) = 6 . 10 = 60, так как количество четных сигнатур последовательности, состоящей из одной ошибки, равно шести, а нечетных равно десяти. Сигнатура последовательности, состоящей из двух ошибок, нечетная, если сгруппировать одиночные ошибки так, чтобы одна из последовательностей давала четную сигнатуру, а другая - нечетную. Остальные комбинации ведут к четной сигнатуре.

Таким образом P(2) =  ≠

≠  = 0,5..

= 0,5..

Вероятности для других последовательностей ошибок можно вычислить аналогично:

Р(14) = Р(2) = 0,5;

Р(12) = Р(4) = 0,5055;

Р(10) = Р(6) = 0,496;

Р(8) = 0,5035.

Следовательно , если за 16 тактов происходит 2, 4, 6, 8, 10, 12, 14 ошибок, то в половине случаев это обнаруживается вторым блоком контроля четности.

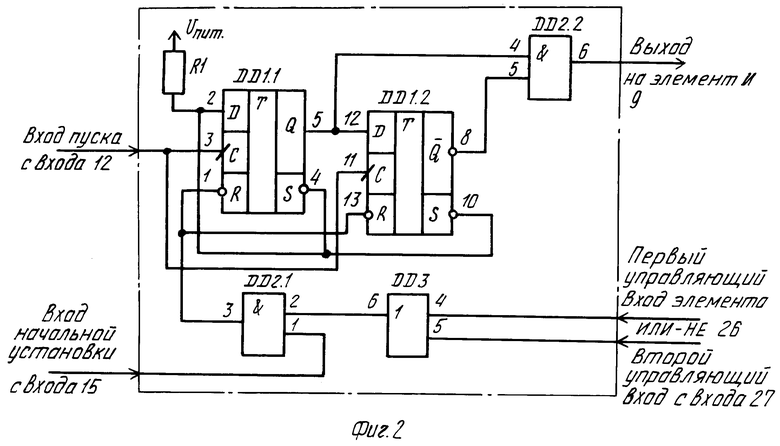

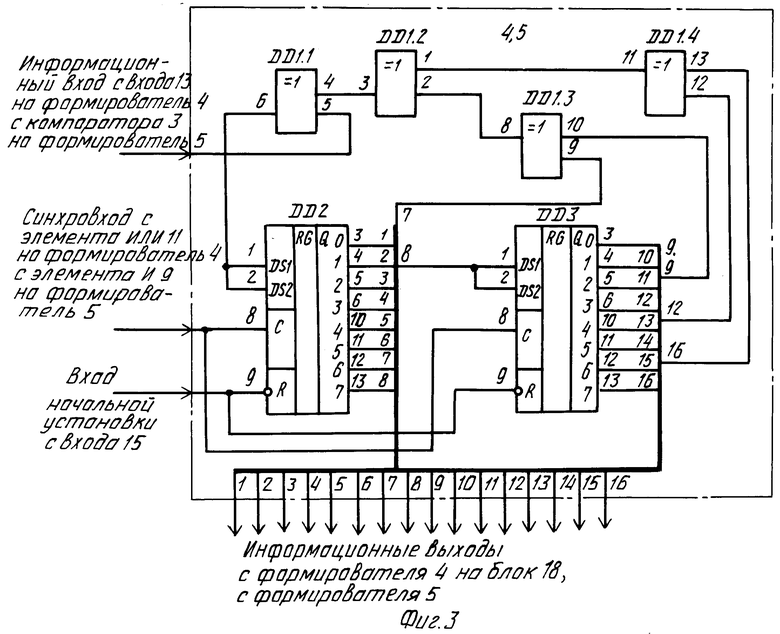

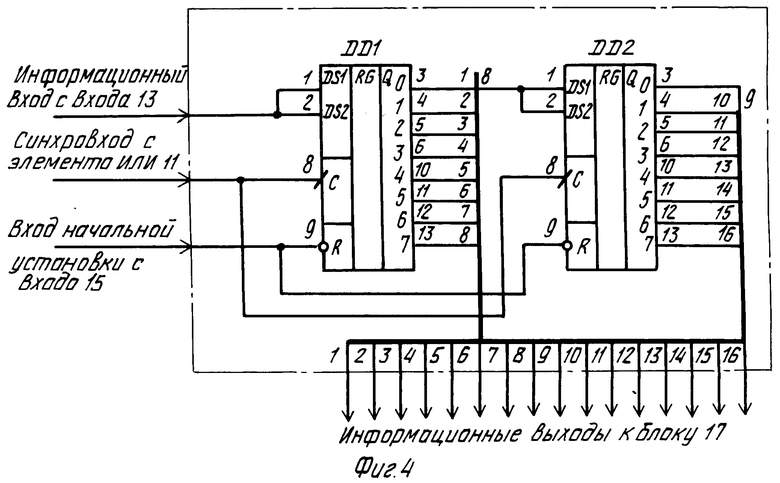

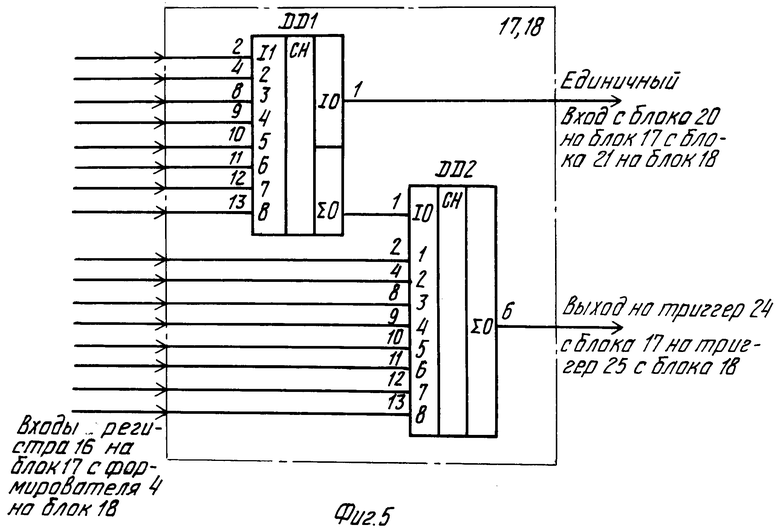

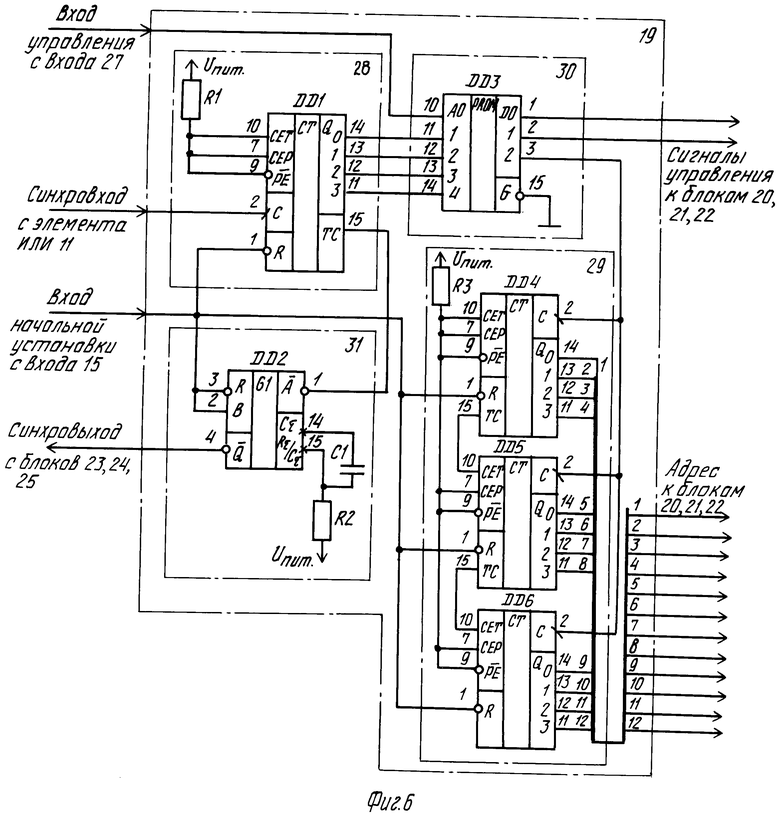

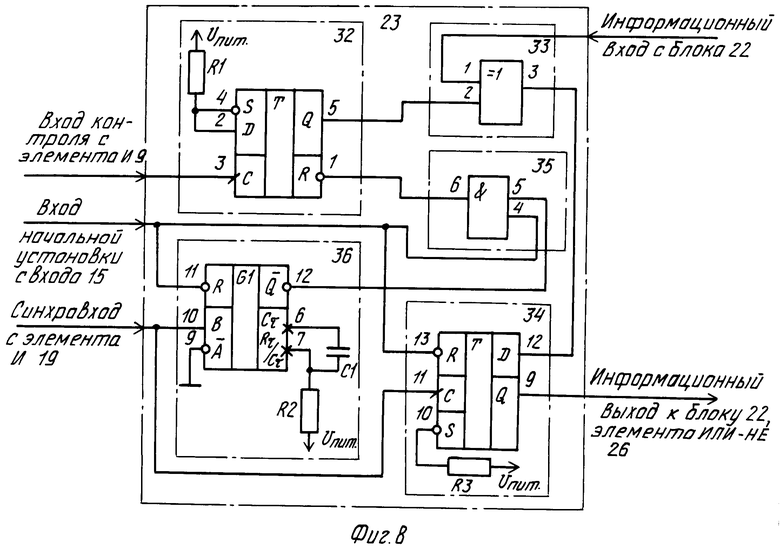

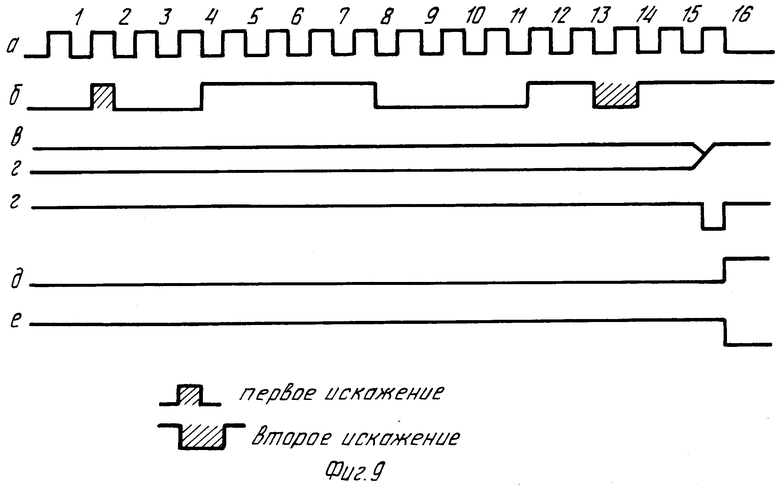

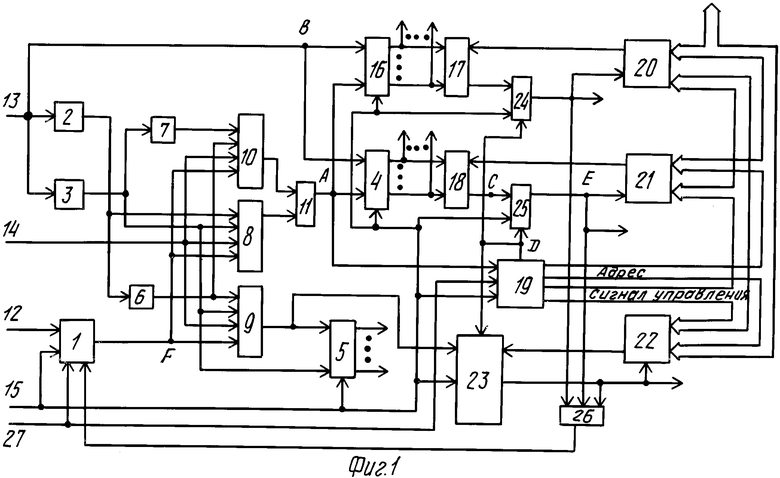

На фиг. 1 приведена функциональная схема анализатора; на фиг. 2 - схема формирователя временных сигналов; на фиг. 3 - схема формирователя сигнатур; на фиг. 4 - схема сдвигового регистра; на фиг. 5 - схема блока контроля четности; на фиг. 6 - схема блока управления; на фиг. 7 - схема блока памяти; на фиг. 8 - схема блока обнаружения третьего состояния; на фиг. 9 - временные диаграммы, иллюстрирующие обнаружение четнократной ошибки.

Сигнатурный анализатор (фиг. 1) содержит формирователь 1 временных сигналов, первый 2 и второй 3 компараторы, формирователи 4, 5 сигнатур, элементы НЕ 6, 7, элементы И 8, 9, 10, элемент ИЛИ 11, вход 12 "Старт-стоп", информационный вход 13, вход 14 синхронизации, вход 15 начальной установки, сдвиговый регистр 16, блоки 17, 18 контроля четности, блок 19 управления, блоки 20, 21, 22 памяти, блок 23 обнаружения третьего состояния, первый 24 и второй 25 триггеры, элемент ИЛИ-НЕ 26, вход 27 "Чтение-запись".

Входы первого 2 и второго 3 компараторов объединены и подключены к информационному входу 14 анализатора, вход пуска формирователя 1 временных сигналов является управляющим входом 12 "Старт-стоп". Выход первого компаратора 2 соединен с входом первого элемента НЕ 6 и первым входом первого элемента И 8, выход второго компаратора 3 соединен с вторым входом первого элемента И 8 и первым входом второго элемента И 9. Выход первого элемента НЕ 6 соединен с вторым входом второго элемента И 9, информационный вход первого формирователя 4 сигнатур подключен к информационному входу 13 анализатора. Выход второго компаратора 3 соединен с входом второго элемента НЕ 7 и информационным входом второго формирователя 5 сигнатур, выход второго элемента НЕ 7 соединен с первым входом третьего элемента И 10, второй вход которого соединен с выходом первого элемента НЕ 6. Третьи и четвертые входы с первого по третий элементов И 8, 9, 10 объединены между собой и подключены к синхровходу 14 анализатора и выходу формирователя 1 временных сигналов соответственно. Выходы первого 8 и третьего 10 элементов И соединены с входами элемента ИЛИ 11, синхровходы первого 4 и второго 5 формирователей сигнатур подключены соответственно к выходам элемента ИЛИ 11 и второго элемента И 9. Входы начальной установки формирователя 1 временных сигналов, формирователей 4, 5 сигнатур, сдвигового регистра 16, блока 19 управления, блока 23 обнаружения третьего состояния, первого 24 и второго 25 триггеров объединены и соединены с входом 15 начальной установки анализатора. Информационный вход сдвигового регистра 16 соединен с информационым входом 13 анализатора, выходы сдвигового регистра 16 и первого формирователя 4 сигнатур соединены соответственно с группами входов первого 17 и второго 18 блоков контроля четности, а синхровходы сдвигового регистра 16 и блока 19 управления соединены с выходом элемента ИЛИ 11. Управляющий вход блока 19 управления является входом 27 анализатора "Чтение-запись", группы адресных и управляющих выходов блока 19 управления соединены по шине адреса и шине сигналов управления с соответствующими группами входов первого 20, второго 21, третьего 22 блоков памяти, информационные входы которых соединены соответственно с единичными входами первого 17 и второго 18 блоков контроля четности и информационным входом блока 23 обнаружения третьего состояния, вход контроля которого соединен с выходом второго элемента И 9. Синхровходы блока 23, первого 24 и второго 25 триггеров объединены и соединены с синхровходом блока 19 управления. Информационные входы первого 24 и второго 25 триггеров соединены соответственно с выходами первого 17 и второго 18 блоков контроля четности, выходы триггеров 24, 25 и информационный выход блока 23 обнаружения третьего состояния соединены соответственно с информационными входами первого 20, второго 21 и третьего 22 блоков памяти и входами элемента ИЛИ-НЕ 26, выход которого соединен с первым управляющим входом формирователя 1 временных сигналов, второй управляющий вход которого соединен с входом 27 "Чтение-запись" анализатора.

Блок 19 управления (фиг. 6) содержит два счетчика 28, 29, дешифратор 30 и формирователь 31 импульса. Входы начальной установки первого 28 и второго 29 счетчиков и формирователя 31 импульсов объединены, являются входом начальной установки блока 19, который подключен к входу 15 начальной установки анализатора. Синхровход первого счетчика 28 является синхровходом блока 19 управления, который подключен к выходу элемента ИЛИ 11. Выходы первого счетчика 28 соединены с входами дешифратора 30, вход выбора режима которого является управляющим входом блока 19 и подключен к входу 27 "Чтение-запись" анализатора. Выход дешифратора 30 образует шину сигналов управления анализатора, синхровход дешифратора 30 соединен с синхровходом второго счетчика 29, выходы которого образуют шину адреса анализатора. Вход запуска формирователя 31 импульса соединен с выходом окончания счета счетчика 28. Выход формирователя 31 импульса является синхровыходом блока 19, подключен к синхровходам триггеров 24, 25 и блока 23.

Блок 23 обнаружения третьего состояния (фиг. 8) содержит триггеры 32, 34, схему 33 сравнения, элемент И 35 и формирователь 36 импульса. Синхровход первого триггера 32 является входом контроля блока и подключен к выходу второго элемента И 9, выход триггера 32 соединен с первым входом схемы 33 сравнения, второй вход которой является информационным входом блока и соединен с выходом блока 22 памяти. Выход схемы 33 сравнения соединен с информационным входом второго триггера 34, выход которого подключен к единичному входу блока 22 и является информационным входом анализатора. Вход начальной установки триггера 32 соединен с выходом элемента И 35, первый вход которого объединен с входами начальной установки второго триггера 34 и формирователя 36 импульса, является входом начальной установки блока 23 и подлкючен к входу 15 начальной установки анализатора. Второй вход элемента И 35 соединен с выходом формирователя 36 импульса, синхровход которого объединен с синхровходом второго триггера 34, является синхровходом блока и подключен к синхровыходу блока 19 управления.

Формирователь 1 временных сигналов (фиг. 2) предназначен для управления циклом формирования сигнатур и выполнен на микросхемах DD1 - КР531МТ2, DD2 - КР531ЛИ1, DD3 - КР531ЛЛ1.

Компаратор 2 предназначен для квантования входного сигнала по двум уровням: логическая "1" и третье состояние и выполнен на микросхеме КР521СА4 (Цифровые и аналоговые интегральные микросхемы. Справочник./Под ред. С.В. Якубовского. - М.: Радио и связь, 1989 (1)). Компаратор 3 предназначен для квантования входного сигнала по двум уровням: логический "0" и третье состояние и выполнен на микросхеме КР521СА4.

Формирователи 4 и 5 сигнатур (фиг. 3) предназначены для сжатия входной последовательности в сигнатуру и выполнены на микросхемах DD1-КР531ЛП5, DD2, DD3 - К555ИР8. (Уильямс Г.Б. Отладка микропроцессорных систем. Пер. с англ. М.: Энергоатомиздат, 1988, с.180).

Элементы НЕ 6 и 7 предназначены для инверсии сигналов, поступающих от компараторов 1 и 2, и представляют собой инверсные выходы компараторов КР521СА4. Элементы И 8, 9, 10 предназначены для разделения сигнала синхронизации по трем направлениям в зависимости от логического состояния входной информации и выполнены на микросхемах К555ЛИ6 (1). Элемент ИЛИ 11 предназначен для объединения синхросигналов, поступающих с выходов элементов И 8 и 10, и выполнен на микросхеме КР531ЛЛ1 (1).

Сдвиговый регистр 16 (фиг. 4) предназначен для накопления шестнадцати битов входной последовательности и выполнен на микросхемах DD1, DD2 - К555ИР8 (1),

Блоки 17 и 18 контроля четности (фиг. 5) предназначены для определения четности входной информации и выполнены на микросхемах DD1, DD2 - КР531ИП5 (Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987 (2)).

Блок 19 управления (фиг. 6) предназначен для формирования циклов чтения и записи для блоков 20, 21, 22 памяти и выдачи строб-импульса для фиксации выходных сигналов с блоков 17, 18 контроля четности и схемы 33 сравнения в блоке 23. Он содержит два счетчика 28, 29, дешифратор 30 и формирователь 31 имульса. Первый счетчик 28 блока 19 предназначен для стробирования импульса формирователя 31 и выдачи воздействий на дешифратор 30 и выполнен на микросхеме DD1 - К555ИЕ10. Второй счетчик 29 блока 19 предназначен для формирования адреса блоков 20, 21, 22 памяти и выполнен на микросхемах DD4, DD5, DD6 - К555ИЕ10 (2). Дешифратор 30 блока 19 управления предназначен для формирования управляющих сигналов блоков 20, 21, 22 памяти и тактирования второго счетчика 29 и выполнен на микросхеме DD3 - К155РЕ3 (Лебедев О.Н. Микросхемы памяти и их применения. - М.: Радио и связь, 1990 (3)). Формирователь 31 импульса блока 19 предназначен для выдачи строба на блок 23 и триггеры 24, 25 анализатора и выполнен на микросхеме DD2 - К555АГ4 (1).

Блоки 20, 21 памяти (фиг. 7) предназначены для хранения информации о четности контролируемой последовательности. Блок 22 памяти предназначен для хранения информации о переходах в третье состояние. В данном случае они выполнены на микросхемах DD1 - КР537РУ3А (3).

Блок 23 обнаружения третьего состояния (фиг. 8) предназначен для фиксации перехода сигналов входной последовательности в Z-состояние. Он содержит триггеры 32, 34, схему 33 сравнения, элемент И 35 и формирователь 36 импульса. Первый триггер 32 блока 23 служит для запоминания факта возникновения третьего состояния и выполнен на микросхеме DD1.1 - КР531ТМ2 (1). Схема 33 сравнения блока 23 предназначена для выдачи сигнала ошибки при несовпадении информации, поступающей от первого триггера 32 блока 23 и третьего блока 22 памяти. Она выполнена на микросхеме DD4 - КР531ЛП5 (1). Второй триггер 34 блока 23 предназначен для фиксации сигнала ошибки на выходе схемы 33 сравнения по строб-сигналу от блока 19 управления и выполнен на микросхеме DD1.2 - КР531ТМ2 (1). Элемент И 35 блока 23 предназначен для объединения сигналов с входа начальной установки анализатора и выхода формирователя импульса блока 23 и выполнен на микросхеме DD2 - КР531ЛИ1 (1). Формирователь 36 импульса блока 23 предназначен для выработки сигнала начальной установки для первого триггера 32 и выполнен на микросхеме DD3 - К555АГ4 (1).

Первый 24 и второй 25 триггеры анализатора предназначены для фиксации синалов ошибки на выходе первого 17 и второго 18 блоков контроля четности соответственно и выполнены на микросхеме КР531ТМ2 (1). Элемент ИЛИ-НЕ 26 предназначен для объединения сигналов ошибки с выходов первого 24, второго 25 триггеров и второго триггера блока 23 и выполнен на микросхеме КР531ЛЕ7 (1).

Анализатор работает следующим образом.

Перед началом рабочего цикла на вход 15 начальной установки подается сигнал, приводящий анализатор в исходное состояние. Под действием этого сигнала на выходе формирователя 1 временных сигналов устанавливается уровень логического "0", блокирующий прохождение сигналов через элементы И 8, 9, 10, устанавливаются в нулевое состояние формирователи 4, 5 сигнатур, сдвиговый регистр 16, счетчики 28 и 29 блока 19 управления. Формирователь 31 импульса блока 19 управления устанавливается в единичное состояние. Устанавливаются в нулевое состояние триггеры 32 и 34 блока 23 обнаружения третьего состояния, а формирователь 36 импульса этого блока устанавливается в единичное состояние. Устанавливаются в нулевое состояние первый 24 и второй 25 триггеры.

На вход 27 "Чтение-запись" подается логический "0", означающий установку режима "чтение". Этот сигнал разрешает формирователю 1 временных сигналов реагировать на состояние его первого входа управления, а также переключает дешифратор 30 блока 19 управления на формирование цикла "чтение" для блоков 20, 21, 22 памяти. При подаче на управляющий вход 12 сигнала "Старт" формирователь 1 временных сигналов разрешает прохождение сигналов синхронизации с входа 14 через элементы И 8, 9, 10, которые в совокупности с компараторами 2 и 3, элементами НЕ 6, 7 и ИЛИ 11 разделяют информационный поток, поступающий на информационный вход 13 анализатора, на две составляющие.

Первая составляющая, образованная сигналами с уровнями логических "0" и "1", сворачивается в сигнатуру в формирователе 4 по синхросигналу с выхода элемента ИЛИ 11. Вторая составляющая, образованная сигналами с уровнем Z (третье состояние), сворачивается в сигнатуру в формирователе 5 по синхросигналу с выхода второго элемента И 9. Синхронно с формирователем 4 сигнатур происходит занесение входной информации в сдвиговый регистр 16. В данном случае разрядность сдвигового регистра выбрана равной 16. Текущая информация в первом формирователе 4 сигнатур и сдвиговом регистре 16 подвергается контролю по четности соответственно в блоках 18 и 17, на единичные входы которых поступает бит четности из блоков 21 и 20 памяти. Если количество единиц в содержимом блоков 4 и 16 в совокупности с битом, поступающим из блоков 21 и 20 памяти, является нечетным, то блоки 18 и 17 вырабатывают сигналы ошибки, поступающие соответственно на информационные входы второго 25 и первого 24 триггеров. Фиксация ошибки в триггерах 25 и 24 происходит по строб-импульсу с синхровыхода блока 19 управления.

Рассмотрим обнаружение четнократной ошибки, т.е. ситуацию когда за 16 тактов синхронизации происходит два искажения входной информационной последовательности (фиг. 9). Данный тип ошибки обнаруживается цепочкой, состоящей из блоков 4, 18, 21 и 25 (фиг. 1). Первый счетчик 28 блока 19 управления (фиг. 6) отсчитывает 16 синхроимпульсов, поступающих с выхода элемента ИЛИ 11 (фиг. 19а) и запускает формирователь 31 импульса блока 19 управления, который вырабатывает строб-импульс (фиг. 19г) на синхровходе блока 19. В течение 16 тактов синхронизации первый формирователь 4 сигнатур обрабатывает входную информацию, содержащую два искажения (фиг. 19б). В 16-м такте синхронизации второй блок 18 контроя четности формирует на своем выходе сигнал ошибки (фиг. 19в), который фиксируется во втором триггере 25 по фронту строб-импульса с синхровыхода блока 19 (фиг. 19г).

На выходе второго триггера 25 устанавливается состояние логической "1" (фиг. 19д), приводящее к установке на выходе элемента ИЛИ-НЕ 26 сигнала остановки анализатора. Этот сигнал воздействует на первый управляющий вход формирователя 1 временных сигналов, что приводит к возникновению на его выходе логического "0" (фиг. 19е), который запрещает прохождение синхросигналов от входа 14 анализатора через элементы И 8, 9, 10. Процесс формирования сигнатур прерывается. Цепочка, состоящая из блоков 16, 17, 20 и 24, работает аналогично при обнаружении нечетного числа искажений входной информационной последовательности.

Параллельно с контролем четности блок 23 обнаружения третьего состояния фиксирует наличие переходов в состояние в течение 16 тактов синхросигнала с выхода элемента ИЛИ 11. Первый триггер 32 блока 23 (фиг. 8) фиксирует синхроимпульс, поступающий с выхода элемента И 9 на вход контроля блока 23. Третий блок 22 памяти выдает на информационный вход блока 23 бит, указывающий на наличие или отсутствие переходов в состояние входной информации в текущих 16 тактах синхросигнала на выходе элемента ИЛИ 11, который сравнивается схемой 33 блока 23 с выходной информацией триггера 32. При наличии сигнала ошибки на выходе схемы 33 сравнения блока 23 он защелкивается во втором триггере 34 блока 23 строб-импульсом с синхровыхода блока 19 управления. Одновременно запускается формирователь 36 импульса блока 23, который вырабатывает сигнал, приводящий первый триггер 32 блока 23 через элемент И 35 блока 23 в исходное состояние. Сигнал ошибки с информационного выхода блока 23 через элемент ИЛИ-НЕ 26 воздействует на первый управляющий вход формирователя 1 временных сигналов, что приводит к остановке анализатора. Если блоки 17, 18 контроля четности и блок 23 обнаружения третьего состояния не выявляют наличия ошибки, процесс формирования сигнатур в блоках 4 и 5 продолжается до подачи на вход 12 анализатора сигнала "Стоп".

Дешифратор 30 блока 19 управления формирует управляющие сигналы, необходимые для работы блоков 20, 21, 22 памяти в режиме "чтение", а также выдает синхросигнал для наращивания содержимого второго счетчика 29 блока 19, который формирует адрес для блоков 20, 21, 22 памяти. Разрядность счетчика 29 определяется исходя из длины выходной информационной последовательности. В данном случае при длине последовательности 64 кбит разрядность счетчика равна 12.

При остановке анализатора по сигналу "Стоп" с выходов формирователей 4 и 5 сигнатур снимаются сигнатуры входной последовательности для сравнения с исходной. При остановке анализатора по сигналу ошибки с выхода элемента ИЛИ-НЕ 26 на выходах второго счетчика 29 блока 19 управления фиксируется номер искаженного отрезка входной последовательности, а на выходах сдвигового регистра 16 - сам искаженный отрезок. Состояние выходов триггеров 24 и 25 и информационного выхода блока 23 позволяет определить характер произошедшей ошибки (см. табл. 2).

Для снятия исходных сигнатур, информации о четности и переходах в Z-состояние на управляющий вход 27 анализатора подается сигнал логической "1", устанавливающий для блока 19 управления режим "запись" и запрещающий для формирователя 1 прерывание синхронизации по входу 14 при поступлении сигнала ошибки с выхода элемента ИЛИ-НЕ 26. Данные с информационных выходов триггеров 24, 25 и блока 23 заносятся в блоки 20, 21, 22 памяти под управлением блока 19. Работа остальных блоков анализатора аналогична работе в режимах обнаружения четнократных ошибок и ошибок по третьему состоянию.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки нечеткой информации | 1990 |

|

SU1758642A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1991 |

|

RU2077415C1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Устройство для формирования циклического синхроимпульса | 1989 |

|

SU1725404A1 |

| Устройство для испытаний гидравлических агрегатов | 1990 |

|

SU1798551A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

Изобретение относится к вычислительной технике и позволяет расширить функциональные возможности анализатора за счет определения номера искаженного участка входной последовательности и характера искажений: четнократные, нечетнократные, ошибки перехода в третье состояние, а также определения факта возникновения искажений непосредственно в процессе формирования сигнатуры. Анализатор содержит формирователь 1 временных сигналов, два компаратора 2, 3, два формирователя 4, 5, два элемента НЕ 6, 7, три элемента И 8, 9, 10, элемент ИЛИ 11. В него введены сдвиговый регистр 16, два блока 17, 18 контроля четности, блок 19 управления, три блока 20, 21, 22 памяти, блок 23 обнаружения третьего состояния, два триггера 24, 25, элемент ИЛИ - НЕ 26. 2 з. п.ф-лы, 2 табл., 9 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сигнатурный анализатор | 1986 |

|

SU1377861A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-07-30—Публикация

1991-04-22—Подача