Изобретение относится в цифровой вычислительной технике и предназначено для использования в системах обработки нечеткой информации, в информационно-советующих системах оперативного управления, а также системах функционального диагностирования.

Известно устройство для выполнения операций над нечеткими операндами (А, С, № 1451677, G 06 F 7/00) содержащее три операционных регистра, регистр адреса, конвейерный регистр микрокоманд, первый и второй дешифраторы, первый и второй шинные формирователи, АЛУ, ПЗУ микрокоманд, группу элементов И, первый и второй коммутатор, элемент И, причем информационные входы первого, второго и

третьего регистров, первые входы группы элементов И подключены к информационным входам устройства и к выходам первого и второго шинного формирователей, первый вход первого регистра соединен с первым информационным входом второго коммутатора, второй выход первого регистра соединен со вторым информационным входом второго коммутатора, первый выход второго регистра соединен с третьим информационным входом второго коммутатора, второй выход второго регистра соединен с четвертым информационным входом второго коммутатора, первый выход третьего регистра соединен с пятым информационным входом второго коммутатора, второй выход третьего регистра соединен с шестым

VJ

сл

00

о

Јь

to

информационным входом второго коммутатора, два выхода которого соединены с информационными входами АЛУ и информационными входами первого коммутатора, управляющий вход второго коммутатора соединен с выходом пятого регистра, первый вход которого соединен с выходом ПЗУ, вход которого соединен с выходом четвертого регистра, первый вход которого соединен со вторым входом пятого регистра и с выходом схемы И первый вход которого соединен со вторым входом четвертого регистра и управляющим входом устройства, выход пятого регистра также соединен с управляющими входами первого, второго, третьего регистров, со вторыми входами группы элементов И, со вторым входом элемента И, с первым входом второго дешифратора и со входом первого дешифратора, первый выход которого соединен с управляющим входом АЛУ, второй выход которого соединен со вторым входом второго дешифратора, первый выход которого соединен с управляющим входом первого коммутатора, а второй выход второго дешифратора соединен с управляющим входом второго шинного формирователя, вход которого соединен с выходом первого коммутатора, выходы группы элементов И соединены с информационным выходом устройства.

Недостатком устройства является жесткий алгоритм выбора адреса следующей микрокоманды, невысокое быстродействие, вследствие одноуровневой конвейерной обработки, частое обращение к внешней памяти за элементами функции принадлежности.

Наиболее близким к предлагаемому по технической сущности является устройство для обработки нечеткой информации (а.с. N; 1545214 СС6Г 7/00), содержащее два арифметико-логических блока, две группы элементов И, блок памяти команд, блок памяти эталонных термов, регистр адреса, регистр признаков, регистр микрокоманд, сдвиговый регистр, коммутатор, шинный формирователь, элемент И и блок операционных регистров. Группа выходов шинного формирователя соединена с первыми входами элементов И первой группы, группа выходов которых подключена к выходу устройства. Выход регистра адреса подключен к входу блока памяти микрокоманд, выход которого подключен к информационному входу регистра микрокоманд, первая группа выходов которого соединена с группой управляющих входов коммутатора, вторая группа выходов регистра микрокоманд соединена с группой управляющих выходов

блока операционных регистроп. Первый выход регистра микрокоманд соединен с первым входом элемента И, второй выход регистра микрокоманд подключен к вторым

входам элементов И первой группы. Информационный вход устройства соединен через шину с первым двунаправленным выходом блока операционных регистров, первым информационным входом первого арифмети0 ко-логического блока, первыми входами элемента И первой группы,а второй двунаправленный выход блока операционных регистров соединен с выходом блока памяти эталонных термов и вторым информацион5 пым входом первого арифметико-логического блока, выход которого подключен к информационному входу сдвигового регистра, выход которого соединен с информационным входом шинного формирователя,

0 Выходы признаков и нулевой разряд информационного входа первого арифметико-логического блока соединены с информационным входом регистра признаков, k-й разряд выхода которого подключен

5 к к-му информационному входу коммутатора, (к 1. М, где М - количество признаков), выход которою соединен с первыми входами элементов И второй группы, и вторым входом элемента И, выход которого соеди0 нен с управляющим входом второго арифметико-логического блока, выходы элементов И второй группы соединены со старшими разрядами первого информационного входа второго арифметико-логиче5 ского блока, причем нулевой разряд первого информационного входа второго арифметико-логического блока соединен с третьим выходом регистра микрокоманд, выход второго арифметико-логического блока соеди0 нен с информационным входом регистра адреса, выход которого соединен с вторым информационным входом второго арифметико-логического блока и входом начальной загрузки адреса устройства. Третья группа

5 выходов регистра микрокоманд соединена с группой адресных входов блока памяти эталонных термов, а четвертый выход регистра микрокоманд соединен с управляющим входом блока памяти эталонных

0 термов, четвертая группа выходов регистра микрокоманд соединена с группой управляющих входов первого арифметико-логического блока, пятая группа выходов регистра микрокоманд соединена со вторыми входа5 ми элементов И второй группы, пятый выход регистра микрокоманд соединен с управляющим входом регистра адреса, шестая группа выходов регистра микрокоманд соединена с группойуправляющих входов сдвигового регистра, а шестой выход регистра микрокоманд

соединен с управляющим входом шинно- го формирователя.

Известное устройство предназначено для выполнения операций над нечеткими переменными, что позволяет управлять по- ведением простого объекта в реальном масштабе времени.

Однако управление поведением сложного обьекта требует обработки гораздо большего обьема нечеткой информации, и поэтому применение устройства-прототипа для управления таким объектом в реальном масштабе времени невозможно, ввиду его ограниченного быстродействия.

Математически поведение сложного объекта можно представить в виде нечеткого гиперграфа Н (X, И, Р), где Xi i I, i {1...m}- множество вершин, , j I, j {1 ...n}- множество ребер, Р -двуместный нечеткий предикат, называемый инциден- тором, который определяется для всех пар (х, и). Для графического представления нечетких ситуаций удобно использовать нечеткие графы. Однозначными представлениями нечеткого гиперграфа являются вершинный Х(Н) и реберный И(Н) нечеткие графы. Подробнее о свойствах нечетких графов можно прочитать в кн. Меликоз А.Н., Берштейн Л.С. Гиперграфы в автоматизации проектирования дискретных устройств, Ростов, РГУ, 1981 г. и в статье Мелихов А.Н., Берштейн Л.С., Канаев М.М. Операции над рас- плывистыми гиперграфзми и возможность их моделирования - в кн. Методы автоматизации проектирования, программирова- ния и моделированил, Таганрог, ТРТИ, 1981, вып. 1.С.129-133.

Вершины нечеткого графа Н представляют собой нечеткие ситуации управляемого объекта. Задача управления заключается в том, чтобы сравнить типовую ситуацию с массивом эталонных ситуаций, определить наиболее близкую эталонную ситуацию к типовой и в соответствии с решающей таблицей принять необходимое решение.

Нечеткая ситуация описывается как

(у.)(уд (Tj)/CTj }.JeUfel

где Tj - терм-множестоо, описывающее один из признаков yi характеризующих ситуацию.

Для его описания используются нечеткие переменные /, DI, С/, где С/ { Uy (d)/(d}, где в свою очередь //,.функции принадлежности.

Для сравнения ситуаций используются операции нечеткого включения

vCS Sj1) v(/us-(Y),(S)

где

vC«s-(Y)s-(Y))

Amax(1 -P -( ()) или нечеткого равенства

/(SSj)«&v(SjSi)Јv(SiS,)

yfy

Указанные операции прототипом выполняются, однако, учитывая большую размерность вершинного графа Х(Н) и большое количество признаков, описывающих каждую ситуацию, для описания всех эталонных ситуаций данного объекта одного ПЗУ эталонных термов оказывается недостаточно. Например, одна микросхема ПЗУ 556 РТ7 или 573 РФ2 (описанная в прототипе), способна содержать описание эталонной ситуации, описываемой 16-ю признаками, каждый из которых представлен терммно- жеством из 128 значений. Такое количество значений необходимо для более четкого различения нечетких квантификаторов много, очень много, средне и т.д. Если же все эталонные ситуации хранить во внешней оперативной памяти, то только для передачи массива из 500 эталонных ситуаций из ОЗУ в устройство, учитывая быстродействие ЭВМ ДНК-2. например, потребуется порядка 3 с. Учитывая затраты времени на запись типовых ситуаций и обработку в устройстве управления объектом в реальном масштабе времени становится невозможным. Поэтому весь массив эталонных ситуаций необходимо хранить в устройстве, что потребовало бы в нашем примере 500 микросхем памяти и селектор адреса микросхем ПЗУ.

Поставленная цель достигается тем, что в устройство, содержащее два арифметико- логических устройства, два блока элементов И, элемент И, сдвиговый регистр, блок памяти микрокоманд, регистр признаков, регистр адреса, коммутатор признаков, блок регистров, блок памяти точек перегиба термов вместо шинного формирователя дополнительно введены два арифметико- логических устройства, триггер, счетчик, блок памяти тангенсов, 3 регистра, мультиплексор, элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вход устройства соединен с одной группой выходов блока регистров, первой группой входов первого арифметико-логического устройства, первой группой входов блока элементов И, выходами мультиплексора, и группой входов первого регистра.

Другая группа двунаправленных выходов блока регистров соединена с выходами второго регистра, второй группой входов третьего арифметико-логического устройства и второй группой входов первого арифметико-логического устройства. Одна группа выходов первого арифметико-логического устройства соединена с группой входов сдвигового регистра, выходы которого соединены с первой группой входов четвертого арифметического устройства и первой группой входов мультиплексора. Входы второй группы входов первого блока элементов И соединены с посьмым выходом регистра микрокоманд, а выходы первого блока элементов I/I являются выходами устройства. Другая группа выходов первого АЛУ, выход переноса первой группы входов первого АЛУ соединены с группой информационных входов регистра признаков, выход которого соединен со входом второго блока элементов И и одним входом первого элемента И, другой выход которого соединен с шестым выходом регистра микрокоманд. Выходы второго блока элементов И соединены с первой группой входов второго АЛУ. Выходы второго АЛУ соединены с группой входов регистра адреса, выходы которого соединены с входами блока памяти микрокоманд и второй группой входов второго АЛУ. Причем входы блока памяти микрокоманд соединены со входом начальной загрузки адреса. Управляющий вход регистра адреса соединен с седьмым выходом регистра микрокоманд, управляющий вход второго АЛУ соединен с выходом первого элемента И. Вторые входы второй группы элементов И соединены с выходом регистра микрокоманд. Группа выходов блока памяти микрокоманд соединена с группой входов регистра микрокоманд. Выход третьего АЛУ соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с тринадцатым выходом регистра микрокоманд, а выход с первым входом второго элемента И. Второй вход второго элемента И соединен с четырнадцатым выходом регистра микрокоманд, а выход со входом мультиплексора. Выходы мультиплексора соединены с группой входов третьего регистра, выходы которого со- единены со второй группой входов четвертого АЛУ и второй группой входов мультиплексора, управляющий вход которого соединен с пятнадцатым выходом регистра микрокоманд. Выход первого регистра соединен с входами блока памяти точек перегиба термов.

Выходы блока памяти точек перегиба соединены с группой входов счетчика и входами блока памяти тангенсов. Выходы блока памяти тангенсов соединены с первой группой входов третьего арифметико- логического устройства. Выход счетчика соединен со входом установки триггера, прямой выход которого соединен с первым управляющим входом третьего арифметико-логического устройства, а инверсный выход, в свою очередь, соединен со вторым управляющим входом третьего арифметико-логического устройства. Выходы третьего арифметико-логического устройства соединены с входом второго регистра. Второй выход регистра микрокоманд соединен с группой управляющих входов блока регистров. Четвертый выход регистра микрокоманд соединен с группой управляющих

входов коммутатора. Первый выход регистра микрокоманд соединен с группой управляющих входов сдвигового регистра. Девятый выход регистра микрокоманд соединен с управляющим входом первого регистра. Третий выход соединен с группой управляющих входов первого арифметико- логического устройства. Десятый выход регистра микрокоманд соединен с группой управляющих входов счетчика. Шестнадцатый выход регистра микрокоманд соединен с управляющим входом третьего регистра. Одиннадцатый выход регистра микрокоманд соединен со входами сброса триггера и второго регистра. Девятнадцатый выход регистра микрокоманд соединен с группой управляющих входов второго регистра.

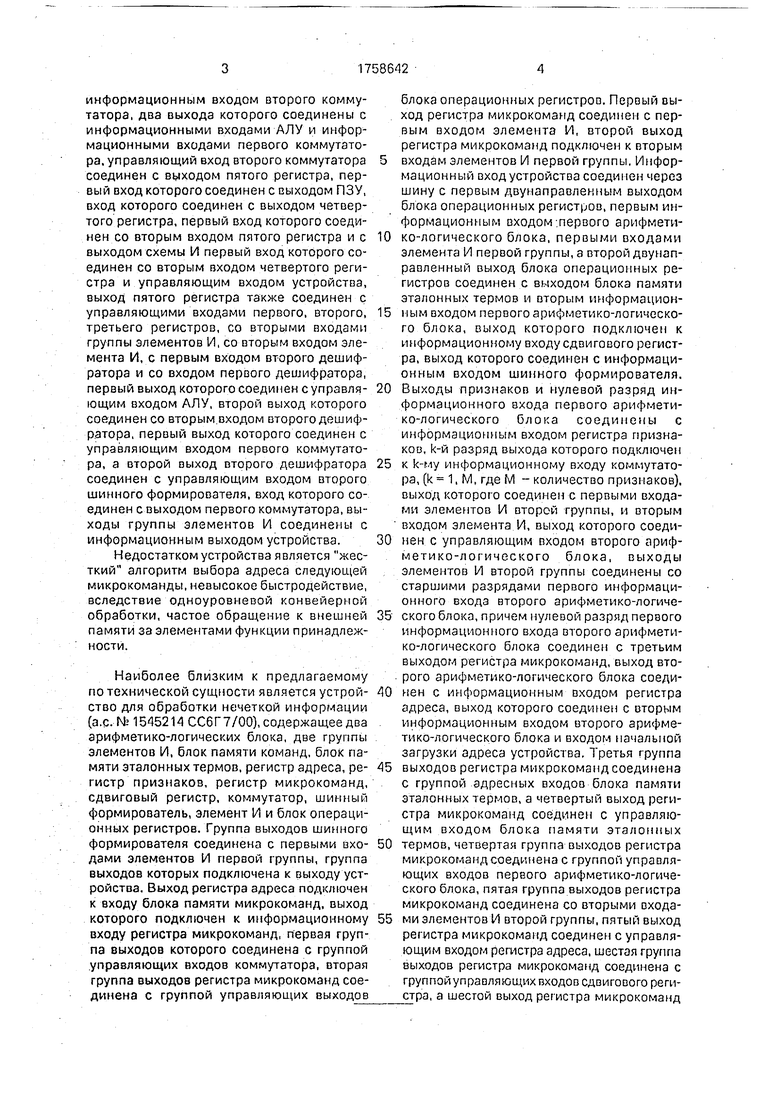

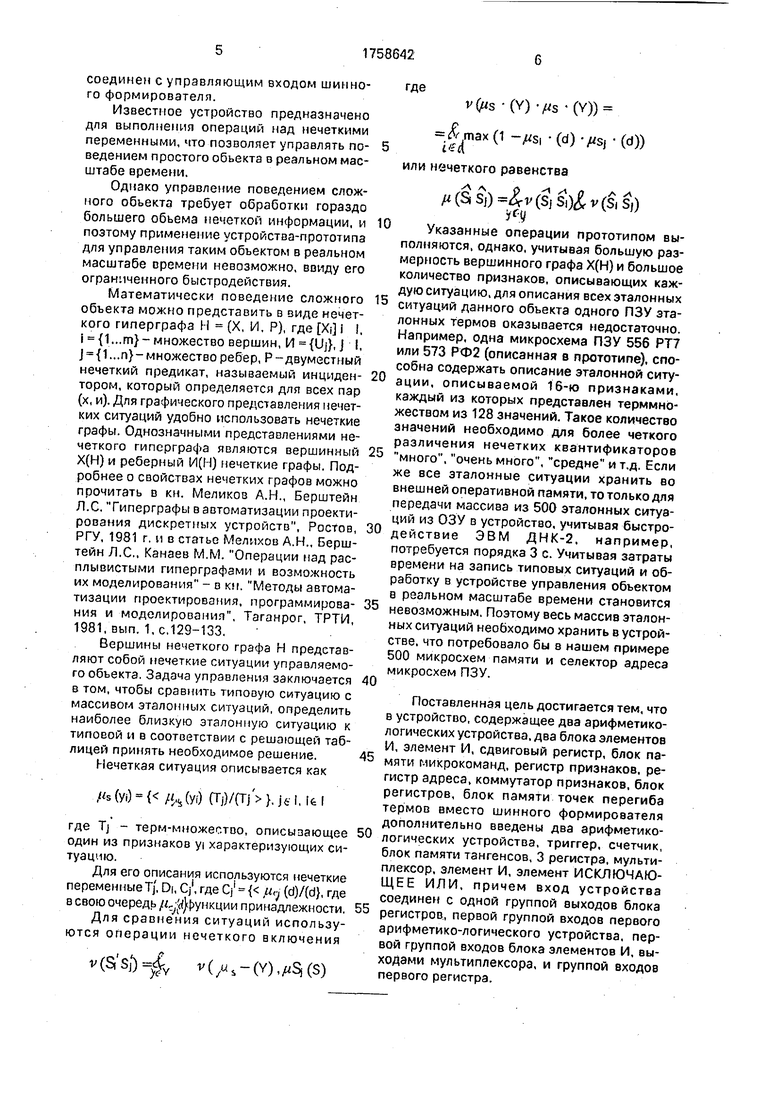

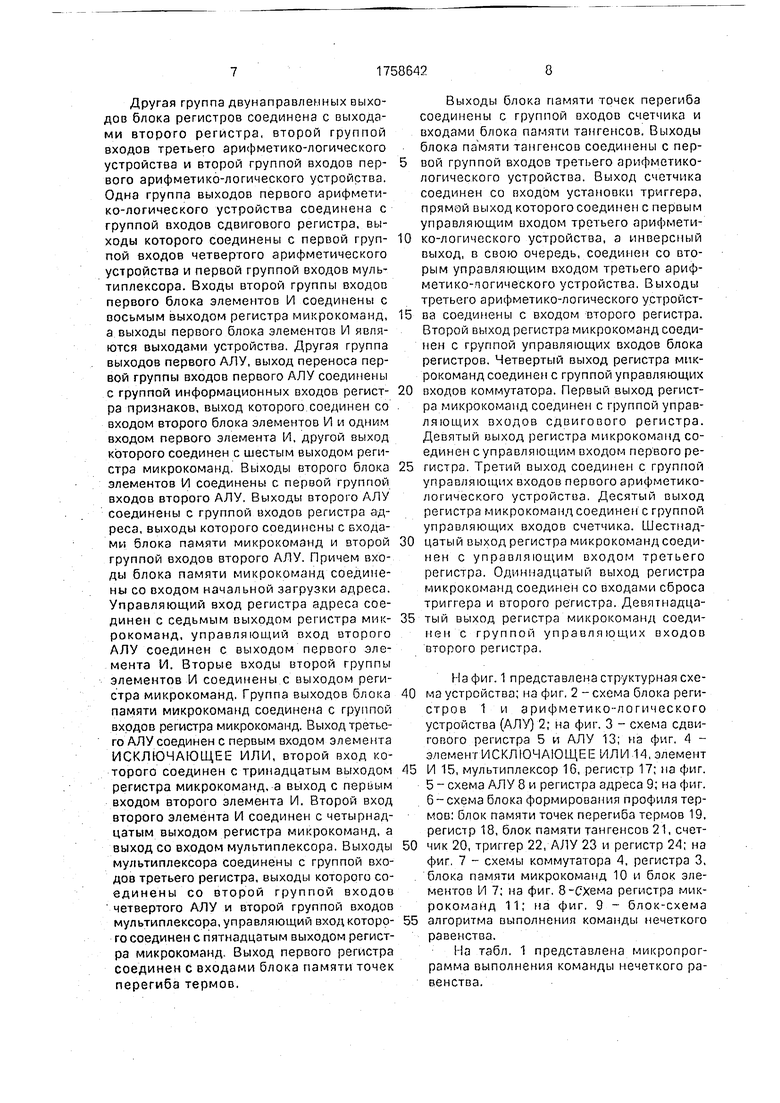

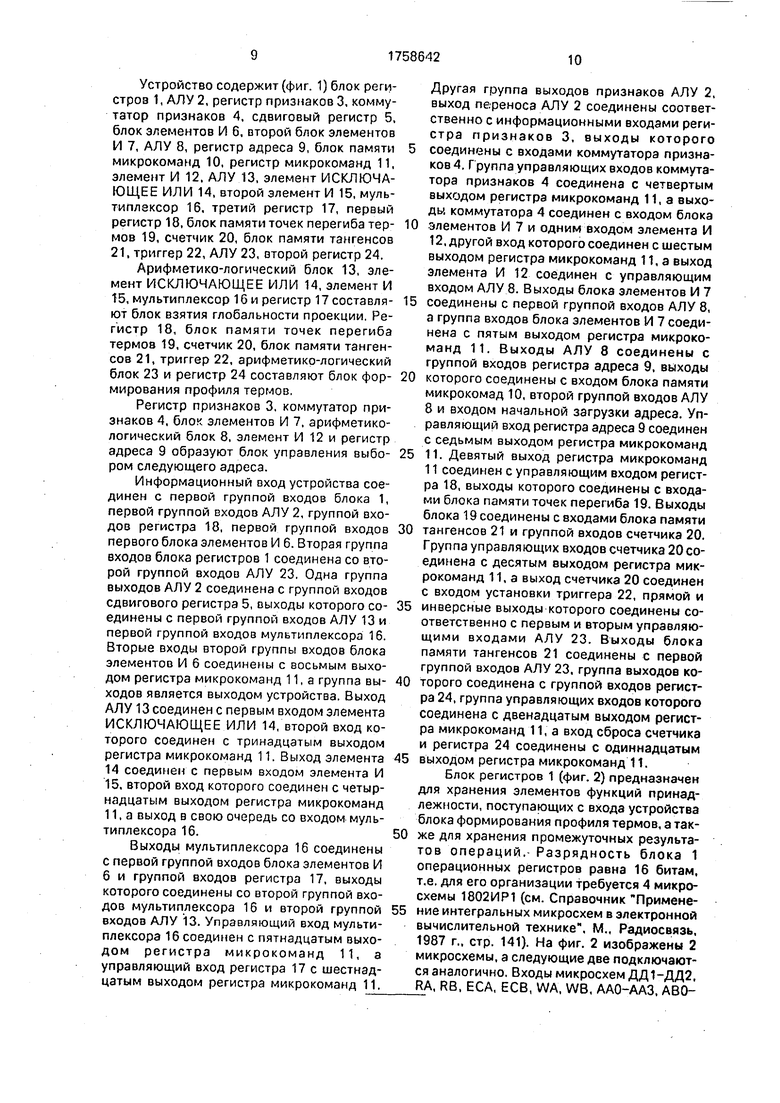

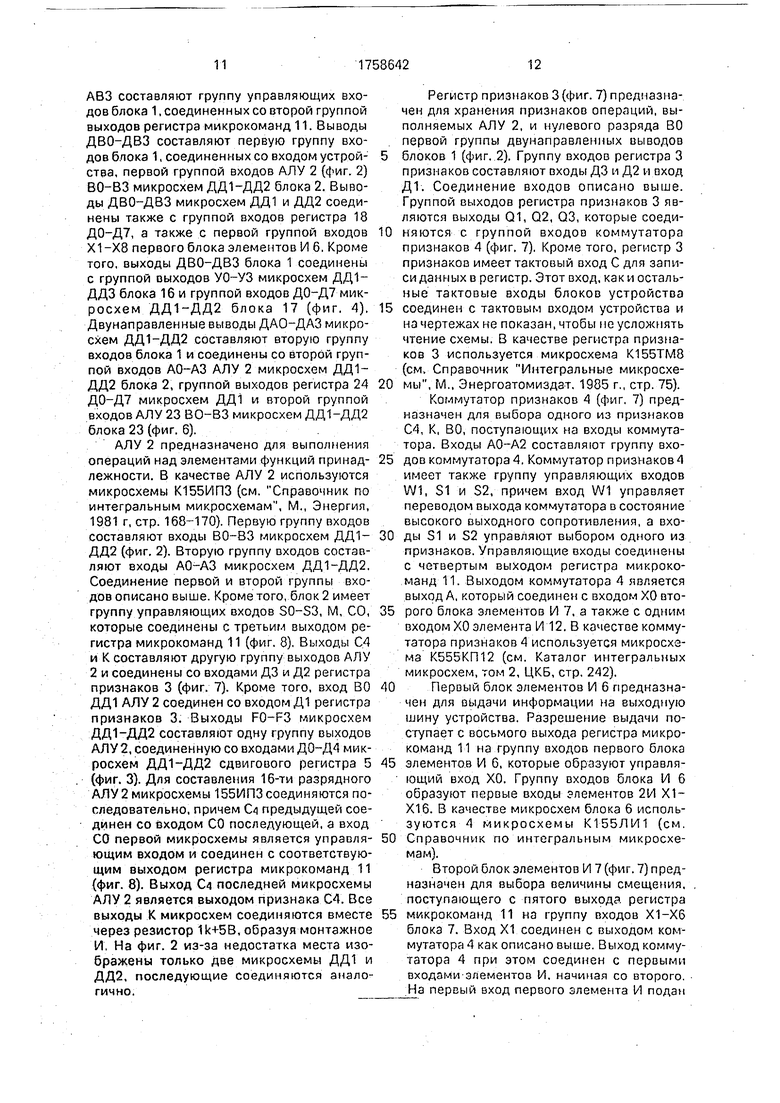

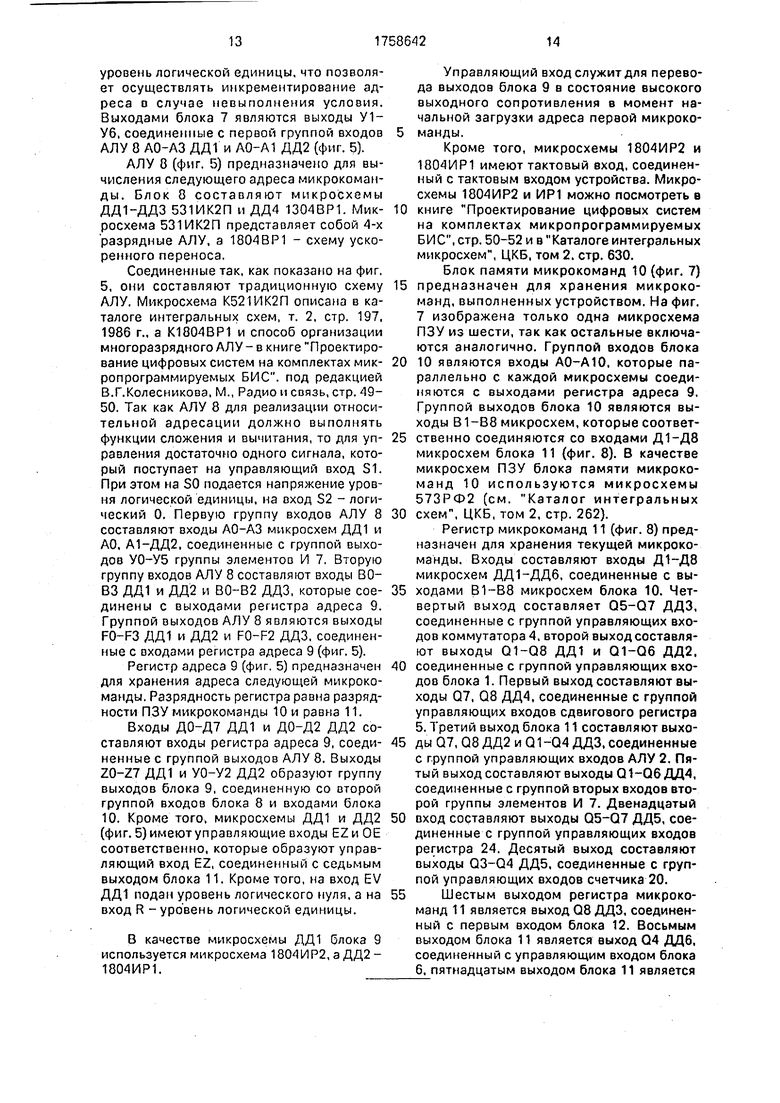

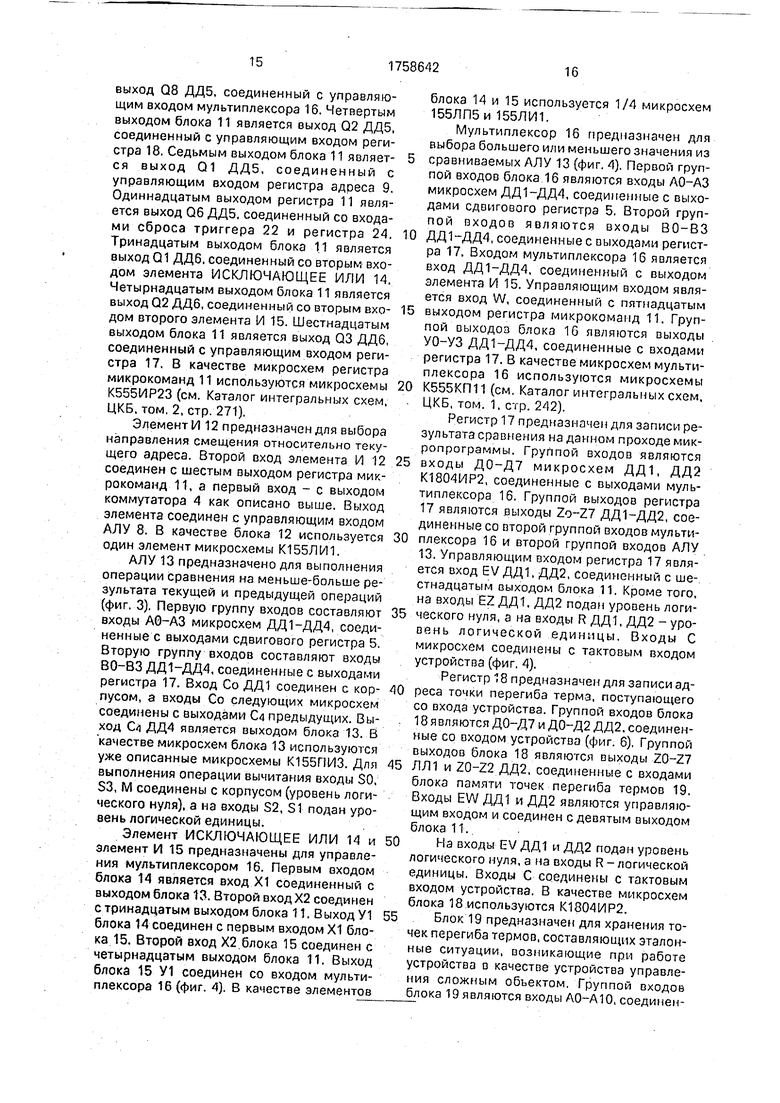

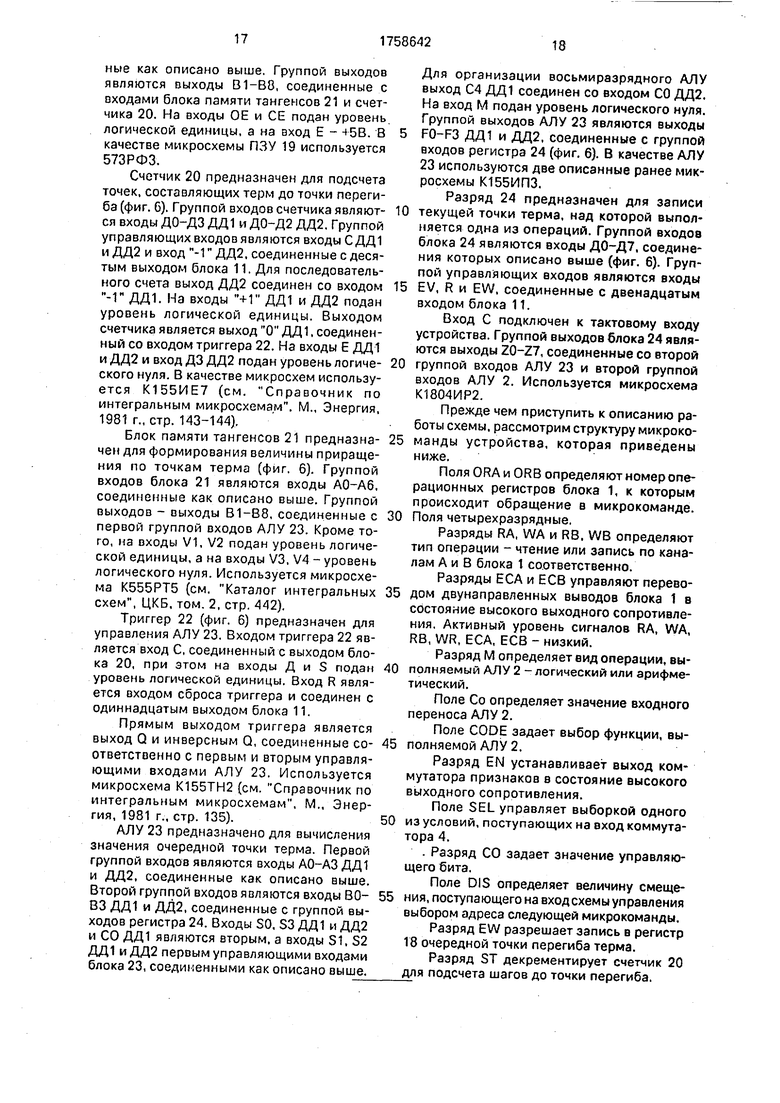

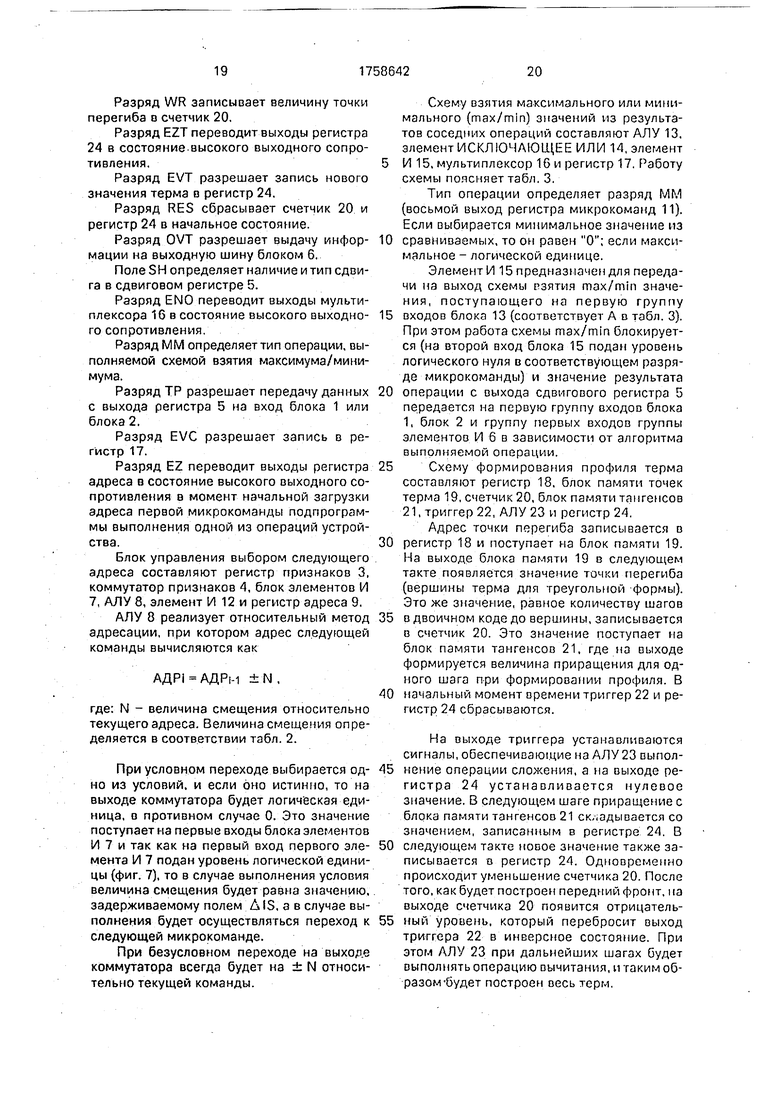

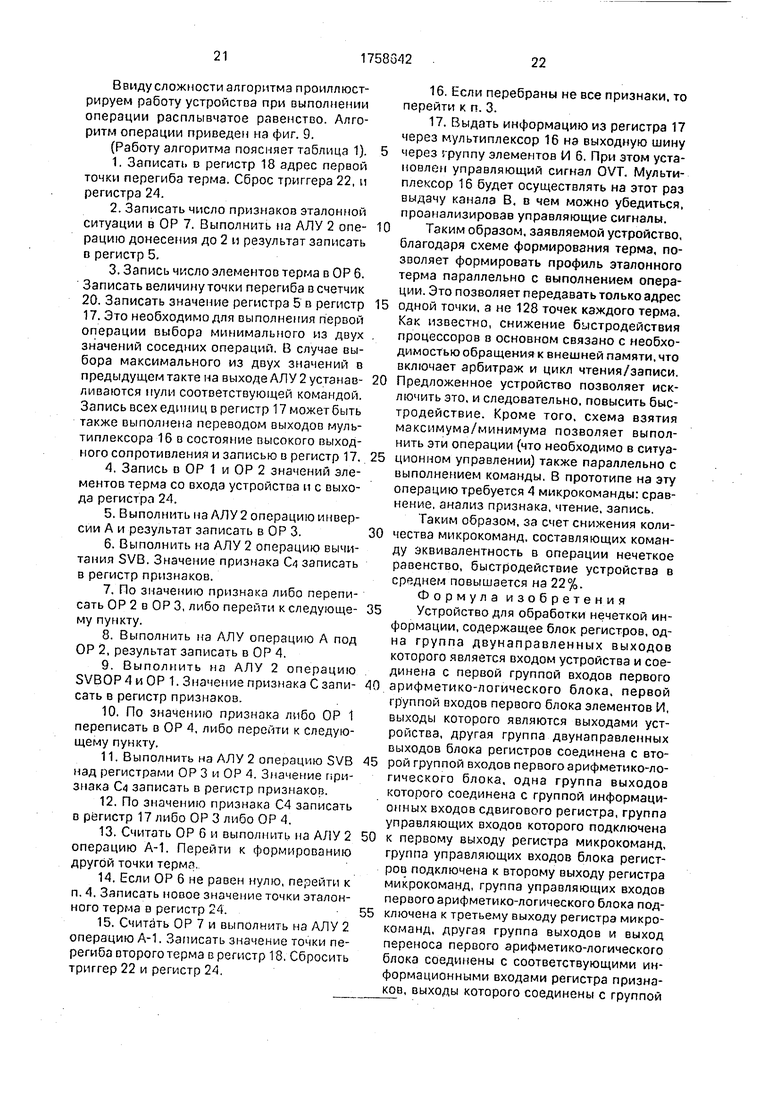

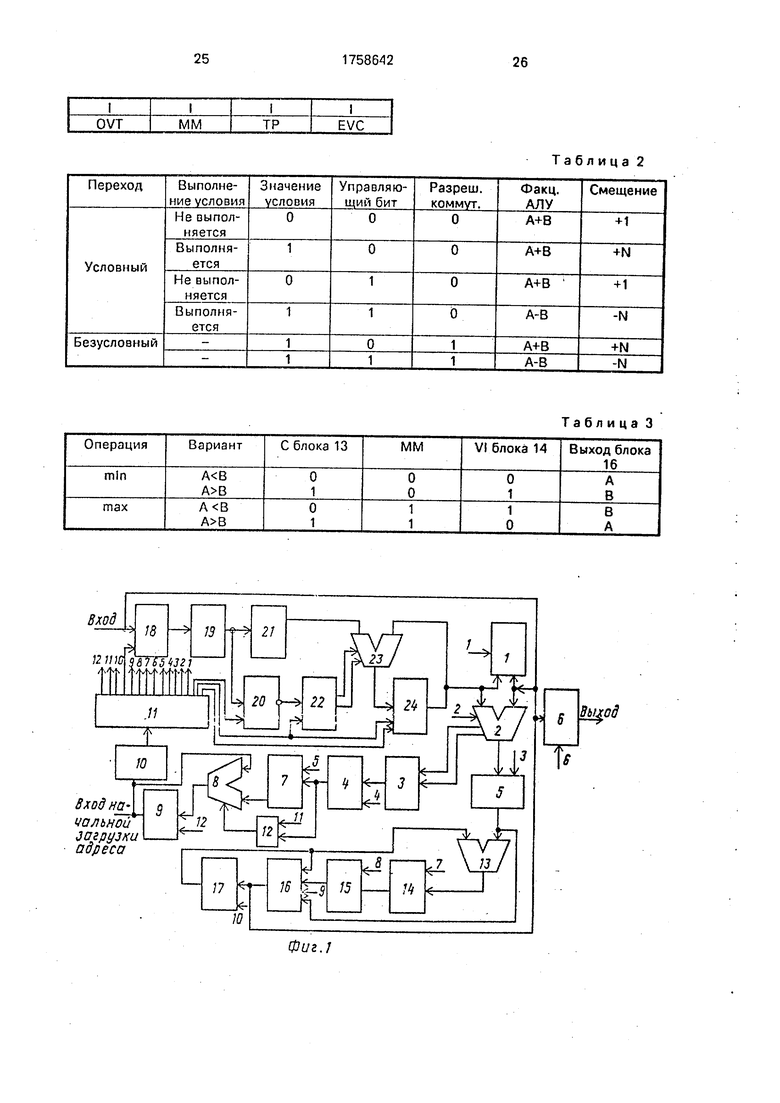

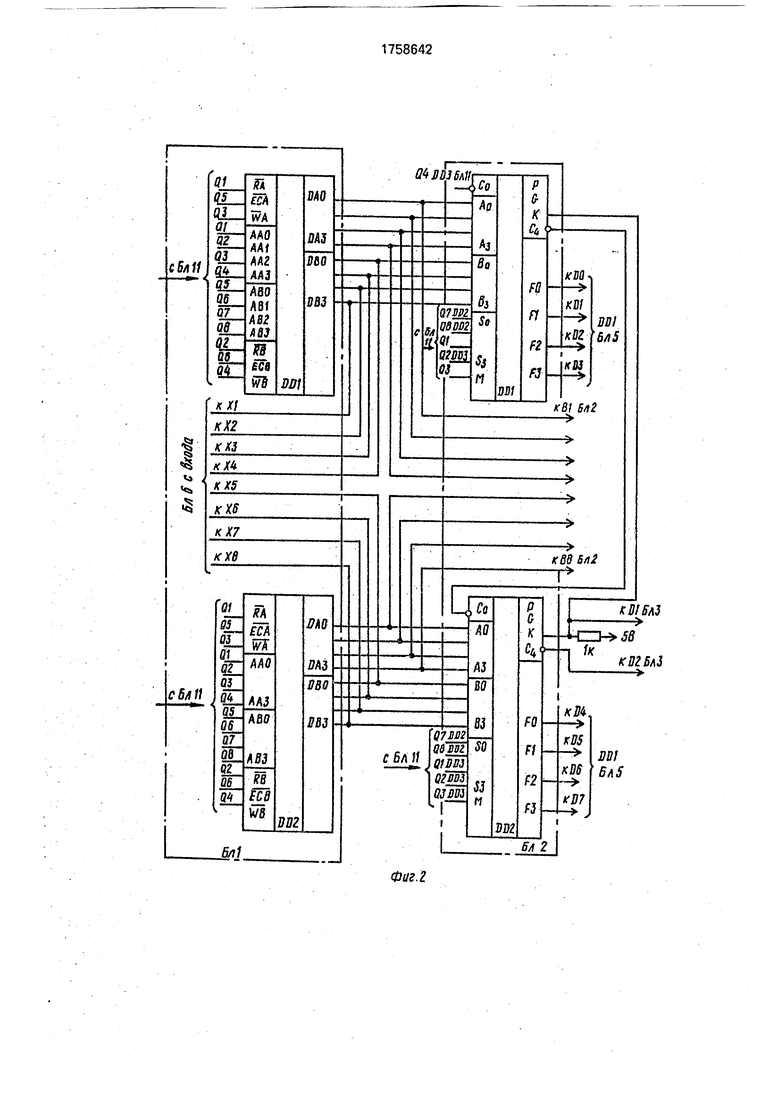

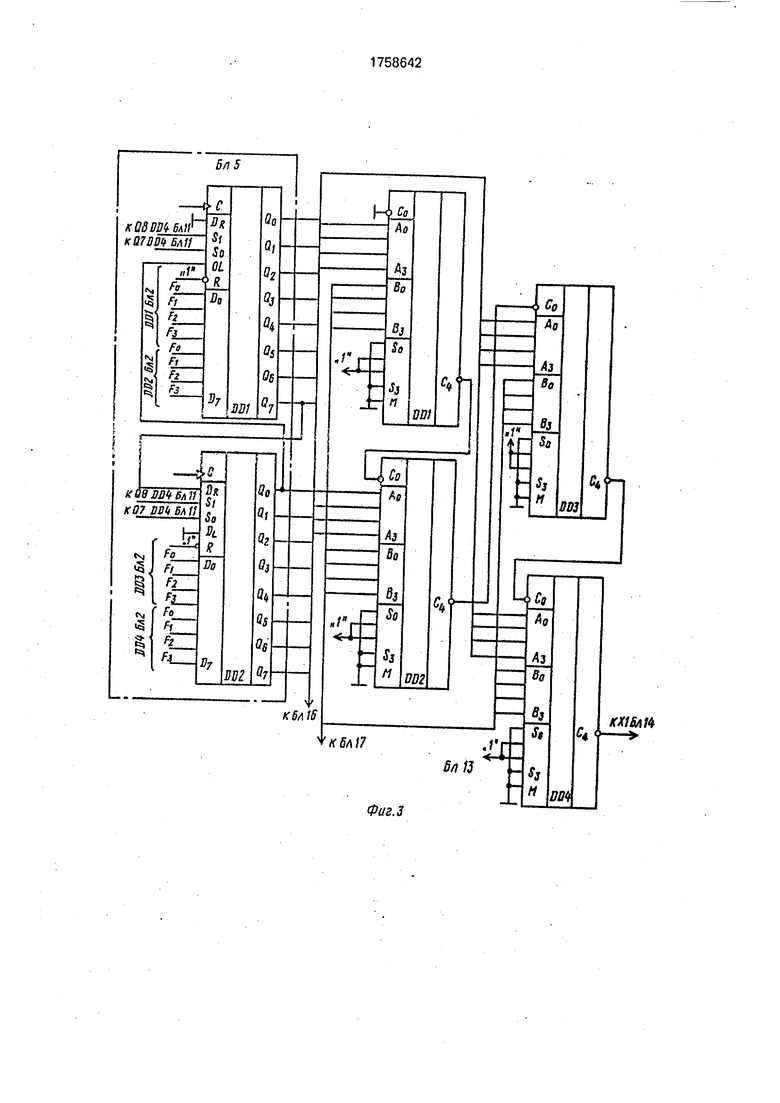

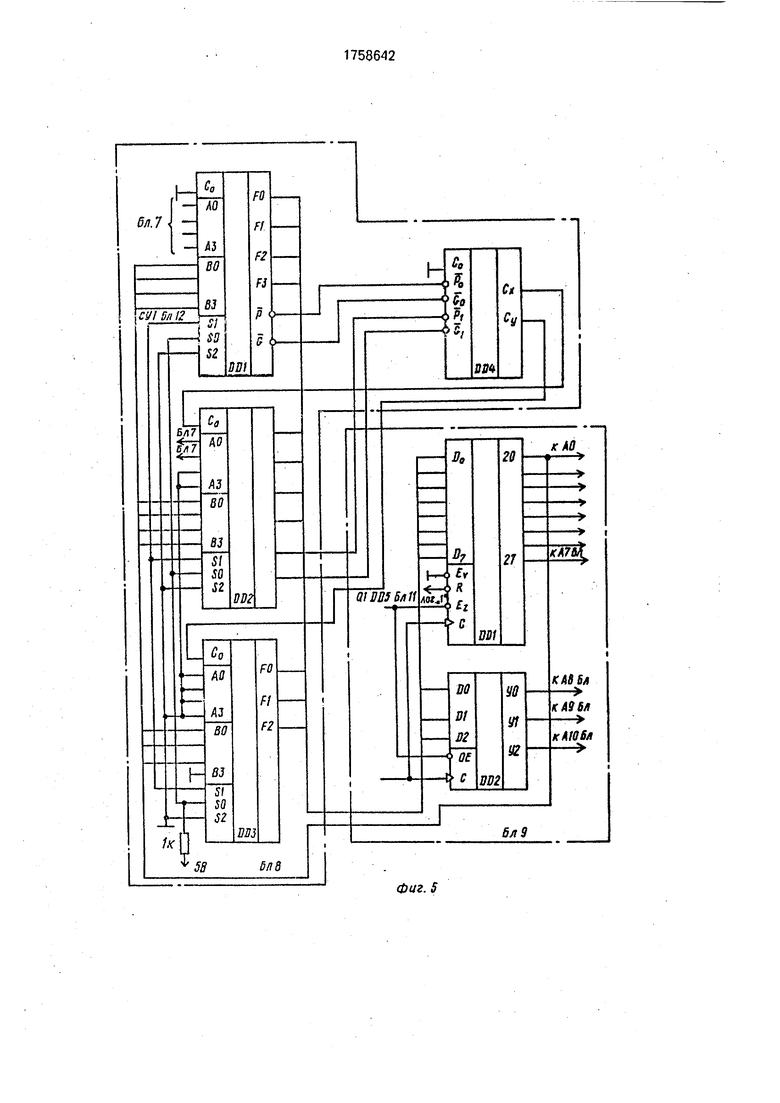

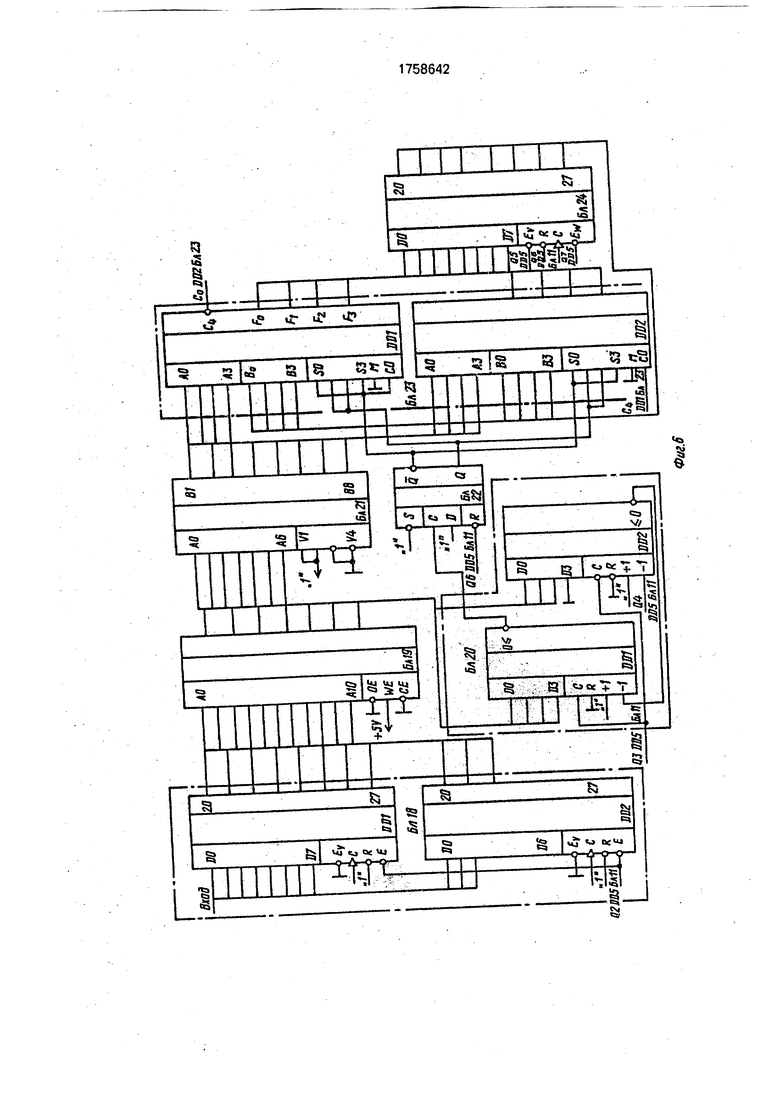

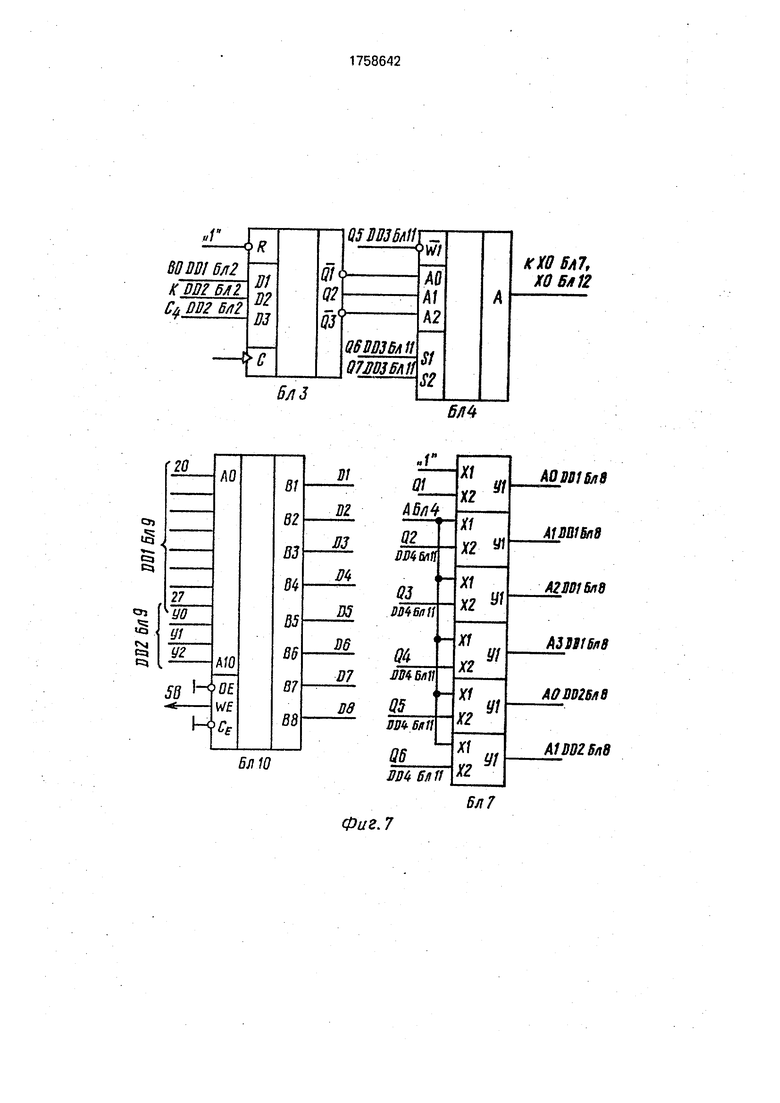

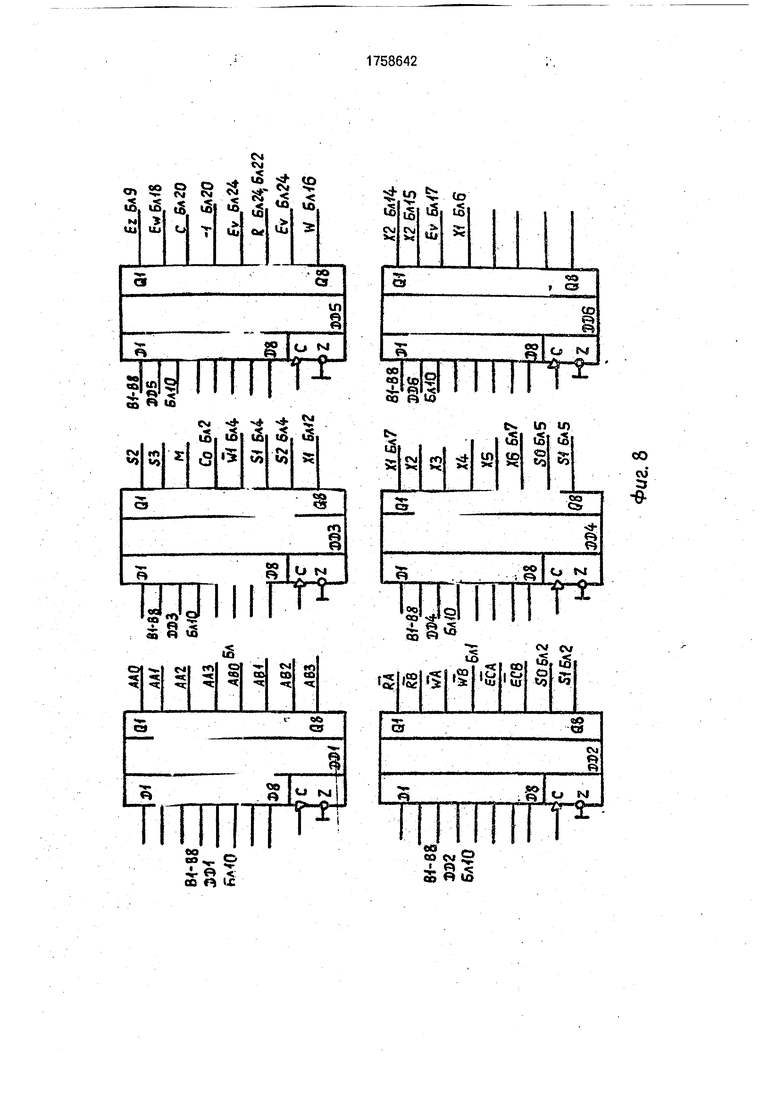

На фиг. 1 представлена структурная схе- ма устройства; на фиг. 2 - схема блока реги- стров 1 и арифметико-логического устройства (АЛУ) 2; на фиг. 3 - схема сдвигового регистра 5 и АЛУ 13; на фиг. 4 - элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, элемент И 15, мультиплексор 16, регистр 17; на фиг.

5- схема АЛУ 8 и регистра адреса 9; на фиг.

6- схема блока формирования профиля термов: блок памяти точек перегиба термов 19, регистр 18, блок памяти тангенсов 21, счетчик 20, триггер 22, АЛУ 23 и регистр 24; на фиг. 7 - схемы коммутатора 4, регистра 3, блока памяти микрокоманд 10 и блок элементов И 7; на фиг. 8-Схема регистра микрокоманд 11; на фиг, 9 - блок-схема

алгоритма выполнения команды нечеткого равенства.

На табл. 1 представлена микропрограмма выполнения команды нечеткого равенства.

Устройство содержит (фиг. 1) блок регистров 1, АЛУ 2, регистр признаков 3, коммутатор признаков 4, сдвиговый регистр 5, блок элементов И 6, второй блок элементов И 7, АЛУ 8, регистр адреса 9, блок памяти микрокоманд 10, регистр микрокоманд 11, элемент И 12, АЛУ 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, второй элемент И 15, мультиплексор 16. третий регистр 17, первый регистр 18, блок памяти точек перегиба термов 19, счетчик 20, блок памяти тангенсов 21, триггер 22, АЛУ 23, второй регистр 24.

Арифметико-логический блок 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, элемент И 15, мультиплексор 16 и регистр 17 составляют блок взятия глобальности проекции. Регистр 18, блок памяти точек перегиба термов 19, счетчик 20, блок памяти тангенсов 21, триггер 22, арифметико-логический блок 23 и регистр 24 составляют блок формирования профиля термов.

Регистр признаков 3, коммутатор признаков 4, блок элементов И 7, арифметико- логический блок 8, элемент И 12 и регистр адреса 9 образуют блок управления выбором следующего адреса.

Информационный вход устройства соединен с первой группой входов блока 1, первой группой входов АЛУ 2, группой входов регистра 18, первой группой входов первого блока элементов И 6. Вторая группа входов блока регистров 1 соединена со второй группой входов АЛУ 23. Одна группа выходов АЛУ 2 соединена с группой входов сдвигового регистра 5, выходы которого соединены с первой группой входов АЛУ 13 и первой группой входов мультиплексора 16. Вторые входы второй группы входов блока элементов И 6 соединены с восьмым выходом регистра микрокоманд 11, а группа выходов является выходом устройства. Выход АЛУ 13 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14, второй вход которого соединен с тринадцатым выходом регистра микрокоманд 11. Выход элемента 14 соединен с первым входом элемента И 15, второй вход которого соединен с четырнадцатым выходом регистра микрокоманд 11, а выход в свою очередь со входом мультиплексора 16.

Выходы мультиплексора 16 соединены с первой группой входов блока элементов И 6 и группой входов регистра 17, выходы которого соединены со второй группой входов мультиплексора 16 и второй группой входов АЛУ 13. Управляющий вход мультиплексора 16 соединен с пятнадцатым выходом регистра микрокоманд 11, а управляющий вход регистра 17 с шестнадцатым выходом регистра микрокоманд 11.

Другая группа выходов признаков АЛУ 2, выход переноса АЛУ 2 соединены соответственно с информационными входами регистра признаков 3, выходы которого

соединены с входами коммутатора признаков 4. Группа управляющих входов коммутатора признаков 4 соединена с четвертым выходом регистра микрокоманд 11, а выходы коммутатора 4 соединен с входом блока

0 элементов И 7 и одним входом элемента И 12, другой вход которого соединен с шестым выходом регистра микрокоманд 11, а выход элемента И 12 соединен с управляющим входом АЛУ 8. Выходы блока элементов И 7

5 соединены с первой группой входов АЛУ 8, а группа входов блока элементов И 7 соединена с пятым выходом регистра микрокоманд 11. Выходы АЛУ 8 соединены с группой входов регистра адреса 9, выходы

0 которого соединены с входом блока памяти микрокомад 10, второй группой входов АЛУ 8 и входом начальной загрузки адреса. Управляющий вход регистра адреса 9 соединен с седьмым выходом регистра микрокоманд

5 11. Девятый выход регистра микрокоманд 11 соединен с управляющим входом регистра 18, выходы которого соединены с входами блока памяти точек перегиба 19. Выходы блока 19 соединены с входами блока памяти

0 тангенсов 21 и группой входов счетчика 20. Группа управляющих входов счетчика 20соединена с десятым выходом регистра микрокоманд 11, а выход счетчика 20 соединен с входом установки триггера 22, прямой и

5 инверсные выходы которого соединены соответственно с первым и вторым управляющими входами АЛУ 23. Выходы блока памяти тангенсов 21 соединены с первой группой входов АЛУ 23. группа выходов ко0 торого соединена с группой входов регистра 24, группа управляющих входов которого соединена с двенадцатым выходом регистра микрокоманд 11, а вход сброса счетчика и регистра 24 соединены с одиннадцатым

5 выходом регистра микрокоманд 11.

Блок регистров 1 (фиг. 2) предназначен для хранения элементов функций принадлежности, поступающих с входа устройства блока формирования профиля термов, а так0 же для хранения промежуточных результатов операций.- Разрядность блока 1 операционных регистров равна 16 битам, т.е. для его организации требуется 4 микросхемы 1802ИР1 (см. Справочник Примене5 кие интегральных микросхем в электронной вычислительной технике. М., Радиосвязь, 1987 г., стр. 141). На фиг. 2 изображены 2 микросхемы, а следующие две подключаются аналогично. Входы микросхем ДД1-ДД2, RA, RB, ЕСА, ЕСВ, WA, WB, ААО-ААЗ, АВОАВЗ составляют группу управляющих входов блока 1, соединенных со второй группой выходов регистра микрокоманд 11. Выводы ДВО-ДВЗ составляют первую группу входов бпока 1, соединенных со входом устройства, первой группой входов АЛУ 2 (фиг. 2) ВО-ВЗ микросхем ДД1-ДД2 блока 2. Выводы ДВО-ДВЗ микросхем ДД1 и ДД2 соединены также с группой входов регистра 18 ДО-Д7, а также с первой группой входов Х1-Х8 первого блока элементов И 6. Кроме того, выходы ДВО-ДВЗ блока 1 соединены с группой выходов УО-УЗ микросхем ДД1- ДДЗ блока 16 и группой входов ДО-Д7 микросхем ДД1-ДД2 блока 17 (фиг. А). Двунаправленные выводы ДАО-ДАЗ микросхем ДД1-ДД2 составляют вторую группу входов блока 1 и соединены со второй группой входов АО-АЗ АЛУ 2 микросхем ДД1- ДД2 блока 2, группой выходов регистра 24 ДО-Д7 микросхем ДД1 и второй группой входов АЛУ 23 ВО-ВЗ микросхем ДД1-ДД2 блока 23 (фиг. 6).

АЛУ 2 предназначено для выполнения операций над элементами функций принадлежности. В качестве АЛУ 2 используются микросхемы К155ИПЗ (см. Справочник по интегральным микросхемам, М., Энергия, 1981 г, стр. 168-170). Первую группу входов составляют входы ВО-ВЗ микросхем ДД1- ДД2 (фиг. 2). Вторую группу входов составляют входы АО-АЗ микросхем ДД1-ДД2. Соединение первой и второй группы входов описано выше. Кроме того, блок 2 имеет группу управляющих входов SO-S3, М, СО, которые соединены с третьим выходом регистра микрокоманд 11 (фиг. 8). Выходы С4 и К составляют другую группу выходов АЛУ 2 и соединены со входами ДЗ и Д2 регистра признаков 3 (фиг. 7). Кроме того, вход ВО ДД1 АЛУ 2 соединен со входом Д1 регистра признаков 3. Выходы FO-F3 микросхем ДД1-ДД2 составляют одну группу выходов АЛУ 2, соединенную со входами ДО-Д4 микросхем ДД1-ДД2 сдвигового регистра 5 (фиг. 3). Для составления 16-ти разрядного АЛУ 2 микросхемы 155ИПЗ соединяются последовательно, причем d предыдущей соединен со входом СО последующей, а вход СО первой микросхемы является управляющим входом и соединен с соответствующим выходом регистра микрокоманд 11 (фиг. 8). Выход С4 последней микросхемы АЛУ 2 является выходом признака С4. Все выходы К микросхем соединяются вместе через резистор 1k+5B, образуя монтажное И, На фиг. 2 из-за недостатка места изображены только две микросхемы ДД1 и ДД2, последующие соединяются аналогично.

Регистр признаков 3 (фиг. 7) предназначен для хранения признаков операций, выполняемых АЛУ 2, и нулевого разряда ВО первой группы двунаправленных выводов

блоков 1 (фиг. 2). Группу входов регистра 3 признаков составляют входы ДЗ и Д2 и вход Д1. Соединение входов описано выше. Группой выходов регистра признаков 3 являются выходы Q1, Q2, Q3, которые соеди0 няются с группой входов коммутатора признаков 4 (фиг. 7). Кроме того, регистр 3 признаков имеет тактовый вход С для записи данных в регистр. Этот вход, как и осталь- ные тактовые входы блоков устройства

5 соединен с тактовым входом устройства и на чертежах не показан, чтобы не усложнять чтение схемы. В качестве регистра признаков 3 используется микросхема К155ТМ8 (см. Справочник Интегральные микросхе0 мы, М., Энергоатомиздат. 1985 г., стр. 75). Коммутатор признаков 4 (фиг. 7) предназначен для выбора одного из признаков С4, К, ВО, поступающих на входы коммутатора. Входы АО-А2 составляют группу вхо5 дов коммутатора 4, Коммутатор признаков4 имеет также группу управляющих входов W1, S1 и S2, причем вход W1 управляет переводом выхода коммутатора в состояние высокого выходного сопротивления, а вхо0 ды S1 и S2 управляют выбором одного из признаков. Управляющие входы соединены с четвертым выходом регистра микрокоманд 11. Выходом коммутатора 4 является выход А, который соединен с входом ХО вто5 рого блока элементов И 7. а также с одним входом ХО элемента И 12. В качестве коммутатора признаков 4 используется микросхз- мз К555КП12 (см. Каталог интегральных микросхем, том 2, ЦКБ, стр. 242).

0 Первый блок элементов И 6 предназначен для оыдачи информации на выходную шину устройства. Разрешение выдачи по- сгупаетс восьмого выхода регистра микрокоманд 11 на группу входов первого блока

5 элементов И 6, которые образуют управляющий вход ХО. Группу входов блока И 6 образуют первые входы элементов 2И Х1- Х16. В качестве микросхем блока 6 используются 4 микросхемы К155ЛИ1 (см.

0 Справочник по интегральным микросхемам).

Второй блок элементов И 7 (фиг. 7) предназначен для выбора величины смещения, поступающего с пятого выхода регистра

5 микрокоманд 11 на группу входов Х1-Х6 блока 7. Вход Х1 соединен с выходом коммутатора 4 как описано выше. Выход коммутатора 4 при этом соединен с первыми входами элементов И, начиная со второго. На первый вход первого элемента И подан

уровень логической единицы, что позволяет осуществлять инкрементирование адреса о случае невыполнения условия. Выходами блока 7 являются выходы У1- Уб,соединенные с первой группой входов АЛУ 8 АО-АЗ ДД1 и АО-А1 ДД2 (фиг. 5).

АЛУ 8 (фиг. 5) предназначено для вычисления следующего адреса микрокоманды. Блок 8 составляют микросхемы ДД1-ДДЗ 531ИК2П и ДД4 1304ВР1. Микросхема 531ИК2П представляет собой 4-х разрядные АЛУ, а 1804ВР1 - схему ускоренного переноса.

Соединенные так, как показано на фиг. 5, они составляют традиционную схему АЛУ. Микросхема К521ИК2П описана в каталоге интегральных схем, т. 2, стр. 197, 1986 г., а К1804ВР1 и способ организации многоразрядного АЛУ - в книге Проектирование цифровых систем на комплектах мик- ропрограммируемых БИС, под редакцией В.Г.Колесникова, М., Радио и связь, стр. 49- 50. Так как АЛУ 8 для реализации относительной адресации должно выполнять функции сложения и вычитания, то для управления достаточно одного сигнала, который поступает на управляющий вход S1. При этом на SO подается напряжение уровня логической единицы, на вход S2 - логический 0. Первую группу входов АЛУ 8 составляют входы АО-АЗ микросхем ДД1 и АО, А1-ДД2, соединенные с группой выходов УО-У5 группы элементов И 7. Вторую группу входов АЛУ 8 составляют входы ВО- ВЗ ДД1 и ДД2 и ВО-В2 ДДЗ, которые соединены с выходами регистра адреса 9. Группой выходов АЛУ 8 являются выходы FO-F3 ДД1 и ДД2 и FO-F2 ДДЗ. соединенные с входами регистра адреса 9 (фиг. 5).

Регистр адреса 9 (фиг. 5) предназначен для хранения адреса следующей микрокоманды. Разрядность регистра равна разрядности ПЗУ микрокоманды 10 и равна 11.

Входы ДО-Д7 ДД1 и ДО-Д2 ДД2 составляют входы регистра адреса 9, соединенные с группой выходов АЛУ 8. Выходы ZO-Z7 ДД1 и УО-У2 ДД2 образуют группу выходов блока 9, соединенную со второй группой входов блока 8 и входами блока 10. Кроме того, микросхемы ДД1 и ДД2 (фиг. 5)имеютуправляющие входы EZn ОЕ соответственно, которые образуют управляющий вход EZ, соединенный с седьмым выходом блока 11, Кроме того, на вход EV ДД1 подан уровень логического нуля, а на вход R - уровень логической единицы.

В качестве микросхемы ДД1 блока 9 используется микросхема 1804ИР2,а ДД2- 1804ИР1.

Управляющий вход служит для перевода выходов блока 9 в состояние высокого выходного сопротивления в момент начальной загрузки адреса первой микроко- манды.

Кроме того, микросхемы 1804ИР2 и 1804ИР1 имеют тактовый вход, соединенный с тактовым входом устройства. Микросхемы 1804ИР2 и ИР1 можно посмотреть в

0 книге Проектирование цифровых систем на комплектах микропрограммируемых БИС, стр. 50-52 и в Каталоге интегральных микросхем, ЦКБ, том 2. стр. 630.

Блок памяти микрокоманд 10 (фиг. 7)

5 предназначен для хранения микрокоманд, выполненных устройством. На фиг. 7 изображена только одна микросхема ПЗУ из шести, так как остальные включаются аналогично. Группой входов блока

0 10 являются входы АО-А10, которые параллельно с каждой микросхемы соединяются с выходами регистра адреса 9. Группой выходов блока 10 являются выходы В1-В8 микросхем, которые соответ5 ственно соединяются со входами Д1-Д8 микросхем блока 11 (фиг. 8). В качестве микросхем ПЗУ блока памяти микрокоманд 10 используются микросхемы 573РФ2 (см. Каталог интегральных

0 схем, ЦКБ, том 2, стр. 262).

Регистр микрокоманд 11 (фиг. 8) предназначен для хранения текущей микрокоманды. Входы составляют входы Д1-Д8 микросхем ДД1-ДД6, соединенные с вы5 ходами В1-В8 микросхем блока 10. Четвертый выход составляет Q5-Q7 ДДЗ, соединенные с группой управляющих входов коммутатора 4, второй выход составляют выходы Q1-Q8 ДД1 и Q1-Q6 ДД2.

0 соединенные с группой управляющих входов блока 1. Первый выход составляют выходы Q7, Q8 ДД4, соединенные с группой управляющих входов сдвигового регистра

5.Третий выход блока 11 составляют выхо- 5 ды Q7, Q8 ДД2 и Q1-Q4 ДДЗ, соединенные

с группой управляющих входов АЛУ 2. Пятый выход составляют выходы Q1-Q6 ДД4, соединенные с группой вторых входов второй группы элементов И 7. Двенадцатый

0 вход составляют выходы Q5-Q7 ДД5, соединенные с группой управляющих входов регистра 24. Десятый выход составляют выходы Q3-Q4 ДД5. соединенные с группой управляющих входов счетчика 20.

5 Шестым выходом регистра микрокоманд 11 является выходОЗ ДДЗ, соединенный с первым входом блока 12. Восьмым выходом блока 11 является выход Q4 ДД6, соединенный с управляющим входом блока

6,пятнадцатым выходом блока 11 является

выход Q8 ДД5, соединенный с управляющим входом мультиплексора 16, Четвертым выходом блока 11 является выход Q2 ДД5, соединенный с управляющим входом регистра 18. Седьмым выходом блока 11 является выход Q1 ДД5, соединенный с управляющим входом регистра адоеса 9. Одиннадцатым выходом регистра 11 является выход Q6 ДД5, соединенный со входами сброса триггера 22 и регистра 24. Тринадцатым выходом блока 11 является выход Q1 ДД6. соединенный со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14. Четырнадцатым выходом блока 11 является выход Q2 ДД6, соединенный со вторым входом второго элемента И 15. Шестнадцатым выходом блока 11 является выход Q3 ДД6, соединенный с управляющим входом регистра 17, В качестве микросхем регистра микрокоманд 11 используются микросхемы К555ИР23 (см. Каталог интегральных схем, ЦКБ, том. 2, стр. 271).

Элемент И 12 предназначен для выбора направления смещения относительно текущего адреса. Второй вход элемента И 12 соединен с шестым выходом регистра микрокоманд 11, а первый вход - с выходом коммутатора 4 как описано выше. Выход элемента соединен с управляющим входом АЛУ 8. В качестве блока 12 используется один элемент микросхемы К155ЛИ1.

АЛУ 13 предназначено для выполнения операции сравнения на меньше-больше результата текущей и предыдущей операций (фиг. 3). Первую группу входов составляют входы А0-АЗ микросхем ДД1-ДД4, соединенные с выходами сдвигового регистра 5. Вторую группу входов составляют входы 80-ВЗ ДД1-ДД4, соединенные с выходами регистра 17. Вход Со ДД1 соединен с корпусом, а входы Со следующих микросхем соединены с выходами СА предыдущих. Выход G ДД4 является выходом блока 13. В качестве микросхем блока 13 используются уже описанные микросхемы К155ПИЗ. Для выполнения операции вычитания входы SO, S3, М соединены с корпусом (уровень логического нуля), а иа входы S2, S1 подан уровень логической единицы.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и элемент И 15 предназначены для управления мультиплексором 16. Первым входом блока 14 является вход Х1 соединенный с выходом блока 13. Второй вход Х2 соединен с тринадцатым выходом блока 11. Выход У1 блока 14 соединен с первым входом Х1 блока 15. Второй вход Х2 блока 15 соединен с четырнадцатым выходом блока 11. Выход блока 15 У1 соединен со входом мультиплексора 16 (фиг. 4). В качестве элементов

блока 14 и 15 используется 1/4 микросхем 155ЛП5и 155ЛИ1.

Мультиплексор 16 предназначен для выбора большего или меньшего значения из

сравниваемых АЛУ 13 (фиг. 4). Первой группой входов блока 16 являются входы АО-АЗ микросхем ДД1-ДД4, соединенные с выходами сдвигового регистра 5. Второй группой входов являются входы ВО-ВЗ

0 ДД1-ДД4, соединенные с выходами регистра 17. Входом мультиплексора 16 является вход ДД1-ДД4, соединенный с выходом элемента И 15. Управляющим входом является вход W, соединенный с пятнадцатым

5 выходом регистра микрокоманд 11. Группой выходов блока 10 являются выходы УО-УЗ ДД1-ДД4, соединенные с входами регистра 17. В качестве микросхем мультиплексора 16 используются микросхемы

0 К555КП11 (см, Каталог интегральных схем, ЦКБ, том. 1. стр. 242).

Регистр 17 предназначен для записи результата сравнения на данном проходе микропрограммы. Группой входов являются

5 входы ДО-Д7 микросхем ДД1, ДД2 К1804ИР2, соединенные с выходами мультиплексора 16. Группой выходов регистра

17являются выходы Zo-Z7 ДД1-ДД2, соединенные со второй группой входов мульти0 плексора 16 и второй группой входов АЛУ 13. Управляющим входом регистра 17 является вход EV ДД1, ДД2, соединенный с шестнадцатым выходом блока 11. Кроме того, на входы EZ ДД1. ДД2 подан уровень логи5 ческого нуля, а на входы R ДД1, ДД2 - уровень логической единицы. Входы С микросхем соединены с тактовым входом устройства (фиг. 4),

Регистр 18 предназначен для записи ад0 реса точки перегиба терма, поступающего со входа устройства. Группой входов блока

18являются ДО-Д7 и ДО-Д2 ДД2, соединенные со входом устройства (фиг. 6), Группой выходов блока 18 являются выходы 20-27

5 ЛЛ1 и 20-22 ДД2. соединенные с входами блока памяти точек перегиба термов 19, Входы EW ДД1 и ДД2 являются управляющим входом и соединен с девятым выходом блока 11.

0На входы EV ДД1 и ДД2 подан уровень

логического нуля, а на входы R -логической единицы, Входы С соединены с тактовым входом устройства. В качестве микросхем блока 18 используются К1804ИР2.

5 Блок 19 предназначен для хранения точек перегиба термов, составляющих эталонные ситуации, возникающие при работе устройства о качестве устройства управления сложным объектом. Группой входов блока 19 являются входы АО-А10, соединенные как описано выше. Группой выходов являются выходы В1-В8, соединенные с входами блока памяти тангенсов 21 и счетчика 20. На входы ОЕ и СЕ подан уровень логической единицы, а на вход Е - -+5В. В качестве микросхемы ПЗУ 19 используется 573РФЗ.

Счетчик 20 предназначен для подсчета точек, составляющих терм до точки перегиба (фиг. 6). Группой входов счетчика являются входы ДО-ДЗ ДД1 и ДО-Д2 ДД2. Группой управляющих входов являются входы С ДД1 и ДД2 и вход -1 ДД2, соединенные с десятым выходом блока 11. Для последовательного счета выход ДД2 соединен со входом -Г ДД1. На входы +Г ДД1 и ДД2 подан уровень логической единицы. Выходом счетчика является выход О ДД1, соединенный со входом триггера 22. На входы Е ДД1 и ДД2 и вход ДЗ ДД2 подан уровень логического нуля.В качестве микросхем используется К155ИЕ7 (см. Справочник по интегральным микросхемам. М., Энергия, 1981 г., стр. 143-144).

Блок памяти тангенсов 21 предназначен для формирования величины приращения по точкам терма (фиг. 6). Группой входов блока 21 являются входы АО-А6, соединенные как описано выше. Группой выходов - выходы В1-В8,соединенные с первой группой входов АЛУ 23. Кроме того, на входы V1, V2 подан уровень логической единицы, а на входы V3, V4 - уровень логического нуля. Используется микросхема К555РТ5 (см. Каталог интегральных схем, ЦКБ, том. 2, стр. 442).

Триггер 22 (фиг. 6) предназначен для управления АЛУ 23. Входом триггера 22 является вход С, соединенный с выходом блока 20, при этом на входы Д и S подан уровень логической единицы. Вход R является входом сброса триггера и соединен с одиннадцатым выходом блока 11.

Прямым выходом триггера является выход Q и инверсным Q, соединенные соответственно с первым и вторым управляющими входами АЛУ 23. Используется микросхема К155ТН2 (см. Справочник по интегральным микросхемам, М., Энергия, 1981 г., стр. 135).

АЛУ 23 предназначено для вычисления значения очередной точки терма. Первой группой входов являются входы АО-АЗ ДД1 и ДД2, соединенные как описано выше. Второй группой входов являются входы ВО- ВЗ ДД1 и ДД2, соединенные с группой выходов регистра 24. Входы SO, S3 ДД1 и ДД2 и СО ДД1 являются вторым, а входы S1, S2 ДД1 и ДД2 первым управляющими входами блока 23, соединенными как описано выше.

Для организации восьмиразрядного АЛУ выход С4 ДД1 соединен со входом СО ДД2. На вход М подан уровень логического нуля. Группой выходов АЛУ 23 являются выходы FO-F3 ДД1 и ДД2, соединенные с группой входов регистра 24 (фиг. 6). В качестве АЛУ 23 используются две описанные ранее микросхемы К155ИПЗ.

Разряд 24 предназначен для записи 0 текущей точки терма, над которой выполняется одна из операций. Группой входов блока 24 являются входы ДО-Д7, соединения которых описано выше (фиг. 6). Группой управляющих входов являются входы 5 EV, R и EW, соединенные с двенадцатым входом блока 11.

Вход С подключен к тактовому входу устройства. Группой выходов блока 24 являются выходы ZO-Z7, соединенные со второй 0 группой входов АЛУ 23 и второй группой входов АЛУ 2. Используется микросхема К1804ИР2.

Прежде чем приступить к описанию работы схемы, рассмотрим структуру микроко- 5 манды устройства, которая приведены ниже.

Поля ORA и ORB определяют номер операционных регистров блока 1, к которым происходит обращение в микрокоманде. 0 Поля четырехразрядные.

Разряды RA, WA и RB. WB определяют тип операции - чтение или запись по каналам А и В блока 1 соответственно.

Разряды ЕСА и ЕСВ управляют перево- 5 дом двунаправленных выводов блока 1 в состояние высокого выходного сопротивления. Активный уровень сигналов RA, WA, RB, WR, ЕСА, ЕСВ - низкий.

Разряд М определяет вид операции, вы- 0 полняемый АЛУ 2 - логический или арифметический.

Поле Со определяет значение входного переноса АЛУ 2.

Поле CODE задает выбор функции, вы- 5 полняемой АЛУ 2.

Разряд EN устанавливает выход коммутатора признаков в состояние высокого выходного сопротивления.

Поле SEL управляет выборкой одного 0 из условий, поступающих на вход коммутатора 4.

. Разряд СО задает значение управляющего бита.

Поле DIS определяет величину смеще- 5 ния, поступающего на вход схемы управления выбором адреса следующей микрокоманды.

Разряд EW разрешает запись в регистр 18 очередной точки перегиба терма.

Разряд ST декрементирует счетчик 20 для подсчета шагов до точки перегиба.

Разряд WR записывает величину точки перегиба о счетчик 20,

Разряд EZT переводит выходы регистра 24 в состояние высокого выходного сопротивления.

Разряд EVT разрешает запись нового значения терма в регистр 24,

Разряд RES сбрасывает счетчик 20 и регистр 24 в начальное состояние.

Разряд OVT разрешает выдачу информации на выходную шину блоком 6.

Поле SH определяет наличие и тип сдвига в сдвиговом регистре 5.

Разряд ENO переводит выходы мультиплексора 16 в состояние высокого выходного сопротивления.

Разряд ММ определяет тип операции, выполняемой схемой взятия максимума/минимума.

Разряд ТР разрешает передачу данных с выхода регистра 5 на вход блока 1 или блока 2.

Разряд EVC разрешает запись в регистр 17.

Разряд EZ переводит выходы регистра адреса в состояние высокого выходного сопротивления в момент начальной загрузки адреса первой микрокоманды подпрограммы выполнения одной из операций устройства.

Блок управления выбором следующего адреса составляют регистр признаков 3, коммутатор признаков 4, блок элементов И 7, АЛ У 8, элемент И 12 и регистр адреса 9.

АЛУ 8 реализует относительный метод адресации, при котором адрес следующей команды вычисляются как

±N ,

где: N - величина смещения относительно текущего адреса. Величина смещения определяется в соответствии табл. 2.

При условном переходе выбирается одно из условий, и если оно истинно, то на выходе коммутатора будет логическая единица, в противном случае 0. Это значение поступает на первые входы блока элементов И 7 и так как на первый вход первого элемента И 7 подан уровень логической единицы (фиг. 7), то в случае выполнения условия величина смеа1ения будет равна значению, задерживаемому полем Д15, а в случае выполнения будет осуществляться переход к следующей микрокоманде.

При безусловном переходе на выходе коммутатора всегда будет на ± N относительно текущей команды.

Схему взятия максимального или минимального (max/min) значений из результатов соседних операций составляют АЛУ 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, элемент

И 15, мультиплексор 16 и регистр 17. Работу схемы поясняет табл. 3.

Тип операции определяет разряд ММ (восьмой выход регистра микрокоманд 11). Если выбирается минимальное значение из

сравниваемых, то он равен если максимальное - логической единице.

Элемент И 15 предназначен для передачи на выход схемы РЗЯТИЯ max/min значения, поступающего на первую группу

входов блока 13 (соответствует А в табл. 3). При этом работа схемы max/min блокируется (на второй вход блока 15 подан уровень логического нуля в соответствующем разряде микрокоманды) и значение результата

операции с выхода сдвигового регистра 5 передается на первую группу входов блока 1, блок 2 и группу первых входов группы элементов И 6 в зависимости от алгоритма выполняемой операции.

Схему формирования профиля терма составляют регистр 18, блок памяти точек терма 19, счетчик 20, блок памяти тангенсов 21, триггер 22, АЛ У 23 и регистр 24.

Адрес точки перегиба записывается в

регистр 18 и поступает на блок памяти 19. На выходе блока памяти 19 в следующем такте появляется значение точки перегиба (вершины терма для треугольной формы). Это же значение, равное количеству шагов

в двоичном коде до вершины, записывается в счетчик 20. Это значение поступает на блок памяти тангенсов 21, где на выходе формируется величина приращения для одного шага при формировании профиля. В

начальный момент времени триггер 22 и регистр 24 сбрасываются.

На выходе триггера устанавливаются сигналы, обеспечивающие на АЛУ 23 выполнение операции сложения, а на выходе регистра 24 устанавливается нулевое значение. В следующем шаге приращение с блока памяти тангенсов 21 складывается со значением, записанным в регистре 24. В

следующем такте новое значение также записывается в регистр 24. Одновременно происходит уменьшение счетчика 20. После того, как будет построен передний фронт, на выходе счетчика 20 появится отрицательный уровень, который перебросит выход триггера 22 в инверсное состояние. При этом АЛУ 23 при дальнейших шагах будет выполнять операцию вычитания, и таким об- разом будет построен весь терм.

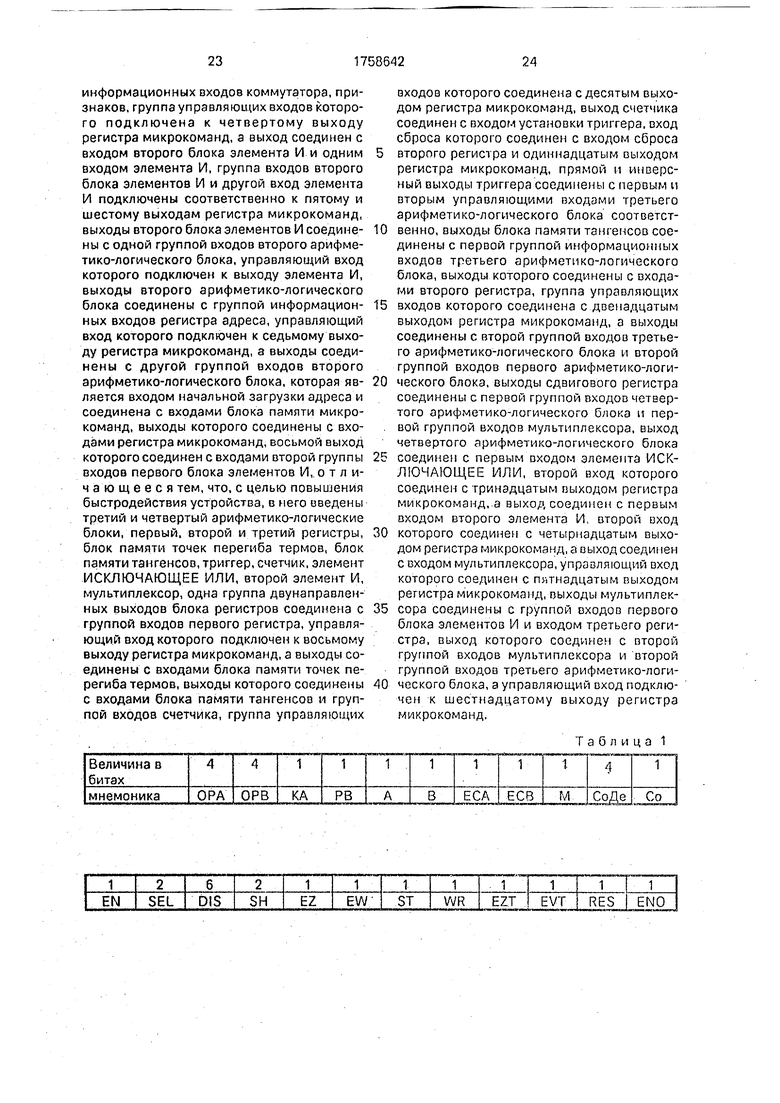

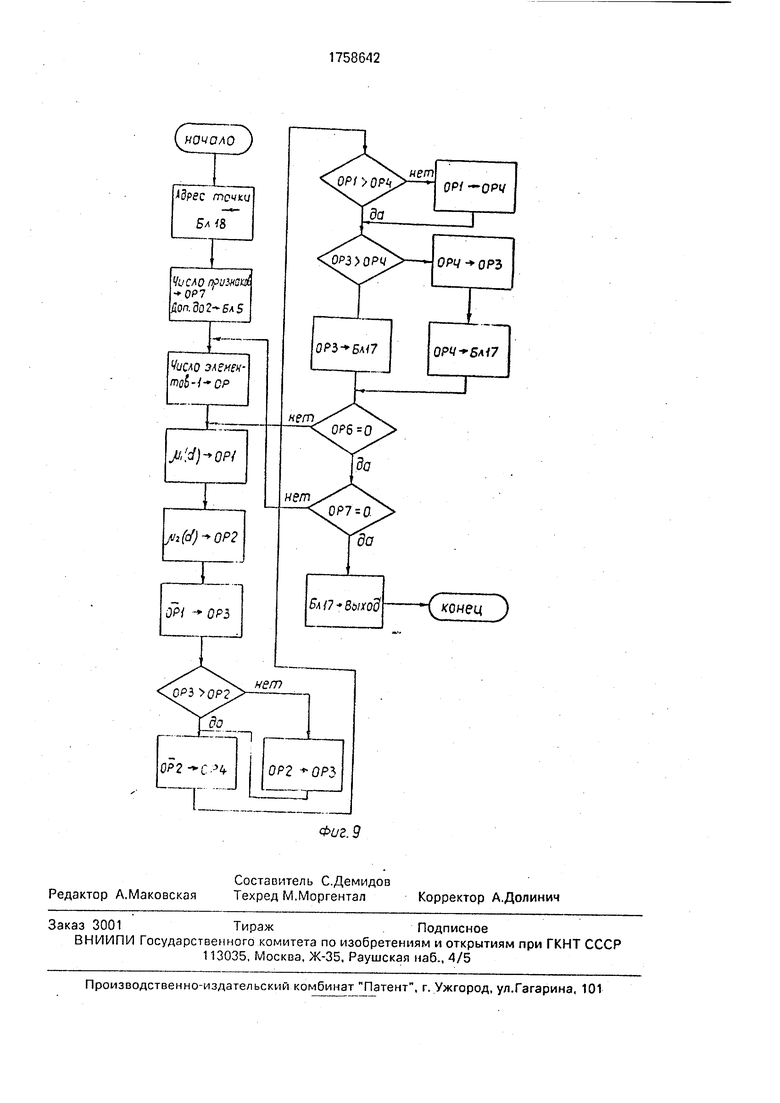

Ввиду сложности алгоритма проиллюстрируем работу устройства при выполнении операции расплывчатое равенстоо. Алгоритм операции приведен на фиг. 9.

(Работу алгоритма поясняет таблица 1).

1. Записать в регистр 18 адрес первой точки перегиба терма. Сброс триггера 22, и регистра 24.

I.Записать число признаков эталонной ситуации в ОР 7. Выполнить на АЛУ 2 операцию донесения до 2 и результат записать в регистр 5.

3.Запись число элементов терма в ОР б. Записать величину точки перегиба в счетчик 20. Записать значение регистра 5 п регистр 17. Это необходимо для выполнения первой операции выбора минимального из двух значений соседних операций. В случае выбора максимального из двух значений в предыдущем такте на выходе АЛУ 2 устанавливаются нули соответствующей командой. Запись всех единиц в регистр 17можетбыть также выполнена переводом выходов мультиплексора 16 в состояние высокого выходного сопротивления и записью в регистр 17.

4.Запись о ОР 1 и ОР 2 значений элементов терма со входа устройства и с выхода регистра 24.

5.Выполнить на АЛУ 2 операцию инверсии А и результат записать в ОР 3.

6.Выполнить на АЛУ 2 операцию вычитания SVB. Значение признака d записать в регистр признаков.

7.По значению признака либо переписать ОР 2 в ОР 3, либо перейти к следующему пункту.

8.Выполнить на АЛУ операцию А под ОР 2, результат записать в ОР 4.

9.Выполнить на АЛУ 2 операцию SVBOP 4 и ОР 1. Значение признака С записать в регистр признаков.

10.По значению признака либо ОР 1 переписать в ОР 4, либо перейти к следующему пункту.

I1.Выполнить на АЛУ 2 операцию SVB над регистрами ОР 3 и ОР 4. Значение признака записать в регистр признаков.

12.По значению признака С4 записать в регистр 17 либо ОР 3 либо ОР 4.

13.Считать ОР 6 и выполнить на АЛУ 2 операцию А-1. Перейти к формированию другой точки терм.

14.Если ОР 6 не равен нулю, перейти к п. 4. Записать новое значение точки эталонного терма в регистр 24.

15.Считать ОР 7 и выполнить на АЛУ 2 операцию А-1. Записать значение точки перегиба второго терма в регистр 18. Сбросить триггер 22 и регистр 24.

16.Если перебраны не все признаки, то перейти к п. 3.

17.Выдать информацию из регистра 17 через мультиплексор 16 на выходную шину

через группу элементов И 6. При этом установлен управляющий сигнал OVT. Мультиплексор 16 будет осуществлять на этот раз выдачу канала В, в чем можно убедиться, проанализировав управляющие сигналы.

0 Таким образом, заявляемой устройство, благодаря схеме формирования терма, позволяет формировать профиль эталонного терма параллельно с выполнением операции. Это позволяет передавать только адрес

5 одной точки, а не 128 точек каждого терма. Как известно, снижение быстродействия процессоров в основном связано с необходимостью обращения к внешней памяти, что включает арбитраж и цикл чтения/записи.

0 Предложенное устройство позволяет исключить это. и следовательно, повысить быстродействие. Кроме того, схема взятия максимума/минимума позволяет выполнить эти операции (что необходимо в ситуа5 ционном управлении) также параллельно с выполнением команды. В прототипе на эту операцию требуется 4 микрокоманды: сравнение, анализ признака, чтение, запись. Таким образом, за счет снижения коли0 чества микрокоманд, составляющих команду эквивалентность в операции нечеткое равенство, быстродействие устройства в среднем повышается на 22%.

Формула изобретения

5 Устройство для обработки нечеткой информации, содержащее блок регистров, одна группа двунаправленных выходов которого является входом устройства и соединена с первой группой входов первого

0 арифметико-логического блока, первой группой входов первого блока элементов И, выходы которого являются выходами устройства, другая группа двунаправленных выходов блока регистров соединена с вто5 рой группой входов первого арифметико-логического блока, одна группа выходов которого соединена с группой информационных входов сдвигового регистра, группа управляющих входов которого подключена

0 к первому выходу регистра микрокоманд, группа управляющих входов блока регистров подключена к второму выходу регистра микрокоманд, группа управляющих входов первого арифметико-логического блока под5 ключена к третьему выходу регистра микрокоманд, другая группа выходов и выход переноса первого арифметико-логического блока соединены с соответствующими информационными входами регистра призна- ков, выходы которого соединены с группой

информационных входов коммутатора, признаков, группа управляющих входов которого подключена к четвертому выходу регистра микрокоманд, а выход соединен с входом второго блока элемента И и одним входом элемента И, группа входов второго блока элементов И и другой вход элемента И подключены соответственно к пятому и шестому выходам регистра микрокоманд, выходы второго блока элементов И соедине- ны с одной группой входов второго арифметико-логического блока, управляющий вход которого подключен к выходу элемента И, выходы второго арифметико-логического блока соединены с группой информацион- ных входов регистра адреса, управляющий вход которого подключен к седьмому выходу регистра микрокоманд, а выходы соединены с другой группой входов второго арифметико-логического блока, которая яв- ляется входом начальной загрузки адреса и соединена с входами блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд, восьмой выход которого соединен с входами второй группы входов первого блока элементов И, о т л и- чающееся тем, что. с целью повышения быстродействия устройства, в него введены третий и четвертый арифметико-логические блоки, первый, второй и третий регистры, блок памяти точек перегиба термов, блок памяти тангенсов, триггер, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй элемент И, мультиплексор, одна группа двунаправленных выходов блока регистров соединена с группой входов первого регистра, управляющий вход которого подключен к восьмому выходу регистра микрокоманд, а выходы соединены с входами блока памяти точек перегиба термов, выходы которого соединены с входами блока памяти тангенсов и группой входов счетчика, группа управляющих

входов которого соединена с десятым выходом регистра микрокоманд, выход счетчика соединен с входом установки триггера, вход сброса которого соединен с входом сброса второго регистра и одиннадцатым выходом регистра микрокоманд, прямой и инверсный выходы триггера соединены с первым и вторым управляющими входами третьего арифметико-логического блока соответственно, выходы блока памяти тангенсов соединены с первой группой информационных входов третьего арифметико-логического блока, выходы которого соединены с входами второго регистра, группа управляющих входов которого соединена с двенадцатым выходом регистра микрокоманд, а выходы соединены с второй группой входов третьего арифметико-логического блока и второй группой входов первого арифметико-логического блока, выходы сдвигового регистра соединены с первой группой входов четвертого арифметико-логического блока и первой группой входов мультиплексора, выход четвертого арифметико-логического блока соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с тринадцатым выходом регистра микрокоманд, а выход соединен с первым входом второго элемента И, второй вход которого соединен с четырнадцатым выходом регистра микрокоманд, а выход соединен с сходом мультиплексора, управляющий вход которого соединен с пятнадцатым выходом регистра микрокоманд, выходы мультиплексора соединены с группой входов первого блока элементов И и входом третьего регистра, выход которого соединен с второй группой входов мультиплексора и второй группой входов третьего арифметико-логического блока, а управляющий вход подключен к шестнадцатому выходу регистра микрокоманд.

Таблица 1

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Микропрограммное вычислительное устройство | 1984 |

|

SU1229761A1 |

| ПРОЦЕССОР ДЛЯ РЕАЛИЗАЦИИ ОПЕРАЦИЙ НАД ЭЛЕМЕНТАМИ НЕЧЕТКИХ МНОЖЕСТВ | 1991 |

|

RU2012037C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1993 |

|

RU2040038C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ | 1994 |

|

RU2079877C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

Устройство для обработки нечеткой информации относится к вычислительной технике, предназначено для использования в информационно-советующих системах оперативного управления. Целью изобретения является повышение быстродействия устройства. Устройство содержит блок 1 регистров, АЛУ 2, регистр 3 признаков, коммутатор 4 признаков, сдвиговый регистр 5, блок 6 элементов И, блок 7 элементов И, АЛУ 8, регистр 9 адреса, блок 10 микрокоманд, регистр 11 микрокоманд, элемент И 12, АЛУ 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, элемент И 15, мультиплексор 16, регистр 17, второй регистр 18. блок 19 памяти точек перегиба термов, счетчик 20, блок 21 памяти тангенсов, триггер 22, АЛУ 23, третий регистр 2Д. Устройство позволяет с повысить быстродействие при выполне- нии операций над элементами термов в t/ процессе управления сложным объектом. -- 9 ил. хL.

Вход

12

Ш

Фиг.1

Таблица 3

Ґ

t Г t)

§

tn

Ј

Ш6л2

j7 ftt УБ1БЛ2

t ocs

S

1:3 «51

iTiWiTl-т г

1 i t I I I I I НГ h t

fca

fNi

3

5

ТМИ1

a

«V

«

P)

- I

л

SS S

Ј

tn

RS «э о о еэ э ° Јэ -5 o. «n « « л - о

з«

§«

- -XI

tnfi

&

S1 Ј

fi

d

i

JrrB

Ј« s

Ca

X§

СЛ

CO

a x ю

нГ

fi

i r-T

r r m.

s-h

з i

О

c-

4

i

5

s«

:

1

ВО

01

иг

оз

АО A3

обш

W1

W

ш

fl

Од...

и

От.

0/7

и

V W

ДО

A3

W

вз к

W

ш

W W

уг

YJ

мтгм

aStOiSaS

оворгвлб armetf

f«tf

вв

20

D7

азш

Bv

сЛл (

В/г 17

SO

га

4

QJDS6

07

27

Ь

fr

ш

SJ 05

I «S

if if if 0

5

t

%

s s

ъч:

v

J ej oe Vu

rt

a

&

kj «л tj

$Й$С& 3

S

S

§

1

I Q

25

53 tS

«

iJS 3

«

4

I

У

5E5

s

I

5§

«a

v/

§

i

«jtae

l

4-

« «5

Ј$

X JL

Ґ

Ј

S

I

§3

«ae

S

ъ

s s

fc

3

4j - кч

%

S

Ol

5

-.

« с

Ol

Ј и

с

Фиг.7

KXO Вл7, ХОБЛ12

ЗбйВЗБлИ

07ШБЛП

SI S2

S.0

4- «

cc n i-c

п

to -. to «v J

JS3.S

1

конец )

| Устройство для выполнения операций над расплывчатыми операндами | 1986 |

|

SU1451677A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки нечеткой информации | 1988 |

|

SU1545214A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| А.И.Мелихов, Л.С.Берштейн Типергра- фы в автоматизации проектирования дискретных устройств, Ростов, РГУ, 1981 | |||

| ж | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-08-30—Публикация

1990-10-16—Подача