Изобретение относится к измерительной технике, а также может быть использовано в радиотехнике для измерения фазы зашумленного сигнала.

Известен измеритель сдвига фаз с ортогональной обработкой сигнала, содержащий два перемножителя, фазовращатель, два интегратора и узел вычисления [1].

Недостатком его является невозможность вычисления фазы чаще одного раза за период.

Ближайшим техническим решением, выбранным в качестве прототипа, является радиоимупльсное устройство измерения разности фаз, содержащее два перемножителя, два фильтра, генератор, два аналого-цифровых преобразователя и цифровой вычислитель общего назначения [2].

Недостатком его является невозможность вычисления фазы чаще одного раза за период.

Целью изобретения является увеличение быстродействия.

Поставленная цель достигается тем, что в устройство измерения разности фаз, содержащее опорный генератор, первый и второй интеграторы и вычислительный блок, причем первый и второй выходы опорного генератора соединены соответственно с первыми входами интеграторов, вторые входы которых объединены, дополнительно введены инвертор, коммутатор, делитель частоты, формирователь импульсов, блок вычитания и блок суммирования, причем вход инвертора является входом устройства в целом и соединен с первым входом коммутатора, второй вход которого подключен к выходу инвертора, входы формирователя импульсов и делителя частоты соединены с первым выходом опорного генератора, а выход делителя частоты подключен к третьему входу коммутатора, выход которого соединен со вторыми входами интеграторов, выход формирователя импульсов подключен к третьим входам интеграторов и первому входу вычислительного блока, второй и третий входы которого соединены с выходами блока суммирования и блока вычитания соответственно, выход первого интегратора подключен к первому входу блока суммирования и второму входу блока вычитания, выход второго интегратора соединен с первым входом блока вычитания и вторым входом блока суммирования.

Сравнение предлагаемого технического решения с прототипом и аналогами не позволило выявить в них совокупность признаков, отличающую предлагаемое решение от прототипа, что позволяет сделать вывод о соответствии критерию "существенные отличия".

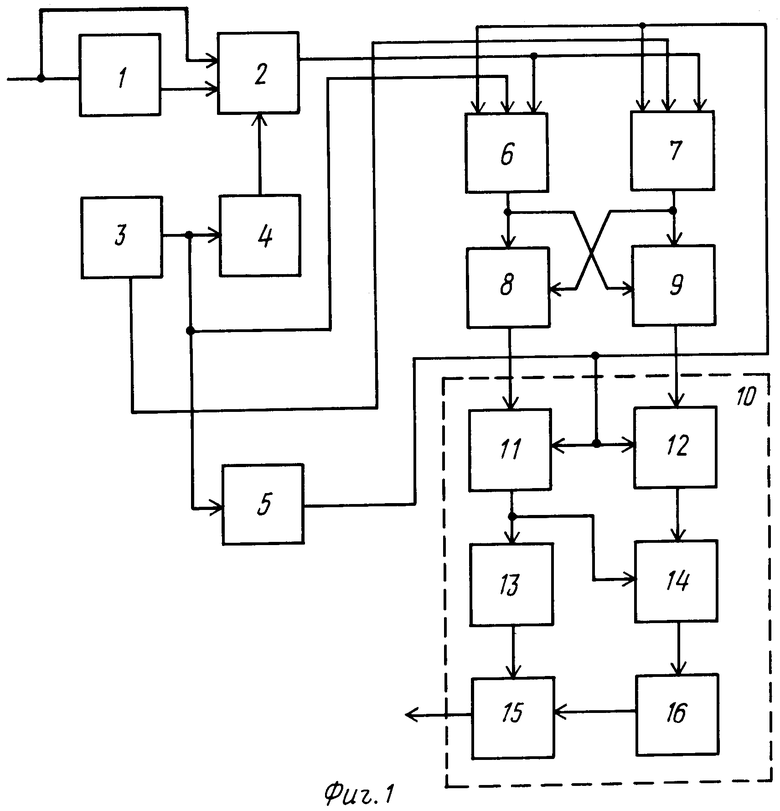

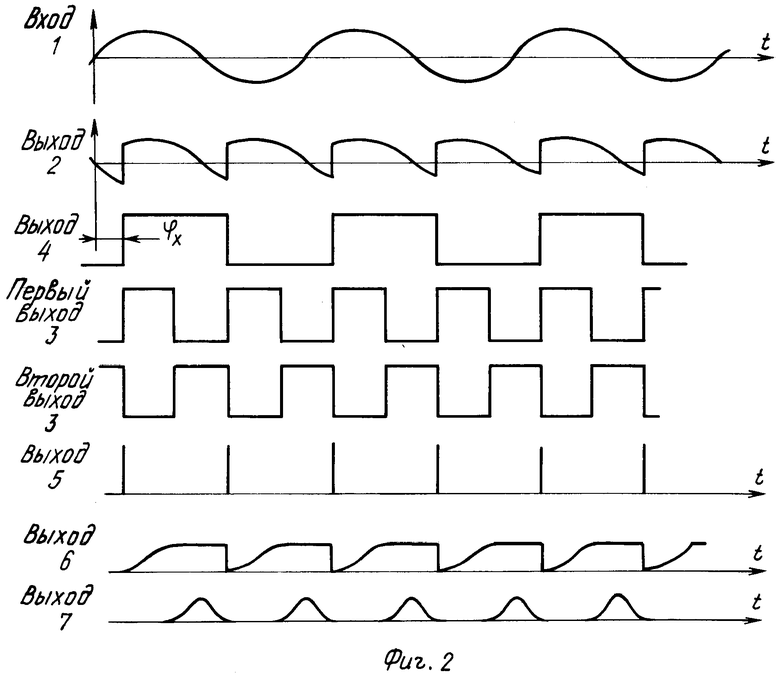

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - эпюры, поясняющие ее работу.

Устройство измерения разности фаз содержит инвертор 1, коммутатор 2, опорный генератор 3, делитель 4 частоты, формирователь 5 импульсов, первый интегратор 6, второй интегратор 7, блок в суммирования, блок 9 вычитания, вычислительный блок 10, состоящий из первого блока 11 памяти, второго блока 12 памяти, первого функционального преобразователя 13, блока 14 вычисления частного, сумматора 15, второго функционального преобразователя 16. При этом первый и второй выходы опорного генератора 3 соединены соответственно с первыми входами интеграторов 6 и 7, вторые входы которых объединены и подключены к выходу коммутатора 2, вход инвертора 1 является входом устройства в целом и соединен с первым входом коммутатора 2, второй вход которого подключен к выходу инвертора 1, входы формирователя 5 импульсов и делителя 4 частоты соединены с первым выходом опорного генератора 3, выход делителя 4 частоты подключен к третьему входу коммутатора 2, выход формирователя 5 импульсов подключен к третьим входам интеграторов 6 и 7, а также к первому входу вычислительного блока 10, второй и третий входы которого соединены с выходами блока 8 суммирования и блока 9 вычитания соответственно, выход первого интегратора 6 подключен к первому входу блока 8 суммирования и второму входу блока 9 вычитания, выход второго интегратора 7 соединен с первым входом блока 9 вычитания и вторым входом блока 8 суммирования, первый вход первого блока 11 памяти является вторым входом вычислительного блока 10, первый вход второго блока 12 памяти является третьим входом вычислительного блока 10, вторые входы блоков 11 и 12 памяти объединены и являются первым входом вычислительного блока 10, вход первого функционального преобразователя 13 соединен с выходом первого блока 11 памяти, первый вход блока 14 вычисления частотного соединен с выходом второго блока 12 памяти, второй вход блока 14 вычисления частного соединен с выходом первого блока 11 памяти, вход второго функционального преобразователя 16 соединен с выходом блока 14 вычисления частного, первый и второй входы сумматора 15 подключены к выходам первого и второго функциональных преобразователей 13 и 16 соответственно.

Устройство работает следующим образом.

Входной сигнал, описываемый формулой Uвх = Uo sin(ωt + ϕx), поступает на интеграторы 6 и 7 либо без изменений, либо пройдя через инвертор. Измеряемой разностью фаз является фаза ϕx между фазой входного колебания и фазой колебания на выходе делителя 4 частоты на два (фиг.2). Сигналы с выхода опорного генератора 3 задают интервалы интегрирования для интеграторов 6 и 7. Интегратор 6 за первую четверть периода вычисляет величину а

a=  uвхdt=

uвхdt=  (cosϕx+sinϕx), а за третью четверть периода величину с

(cosϕx+sinϕx), а за третью четверть периода величину с

c=  (-uвх)dt=

(-uвх)dt=  (cosϕx+sinϕx)

(cosϕx+sinϕx)

Интегратор 7 работает во время второй и четвертой четверти периода и соответственно вычисляет величины b и d

b=  uвхdt=

uвхdt=  (cosϕx-sinϕx)

(cosϕx-sinϕx)

D=  (-uвх)dt=

(-uвх)dt=  (cosϕx-sinϕx)

(cosϕx-sinϕx)

Сигналы с интеграторов 6 и 7 подаются на блок 8 суммирования и блок 9 вычитания, которые два раза за период вычисляют величины ζ и η соответственно

η=a-b=c-d=  sinϕx

sinϕx

ζ=a+b=c+d=  cosϕx

cosϕx

Формирователь 5 импульсов формирует дважды за период короткие импульсы (фиг. 2), по переднему фронту которых информация с блока 8 суммирования и блока 9 вычитания заносится в блоки памяти 11 и 12 соответственно. По заднему фронту этих импульсов происходит обнуление интеграторов 6 и 7.

Неизвестная фаза ϕx полностью определяется величинами ζ и η и может быть вычислена по формуле

ϕx=arctg +

+  (1+sgn(-ζ))

(1+sgn(-ζ))

Вычисления по данной формуле производятся в вычислительном блоке 10. Первый функциональный преобразователь 13 реализует функцию f1(x)=  (1+sgn(-x)), а второй функциональный преобразователь 16 - функцию f2(x) = arctg x.

(1+sgn(-x)), а второй функциональный преобразователь 16 - функцию f2(x) = arctg x.

Преимуществом предлагаемого устройства является возможность произвести быстрое измерение фазы сигнала в шумах при относительно простой реализации устройства, при этом результат не зависит от амплитуды входного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| ЦИФРОВОЙ ФАЗОМЕТР | 2002 |

|

RU2207579C1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Устройство для квазикогерентного приема фазоманипулированных сигналов | 1984 |

|

SU1239885A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

| Функциональный генератор | 1983 |

|

SU1141427A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1989 |

|

SU1713103A1 |

Изобретение относится к измерительной технике и позволяет повысить быстродействие измерения разности фаз при зашумленном входном сигнале. Сущность изобретения: устройство содержит инвертор, коммутатор, опорный генератор, делитель, два интегратора, формирователь импульсов, блоки суммирования и вычитания, вычислительный блок. 1 з.п. ф-лы, 2 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США N 3602812, кл | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

Авторы

Даты

1994-08-15—Публикация

1988-07-06—Подача