ел

Од

о

05

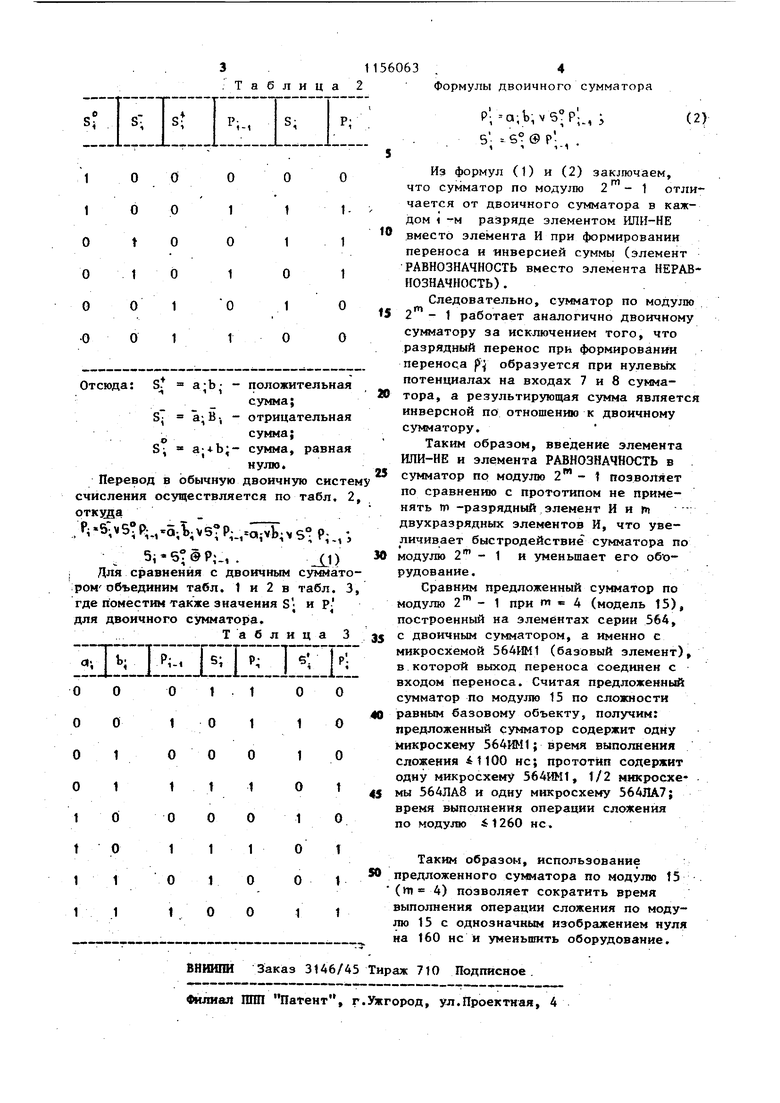

со рГзобретеиие относится к вычислительной технике и может быть использовано в устройствах обнаружения и исправ;гения ошибок корректирую1цими кодами. Известен комбинационный двоичный сумматор, содержащий в каждом разряде элементы И и ИЛИ fl} . Недостаток такого сумматора его низкое быстродействие при сложеНИИ чисел по модулю 2-1. Наиболее близким техническим решением к изобретению является сумматор по модулю 2 - 1, содержащий т одноразрядных сумматоров с целью циклического переноса, каждый из которых содержит два элемента НЕРАВНОЗНАЧНОСТЬ, два элемента И и элемент ИЛИ, аходы которого соединены с выходами элементов И, входы первых элементов И и НЕРАВНОЗНАЧНОСТЬ являются входами сумматора, а входы вторых элементов И и НЕРАВНОЗНАЧНОСТЬ соединены с выходами первого элемента НЕРАВНОЗНАЧНОСТЬ и с входом переноса из предыдущего разряда сумматора. Кроме того, сумматор содержит 1Т1 разрядный элeмeнt И и m двухраз-рядных элементов И, причем входы Т1-разрядного элемента И соединены L выходами вторых элементов НЕРАВНОЗНАЧНОСТЬ всех одноразрядных сумматоров, а его выход - с первыми входами двухразрядных элементов И, Вторые входы которых соединены с выходами элементов НЕРАВНОЗНАЧНОСТЬ соответственно 2J . Недостаток известного сумматора его малое быстродействие и относительная СЛОЖНОСТЬ . Целью изобретения является повышение быстродействия и упрощение сумматорв. Поставленная цель достигается тем что сумматор по модулю 1, содер жащий в каждом разряде элемент НЕРАВ НОЗНАЧНОСТЬ, элемент И и элемент ИЛИ один из входов которого подключен к выходу элемента И, один из входов которого соединен с выходом элемента НЕРАВНОЗНАЧНОСТЬ, а другой является входом переноса из предыдущего разря да сумматора, входы элемента НЕРАВНО ЗНАЧНОСТЬ являются входами соответствующего разряда сую атора, а выход элемента ИЛИ является выходом переноса в последующий разряд сумматора, содержит в каждом разряде элемент 1 32 ЙЛИ-НЕ и элемент РАВНОЗНАЧНОСТЬ, причем входы элемента ШТИ-НЕ соединены с соответствующими входами элемента НЕРАВНОЗНАЧНОСТЬ, а его выход соединен с другим входом элемента ИЛИ, входы элемента РАВНОЗНАЧНОСТЬ соединены соответственно с выходом элемента НЕРАВНОЗНАЧНОСТЬ и другим входом элемента И, а его выход является выходом соответствующего разряда сумматора. На чертеже изображена блок-схема предложенного сумматора. Сумматор по модулю 2 - 1 содержит W одноразрядных сумматоров , каждый из которых содержит элемент НЕРАВНОЗНАЧНОСТЬ 2, элемент ИЛИ-МЕ 3, элемент И 4, элемент ИЛИ 5, элемент РАВНОЗНАЧНОСТЬ 6. Выходы 7, и 8,-8 элементов НЕРАВНОЗНАЧНОСТЬ 2 и ИЛИ-НЕ 3 являются входами соответствующего разряда сумматора. Выход элемента ИЛИ 5 является выходом переноса соответствующего разряда сумматора, а выходы 9|-9j,Bcex элементов РАВНОЗНАЧНОСТЬ 6 являются выходами сумматора по модулю 2 - 1. Сумматор по модулю 2-1 работает следующим образом. Заменим сложение по модулю 1 входных аргументов А и В вычитанием: где В - порязрядная инверсия В . Представим теперь вычитаемое (-8) в отрицательной двоичной системе счисления. Тогда сложение аргумента А с .аргументом (-В) осуществляется, без переноса. Например, сложим числа 101 и В 110 по модулю 7. Инверсия & : В 001 -В 001 Сложим А + (-§): 101 Действительно, fSfely Однако в общем случае результат может получиться в двоичной избытрчг ной системе счисления с 1, О, 1, Таблица сложения в каждом разряде представлена в табл. 1. Т а б л и - ...:: bZrZlJ. 0т 1о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для алгебраического сложения в избыточной двоичной системе счисления | 1981 |

|

SU1003073A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1977 |

|

SU696450A1 |

| Устройство для умножения по модулю М=2 @ -1 | 1986 |

|

SU1383339A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2+1 | 1992 |

|

RU2018929C1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Устройство для сложения чисел в избыточной системе счисления | 1978 |

|

SU763896A1 |

СУММАТОР ПО МОДУЛЮ 2 - 1, содержащий в.каждом разряде элемент НЕРАВНОЗНАЧНОСТЬ, элемент И и элемент ИЛИ, один из входов которого подключен к выходу элемента И, один из входов которого соединен с выходом элемента НЕРАВНОЗНАЧНОСТЬ, а другой является входом переноса из f S .: ... ,.-,,-.,,.,,J предыдущего разряда сумматора, входы элемента НЕРАВНОЗНАЧНОСТЬ являются входами соответствующего разряда сумматора, а выход элемента ИЛИ является выходом переноса в последующий разряд сумматора, отличающийся тем, что, с целью повышения быстродействия и упрощения сумматора, он содержит в каждом разряде элемент ИЛ11-НЕ и элемент РАВНОЗНАЧНОСТЬ, причем входы элемента ИЛИ-НЕ соединены с соответствующими входами элемента НЕРАВНОЗНАЧНОСТЬ, его выход соединен с другим входом элемента ИЛИ, входы элемента РАВНОЗНАЧНОСТЬ соединены соответственно с выходом элемента НЕРАВНОЗНАЧНОСТЬ (Л и другим входом элемента И, а его выход является выходом соответствую.щего разряда сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Комбинационный сумматор | 1979 |

|

SU800992A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Савельев А.Я | |||

| Арифметические и логические основы цифровых автоматов | |||

| М., Высшая школа, 1980, с | |||

| Схема обмотки ротора для пуска в ход индукционного двигателя без помощи реостата, с применением принципа противосоединения обмоток при трогании двигателя с места | 1922 |

|

SU122A1 |

Авторы

Даты

1985-05-15—Публикация

1984-01-19—Подача