Изобретение относится к вычислительной технике, а именно к устройствам, организующим процедуры обмена персональной ЭВМ с внешними объектами по шине SCS1, такими как НМД, НМЛ, АЦПУ и др., а также может быть использовано для построения локальных сетей ЭВМ.

Известно устройство для сопряжения системной и локальной магистралей, содержащее операционный блок, блок групповой пересылки, блок управления доступом к магистралям, арбитр локальной магистрали, блок сопряжения с системной магистралью, блок сопряжения с локальной магистралью, дешифратор, адресные регистры [1].

Недостатком известного устройства является его сложность.

Наиболее близким к заявленному техническим решением является контроллер обмена NCR 5386 SCS1 [2], содержащий блок прямого доступа к памяти, компаратор адресов, блок управления записью и чтением, блок прерывания, первый буфер данных, регистр прерываний, блок задания собственного адреса и паритета, регистр команд, регистр состояния, дешифратор команд, узел фиксации флага состояния, счетчик байтов, узел фиксации обнуления счетчика, блок регистров данных, регистр номера внешнего устройства, узел фиксации занятости шины, местный блок синхронизации, блок контроля паритета, блок контроля фазы, блок синхронизации шины, блок управления обменом, блок выбора фазы, второй буфер данных, блок управления внешними усилителями.

Недостатком известного устройства является то, что оно требует при своем подключении дополнительных элементов, выполненных на микросхемах малой степени интеграции.

Изобретение решает задачу упрощения построения платы устройства за счет внесения элементов, осуществляющих арбитраж внутрь микросхемы устройства, что позволяет разделить шины данных и арбитража. Кроме того, введение регистра диагностики и режима общего аппаратного сброса упрощает диагностику устройства.

Указанный технический результат достигается тем, что в устройство, содержащее блок прямого доступа к памяти, селектор адресов, блок управления записью и чтением, блок прерывания, первый и второй буферы данных, регистр прерываний, блок задания собственного адреса и паритета, регистр команд, регистр состояний , дешифратор команд, узел фиксации флага состояния, счетчик байтов, узел фиксации обнуления счетчика, блок регистров данных, регистр номера внешнего объекта, узел фиксации занятости шины, местный блок синхронизации, блок контроля паритета, блок контроля фазы, блок синхронизации шины, блок управления обменом, блок выбора фазы, блок управления внешними усилителями, причем выход и первый вход блока прямого доступа к памяти, группа входов блока управления записью и чтением, выход блока прерывания, группа входов компаратора адресов подключены к соответствующим управляющим и адресным шинам ЭВМ, первая группа входов-выходов первого буфера данных подключена к шине данных ЭВМ, а вторая группа входов-выходов соединена с входами-выходами данных регистра прерываний, блока задания собственного адреса и паритета, регистра команд, счетчика байтов, регистра состояний, первыми входами-выходами данных блока регистра данных и регистра номера внешнего объекта, информационные входы блока задания собственного адреса и паритета соединены с соответствующими управляющими шинами ЭВМ, а управляющие входы - соответственно с выходами селектора адресов и выходом записи блока управления записью и чтением, выход селектора адресов соединен с управляющими входами регистра команд, регистра прерываний, счетчика байтов, блока регистров данных, регистра номера внешнего объекта, выход записи блока управления записью и чтением соединен с входами записи регистра команд, счетчика байтов, регистра состояний, блока регистров данных, а выход чтения - с входами чтения регистра команд, регистра прерываний, регистра состояний, регистра номера внешнего объекта, блока регистров данных, второй вход-выход данных которого соединен с входом-выходом данных блока контроля паритета, вторым входом-выходом данных регистра номера внешнего объекта и первым входом-выходом данных второго буфера данных, второй вход-выход данных и вход-выход идентификации которого соединены соответственно с шиной данных и шиной управления внешних объектов, выходы и входы-выходы управления внешними объектами блока управления внешними усилителями, блока синхронизации шины, блока управления обменом данными, блока выбора фазы соединены с соответствующими управляющими входами и входами-выходами внешних объектов, выход узла фиксации флага состояния соединен с входами блока управления внешними усилителями, блока выбора фазы, первыми входами местного блока синхронизации и дешифратора команд, второй вход которого соединен с выходом регистра команд, а выход - с вторым входом местного блока синхронизации и первым синхровходом блока синхронизации шины, второй синхровход которого соединен с первым выходом местного блока синхронизации и синхровходами блока управления обменом данными и второго буфера данных, первый и второй выходы состояния блока синхронизации шины непосредственно и через узел фиксации занятости шины соединены с первым и вторым выходами узла фиксации флага состояния, соединенным также с входом соответствующего разряда регистра состояний, входы остальных разрядов которого соединены соответственно с выходами узла фиксации обнуления счетчика, блока контроля паритета, блока контроля фазы и первым выходом регистра прерывания, второй выход и первый вход которого соединены соответственно с входом блока прерывания и выходом регистра состояний, второй вход блока прямого доступа к памяти соединен с вторым выходом местного блока синхронизации, третий вход которого соединен с выходом счетчика байтов, соединенным также с входом узла фиксации обнуления счетчика и входом данных регистра команд, выход блока задания собственного адреса и паритета соединен с контрольными входами блока контроля паритета и второго буфера данных, выход блока управления обменом данными - с входом управления счетчика байтов, выход блока контроля паритета - с вторым контрольным входом второго буфера данных, выход блока выбора фазы - с входом блока контроля фазы, введены регистр диагностики, арбитражный блок, первый и второй входы которого соединены соответственно с выходом блока задания собственного адреса и паритета и первым выходом местного блока синхронизации, а группа выходов соединена с шиной арбитража внешних объектов, причем выход общего сброса блока синхронизации шины соединен с входами соответствующих разрядов регистра прерываний и регистра состояний, синхронизации, группа выходов регистра собственного номера соединена с группой входов буфера арбитражной шины, группа выходов которого является группой выходов блока, группа входов-выходов данных, управляющий вход и вход чтения регистра диагностики соединены соответственно с второй группой входов-выходов первого буфера данных, с выходом селектора адресов, выходом чтения блока управления записью и чтением, при этом арбитражный блок содержит регистр собственного номера и буфер арбитражной шины, входы которых являются соответственно первым и вторым входами блока, группа выходов регистра собственного номера соединена с группой входов буфера арбитражной шины, группа выходов которого является группой выходов блока.

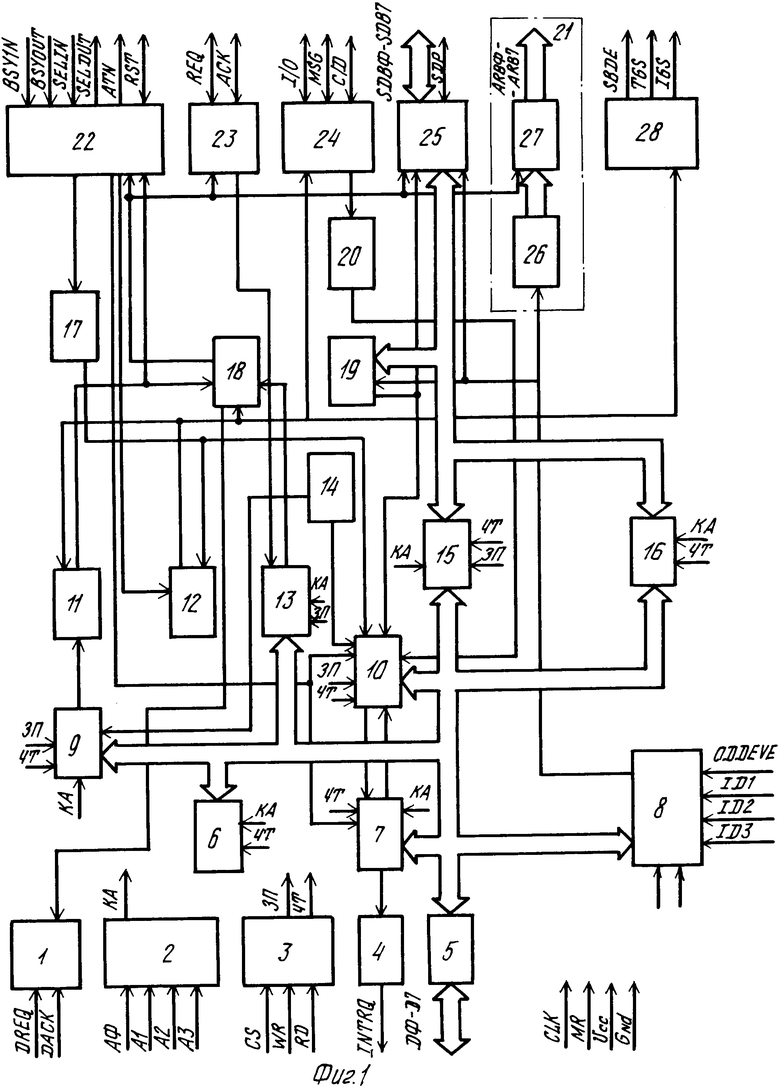

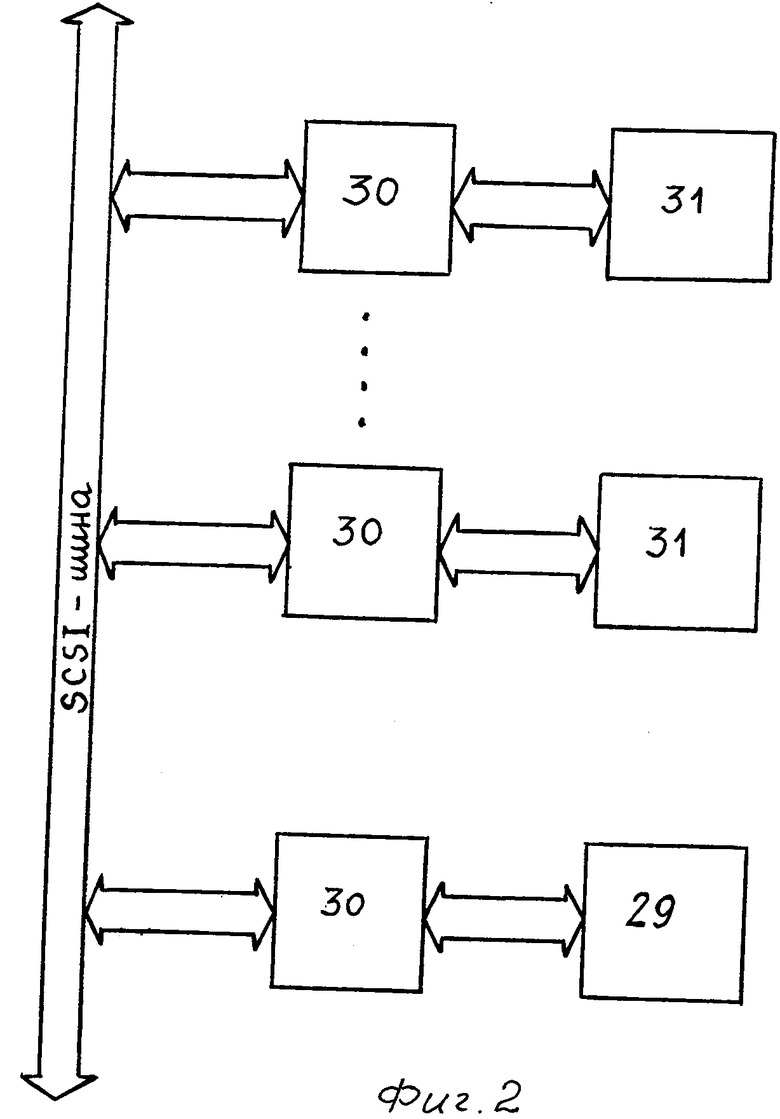

На фиг. 1 изображена схема устройства; на фиг. 2 - схема вычислительного комплекса, в котором применяется устройство.

Устройство содержит (фиг. 1) блок 1 прямого доступа к памяти, селектор 2 адресов, блок 3 управления записью и чтением, блок 4 прерывания, первый буфер 5 данных, регистр 6 диагностики, регистр 7 прерываний, блок 8 задания собственного адреса и паритета, регистр 9 команд, регистр 10 состояний, дешифратор 11 команд, узел 12 фиксации флага состояния, счетчик 13 байтов, узел 14 фиксации обнуления счетчика, блок 15 регистров данных, регистр 16 номера внешнего объекта, узел 17 фиксации занятости шины, местный блок 18 синхронизации, блок 19 контроля паритета, блок 20 контроля фазы, арбитражный блок 21, блок 22 синхронизации шины, блок 23 управления обменом, блок 24 выбора фазы, второй буфер 25 данных, регистр 26 собственного номера, буфер 27 арбитражной шины, блок 28 управления внешними усилителями.

Вычислительный комплекс (фиг. 2) содержит персональную ЭВМ 29, устройства 30 сопряжения, внешние объекты 31.

Все блоки устройства выполнены стандартными. Новые связи регистра 7 прерываний и регистра 10 состояний обеспечены тем, что в них использованы дополнительные разряды. Регистр 7 прерываний представляет собой восьмиразрядный регистр, доступный только на чтение, который совместно с регистром 10 состояний используется процессором для определения причины возникшего прерывания. По окончании чтения регистра 7 прерываний его биты, отображающие причину прерывания, автоматически сбрасываются. Регистр 10 состояний - это восьмиразрядный регистр, oдин из разрядов которого используется для контроля сигнала "Аппаратный сброс". Логическая "1" в этом разряде показывает, что на SCSI-шине установлен сигнал "Аппаратный сброс" всех подключенных к ней объектов. Если было прерывание по приходу сигнала "Аппаратный сброс", то по этому разряду отслеживается момент, когда его сняли. Регистр 6 диагностики - это восьмиразрядный регистр, доступный только на чтение. После включения питания он всегда содержит код 10000000 - "Самодиагностика успешно завершена".

Устройство выполняется в виде микросхемы и может работать в двух режимах: "ведущем и ведомом". Кроме того, устройство поддерживает арбитраж SCSI-шины (включая реселекцию) и может работать управляющим процессором в режиме прямого доступа к памяти (ПДП). В работе устройства определены следующие фазы.

Первая фаза "шина свободна" показывает, что никакое устройство не подключено к шине, не использует ее и она доступна для любого из них. Эта фаза характеризуется одновременным отсутствием сигналов BSY и SEL на соответствующих входах блока 22 в течение заданного промежутка времени, который необходим для успокоения сигналов в кабеле.

Вторая фаза "арбитраж шины" позволяет одному внешнему объекту захватить управление SCSI-шиной так, чтобы оно могло выполнять функцию "ведущего" или "ведомого". Микросхема устройства поддерживает арбитраж шины, поэтому она может использоваться для построения систем с несколькими "ведущими". Процедура арбитража шины SCSI осуществляется следующим образом. После фазы "шина свободна" устройство ждет некоторое время, затем выставляет одновременно на входе данных буфера 25 свой номер и сигнал BSY на вход блока 22. После ожидания заданного интервала времени внешний объект проверяет состояние шины данных. Если более приоритетный объект выставил свой номер, то устройство должно сбросить сигнал BSY и свой номер и вернуться к первой фазе. Если устройство имеет самый высокий приоритет, то оно устанавливает сигнал SEL на входе блока 22.

Третья фаза "селекция" позволяет выбрать "ведомого" с целью выполнения им определенной функции (например, чтения или записи). Во время фазы "селекция" сигнал I/O на входе блока 24 должен быть сброшен, чтобы отличить ее от фазы "реселекция". Процедура селекции выполняется следующим образом. Внешний объект, выигравший арбитраж, определяет себя в качестве "ведущего" тем, что не устанавливает сигнал I/O на выходе блока 24. Затем "ведущий" устанавливает на входе-выходе данных буфера 25 свой собственный номер и номер выбранного "ведомого", объединяя их по ИЛИ. После установки всех этих сигналов на шине "ведущий" снимает свой сигнал BSY на выходе блока 22 и затем переходит в режим ожидания сигнала BSY от выбранного "ведомого". "Ведомый" определяет, что его пытается вызвать "ведущий" по комбинации сигналов SEL и своего номера на шине данных. После этого "ведомый" запоминает номер "ведущего" и устанавливает свой сигнал BSY. Получив сигнал BSY на входе блока 22, "ведущий" снимает свой сигнал SEL и номера "ведомого" и свой собственный, чем завершается фаза "селекция".

Четвертая фаза "реселекция" выполняется аналогично фазе "селекция" за исключением того, что "ведущий" и "ведомый" меняются местами и "ведомый" при этом устанавливает сигнал I/O на выходе блока 24. Таким образом, после операций селекции и реселекции сигнал BSY всегда устанавливает "ведомый". Блок 19 контроля паритета не позволяет установить ответные сигналы при ошибке паритета.

После установления связи между "ведущим" и "ведомым" выполняется фаза "обмен информацией". К данной фазе относятся команды приема и передачи команд, данных и сообщений. Данные команды завершаются прерыванием и допускаются только для микросхемы, находящейся в режиме "ведомого". В данных командах могут использоваться модификаторы, определяющие режим ПДП и "передача одиночного байта".

Перед загрузкой кода команды в регистр 9 команд должен быть загружен счетчик 13 байтов, за исключением режима "передача одиночного байта". После загрузки команды в регистр 9 в устройстве сбрасываются флаги, сигнализирующие о том, что регистры данных блока 15 заполнены и он переходит в режим ожидания поступления данных от SCSI-шины и от процессора соответственно в режимах приема и передачи.

После определения информационной фазы устройство производит обмен данными между процессором и шиной SCSI. Если в коде команды определен флаг ПДП, то обмен происходит без обращения к блоку 15 регистров при помощи сигналов DREQ и DACK блока 1. В противном случае обмен происходит через блок 15 регистров данных. После завершения приема (передачи) данных устройство вырабатывает сигнал прерывания, устанавливая соответствующие разряды в регистрах 7 и 10, после чего остается в состоянии "ведомого", занимая шину. Если значение счетчика 13 равно нулю, то, значит, успешно переданы все байты и узел 14 формирует сигнал на своем выходе, который поступает в соответствующий разряд регистра 10 состояний. Если в регистре состояний был установлен бит "Parity Enable", то при обмене данными устройство выполняет контроль паритета. При обнаружении ошибки паритета вырабатывается прерывание и в регистре 7 прерываний устанавливается флаг "завершение операции", а в регистре 10 состояний - флаг "ошибка паритета". Счетчик 13 байтов показывает количество непереданных (не принятых) байтов, включая и ошибочный. Если во время обмена данными "ведущий" установил сигнал ATN на выходе блока 22, то в регистре 7 прерываний установлен разряд "обслуживание шины". Процедуры обмена данными могут быть остановлены до завершения путем загрузки в регистр 9 команд команды "пауза". В этом случае "ведомый" завершает прием (передачу) текущего байта и останавливает свою работу, сохраняя значение счетчика байтов и состояние сигналов I/O, C/D, MSG. После этого можно использовать команду разрыва связи с "ведущим" или повторно загрузить прерванную команду, не меняя значения счетчика 13 байтов для ее продолжения.

Команда "Transfer Info" является командой обмена для контроллера, находящегося в режиме "ведущего", она также завершается прерыванием. Эта команда подается только в ответ на прерывание по "обслуживанию шины". По получении прерывания, но до выдачи команды процессор должен проанализировать состояние сигналов I/O, C/D, MSG в регистре 10 состояний, чтобы определить фазу SCSI-шины и направление передачи, а также загрузить счетчик 13 байтов. В дальнейшем обмен происходит аналогично предыдущему. Завершение обмена и выдача прерывания происходят в следующих случаях.

Устройство передало (приняло) заданное счетчиком 13 количество байтов.

"Ведомый" изменил фазу (сигналы I/O, C/D, MSG), что фиксируется блоком 24, до обнуления счетчика 13.

"Ведомый" освободил SCSI-шину и сбросил сигнал BSY, после чего устройство переходит в состояние "отсоединено".

Был принят последний байт данных в фазе "Message In". В этом случае в регистре 7 прерываний установлен разряд "завершение операции" и сигнал ACK остается установленным по окончании команды. Это дает возможность процессору выдать сигнал ATN для передачи ответного сообщения "ведомому". После этого для снятия сигнала АСК необходимо выдать команду "сообщение принято". Обнаруженная ошибка паритета не может служить причиной завершения команды и выдачи прерывания. Для этого устройство должно дождаться одного из вышеописанных случаев. Если команду необходимо срочно завершить, что можно использовать команду "сброс" или "разъединение". Эти команды переводят "ведущее" устройство в состояние "отсоединено", а связанный с ним "ведомый" остается на шине. Поэтому, если необходимо остановить работу и "ведомого", то надо использовать команду "сброс" SCSI-шины", устанавливая сигнал на входе-выходе блока 22, с выхода которого он поступает в соответствующие разряды регистра 7 прерываний и регистра 10 состояний "ведомого" устройства, что останавливает его работу, освобождая при этом SCSI-шину. Сброс сигнала RSТ происходит после записи в регистр 9 команд устройства любой другой команды.

Арбитражный блок 21 введен для разделения шины арбитража и шины данных, что позволяет устройству одновременно выдавать собственный адрес и "прослушивать" шину данных, чтобы определить "победителя".

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТРОЛЛЕР ОБМЕНА | 1993 |

|

RU2032214C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| СИСТЕМА ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1994 |

|

RU2103744C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство обработки информации с переменной длиной команд | 1990 |

|

SU1817099A1 |

| АРХИТЕКТУРА ПРОЦЕССОРА ВВОДА-ВЫВОДА, КОТОРЫЙ ОБЪЕДИНЯЕТ МОСТ МЕЖСОЕДИНЕНИЯ ПЕРВИЧНЫХ КОМПОНЕНТ | 1996 |

|

RU2157000C2 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

Изобретение относится к вычислительной технике, а именно к устройствам, организующим процедуры обмена персональной ЭВМ с внешними объектами по шине S CS1, такими как НМД, НМЛ, АЦПУ и др., а также может быть использовано для построения локальных сетей ЭВМ. Целью изобретения является упрощение устройства и его диагностики. Устройство содержит блок ПДП, селектор адресов, блок управления записью и чтением, блок прерывания, первый и второй буферы данных, регистр диагностики, блок задания собственного адреса и паритета, регистра команд, узел фиксации флага состояния, счетчик байтов, узел фиксации обнуления счетчика, блок регистров данных, регистр номера внешнего объекта, узел фиксации занятости шины, местный блок синхронизации, блок контроля паритета, блок контроля фазы, блок синхронизации шины, блок управления обменом, блок выбора фазы, блок синхронизации шины, блок управления внешними усилителями и арбитражный блок. 1 з.п. ф-лы, 2 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для направления движений охлаждающей среды в реактивных катушках, трансформаторах и т.п. Устройствах | 1926 |

|

SU5386A1 |

Авторы

Даты

1994-08-30—Публикация

1993-02-11—Подача