которого соединены с выходами первого счетчика и входами первой груп пы блока индикации, входы второй группы которого являются входами устройства и соединены с входами первой группы блока сравнения, входы второй группы которого соединены с входами третьей группы блока индикации и выходами второго регист ра сдвига, информационный вход которого подключен к неинвертирующему выходу второго Г -триггера, ин1160414

вертирующий выход которого соединен

-i с вторым входом второго элемента И, третьим входом соединенного с выходом второго коммутатора, информационные входы которого подключены к выходам первого регистра сдвига, входы установки в О первого и второго D -триггеров подключены соответственно к выходам шестого и пятого элементов И, а входы элемента ИЛИ соединены с выходом триггера сбоя и выходами первого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для ввода информации | 1986 |

|

SU1377863A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее блок сравнения, блок индикации, первый счетчик, первый регистр сдвига, элемент ИЛИ и блок управления, содержащий генератор импульсов, формирователь импульсов, второй счетчик, дешифратор и первьм элемент И, выход генератора импульсов соединен с частотным, входом формирователя импульсов, первый выход которого соединен с первым входом первого элемента И и вгодом второго счетчика, быход которого подключен к входам дешифратора, один выход которого соединен с вторым входом первого элемента И,; выход элгмента ИЛИ соединен с входом управления формирователя импульсов, выходы группы первого счетчика являются выходами устройства, тактовый вход первого регистра сдвига соединен с вторым выходом формирователя импульсов, выход первого элемента И подключен к счетному входу первого счетчика, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в него введены блок памяти, второй регистр сдвига. первый и второй коммутаторы, второй и третий элементы И, первый и второй D-триггеры , триггер сбоя, а блок управления содержит четвертый, пятый, и шестой элементы И, один выход дешифратора и второй выход формирователя импульсов подключены к соответствующим входам четвертого элемента И, первьй выход формирователя импульсов соединен с первыми входами пятого и шестого элементов И, другие выходы дешифратора соответственно соединены с вторыми входами пятого и шестого элементов И, информационный вход триггера сбоя соединен с выходом блока сравнения,а управляющий вход подключен к выходу (Л четвертого элемента И, выходы второго счетчика соединены с упра,вляющими входами первого и второго коммутаторов и адресными входами блока памяти, выход которого соединен с информационными входами первого и второго D-триггеров, управляющие входы которых соединены с выходами О5 соответственно третьего и второго, элементов И, первые входы которых о соединены с вторым выходом формиро4 вателя импульсов и тактовым входом второго регистра сдвига, управляющий вход которого и управляющий вход первого регистра сдвига соединены соответственно с другими выходами дешифратора, информационный вход первого регистра сдвига подключен к неинвертирующему выходу первого D-триггера, инвертирующим выходом соединенного с вторым входом первого элемента И, третий вход которого подключен к выходу первого коммутатора, информационные входы

. Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматической проверки функционирования программируемых логических элементов.

Целью изобретения является повышение быстродействия устройства.

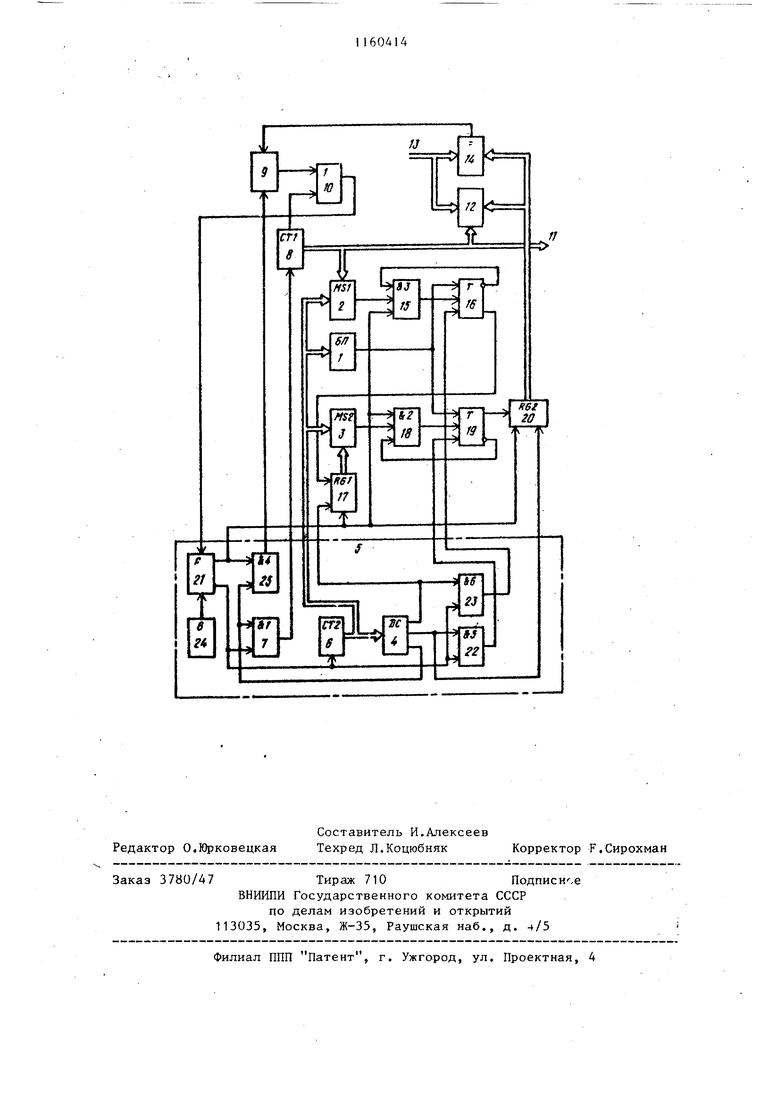

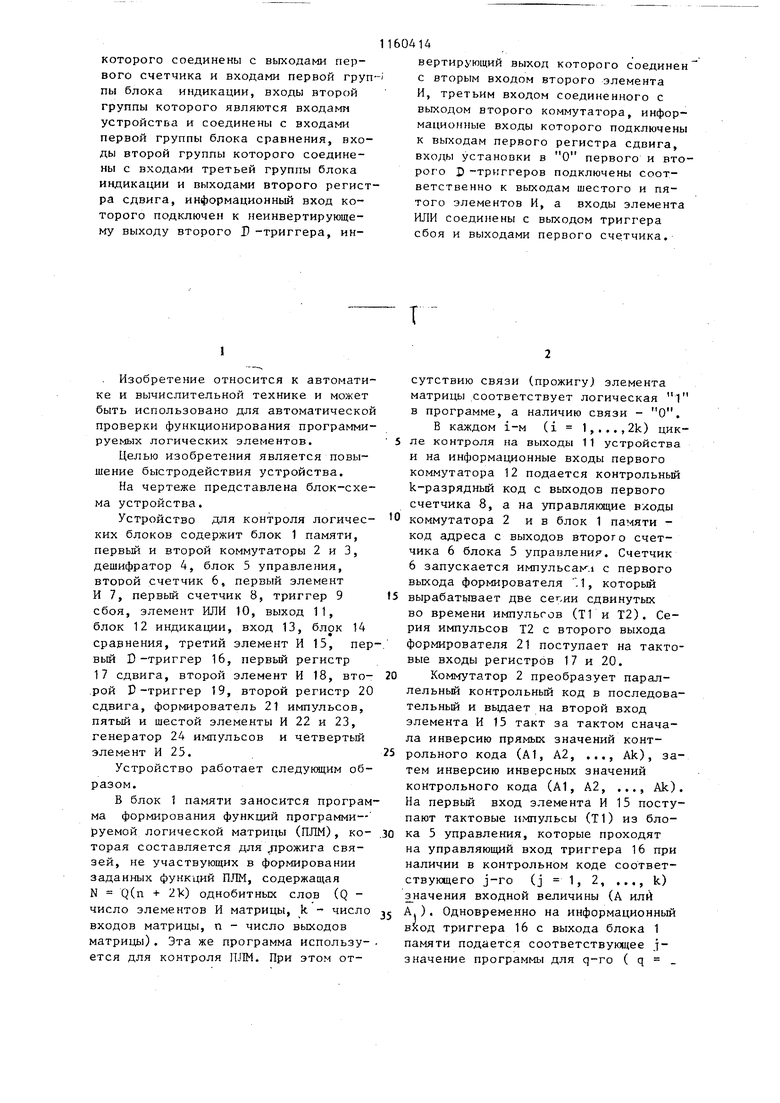

На чертеже представлена блок-схема устройства.

Устройство для контроля логических блоков содержит блок 1 памяти, первый и второй коммутаторы 2 и 3, дешифратор 4, блок 5 управления, второй счетчик 6, первый элемент И 7, первьй счетчик 8, триггер 9 сбоя, элемент ИЛИ 10, выход 11, блок 12 индикации, вход 13, блок 14 сравнения, третий элемент И 15, первьй D -триггер 16, первый регистр 17 сдвига, второй элемент И 18, второй Р-триггер 19, второй регистр 20 сдвига, формирователь 21 импульсов, пятый и шестой элементы И 22 и 23, генератор 24 импульсов и четвертый элемент И 25.

Устройство работает следующим образом.

В блок 1 памяти заносится программа формирования функций программи- руемой логической матрицы (ПЛМ), которая составляется для .прожига связей, не участвующих в формировании заданных функций ПЛМ, содержащая N Q(n + 21) однобитных слов (Q число элементов И матрицы, k - число входов матрицы, п - число выходов матрицы). Эта же программа используется для контроля ПЛМ. При этом отсутствию связи (прожигу) элемента матрицы соответствует логическая 1 в программе, а наличию связи - О. В каждом i-M (i 1,...,2k) цикле контроля на выходы 11 устройства

и на информационные входы первого коммутатора 12 подается контрольный k-разрядный код с выходов первого счетчика 8, а на управлякяцие входы О коммутатора 2 ив блок 1 памяти код адреса с выходов второго счетчика 6 блока 5 управления. Счетчик 6 запускается импульсаг л с первого выхода формирователя -1, которьй

5 вырабатывает две сег.ии сдвинутых

во времени импульсов (Т1 и Т2). Серия импульсов Т2 с второго выхода формирователя 21 поступает на тактовые входы регистров 17 и 20. 0 Коммутатор 2 преобразует параллельный контрольный код в последовательный и выдает на второй вход элемента И 15 такт за тактом сначала инверсию прямых значений контрольного кода (А1, А2, ..., Ak), затем инверсию инверсных значений контрольного кода (А1, А2, ..., Ak). На первьш вход элемента И 15 поступают тактовые импульсы (Т1) из блока 5 управления, которые проходят на управляющий вход триггера 16 при наличии в контрольном коде соответствующего j-ro (j 1, 2, ,.., k) з начения входной величины (А или

5 А. ). Одновременно на информационный вход триггера 16 с выхода блока 1 памяти подается соответствующее jзначение программы для q-ro ( q

3П

1, 2, ..., Q) элемента ПЛМ. Если в программе записано, что данное значение контртльного кода (А: или А.) входит в логическое выражение для функции FQ(п), но отсутствует в i-контрольном коде, то D -триггер 16 перебрасывается в единичное соетояние, запирает вход элемента И 15 и остается в этом состоянии до конца q-ro этапа контроля, т.е. единичное состояние D-триггера 16 соответствует нулевому значению функции при данном i-м контрольном коде. Триггер 16 перебрасывается в единичное состояние при наличии единиц на втором входе элемента И 1 и на информационном входе триггера 16, что соответствует отсутствию в контрольном коде значения одного из входных сигналов.

По окончании q-ro этапа контроля (через 2k тактов) с третьего выхода дешифратора 4 блока 5 управления подается управляющий сигнал (V3) в регистр 17 сдвига и по заднему фрон ту импульса сдвига (Т2) в регистр записывается информация с выхода триггера 16 (О или 1). Затем с выхода шестого элемента И 23 блока управления на вход установки О триггера 16 поступает импульс сброса (СБР1 V3T1) и перебрасывает триггер 16 в нулевое состояние.

Коммутатор 3, элемент И 18, триггер 19 и регистр 20 образуют цепь фор1 1ирования эталонных выходных функций В (функции ИЛИ) ПЛМ аналогично функций И коммутатором 2, элементом И 15, триггером 16 и регистром 17. Если одна из функций, входящих в выходную функцию В (или), равна единице, то триггер 19 перебрасывается в единичное состояние.

Коммутаторы 2 и 3 управляются кодом ад.реса, которьй также подается в блок 1 памяти для считывания со- ответствующегб значения программы работы (прожига) ПЛМ.

14-4

По окончании (Q + п)-го этапа контроля в регистре 20 записаны п эталонных значений функций В при данном 1-м контрольном коде теста. С первого выхода дешифратора 4 поступает разрешающий потенциал (VI) на вход элемента И 7 блока 5 управления, с выхода которого импульс сравнения (Uop V 1 -Tl)поступает на управляю ций вход триггера 9 сбоя, на информационньв вход которого с выхода блока 14 сравнения подается результат сравнения эталонных значений выходов ШТМ (с выходов регистра 20) со значениями с входов 13 устройства (выходов контролируемой ПЛМ, на входы которой подается тот же i-й контрольный код теста, что и на входы коммутатора 2).

При несовпадении сравниваемых значений с выхода блока 14 сравнения единичный потенциал поступает в триггер 9 сбоя и тот перебрасывается в единичное состояние. При этом формирователь 21 блока 5 управления запирается потенциалом триггера 9 .сбоя и режим контроля останавливается в i-M цикле. Блок 12 индикации показывает значение i-контрольного кода, при котором происходит сбой (неверный прожиг одной из связей ПЛМ), а также значения выходов контролируемой ПЛМ и регистра 20 (эталонные значения).

При отсутствии сбоя режима конт роля по окончании 2-го цикла счетчик 8 через элемент ИЛИ 10 подает запирающий сигнал в блок 5 управления (конец контроля). Режим контроля закончен, ПЛМ прожжена в соответствии с программой.

Таким образом, предлагаемое устройство позволяет проводить оперативньй автоматический контроль программируемых логических блоков в соответствии с заданной программой с выявлением неисправностей отдельных элементов логического блока.

| Устройство для обнаружения неисправностей цифровых систем | 1973 |

|

SU561965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| 1979 |

|

SU826357A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-21—Подача