Изобретение относится к технике связи и вычислительной технике и может быть использовано при создании новой и модернизации существующей аппаратуры передачи данных.

Известно устройство для передачи и приема дискретной информации с адресным запросом ошибок, содержащее в прямом канале последовательно соединенные блок управления, источник информации, накопитель адресов искаженных комбинаций, выход и другой вход которого соединены соответственно с адресным входом и с управляющим входом накопителя, который соединен с вторым выходом блока управления, третий выход которого соединен с входом датчика служебных комбинаций, причем выход кодера и вход декодера являются соответственно входом прямого канала связи, а на приемной стороне - последовательно соединенные декодер, вход синхронизации которого соединен с выходом дешифратора служебных комбинаций, накопитель приема и потребитель информации, а также последовательно соединенные накопитель адресов принимаемых комбинаций и кодер, причем контрольный выход декодера соединен с входом накопителя адресов принимаемых комбинаций, причем вход дешифратора служебных комбинаций и выход кодера являются соответственно выходом прямого канала связи и входом обратного канала связи.

Однако известное устройство обладает недостаточной помехоустойчивостью.

Цель изобретения - повышение помехоустойчивости.

Цель достигается тем, что в устройство для передачи и приема дискретной информации с селективным запросом ошибок, содержащее на передающей стороне последовательно соединенные блок управления, источник информации, накопитель и кодер, датчик служебных комбинаций, последовательно соединенные декодер и накопитель адресов искаженных комбинаций, выход и другой вход которого соединены соответственно с адресным входом и с управляющим входом накопителя, который соединен с вторым выходом блока управления, третий выход которого соединен с входом датчика служебных комбинаций, причем выход кодера и вход декодера являются соответственно входом прямого канала связи и выходом обратного канала связи, а на приемной стороне - последовательно соединенные декодер, вход синхронизации которого соединен с выходом дешифратора служебных комбинаций, накопитель приема и потребитель информации, а также последовательно соединенные накопитель адресов принимаемых комбинаций и кодер, причем контрольный выход декодера соединен с входом накопителя адресов принимаемых комбинаций, причем вход дешифратора служебных комбинаций и выход кодера являются соответственно выходом прямого канала связи и входом обратного канала связи, введены последовательно соединенные формирователь адресной маски и сумматор по модулю два, включенный между выходом кодера и входом прямого канала связи, причем адресный вход формирователя адресной маски соединен с выходом накопителя адресов искаженных комбинаций, выход датчика служебных комбинаций подключен к другому входу кодера, а вход синхронизации формирователя адресной маски является входом синхронизации устройства, а на приемной стороне сведены последовательно соединенные формирователь адресной маски и сумматор по модулю два, другой вход и выход которого соединены соответственно с входом дешифратора служебных комбинаций и с информационным входом декодера, а выход накопителя адресов принимаемых комбинаций соединен с адресным входом формирователя адресной маски, вход синхронизации которого является входом синхронизации устройства.

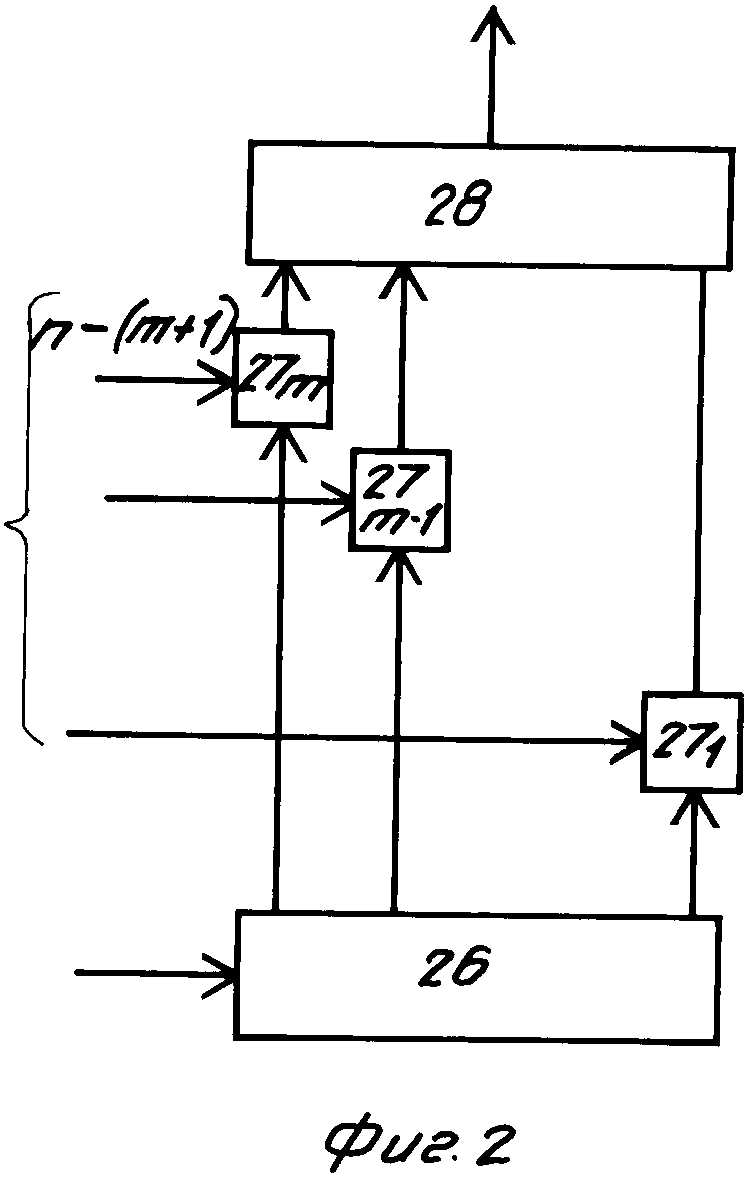

Кроме того, формирователи адресной маски на передающей и приемной сторонах выполнены идентично в виде m-разрядного регистра, вход записи которого является адресным входом формирователя адресной маски, а выходы разрядов m-разрядного регистра сдвига через соответствующие элементы И соединены с входами элемента ИЛИ, выход которого является выходом формирователя адресной маски, входом синхронизации которого являются вторые входы m элементов И.

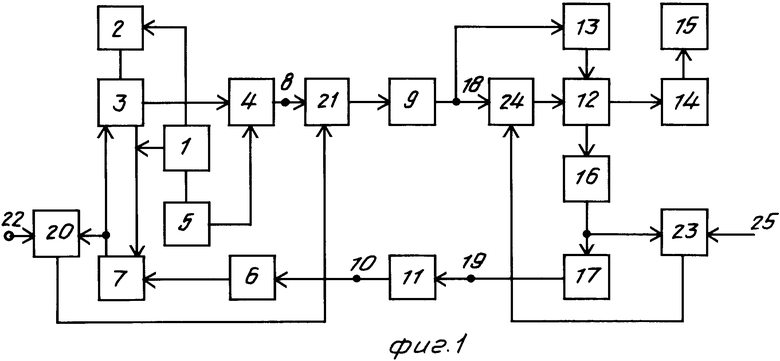

На фиг.1 представлена функциональная схема предложенного устройства; на фиг.2 - функциональная схема формирователя адресной маски.

Устройство для передачи и приема дискретной информации с селективным запросом ошибок содержит на передающей стороне последовательно соединенные блок 1 управления, источник 2 информации, накопитель 3 и кодер 4, датчик 5 служебных комбинаций, последовательно соединенные декодер 6 и накопитель 7 адресов искаженных комбинаций, выход и другой вход которого соединены соответственно с адресным входом и с управляющим входом накопителя, который соединен с вторым выходом блока 1 управления, третий выход которого соединен с входом датчика 5 служебных комбинаций, причем выход кодера 4 и вход декодера 6 являются соответственно входом 8 прямого канала 9 связи и выходом 10 обратного канала 11 связи, а на приемной стороне - последовательно соединенные декодер 12, вход синхронизации которого соединен с выходом дешифратора 13 служебных комбинаций, накопитель 14 приема и потребитель 15 информации, а также последовательно соединенные накопитель 16 адресов принимаемых комбинаций и кодер 17, причем контрольный выход декодера 12 соединен с входом накопителя 16 адресов принимаемых комбинаций, причем вход дешифратора 13 служебных комбинаций и выход кодера 17 являются соответственно выходом 18 прямого канала 9 связи и входом 19 обратного канала 11 связи. На передающей стороне устройство содержит последовательно соединенные формирователь 20 адресной маски и сумматор 21 по модулю два, включенный между выходом кодера 4 и входом 8 прямого канала 9 связи. Адресный вход формирователя 20 адресной маски соединен с выходом накопителя 7 адресов искаженных комбинаций, выход датчика 5 служебных комбинаций подключен к другому входу кодера 4, а вход синхронизации формирователя 20 адресной маски является входом 22 синхронизации устройства. На приемной стороне устройство содержит также последовательно соединенные формирователь 23 адресной маски и сумматор 24 по модулю два, другой вход и выход которого соединены соответственно с входом дешифратора 13 служебных комбинаций и с информационным входом декодера 12, а выход накопителя 16 адресов принимаемых комбинаций соединен с адресным входом формирователя 23 адресной маски, вход синхронизации которого является входом 25 синхронизации устройства. Формирователи 20 и 23 адресной маски на передающей и приемной сторонах выполнены идентично в виде m-разрядного сдвига, вход записи которого является адресным входом формирователя адресной маски, а выходы разрядов m-разрядного регистра через соответствующие элементы И 27 соединены с входами элемента ИЛИ 28, выход которого является выходом формирователя адресной маски, входом синхронизации которого являются вторые входы m элементов И.

Устройство работает следующим образом.

По запросу блока 1 управления источник 2 информации выдает в накопитель 3 блок информации, состоящей из mk-разрядных комбинаций. После заполнения накопителя 3 датчик 5 служебных комбинаций по команде блока 1 управления посылает через кодер 4 по прямому каналу 9 служебную комбинацию начала сообщений. После этого из накопителя 3 информация k-разрядными комбинациями вводится в кодер 4, где они дополняются nk-проверочными разрядами, и через сумматор 21 по модулю 2 передается по прямому каналу 9. По получении комбинации начала сообщения дешифратором 13 служебных комбинаций приемная сторона входит в цикловую фазу, после чего приходящие затем из канала связи 9 через сумматор 24 по модулю два комбинации (n, k) линейного или циклического кода проверяются декодером 12 на наличие ошибок.

Информационные разряды кодовых комбинаций, в которых декодер 12 не обнаружил ошибок, записываются в регистры накопителя 14 приема, соответствующие порядковому номеру комбинации в данном блоке. Кодовые комбинации, в которых декодер 12 обнаружил ошибки, стираются в накопителе этого блока и в накопитель 14 приема не переписываются. В накопителе 16 адресов принимаемых комбинаций формируется m-разрядная комбинация адресов (номеров позиций) искаженных комбинаций, содержащая "единицы" в тех разрядах, которые соответствуют номерам позиций искаженных комбинаций в принимаемом блоке.

По окончании приема сообщения комбинация адресов искаженных комбинаций через кодер 17, обратный канал 11, декодер 6 поступает в накопитель 7 адресов искаженных комбинаций, а также запоминается формирователем 23 адресной маски. Принятая адресная комбинация записывается в формирователь 20 адресной маски и подается на адресный вход накопителя 3.

В этом режиме сумматор 21 по модулю два осуществляет поразрядное сложение по модулю два m младших (m ≅ n-k) проверочных разрядов повторно передаваемых комбинаций с принятой m-разрядной комбинацией адресов, последовательно выдаваемой формирователем 20 адресной маски. При этом адреса (номера позиций) повторяемых комбинаций могут не совпадать с их адресами при первоначальной передаче.

На приемной стороне после получения комбинации начала сообщения повторно передаваемые кодовые комбинации из прямого канала 9 связи поступают на сумматор 24 по модулю два, который осуществляет поразрядное сложение по модулю два m младших проверочных разрядов каждой из них с запрошенной m-разрядной комбинацией адресов, последовательно выдаваемой формирователем 23 адресной маски.

Очевидно, что если принятая по обратному каналу 11 связи комбинация адресов не совпадает с запрашиваемой, то декодер 12 повторно зафиксирует прием с ошибками всех повторяемых комбинаций. В накопителе 16 формируется идентичная комбинация запрашиваемых адресов, которая передается по обратному каналу 11 связи на передающую сторону, а также запоминается формирователем 23 адресной маски. Далее цикл переспроса повторяется.

Если же адресная маска формирователя 20 совпадает с адресной маской формирователя 23, то информационные части кодовых комбинаций, принятых без ошибок, записываются в соответствующие регистры накопителя 14 приема. Искаженные комбинации стираются в накопителе декодера 12, в накопителе 16 формируется новая комбинация адресов, которая передается по обратному каналу 11 связи на передающую сторону и, кроме того, запоминается формирователем 23 приемной стороны. Процесс переспроса повторяется до тех пор, пока не будет правильно принята последняя комбинация сообщения.

В этом случае принятый блок информации из накопителя 14 приема выдается потребителю 15 информации, в накопителе 16 адресов принимаемых комбинаций формируется нулевая адресная комбинация, которая передается по обратному каналу 11 связи и запоминается формирователем 23. На приемной стороне нулевая адресная часть запросной комбинации записывается в формирователь 20 и через адресный вход - в схему управления накопителя 3. Устройство переходит в исходное состояние и готово к передаче очередного блока информации.

Формирователь 20 (23) адресной маски содержит регистр 26 сдвига, вход записи которого является адресным входом формирователя, выходы 1,2,...,m-го разрядов регистра 26 через соответствующие элементы И 27 образуют m входов синхронизации.

Входы синхронизации формирователя 20 (23) подключены к соответствующим m входам распределителя передачи (приема), единичные сигналы на которых соответствуют моментам передачи (приема) m младших проверочных разрядов кодовых комбинаций.

В исходном состоянии в регистр 26 записана нулевая комбинация адресов и сигналы на выходе формирователя 20 (23) отсутствуют.

При обнаружении ошибок в регистр 26 заносится комбинация адресов, содержащая "единицы" в тех из m разрядов, номера которых соответствуют номерам искаженных комбинаций. Комбинация адресов, хранящаяся в регистре 26 весь цикл переспроса, образует адресную маску, которая по сигналам входа синхронизации в последовательном коде выдается на выход формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Комплекс декаметровой радиосвязи | 2020 |

|

RU2737763C1 |

| Способ передачи и приема дискретных сообщений в комплексе декаметровой радиосвязи | 2020 |

|

RU2743233C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ РЕЧЕВЫХ СООБЩЕНИЙ | 1994 |

|

RU2085044C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2090982C1 |

| СПОСОБ ПЕРЕДАЧИ СООБЩЕНИЙ В ПОЛУДУПЛЕКСНОМ КАНАЛЕ СВЯЗИ | 1996 |

|

RU2127953C1 |

| МНОГОЧАСТОТНЫЙ ПРИЕМНИК ДЕЛЬТА-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1993 |

|

RU2090981C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1996 |

|

RU2107995C1 |

Изобретение относится к технике связи и вычислительной технике и может быть использовано при создании новой и модернизации существующей аппаратуры передачи данных классической схемы систем с адресным повторением. Цель изобретения - повышение помехоустойчивости. Устройство для передачи и приема дискретной информации содержит блок управления, источник информации, накопитель, кодер, датчик служебных комбинаций, декодер, накопитель адресов искаженных комбинаций, канал связи, обратный канал связи, декодер, дешифратор служебных комбинаций, накопитель приема, потребитель информации, накопитель адресов принимаемых комбинаций, кодер, формирователь адресной маски, сумматор по модулю два, причем в состав формирователя адресной маски входят элемент И, элемент ИЛИ и регистр. 1 з.п. ф-лы, 2 ил.

| Шварцман Б.О | |||

| и Емельянов Г.А | |||

| Теория передачи дискретной информации | |||

| М.: Связь, 1979, с.362-368. |

Авторы

Даты

1994-08-30—Публикация

1991-03-18—Подача