Изобретение относится к вычислительной технике и может быть использовано для построения многомашинных и многопроцессорных вычислительных систем (ВС) с использованием памяти общего пользования.

Известно устройство для сопряжения вычислительных машин, содержащее блоки сопряжения, коммутаторы, блоки захвата шин диспетчера, информационные шины, шину диспетчера, блоки адаптеров абонентов, блоки служебных триггеров коммутатора [1].

Известное устройство сложно, имеет большое время и сложную процедуру доступа к данным.

Наиболее близким по технической сущности к предлагаемому является многоканальное устройство для обмена данными между модулями ВС, содержащее каналы (количество которых равно количеству модулей ВС), каждый из которых содержит четыре триггера, первый, третий и второй элементы НЕ, первый-четвертый, шестой, пятый, седьмой, восьмой элементы И, второй, первый и третий элементы ИЛИ, первый, третий, второй и четвертый элементы задержки, два формирователя импульсов, четыре элемента И-НЕ, два блока буферной памяти, четыре счетчика, две схемы сравнения, дешифратор, вход сигнала опроса канала, выход сигнала опроса канала, информационные вход и выход канала, выход сигнала разрешения запроса канала, выход сигнала прерывания канала, вход сигнала запроса канала, линию запроса устройства, шину запрета устройства, шину апробирования устройства, шину ответа устройства, шину адреса устройства, шину данных устройства [2].

Недостатками известного устройства являются большое время пересылки данных от одной ЭВМ к другой, ограниченные функциональные возможности из-за отсутствия циклического приоритета доступа для исключения столкновений, раздельный (по каналам ЭВМ) ресурс ЗУ, аппаратная избыточность, возможность монопольного захвата ресурса.

Целью изобретения является уменьшение времени обмена данными во всем диапазоне загрузки, расширение функциональных возможностей, минимизация аппаратной части, введение циклического изменения уровней приоритета ЭВМ при максимальной загрузке устройства.

Цель достигается тем, что в устройство обмена ВС, содержащее первый, второй и третий дешифраторы, входы которых соединены с соответствующими линиями соответственно первой, второй и третьей шин адреса, тринадцать элементов И, четыре элемента ИЛИ, ОЗУ, формирователь импульсов, три линии задержки и три триггера, введены ПЗУ, сумматор по модулю больше двух, счетчик, адресный коммутатор, двунаправленный коммутатор, первая, вторая и третья шины записи, первая, вторая и третья шины чтения, первая, вторая и третья шины готовности, первая, вторая и третья шины начала машинного цикла, первая, вторая и третья двунаправленные шины данных, причем первая, вторая и третья шины готовности соединены соответственно с третьим, четвертым и пятым выходами ПЗУ и первым, вторым и третьим входами сумматора по модулю больше двух, выход которого соединен со счетным входом счетчика, выходы нулевого и первого разрядов которого соединены соответственно с шестым и седьмым адресными входами ПЗУ, третий, четвертый и пятый адресные входы которого соединены соответственно с выходами первого, второго и третьего триггеров и прямыми входами первого и второго элементов И, третьего, четвертого элементов И и пятого, шестого элементов И, выход первого элемента И соединен с первыми входами первого элемента ИЛИ и седьмого элемента И, выход третьего элемента И соединен с первыми входами второго элемента ИЛИ и восьмого элемента И, выход пятого элемента И соединен с первыми входами третьего элемента ИЛИ и девятого элемента И, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, выход которого соединен с первым входом десятого элемента И, выход которого соединен с входом первой линии задержки, выход которой соединен с нулевым адресным входом ПЗУ, входами выборки первых информационных входов адресного коммутатора и первых информационных входов-выходов двунаправленного коммутатора и вторым входом седьмого элемента И, первый адресный вход которого соединен с выходом второй линии задержки, входами выборки вторых входов адресного коммутатора и двунаправленного коммутатора данных и вторым входом восьмого элемента И, вход которого соединен с выходом одиннадцатого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход шестого элемента И соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с первым входом двенадцатого элемента И, выход которого соединен с входом третьей линии задержки, выход которой соединен с вторым адресным входом ПЗУ, вторым входом девятого элемента И и третьими входами выборки третьих входов адресного коммутатора и входов-выходов двунаправленного коммутатора данных, выходы седьмого, восьмого и девятого элементов И соединены с соответствующими входами четвертого элемента И, выход которого соединен с входом направления коммутатора данных и входом формирователя импульсов, выход которого соединен с входом записи ОЗУ, вход разрешения которого соединен с шестым выходом ПЗУ, седьмой выход которого соединен с первым входом тринадцатого элемента И, второй вход которого соединен с выходом сумматора по модулю больше двух, первая, вторая и третья шины начала машинного цикла соединены соответственно с входами синхронизации первого, второго и третьего триггеров, информационные входы которых соединены с выходами соответственно первого, второго и третьего дешифраторов, первая, вторая и третья шины записи соединены с инверсными входами первого, третьего и пятого элементов И, первая, вторая и третья шины чтения соединены с инверсными входами соответственно второго, четвертого и шестого элементов И, первая, вторая и третья шины адреса соединены соответственно с первыми, вторыми и третьими информационными входами адресного коммутатора, информационные выходы которого соединены с соответствующими адресными входами ОЗУ, входы данных которого соединены с соответствующими разрядами первых, вторых и третьих информационных выходов коммутатора данных, первые, вторые и третьи информационные входы которого соединены с соответствующими разрядами информационных выходов ОЗУ, первая, вторая и третья двунаправленные шины данных соединены с соответствующими разрядами первых, вторых и третьих информационных входов-выходов двунаправленного коммутатора данных.

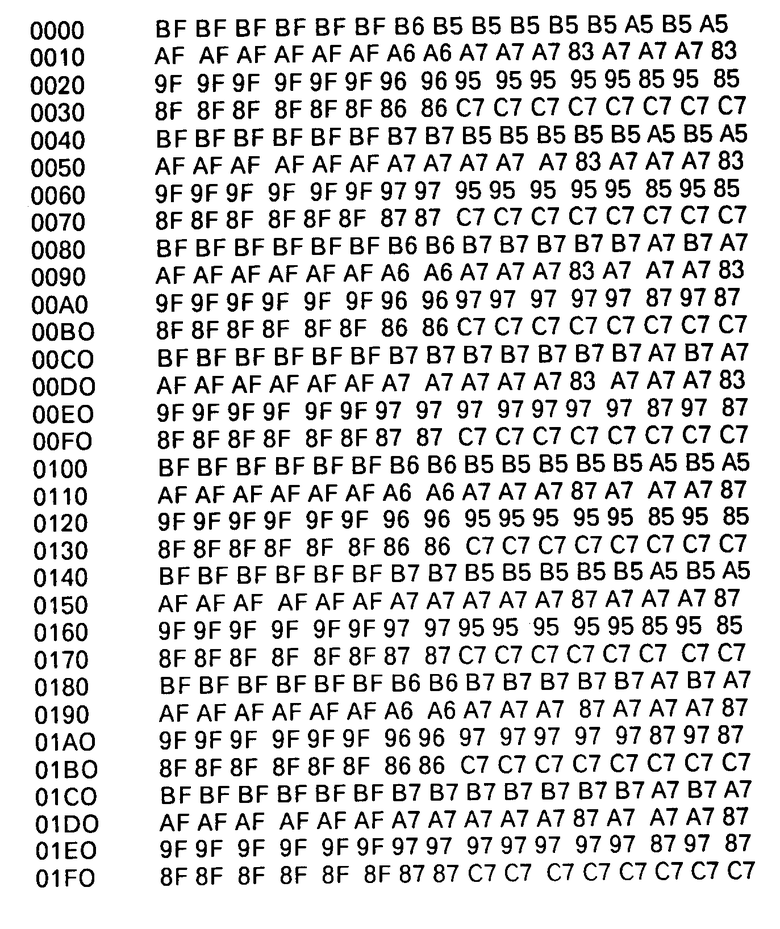

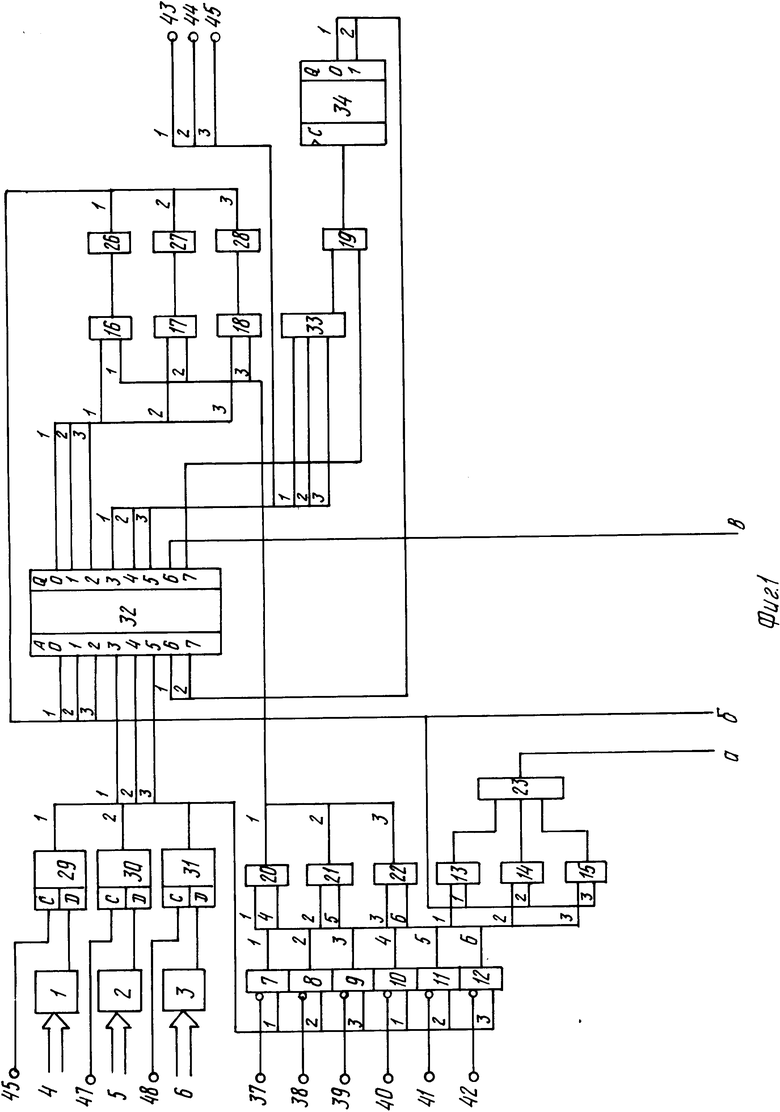

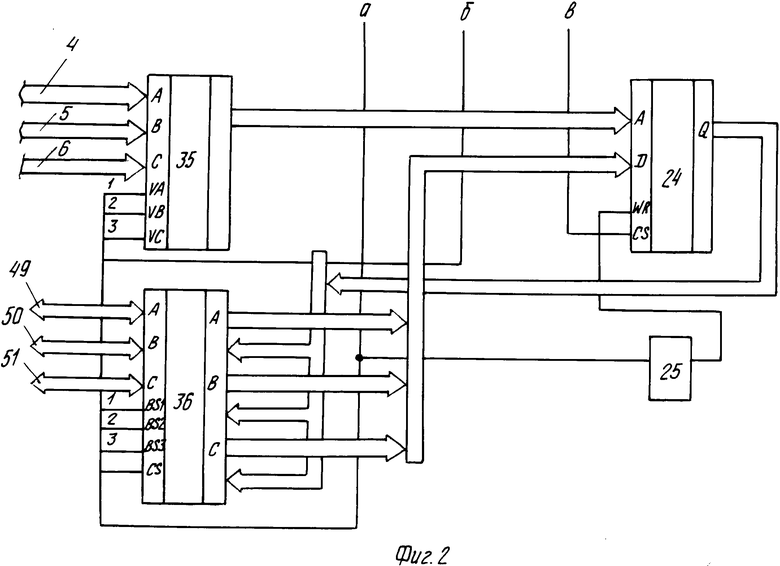

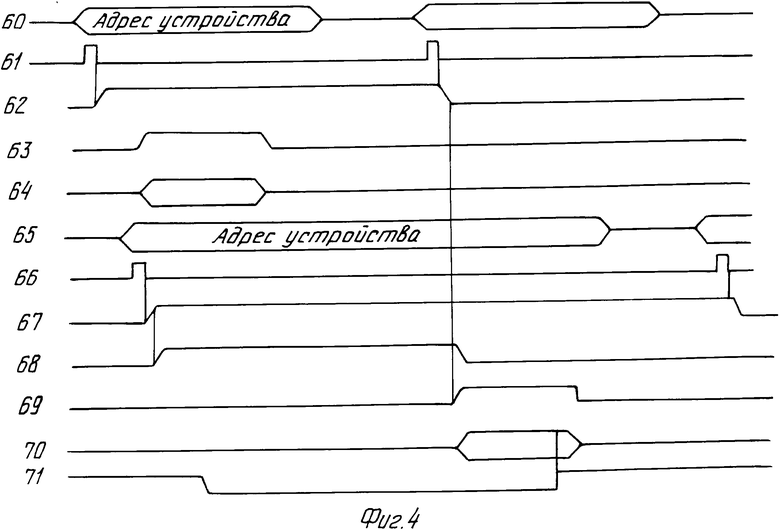

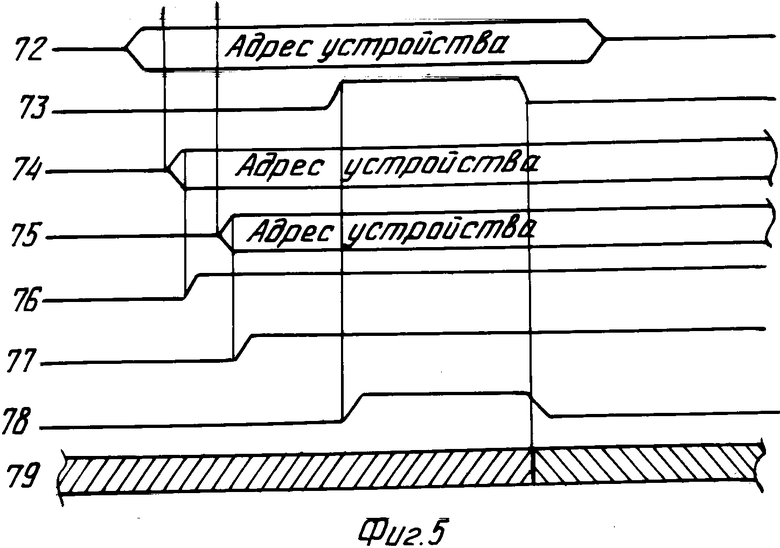

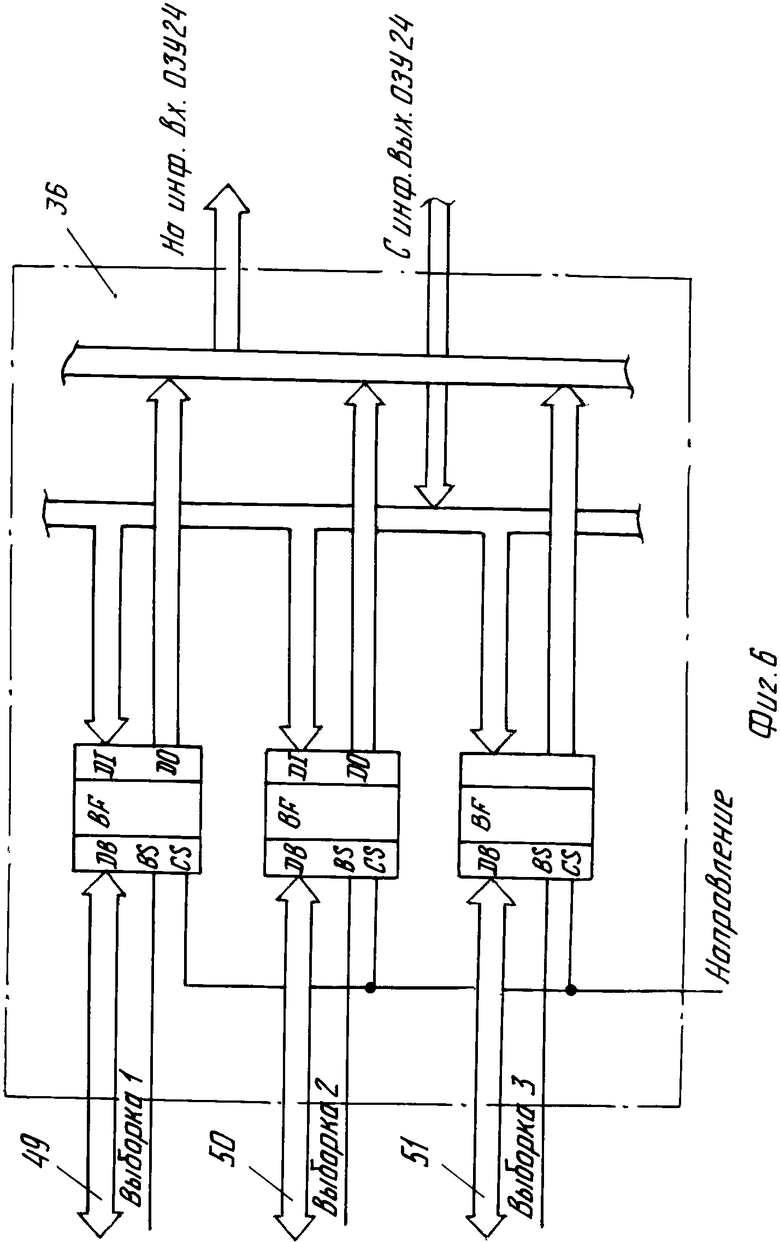

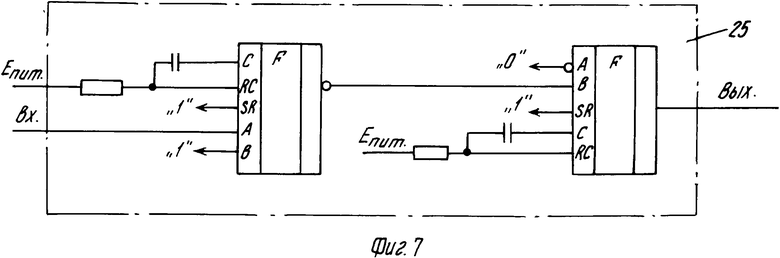

На фиг.1 и 2 представлена схема электрического функционального устройства обмена ВС; на фиг.3, 4 и 5 показаны временные диаграммы работы; на фиг.6 и 7 - возможные реализации некоторых узлов.

Устройство содержит первый, второй и третий дешифраторы 1, 2 и 3, входы которых соединены с соответствующими первой, второй и третьей шинами 4, 5 и 6 адреса, тринадцать элементов 7-19 И, четыре элемента ИЛИ 20-23 оперативную память (ОЗУ) 24, формирователь 25 импульсов, три элемента 26-28 задержки, три триггера 29-31, постоянную память (ПЗУ) 32, сумматор 33 по модулю К (К > 2) 33, счетчик 34, адресный коммутатор 35, двунаправленный коммутатор 36, первую, вторую и третью шины 37, 38 и 39 записи, первую, вторую и третью шины 40, 41 и 42 чтения, первую, вторую и третью шины 43, 44 и 45 готовности, первую, вторую и третью шины 46, 47 и 48 начала машинного цикла, первую, вторую и третью двунаправленные шины 49, 50 и 51 данных. Первая, вторая и третья шины 43, 44 и 45 готовности соединены соответственно с третьим, четвертым и пятым входами ПЗУ 32 и первым, вторым и третьим входами сумматора 33 по модулю больше двух, выход которого соединен со счетным входом счетчика 34. Выходы нулевого и первого разрядов счетчика 34 соединены соответственно с шестым и седьмым адресными входами ПЗУ 32, третий, четвертый и пятый адресные входы которого соединены соответственно с выходами первого, второго и третьего триггеров 29, 30 и 31 и прямыми входами первого и второго элементов И 7 и 10, третьего, четвертого элементов И 8, 11 и пятого, шестого элементов И 9, 12. Выход первого элемента И 7 соединен с первыми входами первого элемента ИЛИ 20, и седьмого элемента И 13, выход третьего элемента И 8 соединен с первыми входами второго элемента ИЛИ 21 и восьмого элемента И 19, выход пятого элемента И 9 соединен с первыми входами третьего элемента ИЛИ 22 и девятого элемента И 15, выход второго элемента И 10 соединен с вторым входом первого элемента ИЛИ 20, выход которого соединен с первым входом десятого элемента И 16. Выход элемента И 16 соединен с входом первого элемента 26 задержки, выход которого соединен с нулевым адресным входом ПЗУ 32, первыми входами выборки первых входов адресного коммутатора 35 , входами-выходами двунаправленного коммутатора 36 данных и вторым входом седьмого элемента И 13. Первый адресный вход элемента И 13 соединен с выходом второго элемента 27 задержки, вторыми входами выборки вторых входов адресного коммутатора 35 и входов-выходов двунаправленного коммутатора 36 данных и вторым входом восьмого элемента И 14, вход которого соединен с выходом одиннадцатого элемента И 17. Первый вход элемента И 17 соединен с выходом второго элемента ИЛИ 21, второй вход которого соединен с выходом элемента ИЛИ 21, второй вход которого соединен с выходом элемента И 11. Выход шестого элемента И 12 соединен с вторым входом третьего элемента ИЛИ 22, выход которого соединен с первым входом двенадцатого элемента И 18. Выход элемента И 18 соединен с входом третьего элемента 28 задержки, выход которого соединен с вторым адресным входом ПЗУ 32 , вторым входом девятого элемента И 16 и третьими входами выборки третьих входов адресного коммутатора 35 и двунаправленного коммутатора 36 данных. Выходы седьмого, восьмого и девятого элементов И 13, 14 и 15 соединены с соответствующими входами четвертого элемента ИЛИ 23, выход которого соединен с входом направления коммутатора 36 данных и входом формирователя 25 импульсов. Выход последнего соединен с входом записи ОЗУ 24, вход разрешения которого соединен с шестым выходом ПЗУ 32. Седьмой выход ПЗУ соединен с первым входом тринадцатого элемента И 19, второй вход которого соединин с выходом сумматора 33 по модулю больше двух. Первая, вторая и третья шины 46, 47 и 48 начала машинного цикла соединены соответственно с входами синхронизации первого, второго и третьего триггеров 29, 30 и 31, информационные входы которых соединены с выходами соответственно первого, второго и третьего дешифраторов 1, 2 и 3. Первая, вторая и третья шины 37, 38 и 39 записи соединены с инверсными входами первого, третьего и пятого элементов И 7, 8 и 9, первая, вторая и третья шины 40, 41 и 42 чтения соединены с инверсными входами соответственно второго, четвертого и шестого элементов И 10, 11 и 12. Первая, вторая и третья шины 4, 5 и 6 адреса соединены соответственно с первыми, вторыми и третьими информационными входами адресного коммутатора 35, информационные выходы которого соединены с соответствующими адресными входами ОЗУ 24. Входы данных ОЗУ соединены с соответствующими разрядами первых, вторых и третьих информационных выходов двунаправленного коммутатора 36 данных, первые, вторые и третьи информационные входы которого соединены с соответствующими разрядами информационных выходов ОЗУ 24. Первая, вторая и третья двунаправленные шины 49, 50 и 51 данных соединены с соответствующими разрядами первых, вторых и третьих информационных входов-выходов двунаправленного коммутатора 36 данных.

Устройство работает следующим образом.

Устройство обмена подключается к системным шинам ЭВМ, каждая системная шина содержит шину адреса, управления (в частности, линии сигналов готовности, записи в память и чтения памяти) и двунаправленную шину данных. Дешифраторы 1-3 и триггеры 29-31 формируют для ПЗУ 32 сигналы признаков обращения к устройству. Комбинаторный узел на элементах И 7-12 и ИЛИ 20, 21 предназначен для формирования признаков обращения в режимах записи-считывания памяти раздельно от каждой ЭВМ. Комбинаторный узел на элементах И 7-15 и ИЛИ 23 формирует признак записи в память от ЭВМ, которой разрешен доступ в текущий интервал времени. ПЗУ 32 и комбинаторный узел на элементах И 16-18 по сигналам признаков обращения к устройству, признакам поступления сигналов записи-считывания и текущего кода приоритетов доступа формирует сигналы признаков разрешения доступа к ОЗУ 24.

Узел на сумматоре 33 элементе И 19 и счетчике 34 определяет текущий код приоритетов доступа ЭВМ к ОЗУ устройства. Коммутатор 35 по признакам разрешения доступа, поступающим от ПЗУ 32, переключает одну из шин 4-6 адреса на адресные входы ОЗУ 24. Коммутатор 36 переключает одну из шин 49-51 данных на входы или с выходов ОЗУ 24 также по признакам разрешения доступа, направление шин между коммутатором 36 и ОЗУ 24 определяется сигналом признака записи от ЭВМ, которой разрешен доступ (поступает с выхода элемента ИЛИ 23). Формирователь 25 вырабатывает строб записи в ОЗУ 24, по времени, расположенный "внутри" сигнала признака записи. Элементы 26-28 отфильтровывают дробление сигналов, поступающих от ПЗУ 32.

Рассмотрим режим записи в ОЗУ устройства информации ЭВМ 1 (ее системная шина образована шинами 4, 37, 40, 49, 46, 43) на фоне отсутствия заявок доступа от двух остальных ЭВМ (см. фиг.3). По адресной шине 4 поступает адрес устройства (52), дешифрируемый дешифратором 1 и зафиксированный триггером 29 (сигнал 54). Фиксация адреса осуществляется сигналом начала машинного цикла (53), поступающим по шине 46 от ЭВМ. Сигнал (54) признака обращения от ЭВМ1 поступает на адресный вход 3 ПЗУ 32, в этом режиме на адресных входах 4 и 5 ПЗУ 32 логические "0", что соответствует отсутствию обращения от ЭВМ2 и 3. Вне зависимости от текущего кода приоритетных уровней, поступающих от счетчика ЗУ, ПЗУ 32 по разряду 0 выдает разрешение доступа (56) к ОЗУ для ЭВМ1 логической "1". Этот сигнал стробируется сигналом (55) записи в память, поступающим с шины 37, на выходе элемента 26 задержки формируется рабочий сигнал (57) разрешения доступа, поступающий к коммутаторам 35 и 36 для подключения к ОЗУ 24 системной шины ЭВМ1. Для ОЗУ 24 формирователь 25 выдает строб записи (58), по которому данные с шины 49 (сигнал 59) записываются в соответствующие ячейки ОЗУ.

Рассмотрим режим поступления заявки от ЭВМ2 (ее системная шина образована шинами 47, 38, 41, 5, 50, 44) на фоне исполнения заявки ЭВМ1 (см. фиг. 4) в режимах чтения из ОЗУ. От ЭВМ по шине 4 поступает адрес устройства (60), фиксируемый сигналом (61) начала машинного цикла. В результате для ПЗУ 32 формируется сигнал (62) признака обращения от ЭВМ1, ПЗУ 32 формирует рабочий сигнал (63) разрешения доступа ЭВМ1 к ОЗУ и на шину 49 выдаются данные из соответствующей ячейки ОЗУ 24. В это время по шине 5 от ЭВМ2 поступает адрес (65) устройства, фиксируемый сигналом (66) начала машинного цикла, поступающим с шины 47. В результате с выхода триггера 30 на адресный вход 4 ПЗУ 32 поступает сигнал (67) признака обращения от ЭВМ 2. Так как это время было выдано разрешение доступа для ЭВМ1, от вне зависимости от текущего кода уровней приоритета для ЭВМ2 с выхода 4 ПЗУ 32 поступает сигнал (68) "Не готов" и машинный цикл ЭВМ2 приостанавливается до окончания сигнала (62) признака обращения ЭВМ1, после чего для ЭВМ2 с выхода 1 ПЗУ 32 поступает сигнал (69) разрешения доступа и из соответствующей ячейки ОЗУ 24 на шину 50 поступают данные (сигналы 70). При этом сигнал (71) "Чтение памяти", поступающий от ЭВМ2 по шине 41, увеличивается по длительности, как и весь машинный цикл ЭВМ в рассматриваемой ситуации.

При одновременном поступлении признаков обращения от любых двух ЭВМ предпочтение отдается той ЭВМ, уровень приоритета которой в данное время выше, машинный цикл ЭВМ более низкого уровня при этом приостанавливается до исполнения заявки от ЭВМ более высокого уровня. При одновременном поступлении трех заявок каждая исполняется последовательно в соответствии с текущим кодом уровня приоритета.

Для устранения возможности монопольного захвата ресурса двумя ЭВМ старших уровней и блокировки доступа для ЭВМ младшего уровня при одновременном поступлении запросов от трех ЭВМ (см. фиг.5) после исполнения заявки ЭВМ самого высокого старшего уровня происходит изменение (икрементирование) кода уровней приоритета и уровни приоритета всех ЭВМ циклически смещаются на один уровень вниз, в результате ЭВМ низшего уровня приобретает статус самого высокого уровня. Новое изменение статуса ЭВМ происходит при следующем одновременном обращении к устройству от трех ЭВМ. Под одновременным понимается поступление заявок от двух ЭВМ в интервале текущего исполнения заявки.

Пусть в рассматриваемом режиме от ЭВМ1 поступает адрес (72) и ей выдается разрешение доступа (73). В этом интервале времени от ЭВМ2 и 3 поступают запросы по шинам адреса (74 и 75) и им соответственно выдаются сигналы "Не готов" (76 и 77). При появлении на двух входах сумматора 33 логической "1" на вход элемента И 19 поступает логическая "1" сигнала разрешения, на счетный вход счетчика 34 поступает сигнал (78) для инкрементирования содержимого счетчика и на адресные входы 6 и 7 ПЗУ 32 поступает новый код (79) уровней приоритета. Срез сигнала (78) определяется срезом сигнала (73) разрешения доступа, чем достигается изменение статуса ЭВМ строго после исполнения заявки самого высокого уровня. На фиг.5 различной штриховкой показаны различающиеся коды статуса ЭВМ.

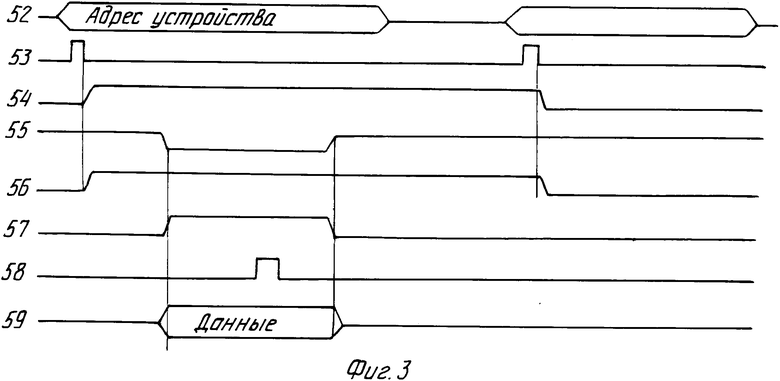

Реализация устройства. Дешифраторы 1-3 могут быть выполнены на комбинаторных элементах или на ПЗУ. Мажоритарный элемент 33 может быть выполнен на микросхеме 533ЛП3. Двунаправленный коммутатор 36 может быть выполнен на шести микросхемах 585АП16 (см. фиг.6). Аналогично может быть выполнен коммутатор 35. Формирователь 25 импульсов может быть реализован на микросхеме 133АГ3 (см. фиг.7). Возможная прошивка ПЗУ32 представлена в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1758648A1 |

| Устройство для сопряжения двух электронно-вычислительных машин | 1985 |

|

SU1291996A1 |

| Устройство для сопряжения ЭВМ | 1991 |

|

SU1837306A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ УСТРОЙСТВАМИ | 1991 |

|

RU2024052C1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1989 |

|

SU1810891A1 |

| Двухканальное устройство для сопряжения | 1982 |

|

SU1070535A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

Изобретение относится к вычислительной технике. Целью изобретения является минимизация времени цикла обмена данными во всем диапазоне загрузки, минимизация аппаратной части, введение циклического изменения уровней приоритета доступа ЭВМ к общему ресуру ЗУ при пиковых значениях загрузки совокупности каналов обмена устройства. Устройство содержит три дешифратора, три D-триггера, два коммутатора, оперативную память, тринадцать элементов И, четыре элемента ИЛИ, три элемента задержки, сумматор по модулю K (K > 2), счетчик, формирователь импульсов и постоянную память (ПЗУ), причем приоритетный (текущий) список хранится и модифицируется счетчиком, а фиксированный алгоритм занятия и высвобождения ресурса общего ЗУ содержится в ПЗУ. 1 табл. , 7 ил.

УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее первый, второй и третий дешифраторы, входы которых соединены с соответствующими линиями соответственно первой, второй и третьей шин адреса, тринадцать элементов И, четыре элемента ИЛИ, оперативную память, формирователь импульсов, три элемента задержки, три триггера, отличающееся тем, что в него введены постоянная память, сумматор по модулю К (где К > 2), счетчик, адресный коммутатор, двунаправленный коммутатор, первая, вторая и третья шины готовности устройства соединены соответственно с первым, вторым и третьим выходами постоянной памяти и первым, вторым и третьим входами сумматора по модулю К, выход которого соединен со счетным входом счетчика, выходы нулевого и первого разрядов которого соединены соответственно с первой группой адресных входов постоянной памяти, вторая группа адресных входов которой соединена соответственно с выходами первого, второго, третьего, четвертого, пятого, шестого элементов И, выход первого элемента И соединен с первыми входами первого элемента ИЛИ и седьмого элемента И, выход третьего элемента И соединен с первыми входами второго элемента ИЛИ и восьмого элемента И, выход пятого элемента И соединен с первыми входами третьего элемента ИЛИ и девятого элемента И, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, Выход которого соединен с первым входом десятого элемента И, выход которого соединен с входом первого элемента задержки, выход которого соединен с нулевым адресным входом постоянной памяти, входами выборки первых входов адресного коммутатора и коммутатора данных и первым входом седьмого элемента И, второй вход которого соединен с выходом второго элемента задержки, входами выборки вторых входов адресного коммутатора и коммутатора данных и первым входом восьмого элемента И, второй вход которого соединен с выходом одиннадцатого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход шестого элемента И соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с первым входом двенадцатого элемента И, выход которого соединен с входом третьего элемента задержки, выход которого соединен с вторым адресным входом постоянной памяти, вторым входом девятого элемента И и третьими входами выборки входов коммутаторов данных и адресного коммутатора, выходы седьмого, восьмого и девятого элементов И соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с входом направления коммутатора данных и входом формирователя импульсов, выход которого соединен с входом записи оперативной памяти, вход разрешения которой соединен с шестым выходом постоянной памяти, седьмой выход которой соединен с первым входом тринадцатого элемента И, второй вход которого соединен с выходом сумматора по модулю К, первая, вторая и третья шины начала машинного цикла устройства соединены соответственно с входами синхронизации первого, второго и третьего триггеров, информационные входы которых соединены с выходами соответственно первого, второго и третьего дешифраторов, первая, вторая и третья шины записи устройства соединены с инверсными входами первого, третьего и пятого элементов И, первая, вторая и третья шины чтения устройства соединены с инверсными входами соответственно второго, четвертого и шестого элементов И, первая, вторая и третья шины адреса устройства соединены соответственно с первым, вторым и третьим информационными входами адресного коммутатора, информационные выходы которого соединены с соответствующими адресными входами оперативной памяти, входы данных которой соединены с соответствующими разрядами первых, вторых и третьих информационных выходов коммутатора данных, первые, вторые и третьи информационные входы которого соединены с соответствующими разрядами информационных выходов оперативной памяти, первая, вторая и третья двунаправленные шины данных устройства соединены с соответствующими разрядами первых, вторых и третьих информационных входов - выходов коммутатора данных.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-09-30—Публикация

1991-06-27—Подача