Изобретение относится к вычислительной технике и может быть использовано для настройки отладки и проверки работы специализированных мик- роЭВМ,

Цель изобретения - расширение функциональных возможностей за счет обесп ечения останова по адресу в зависимости от типа выполненного мик- роЭВМ цикла.

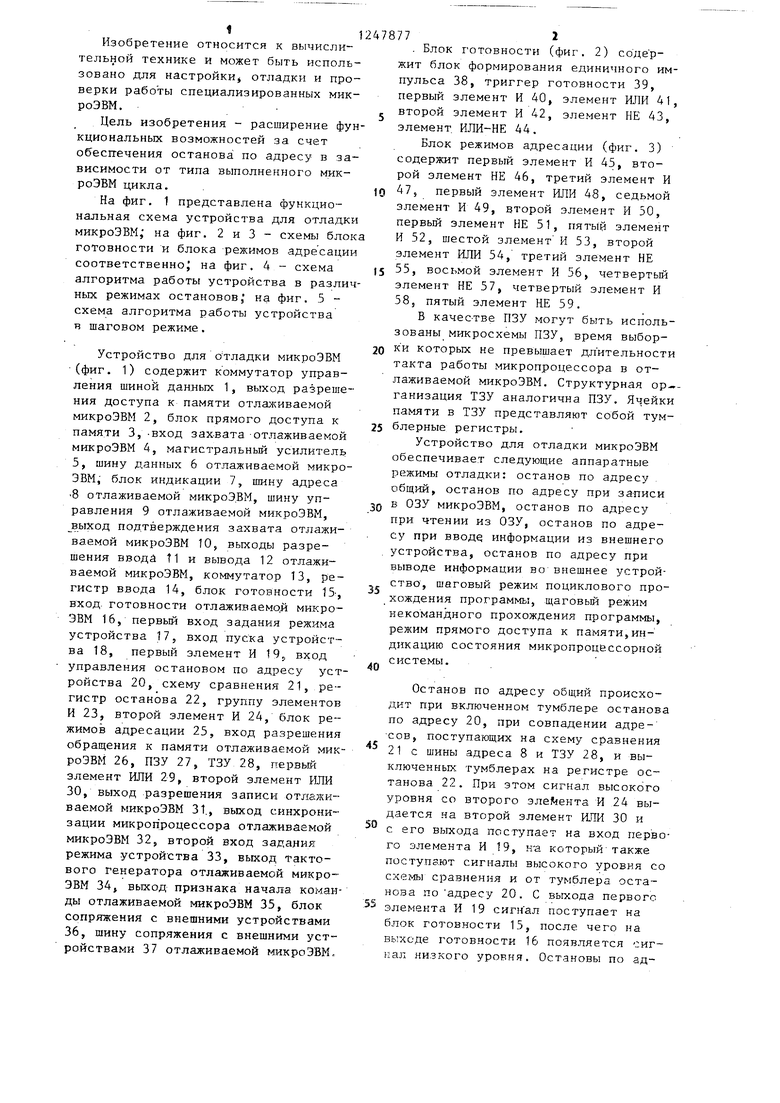

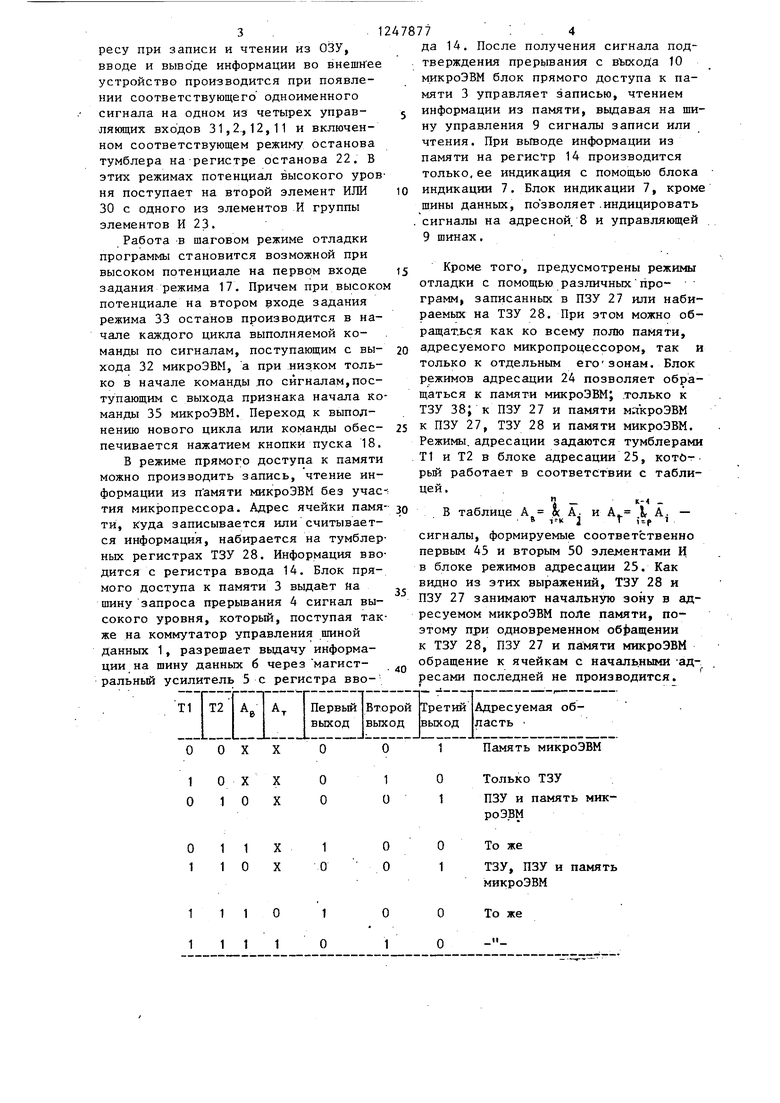

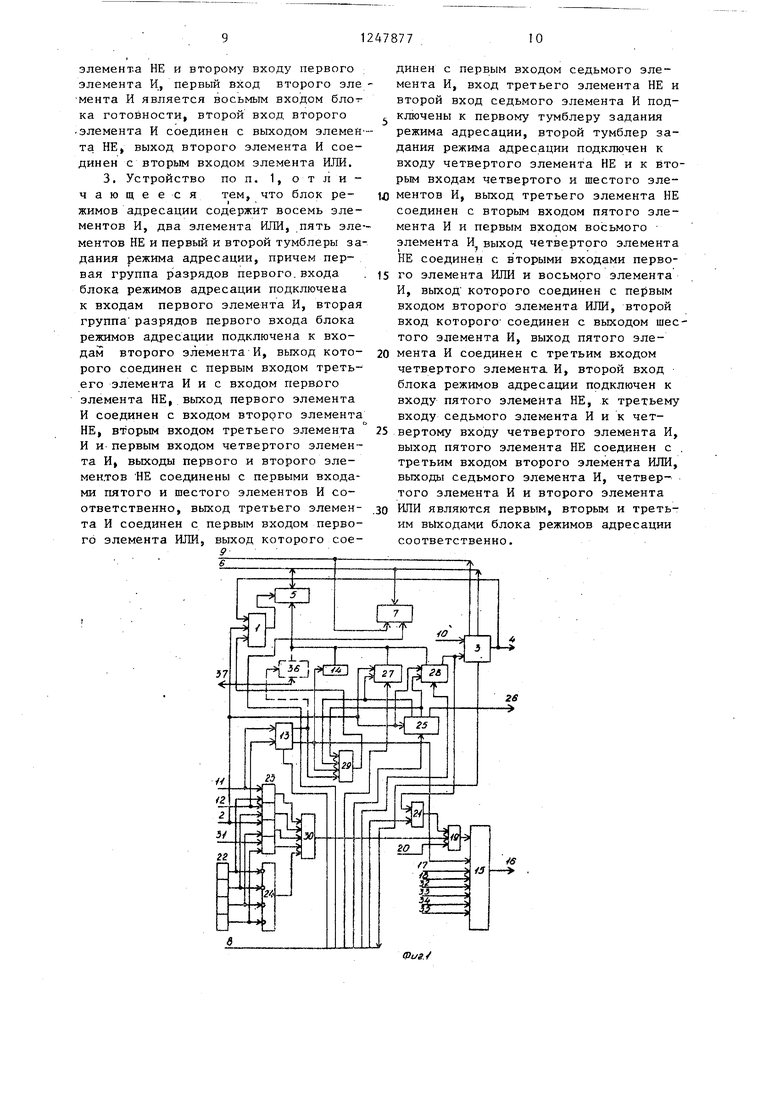

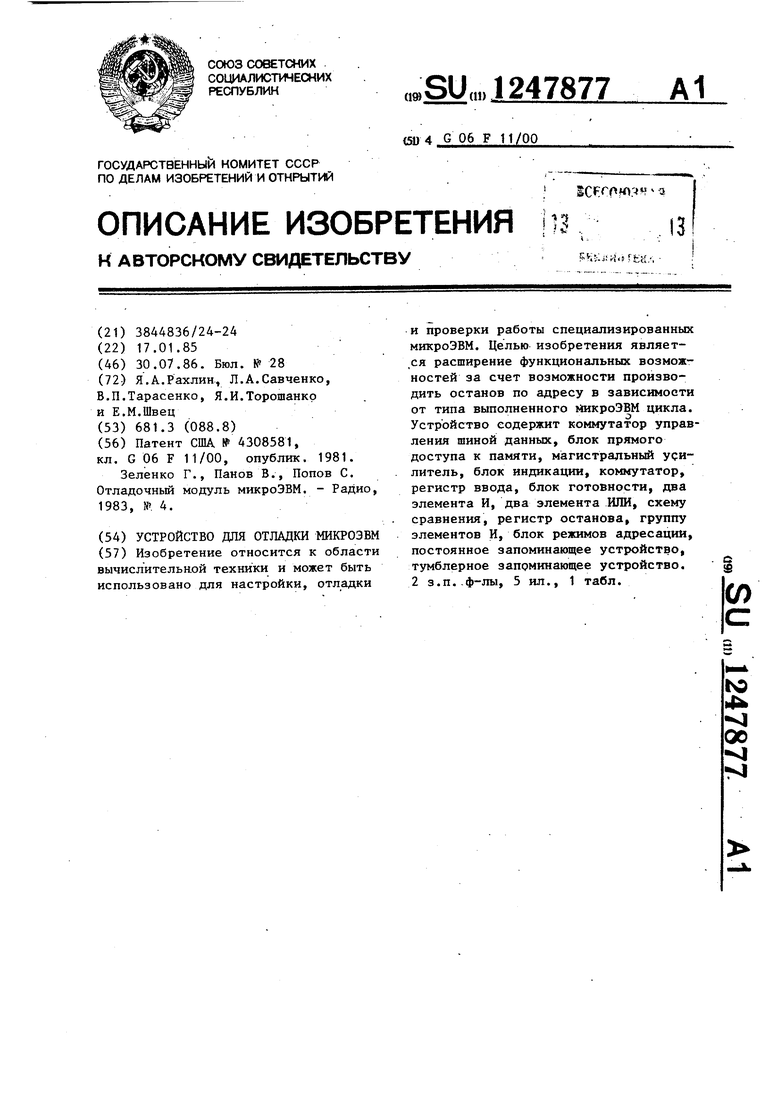

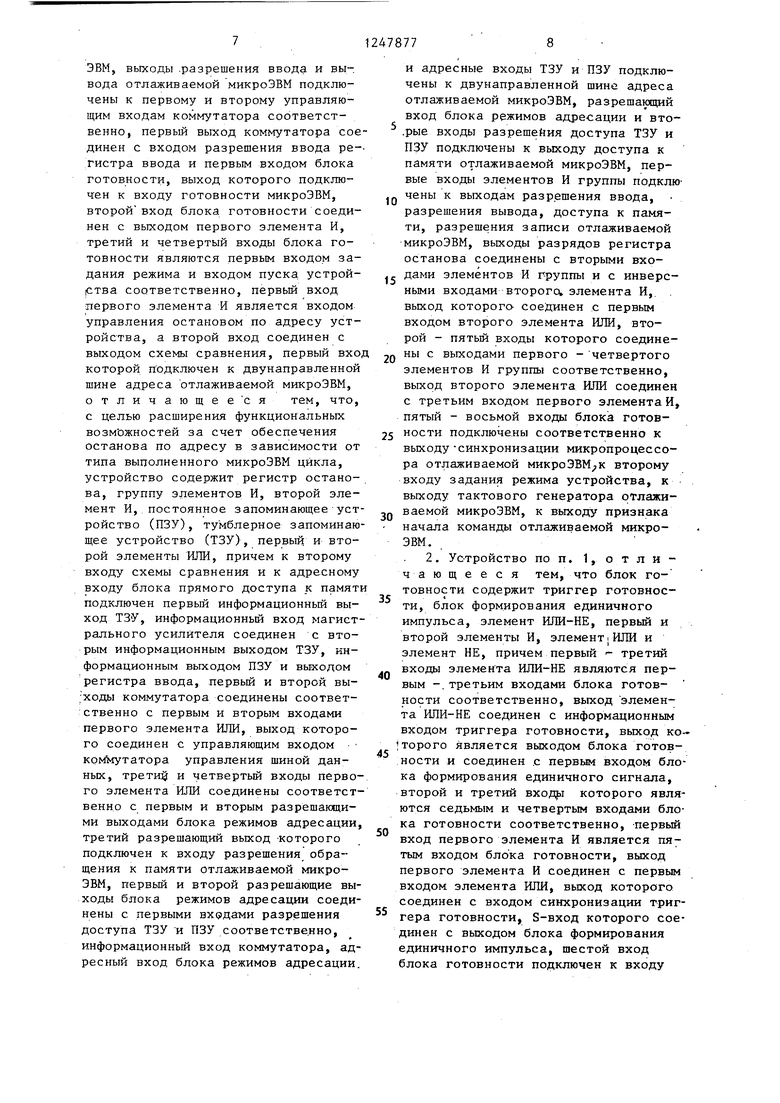

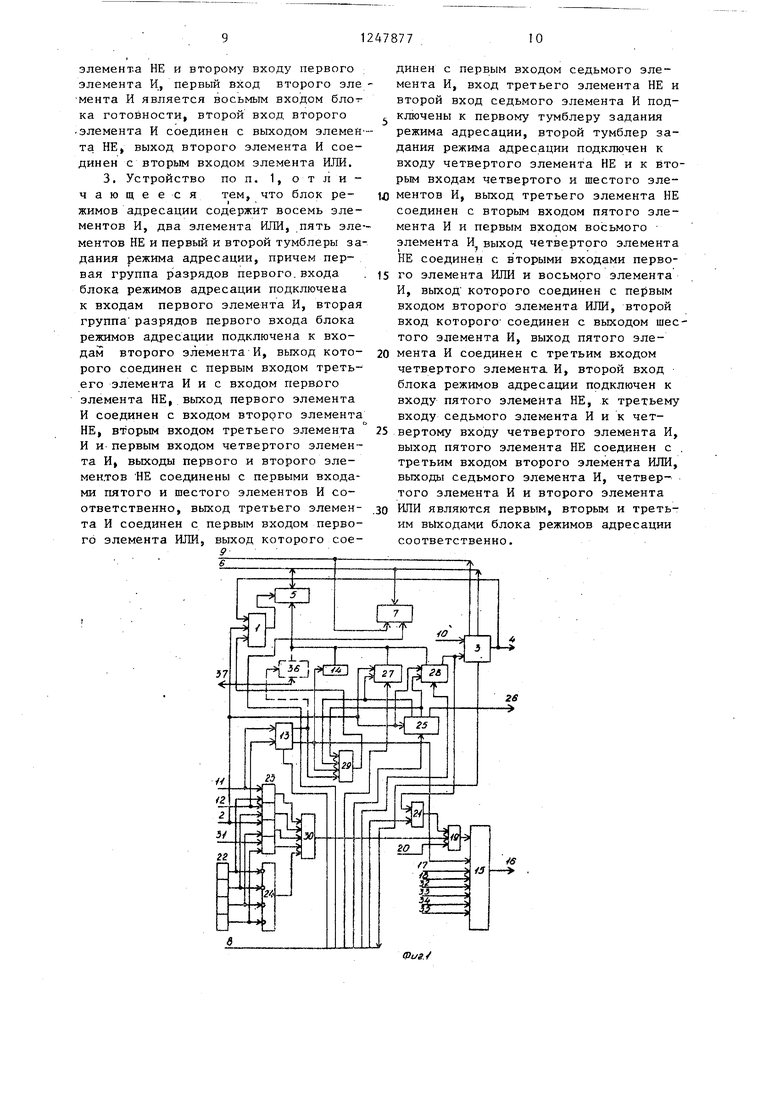

На фиг. 1 представлена функциональная схема устройства для отладки микроэвм, на фиг. 2 и 3 - схемы блок готовности и блока режимов адресации соответственно; на фиг. 4 - схема алгоритма работы устройства в различных режимах остановов; на фиг. 5 схема алгоритма работы устройства в шаговом режиме.

Устройство для о тладки микроЭВМ (фиг. 1) содержит коммутатор управления шиной данных 1, выход разрешения доступа к памяти отлаживаемой микроэвм 2, блок прямого доступа к памяти 3, -вход зах-вата -отлаживаемой микроэвм 4, магистральньй усилитель 5, шину данных 6 отлаживаемой микро- ЭВМ, блок индикации 7, шину адреса 8 отлаживаемой микроЭВМ, шину управления 9 отлаживаемой микроЭВМ, выход подтверждения захвата отлаживаемой микроэвм 10J выходы разрешения ввода t1 и вывода 12 отлаживаемой микроэвм, коммутатор 13, регистр ввода 14, блок готовности 15-, вход готовности отлаживаемой микро- ЭВМ 16, первый вход задания режима устройства 17, вход пуска устройства 18, первый элемент И 195 вход управления остановом по адресу устройства 20, схему сравнения 21, регистр останова 22, группу элементов И 23, второй элемент И 24, блок режимов адресации 25, вход разрешения обращения к памяти отлаживаемой мик- роЭВМ 26, ПЗУ 27, ТЗУ 28, первьй элемент ИЛИ 29, второй элемент ИЛИ 30, выход разрешения записи отлаживаемой микроэвм 31., выход синхронизации микропроцессора отлаживаемой микроэвм 32, второй вход задания режима устройства 33, выход тактового генератора отлаживаемой микро- ЭВМ 34, выход признака начала команды отлаживаемой микроЭВМ 35, блок сопряжения с внешними устройствами 36, шину сопряжения с внешними устройствами 37 отлаживаемой микроЭВМ,

Блок готовности (фиг. 2) соде р- жит блок формирования единичного импульса 38, триггер готовности 39, первый элемент И 40, элемент ИЛИ 41,

второй элемент И 42, элемент НЕ 43, элемент ИЛИ-НЕ 44.

Блок режимов адресации (фиг. 3) содержит первый элемент И 45, второй элемент НЕ 46, третий элемент И 47, первый элемент ИЛИ 48, седьмой элемент И 49, второй элемент И 50, первый элемент НЕ 51, пятый элемент И 52, шестой элемент И 53, второй элемент ИЛИ 54, третий элемент НЕ

55, восьмой элемент И 56, четвертьш элемент НЕ 57, четвертый элемент И 58, пятый элемент НЕ 59.

В качес-тве ПЗУ могут быть использованы микросхемы ПЗУ, время выборк и которых не превышает длительности такта работы микропроцессора в отлаживаемой микроэвм. Структурная ор-- ганизация ТЗУ аналогична ПЗУ. Ячейки памяти в ТЗУ представляют собой тумблерные регистры.

Устройство для отладки микроЭВМ обеспечивает следующие аппаратные режимы отладки: останов по адресу . общий, останов по адресу при за-писи

в ОЗУ микроэвм, останов по адресу при чтении из ОЗУ, останов по адресу при вводе информации из внешнего устройства, останов по адресу при выводе информации во внешнее устрой

хождения программы, щаговьи режим кекомандного прохождения программы, режим прямого доступа к памяти,индикацию состояния микропроцессорной системы.

5

Останов по адресу общий происходит при включенном тумблере останова по адресу 20, при совпадении адресов, поступающих на схему сравнения 21 с шины адреса 8 и ТЗУ 28, и выключенных тумблерах на регистре останова 22. При этом сигнал высокого уровня со второго элемента И 24 выдается на второй элемент ИЛИ 30 и с его выхода поступает на вход первого элемента И 19, н-а который также поступают сигналы высокого уровня со схемы сравнения и от тумблера останова по адресу 20. С выхода первого элемента И 19 сигн ал поступает на блок готовности 15, после чего на выхсде готовности 16 появляется сиг- кал низкого уровня. Остановы по ад0

pecy при записи и чтении из , вводе и выводе информации во внешнее устройство производится при появлении соответствующего одноименного сигнала на одном из четырех управляющих входов 31,2., 12,11 и включенном соответствующем режиму останова тумблера на-регистре останова 22. В этих режимах потенциал высокого уров ня поступает на второй элемент ИЖ 30 с одного из элементов И группы элементов И 23.

Работа в шаговом режиме отладки программы становится возможной при высоком потенциале на первом входе задания режима 17. Причем при высоко потенциале на втором входе задания режима 33 останов производится в начале каждого цикла выполняемой команды по сигналам, поступающим с выхода 32 микроэвм, а при низком только в начале команды .по сигналам,поступающим с выхода признака начала команды 35 микроэвм. Переход к выполнению нового цикла или команды обеспечивается нажатием кнопки пуска 18.

В режиме прямого доступа к памяти можно производить запись, чтение информации из п амяти микроэвм без учас тия микропрессора. Адрес ячейки памя ти, куда записывается или считывается информация, набирается на тумблерных регистрах ТЗУ 28. Информация вводится с регистра ввода 14. Блок прямого доступа к памяти 3 выдает На шину запроса прерывания 4 сигнал высокого уровня, который, поступая также на коммутатор управления шиной данных 1, разрешает вьщачу информации на шину данных б через магистральный усилитель 5с регистра вво

О О X X

110 111

О О

1 о

1

о

0

S

0

о

5

5

да 14. После получения сигнала подтверждения прерывания с выхода 10 микроэвм блок прямого доступа к памяти 3 управляет записью, чтением информации из памяти, вьщавая на шину управления 9 сигналы записи или чтения. При вьШоде информации из памяти на регистр 14 производится только, ее индикация с помощью блока индикации 7. Блок индикации 7, кроме шины данных, по зволяет .индицировать . сигналы на адресной. 8 и управляющей 9 шинах.

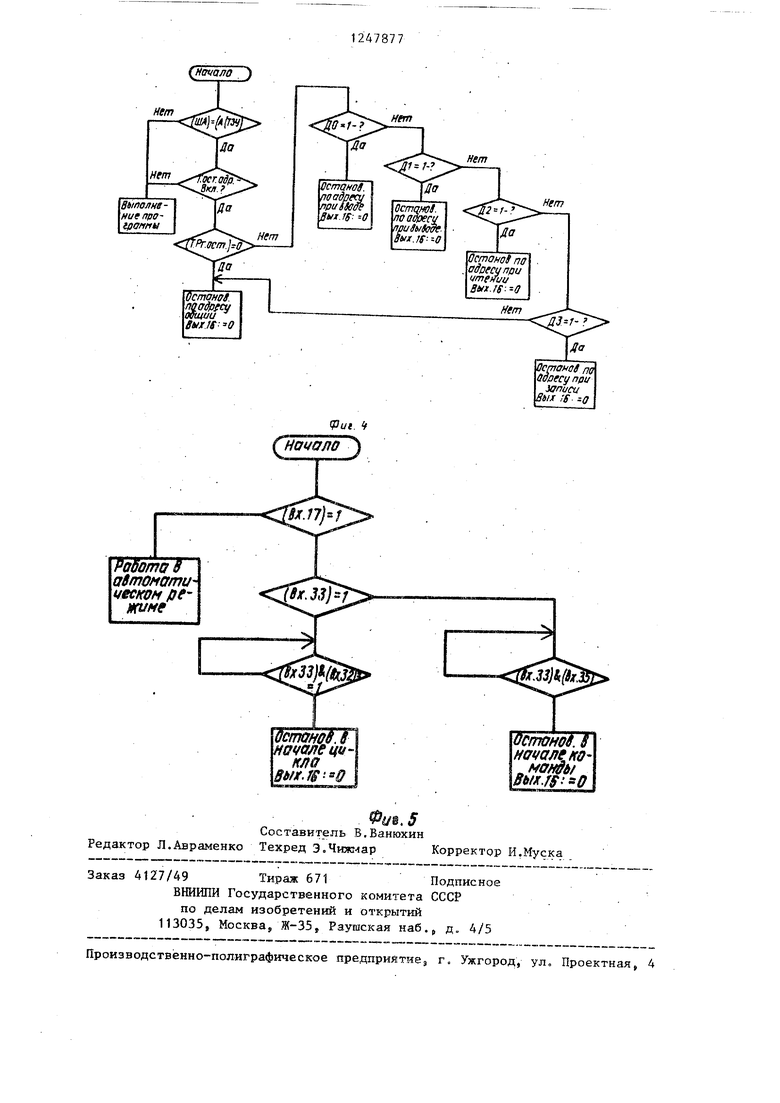

Кроме того, предусмотрены режимы отладки с помощью различных программ, записанных в ПЗУ 27 или набираемых на ТЗУ 28. При этом можно обращаться как ко всему полю памяти, адресуемого микропроцессором, так и только к отдельным его зонам. Блок режимов адресации 24 позволяет обращаться к памяти микроэвм только к ТЗУ 38; к ПЗУ 27 и памяти макроЭВМ к ПЗУ 27, ТЗУ 28 и памяти микроЭВМ. Режимы, адресации задаются тумблерами Т1 и Т2 в блоке адресации 25, котй- рьй работает в соответствии с таблицей .

1 - It- В таблице А « А. и А.. А. -

6 i-d 2 t ;.р 1

сигналы, формируемые соответственно первым 45 и вторым 50 элементами И в блоке режимов адресации 25. Как видно из этих выражений, ТЗУ 28 и ПЗУ 27 занимают начальную зону в адресуемом микроэвм norte памяти, поэтому при одновременном об)ащении к ТЗУ 28, ПЗУ 27 и памяти микроЭВМ обращение к ячейкам с начальными адресами последней не производится.

о 1

о 1

о о

Память микроэвм

Только ТЗУ

ПЗУ и память мик- роЭ.ВМ

То же

ТЗУ, ПЗУ и память микроэвм

То же

В таблице X означает, что сигнал может принимать значение как О, так и 1.

Программные средства устройства для отладки микроЭВМ обеспечивают следующие режимы отладки: ручной побайтный ввод информации в память системы, тестовую проверку узлов микроэвм, циклическое выполнение команды, ввод - вывод информации с внешних устройств.

Ручной побайтной ввод информации может производиться либо с регистра ввода 14, либо с ТЗУ 28, при этом программа ввода набирается на ТЗУ 28, либо используется та, которая имеется в ПЗУ 27. В этом режиме блок режимов адресации 25 разрешает о бра- щение к ТЗУ 28, ПЗУ 27 и память мик- роЭВМ. Выбор регистра ввода вывода 14 производит коммутатор 13. Сиг-налы разрешения обращения с блока адресации 25 поступают также на элемент ИЛИ 29, с его выхода один из них выдается в коммутатор управления шиной данных 1, которая управляет подключением к шине данных 6 ТЗУ 29 или ПЗУ 27 или регистра ввода 14.

Тестовая проверка узлов производится с помощью специализированных программ, написанных в соответствии со спецификой тестируемых узлов мик- роЭВМ. и записанных в ПЗУ 27.

Циклическое выполнение какой-либо команды микропроцессора производится, когда блок режимов адресации 25 разрешает обращение только к ТЗУ 28. При этом на всех тумблерных регистрах ТЗУ 28 должен быть набран код проверяемой команды.

Ввод - вывод информации с внешних устройств производится с помощью блока сопряжения с внешними устройствами 36 через шину сопряжения с внешними устройствами 37. Обращение к внешним устройствам происходит при появлении сигналов на 11 или 12 выходах микроэвм и адреса внешнего устройства на шине адреса 8. При этом коммутатор 13 выдает на схему сопряжения с внешними устройствами 36 сигнал разрешения обращения к соответ- ствукщему внешнему устройству, В качестве внешних устройств могут выступать перфоратор и фотосчитыватель

Алгоритм работы устройства в различных режимах остановов приведен на фиг. 4. Здесь используются следукйдие

5

обозначения: (ША) - содержимое шины адреса 8; (А(ТЗУ) - содержимое регистров ТЗУ 28, на которых набирается адрес останова; Т. ост.адр. - тумблер останова по адресу (вход управ- -ления останова по адресу 20), (Т.Рг. ост.) - содержимое тумблерного ре-- гистра останова 22, ДО, Д1, Д2, ДЗ - Q нулевой, первый, второй и третий раз- ряды тумблерного регистра останова 22 .

Алгоритм работы .устройства в шаговом режиме приведен на фиг. 5. Здесь символ & обозначает конъюнкцию сигналов на соответствующих выходах устройства (указаны в скобках).

Формула изобретения

0 „

1. Устройство для отладки микро- ЭВМ, содержащее коммутатор управления шиной данных, магистральный усилитель, блок индикации, блок пря мо- 5 го доступа к памяти, блок режимов адресации, регистр ввода, коммутатор, схему сравнения, блок готовности, элемент И, причем первый информационный вход коммутатора управления шиной данных подключен к выхо- - ду доступа к памяти отлаживаемой

микроэвм, второй информационный вход коммутатора управления шиной данных подключен к выходу захвата блока прямого доступа к памяти, подключенному также к входу захвата отлаживаемой микроэвм, информационньй выход блока прямого доступа к памяти подключен к двунаправленной- шине

. данных отлая;иваемой микроЭВМ, к которой также подключены первьй вход

. блока индикации и выход магистрального усилителя, управляющий вход магистрального усилителя соединен с выходом коммутатора управления шиной данных, выход режима блока прямого доступа к памяти соединен с вторым входом блока индикации и с входной шиной управлеЬия чтением - записью отлаживаемой микроЭВМ, ад- ресньш выход блока прямого доступа к памяти подключен-к двунаправленной шине адреса отлаживаемой микро- ЭВМ, третий вход блока индикации подключен к двунаправленной шине ад- 5 реса отлаживаемой микроЭВМ разрешающий вход блока прямого доступа к памяти подключен к выходу подтверждения захвата отлаживаемой микро0

5

0

5

0

ЭВМ, выходы .разрешения ввода и вывода отлаживаемой микроЭВМ подключены к первому и второму управляющим входам коммутатора соответственно, первый выход коммутатора соединен с входом разрешения ввода регистра ввода и первым входом блока готовности, выход которого подключен к входу готовности микроэвм, второй вход блока готовности соединен с выходом первого элемента И, третий и четвертый входы блока готовности являются первым входом задания режима и входом пуска устрой- |Ства соответственно, первый вход первого элемента И является входом управления остановом по адресу устройства, а второй вход соединен с выходом схемы сравнения, первый вхо которой подключен к двунаправленной шине адреса отлаживаемой микроЭВМ, отличающее с я тем, что, с целью расширения функциональных возможностей за счет обеспечения останова по адресу в зависимости от типа выполненного микроЭВМ цикла, устройство содержит регистр останова, группу элементов И, второй элемент И, постоянное запоминающее устройство (ПЗУ), тумблерное запоминающее устройство (ТЗУ), первый и второй элементы ИЛИ, причем к второму входу схемы сравнения и к адресному входу блока прямого доступа к памят подключен первый информационный выход ТЗУ, информационный вход магистрального усилителя соединен с вторым информационным выходом ТЗУ, информационным выходом ПЗУ и выходом регистра ввода, первый и второй вы- ходы коммутатора соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с управляющим входом коМ угутатора управления шиной данных, третиу и четвертый входы первого элемента ИЛИ соединены соответственно с первым и вторым разрешающими выходами блока режимов адресации, третий разрешающий выход -которого подключен к входу разрешения обращения к памяти отлаживаемой микро- ЭВМ, первый и второй разрешающие выходы блока режимов адресации соединены с первыми входами разрешения доступа ТЗУ и ПЗУ соответственно, информационный вход коммутатора, адресный вход блока режимов адресации.

и адресные входы ТЗУ и ПЗУ подключены к двунаправленной шине адреса отлаживаемой микроЭВМ, разрешающий вход блока режимов адресации и вто- .рые входы разрешейия доступа ТЗУ и ПЗУ подключены к выходу доступа к памяти отлаживаемой микроЭВМ, первые входы элементов И группы подклюJQ чены к выходам разрешения ввода, разрешения вывода, доступа к памяти, разрешения записи отлаживаемой микроэвм, выходы разрядов регистра останова соединены с вторыми вхо-г дами элементов И группы и с инверсными входами второго, элемента И,. . выход которого- соединен с первым входом второго элемента ИЛИ, второй - пятый входы которого соедине2Q ны с выходами первого - четвертого элементов И группы соответственно, выход второго элемента ИЛИ соединен с третьим входом первого элемента И, пятый - восьмой входы блока готов5 ности подключены соответственно к выходу -синхронизации микропроцессора отлаживаемой микроЭВМ к второму входу задания режима устройства, к выходу тактового генератора отлажи Баемой микроэвм, к выходу признака начала команды отлаживаемой микро- ЭВМ.

2, Ус-тройство по п. 1, о т л и - чающееся тем, что блок го- товности содержит триггер готовности, блок формирования единичного импульса, элемент ИЛИ-НЕ, первый и второй элементы И, элемент ИЛИ и элемент НЕ, причем первый -- третий входы элемента ИЛИ-НЕ являются первым -.третьим входами блока готовности соответственно, выход элемента ИЛИ-НЕ соединен с информационным входом триггера готовности, выход ко- ;торого является выходом блока готовности и соединен с первым входом блока формирования единичного сигнала, второй и третий входьт которого являются седьмым и четвертым входами блока готовности соответственно, -первый вход первого элемента И является пятым входом бло ка готовности, выход первого элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с входом синхронизации триггера готовности, S-вход которого соединен с выходом блока формирования единичного импульса, шестой вход блока готовности подключен к входу

5

0

5

0

элемента НЕ и второму входу первого элемента И, первый вход второго эле мента И является восьмым входом блока готовности, второй вход второго элемента И соединен с выходом элемента НЕ, выход второго элемента И соединен с вторым входом элемента ИЛИ.

3. Устройство по п. 1, о т л и - ч ающе ее я тем, что блок режимов адресации содержит восемь элементов И, два элемента ИЛИ, пять элементов НЕ и первый и второй тумблеры задания режима адресации, причем первая группа разрядов первого.входа блока режимов адресации подключена к входам первого элемента И, вторая группа разрядов первого входа блока режимов адресации подключена к входам второго элемента И, выход которого соединен с первым входом третьего элемента И и с входом первого элемента НЕ, выход первого элемента И соединен с входом второго элемента НЕ, вторым входом третьего элемента И и- первым входом четвертого элемента И, выходы первого и второго элементов НЕ соединены с первыми входами пятого и шестого элементов И соответственно, выход третьего элемента И соединен с первым входом первого элемента ИЛИ, выход которого сое- 9-

инен с первым входом седьмого элемента И, вход третьего элемента НЕ и второй вход седьмого элемента И под- ключены к первому тумблеру задания режима адресации, второй тумблер задания режима адресации подключен к входу четвертого элемента НЕ и к вторым входам четвертого и шестого элементов И, выход третьего элемента НЕ соединен с вторым входом пятого элемента И и первым входом восьмого элемента И выход четвертого элемента НЕ соединен с в торыми входами первого элемента ИЛИ и восьмого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, выход пятого элемента И соединен с третьим входом четвертого элемента И, второй вход блока режимов адресации подключен к входу пятого элемента НЕ, к третьему входу седьмого элемента И и к четвертому входу четвертого элемента И, выход пятого элемента НЕ соединен с . третьим входом второго элемента ИЛИ, выходы седьмого элемента И, четвер- того элемента И и второго элемента

ИЛИ являются первым, вторым и третьим выходами блока режимов адресации соответственно.

50

J52

фиг. 2

26

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отладки микроЭВМ | 1986 |

|

SU1432531A1 |

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ МИКРОЭВМ | 1990 |

|

RU2015540C1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

Изобретение относится к области вычислительной техники и может быть использовано для настройки, отладки и проверки работы специализированных микроэвм. Целью изобретения являет- ,ся расширение функциональных возможностей за счет возможности производить останов по адресу в зависимости от типа выполненного httiKpo3BM цикла. Устройство содержит коммутатор управления шиной данных, блок прямого доступа к памяти, магистральный усилитель, блок индикации, коммутатор, регистр ввода, блок готовности, два элемента И, два элемента ИЛИ, схему сравнения, регистр останова, группу элементов И, блок режимов адресации, постоянное запоминающее устройство, тумблерное запрминающее устройство. 2 З.П..Ф-ЛЫ, 5 ил., 1 табл. с S сл to 4ib vj 00 a

Qlovaffo

останов. S Hot/ам циклеSbifJ - Q

останов. 8 fffft/ам/гд мот/

SlHX.rf:sff

.5

Составитель В.Ванюхин Редактор Л.Аараменко Техред Э.Чюю-1ар Корректор И.Муска

Заказ 4127/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.„ д. 4/5

Производственно-полиграфическое пре,Ц1рийтие9 г, Ужгород, ул. Проектная, 4

| Патент США № 4308581, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Зеленко Г., Панов В., Попов С | |||

| Отладочный модуль микроЭВМ | |||

| - Радио, 1983, № | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-07-30—Публикация

1985-01-17—Подача