Предлагаемое изобретение относится к вычислительной технике и может быть использовано для построения многоканальных и многопроцессорных вычислительных систем (ВС) с использованием некоторого ресурса памяти общего пользования.

Известно устройство для сопряжения, вычислительных машин, содержащее блоки сопряжения, коммутаторы, блоки захвата шин диспетчера, информационные шины, шину диспетчера, блоки адаптеров абонентов, блоки служебных триггеров коммутатора (1). Известное устройство излишне сложно, имеет большое время и сложную процедуру доступа к данным.

Наиболее близким по технической сущности к предлагаемому является многоканальное устройство для обмена данными между модуляциями вычислительной системы, содержащее каналы 1,.., (количество которых равно количеству модулей ВС). каждый из которых содержит четыре триггера, первый, третий и второй элементы НЕ, первый - четвертый, шестой, пятый, седьмой, восьмой, восьмой элементы И, второй, первый и третий элементы ИЛИ. первый, третий, второй и четвертый элементы задержки, два формирователя импульсов, четыре элемента И НЕ. два блока буферной памяти четыре счетчика, две схемы сравнения, дешифратор, вход сигнала опроса канала, выход сигнала опроса канала, информационные вход и выход канала, выход сигнала разрешения запроса канала прерывания канала, вход сигнала запроса канала, линию запроса устройства, шину запрета устройства, шину стробирования устройства, шину ответа устройства, шину адреса, устройства, шину данных устройст

сл

00

о

00

ва(2). Известное устройство принято за прототип.

Недостатком известного устройства является большое время пересылки данных от одной ЭВМ к другой, узкие функциональные возможности из-за отсутствия циклического приоритета доступа для исключения столкновений, раздельный (по каналам ЭВМ) ресурс ЗУ, большая аппаратная избыточность.

Целью изобретения является уменьшение времени обращения к памяти устройства.

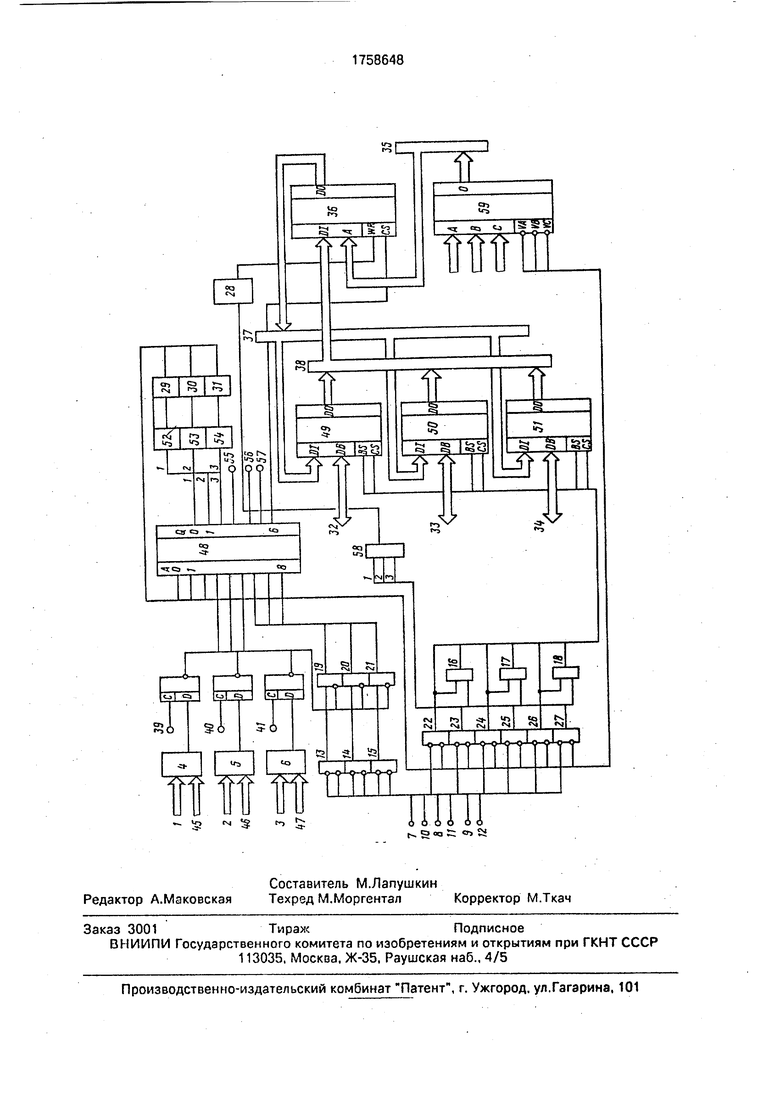

Устройство содержит первый 4, второй

5и третий 6 дешифраторы, с первого по шестой элементы ИЛИ 13-18, с первого по девятый элементы И 19-27, формирователь импульсов 28. первый 29, второй 30 и третий 31 элементы задержки, накопитель 36, первый 42, второй 43 и третий 44 D-триггеры, блок постоянной памяти 48, первый 49, второй 50 и третий 51 шинные формирователи, первый 52, второй 53 и третий 54 триггеры Шмидта, седьмой элемент ИЛИ 58, коммутатор 59.

На чертеже также обозначены первая 1, вторая 2 и третья группы адресных входов, первый 7, второй 8 и третий 9 входы чтения, первое 32, второе 33 и третье 34 группы информационных входов - выходов, адресные входы накопителя 35, информационные выходы 37 и входы 38 накопителя, первый 39, второй 40 и третий 41 входы обращения, первая 45, вторая 46 и третья 47 группы входов адреса страницы памяти, первый 55, второй 56 и третий 57 выходы сигналов готовности.

Устройство работает следующим образом. На шины 45, 46 и 47 поступает номер (адрес) страницы ОЗУ, в которой работает устройство. С выходов дешифраторов 4,5 и

6признак выборки адреса устройства поступает на входы D-триггеров 42,43 и 44, где фильтруется сигналами начала машинного цикла, поступающими по шинам 39, 40 и 41 и поступают на соответствующие адресные входы блока 48. Цель фильтрации сигналов выборка адреса исключение самовозбуждения блока 48 при быстрой смене сигналов на адресных шинах 1, 2 и 3 при смене текущего адреса, особенно при переходе шин адреса в выключенное состояние. Пары логических элементов 13 и 19,14 и 20,15 и 21 формируют признак обращения в режимах записи или чтения памяти, далее эти сигналы поступают на соответствующие адресные входы блока 48. Каждый из трех младших информационных разрядов блока 48 соединен со входом узла триггера Шмидта - элемент задержки, выход которого соединен с соответствующими младшими адресными входами блока 48, образуя положительную асинхронную обратную логическую связь. Таким образом, блок 48

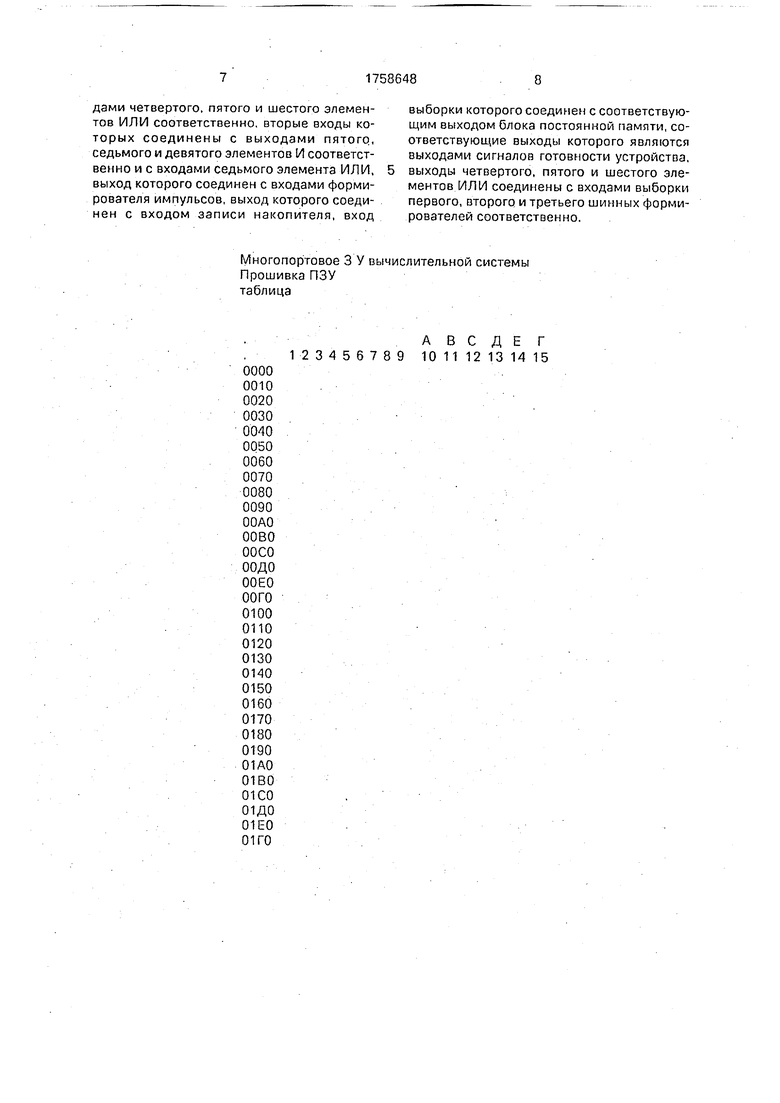

представляет собой и выполняет функцию определенной совокупности комбинаторных логических элементов и асинхронных триггеров, конкретные логические функции которых и электрические связи между кото0 рыми определяют таблицей прошивки блока 48 (смотри таблицу).

Шинные формирователи 49, 50 и 51 позволяют сформировать из двунаправленных шин 32, 33 и 34 данных две шины данных

5 устройства, информационную выходную шину 37 и информационную входную шину 38. У правление шинными формирователями осуществляется комбинаторным логическим узлом, выполненным на элементах

0 22 27, 16, 17 и 18, на входы которого

поступают сигналы разрешения канала с блока 48 и сигналы записи чтения памяти от микро ЭВМ,

Комбинация адресов устройства осуще5 ствляется коммутатором 59, управляемым сигналами разрешения канала, поступающими с блока 48.

Элемент58 и формирователь импульсов 28 формируют импульс записи для накопи0 теля 36.

Рассмотрим простейший случай обра- одной микро ЭВМ к устройству в режиме записи в память одного байта информации.

5 С шины 7 на адресные входы блока 48 поступает сигнал записи. При совпадении соответствующих обращений и записи на младшем (нулевом) выходе ПЗУ формируется сигнал разрешение канала 1, который

0 поступает также на младший (нулевой) адресный вход блока 48 для запоминания этого события. Сигнал разрешения канала 1 в сочетании с сигналом запись открывает шинный формирователь 49 в направлении

5 от шины 32 данных (микро ЭВМ) к входу 38 накопителя. Сигнал разрешения канала 1 открывает также коммутатор 59 в направлении от шины 1 адреса (микро ЭВМ) к входу 35 (накопителя). Логические элементы 23,

0 25, 27 и 28 формируют сигнал запись. Формирователь импульсов 28 формирует из длинного сигнала запись строб в накопитель расположенный гарантированно внутри сигнала запись. Режим чтения памяти

5 принципиально не отличается от режима записи памяти.

К данному устройству может быть подключена несколько микро ЭВМ (число которых принципиально не ограничено). Расширением вероятных конфликтных ситуаций, связанных с временным наложением циклов записи-чтения различных микро ЭВМ, работающих асинхронно, занят логический узел, выполненный на осноое блока постоянной памяти 48.

В общем виде механизм разрешения конфликтов таков. При обращении второй (номер условен) микро ЭВМ к устройству во время начавшегося цикла записи или чтения первой микро ЭВС второй микро ЭВМ по шине готовность выдается сигнал не готов, блокирующий вторую микро ЭВМ вплоть до окончания цикла записи или чтения первой микро ЭВМ, после чего вторая микро ЭВМ может продолжить свой цикл записи или чтения при условии, если за это время (ее блокировки) не поступил запрос на обслуживание от микро ЭВМ с большим приоритетом доступа (рейтинг уровня приоритетов доступа заложен в блок 48, в противном случае вторая микро ЭВМ остается заблокированной вплоть до окончания цикла записи или чтения третьей микро ЭВМ.

При одновременном обращении двух и более микро ЭВМ разрешение доступа выдается микро ЭВМ с большим уровнем приоритета доступа.

Дешифраторы 4, 5 и 6 и блок 48 могут быть реализованы на микро ЭВМ схеме типа 556РТ5, триггеры Шмидта 52, 53 и 54 на микросхеме типа 133ТЛ2, элементы задержки на любом логическом элементе (например, на микросхеме 133 ЛИ1), шинные формирователи 49, 50 и 51 на микросхеме типа 585ВА85, накопитель 36 на микросхемах типа 541РУ1.

Формирователь импульсов 28 может быть выполнен на микросхеме типа 133ПГЗ.

Коммутатор 59 может быть выполнен на трех микросхемах типа 585ВА86, соответствующие выходы которых объединены, а вход разрешения каждого канала соединен с выводом 11 микросхемы.

Технико-экономические показатели предлагаемого устройства обеспечиваются сокращением обьема аппаратной части, сокращением времени доступа (для микро ЭВМ данное устройство является транспарентной частью его собственной памяти), быстрым разрешением конфликтов и неограниченностью объема памяти и числа микро ЭВМ, подключенных к данному устройству.

Формула изобретения Многопортовое запоминающее устройство, содержащее первый, второй и третий дешифраторы, с первого по шестой элементы ИЛИ, с первого по шестой элементы ИЛИ, с первого по девятый элементы И, формирователь импульсов первый, второй

и третий элементы задержки, накопитель, входы первых групп первого, второго и третьего дешифраторов являются соответствующими адресными входами устройства, первые входы первого, второго и третьего элементов И соединены соответственно с выходами первого, второго и третьего элементов ИЛИ, отличающееся тем, что, с целью уменьшения времени обращения к

0 памяти устройства, в него введены первый, второй и третий D-триггеры, блок постоянной памяти, седьмой элемент ИЛИ. первый, второй и третий триггеры Шмидта, первый, второй и третий шинные формирователи и

5 коммутатор, выходы которого соединены с адресными входами накопителя, информационные входы и выходы которого соединены соответственно с информационными выходами и информационными входами пер0 вых групп соответственно первого, второго и третьего шинных формирователей, информационные входы вторых групп которых являются соответствующими информационными входами-выходами устройства, информаци5 онные входы первой, второй и третьей групп коммутатора соединены с входами первых групп первого, второго и третьего дешифраторов, входы вторых групп которых являются соответствующими адоесными входами

0 выбора страницы памяти устройства, выходы первого, второго и третьего дешифрато- ров соединены соответственно с информационными входами первого, второго и третьего D-триггеров, входы синхрони5 зации которых являются соответствующими входами обращения устройства, выходы первого, второго и третьего D-триггеров соединены с соответствующими адресными входами блока постоянной памяти и с вто0 рыми входами первого, второго и третьего элементов И соответственно, выходы которых соединены со старшими адресными входами блока постоянной памяти, соответствующие младшие выходы которого соеди5 пены с входами первого, второго и третьего триггеров Шмидта, выходы которых соединены с входами элементов задержки, выходы которых соединены с соответствующими младшими адресными входами блока посто0 янной памяти, с управляющими входами коммутатора и с первыми входами элемен- тов-И с четвертого по девятый соответственно, вторые входы которых соединены соответственно с входами первого, второго

5 и третьего элементов ИЛИ и являются соответствующими входами записи и чтения устройства, выходы четвертого, шестого и восьмого элементов И соединены с управляющими входами первого, второго и третьего шинных формирователей и с первыми входами четвертого, пятого и шестого элементов ИЛИ соответственно, вторые входы которых соединены с выходами пятого, седьмого и девятого элементов И соответственно и с входами седьмого элемента ИЛИ, выход которого соединен с входами формирователя импульсов, выход которого соединен с входом записи накопителя, вход

выборки которого соединен с соответствующим выходом блока постоянной памяти, соответствующие выходы которого являются выходами сигналов готовности устройства, выходы четвертого, пятого и шестого элементов ИЛИ соединены с входами выборки первого, второго и третьего шинных формирователей соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство управления процессом приготовления многокомпонентных смесей | 1989 |

|

SU1688127A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения многоканальных и многопроцессорных вычислительных систем. Цалью изобретения является уменьшение времени обращения к памяти устройства. Устройство содержит первый, второй и третий дешифраторы, с первого по седьмой элементы ИЛИ, с первого по девятый элементы И, формирователь импульсов, первый, второй и третий элементы задержки, накопитель, первый, второй и третий D-триггеры, блок постоянной памяти, первый, второй и третий шинные формирователи, первый, второй и третий триггеры Шмидта, коммутатор. Устройство позволяет обеспечить асинхронную независимость процессов доступа к индивидуальным и общим секторам памяти вычислительной системы с быстрым разрешением конфликтов обращения. 1 ил., 1 табл.

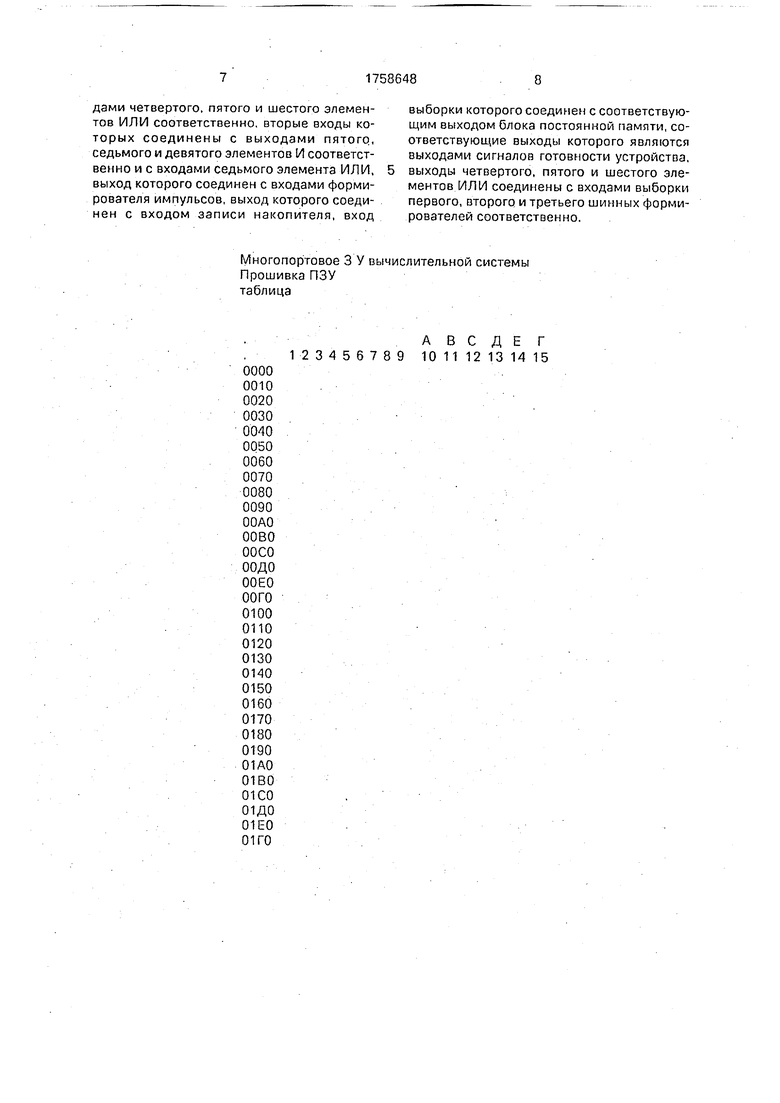

Многопортовое 3 У вычислительной системы

Прошивка ПЗУ

таблица

123456789

0000 0010 0020 0030 0040 0050 0060 0070 0080 0090 ООАО ООВО

оосо оодо

ООЕО

оого

0100

0110

0120

0130

0140

0150

0160

0170

0180

0190

01АО

01ВО

01СО

01ДО

01ЕО

01 ГО

А В С Д Е Г 10 11 12 13 14 15

| Устройство для сопряжения вычислительных машин | 1983 |

|

SU1179361A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-30—Публикация

1990-04-06—Подача