Изобретение относится к вычислительной технике и может быть использовано для построения многомашинных вычислительных систем (сетей), объединяющих ЭВМ разного типа и класса.

Известно устройство для сопряжения цифровых вычислительных машин с внешними устройствами, содержащее шифратор признаков обращения, счетчик состояний обмена с машиной, дешифратор состояний обмена с машиной, шифратор кода состояния обмена с машиной, блок регистров, дешифратор режима, триггеры, блок дешифрации команд и адресов обращения, счетчик состояния обмена с внешним устройством, дешифратор состояния обмена с внешним устройством, шифратор кода состояния обмена с внешним устройством, элемент ИЛИ [1].

Известное устройство сложно, не может быть адаптировано к любому типу ЭВМ и ее шинам и имеет низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому устройству является устройство для сопряжения каналов ввода-вывода с внешними устройствами, содержащее блоки связи с каналом, блоки связи с внешними устройствами, группы канальных входов-выходов, группы входов-выходов внешних устройств, линии связи, причем каждый блок связи с каналом содержит узел приемников, узел передатчиков, узел трансляции, узел формирования последовательности сигналов выборки, узел коммутации и узел управления выборкой, каждый блок связи с внешними устройствами содержит узел передатчиков и узел приемников [2].

Известное устройство функционально жестко ориентировано, не может быть оперативно (программно) адаптировано к любому типу и классу ЭВМ, имеет сепаратированную шину ввода-вывода ЭВМ.

Целью изобретения является повышение функциональной гибкости, оперативной адаптированности к любому типу и классу ЭВМ при минимальном времени перестройки путем предоставления пользователю унифицированной внешней шины, управляемой программно и могущей иметь любую желаемую архитектуру, протокол поддержки которой обеспечивается программно (выбирается из меню пользователя).

Цель достигается тем, что в устройство сопряжения ЭВМ с внешними устройствами, содержащее узел коммутации, узел управления выборкой, группу блоков связи с внешними устройствами, состоящих каждый из узла передатчиков и узла приемников, причем выходы узла передатчиков соединены с соответствующей выходной шиной внешних устройств, входы узла приемников соединены с соответствующей входной шиной внешних устройств, шину ЭВМ, введены первый и второй буферные формирователи, в блок связи с внешними устройствами группа параллельных регистров, а узел управления выборкой содержит постоянную память, первый и второй дешифраторы, причем двунаправленная шина данных ЭВМ соединена с соответствующими входами-выходами узла коммутации, входы и выходы которого соединены с соответствующими линиями двунаправленной шины данных устройства, соединенной с соответствующими параллельными входами данных параллельных регистров группы и соответствующими входами узла приемников каждого блока связи с внешними устройствами группы, параллельные информационные выходы каждого параллельного регистра группы соединены с входами узла передатчиков соответствующего блока связи с внешними устройствами группы, выходная шина внешних устройств и входная шина внешних устройств каждого блока связи с внешними устройствами группы соединены с линиями соответствующей двунаправленной шины внешних устройств, шина адреса ЭВМ соединена с соответствующими входами первого буферного формирователя, младшие разряды выхода которого соединены с адресными входами первого и второго дешифраторов, средний разряд выхода - с первым инверсным входом управления второго дешифратора, старшие разряды выхода - с соответствующими адресными входами постоянной памяти, линии записи и чтения шины управления ЭВМ соединены соответственно с первым и вторым входами второго буферного формирователя, первый выход которого соединен с входом управления узла коммутации и соответствующим адресным входом постоянной памяти, второй выход - с соответствующим адресным входом постоянной памяти, нулевой разряд выхода которой соединен с входом выборки узла коммутации, первый разряд выхода - с первым инверсным входом управления первого дешифратора и прямым входом управления второго дешифратора, второй разряд выхода - с вторыми инверсными входами управления выборкой первого и второго дешифраторов, третий разряд выхода - с прямым входом управления первого дешифратора, выходы первого дешифратора соединены с входами синхронизации параллельных регистров группы, выходы второго дешифратора - с входами выборки узлов приемников соответствующих блоков связи с внешними устройствами, при этом узел передатчиков содержит группы инверторов с выходом типа "открытый коллектор" и две группы регистров, причем выход инверторов группы является входами узла передатчиков, выход каждого инвертора группы соединен с первым выводом соответствующего резистора первой группы, второй вывод которого соединен с соответствующим выходом узла передатчиков и первым выводом соответствующего резистора второй группы, вторые выводы резисторов второй группы соединены с источником напряжения питания устройства.

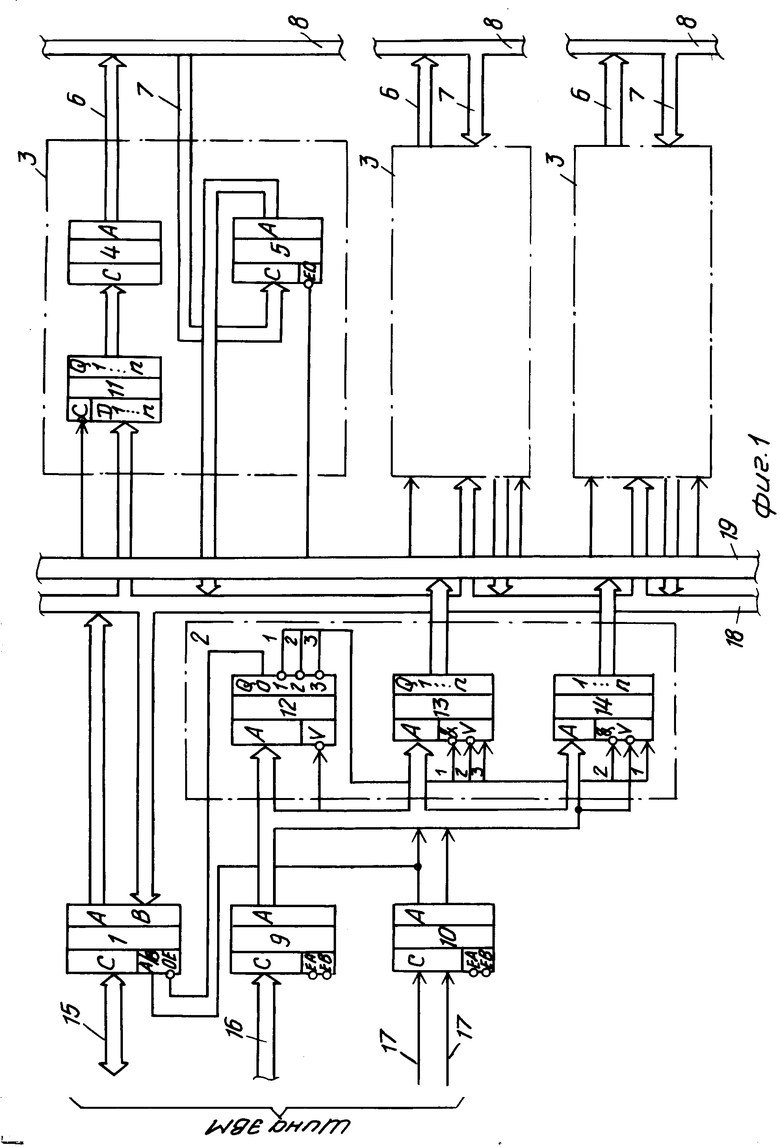

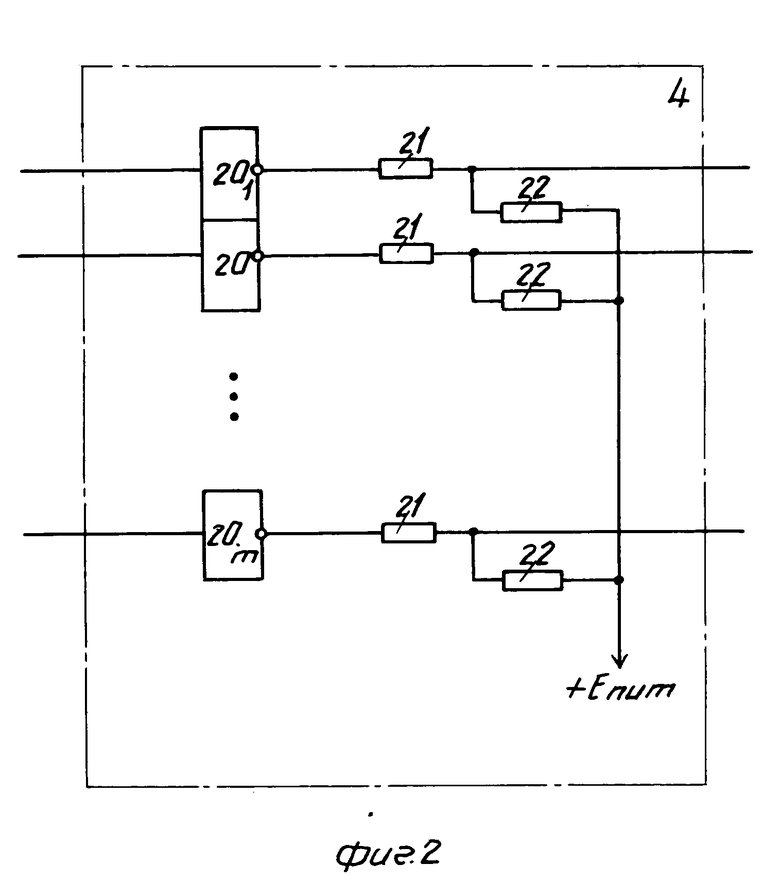

На фиг. 1 представлена схема устройства сопряжения ЭВМ с внешними устройствами; на фиг. 2 - схема узла передатчиков.

Устройство содержит узел 1 коммутации, узел 2 управления выборкой, блоки 3 связи с внешними устройствами, состоящие каждый из узлы 4 передатчиков и узла 5 приемников, причем выходы узла передатчиков соединены с соответствующей входной шиной 6 внешних устройств, входы узла приемников - с соответствующей входной шиной 7 внешних устройств, двунаправленные шины 8 внешних устройств, первый и второй буферные формирователи 9 и 10, параллельные регистры 11, постоянную память 12, первый и второй дешифраторы 13 и 14, двунаправленную шину 15 данных ЭВМ, шину 16 адреса ЭВМ, шину 17 управления ЭВМ, двунаправленную шину 18 данных устройства, шину 19 управления устройства. Двунаправленная шина 15 данных ЭВМ соединена с соответствующими входами-выходами узла 1 коммутации, выходы и входы которого соединены с соответствующими линиями двунаправленной шины 18 данных устройства, соединенными с соответствующими параллельными входами данных параллельных регистров 11 и соответствующими выходами узла 5 приемников блоков 3 связи с внешними устройствами. Параллельные информационные выходы параллельных регистров 11 соединены с соответствующими входами узла 4 передатчиков блока 3 связи с внешними устройствами. Выходная шина 6 внешних устройств и входная шина 7 внешних устройств блока 3 связи с внешними устройствами соединены с соответствующими линиями двунаправленной шины 8 внешних устройств. Шина 16 адреса ЭВМ соединена с соответствующими входами первого буферного формирователя 9, младшие разряды выхода которого соединены с соответствующими адресными входами первого и второго дешифраторов 13 и 14, средний разряд выхода - с первым инверсным входом управления второго дешифратора 14, старшие разряды выходов - с соответствующими адресными входами памяти 12. Линии записи и чтения шины 17 управления ЭВМ соединены соответственно с первым и вторым входами второго буферного формирователя 10, первый выход которого соединен с входом управления узла коммутации и соответствующим адресным входом памяти 12, второй выход - с соответствующим адресным входом памяти 12. Нулевой разряд выхода последней соединен с входом выборки узла 1 коммутации, первый разряд выхода - с первым инверсным входом управления первого дешифратора 13 и прямым входом управления второго дешифратора 14, второй разряд выходов - с вторыми инверсными входами управления выборкой первого и второго дешифраторов 13 и 14, третий разряд выходов - с прямым входом управления первого дешифратора 13. Выходы первого дешифратора 13 соединены соответственно с входом синхронизации параллельного регистра 11 каждого блока 3 связи с внешними устройствами, выходы второго дешифратора 14 - с входами выборки узла 5 приемников каждого блока 3 связи с внешними устройствами.

Узел 4 передатчиков (фиг. 2) содержит группу инверторов 20 с выходом типа "открытый коллектор", причем входы инверторов 20 являются входами узла 4 передатчиков, выход каждого инвертора 20 соединен с первым выводом соответствующего резистора 21 первой группы, второй вывод которого соединен с соответствующим выходом узла 4 передатчиков и первым выводом соответствующего резистора 22 второй группы. Вторые выводы этих резисторов соединены с источником напряжения питания устройства.

Устройство работает следующим образом.

В соответствии с функциональным назначением устройство посредством шины ЭВМ подключается к главной ЭВМ, шины 8 образуют внешние шины требуемой архитектуры. Шина ЭВМ имеет стандартное членение на шину 15 данных (двунаправленную), шину 16 адреса и шину 17 управления (на фиг. 1 показана только часть линий шины управления - запись в память и чтение памяти). С главной ЭВМ устройство функционирует следующим образом.

Поступающий с шины ЭВМ код адреса (выполняемой функции), пройдя через буферный формирователь 9, далее дешифруется в памяти 12 и двух дешифраторах 13 и 14. На память 12 поступает старшая часть кода адреса, определяющая включение устройства в шину 15 данных (нулевой разряд выхода памяти 12), выборку необходимого дешифратора 13 или 14 (первый, второй и третий разряды выходов памяти 12). На адресные входы дешифраторов 13 и 14 поступает младшая часть кода адреса с шины ЭВМ. С дешифратора 13 на соответствующий блок 3 поступает сигнал (строб), разрешающий запись в регистр 11 слова данных с шины ЭВМ через узел 1. С дешифратора 14 на соответствующий блок 3 поступает сигнал выборки узла 5 и на шину 15 слова данных через узел 1. Вектор коммутации узла 1 определяется сигналом чтения шины 17 управления. Таким образом, функциональное назначение укрупненных узлов устройства следующее.

Узел 1 коммутирует поток данных для записи в блок 3 и для чтения из блока 3. Буферные формирователи 9 и 10 образуют физический буфер шин 16 и 17 адреса и данных соответственно. Узел 2 формирует сигналы управления и выборки блоков 3. Блоки 3 образуют физические порты внешних устройств. Блок 3 содержит оперативное ЗУ на регистре 11 и физический стык с шиной 8, выполненный на узлах 4 и 5 передатчиков и приемников соответственно. Со стороны главной ЭВМ режимы записи и чтения блока 3 по времени разделены и осуществляются соответственно подачей строба на вход синхронизации регистра 11 и выборки на соответствующий вход узла 5.

Простота блока 3 обуславливает особенности графика шин 8 и обеспечивается соответствующим построением узла 4 передатчиков. Узел 4 выполнен на инвертоpах 20 с открытым коллектором (стоком и т.п.) и резисторах 21 и 22. При подаче на вход узла 4 логической "1" на выходе формируется логический "0". При подаче логического "0" на входы узла 4 последний переходит в так называемое "третье" (высокоимпедансное) состояние, однако на шине 8 поддерживается логическая "1" резисторами 22. Резисторы 21 позволяют одновременно подключить к (возможно) двунаправленной шине 8 узел 4 передатчиков и узел 5 приемников. Таким образом, показанное на фиг. 2 построение узла 4 позволяет одновременно включать в двунаправленную шину 8 внешних устройств как узел 4 передатчиков, так и узел 5 приемников. В режиме разделения шины 8 по времени узел 4 передатчиков отключается записью в регистр 11 слова данных с нулевым содержанием.

Структурно устройство содержит К блоков 3 разрядностью М, однако на уровне представления устройства (главной ЭВМ) каждая линия шины 8 самостоятельна и имеет лишь условный адрес (К, М). Таким образом, главная ЭВМ оперирует со множеством элементарных портов линий шины 8 внешнего устройства, причем каждая линия шины 8 может быть "построена" как для записи (передачи), так и для чтения (приема). Кроме того, совокупности линий шины 8 могут быть оперативно сгруппированы (на уровне представления главной ЭВМ) по архитектурному признаку интерфейса, произвольность построения которого позволяет адаптировать шину 8 к любому типу терминала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение функциональной гибкости, оперативной адаптированности к любому типу и классу ЭВМ при минимальном времени перестройки. Устройство содержит узел коммутации, два буферных формирователя, постоянную память, два дешифратора, группу блоков связи с внешними устройствами, каждый из которых содержит параллельный регистр, узел приемников и узел передатчиков. Изобретение предоставляет пользователю унифицированную внешнюю шину, управляемую программно и могущую иметь любую желаемую архитектуру, протокол поддержки которой обеспечивается также программно. 2 ил.

УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ УСТРОЙСТВАМИ, содержащее узел коммутации, узел управления выборкой, группы блоков связи с внешними устройствами, состоящие каждый из узла передатчиков и узла приемников, выходы узла передатчиков соединены с соответствующей выходной шиной внешних устройств, входы узла приемников соединены с соответствующей входной шиной внешних устройств, отличающееся тем, что, с целью повышения функциональной гибкости, оперативной адаптированности к любому типу и классу ЭВМ при минимальном времени перестройки, в него введены первый и второй буферные формирователи, в блок связи с внешними устройствами группа параллельных регистров, а узел управления выборкой содержит постоянную память, первый и второй дешифраторы, причем двунаправленная шина данных ЭВМ соединена с соответствующими входами-выходами узла коммутации, выходы и входы которого соединены с соответствующими линиями двунаправленной шины данных устройства, соединенной с соответствующими параллельными входами данных параллельных регистров группы и соответствующими выходами узла приемников каждого блока связи с внешними устройствами группы, параллельные информационные выходы каждого параллельного регистра группы соединены с входами узла передатчиков соответствующего блока связи с внешними устройствами группы, выходная шина внешних устройств и входная шина внешних устройств каждого блока связи с внешними устройствами группы соединены с линиями соответствующей двунаправленной шины внешних устройств, шина адреса ЭВМ соединена с входами первого буферного формирователя, младшие разряды выхода которого соединены с адресными входами первого и второго дешифраторов, средний разряд выхода - с первым инверсным входом управления второго дешифратора, старшие разряды выхода - с соответствующими адресными входами постоянной памятью, линии записи и чтения шины управления ЭВМ соединены соответственно с первым и вторым входами второго буферного формирователя, первый выход которого соединен с входом управления узла коммутации и соответствующим адресным входом постоянной памяти, второй выход - с соответствующим адресным входом постоянной памяти, нулевой разряд выхода которой соединен с входом выборки узла коммутации, первый разряд выхода - с первым инверсным входом управления первого дешифратора и прямым входом управления второго дешифратора, второй разряд выхода - с вторыми инверсными входами управления выборкой первого и второго дешифраторов, третий разряд выхода - с прямым входом управления первого дешифратора, выходы первого дешифратора соединены с входами синхронизации параллельных регистров, группы выхода второго дешифратора соединены с входом выборки узлов приемников соответствующих блоков связи с внешними устройствами, узел передатчиков содержит группу инверторов с выходом типа открытый коллектор и две группы резисторов, входы инверторов группы являются входами узла передатчиков, выход каждого инвертора группы соединен с первым выводом соответствующего резистора первой группы, второй вывод которого соединен с соответствующим выходом узла передатчиков и первым выводом соответствующего резистора второй группы, вторые выводы резисторов второй группы соединены с источником напряжения питания устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1983 |

|

SU1179352A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-11-30—Публикация

1991-01-16—Подача