Изобретение относится пычнсли- тельной техш1ке и может быть использовано для сопряжения двух устройств обработки данных.

Цель изобретния - повыи1ение быстродействия устройства за счет совмещения во времени приема и передачи информации.

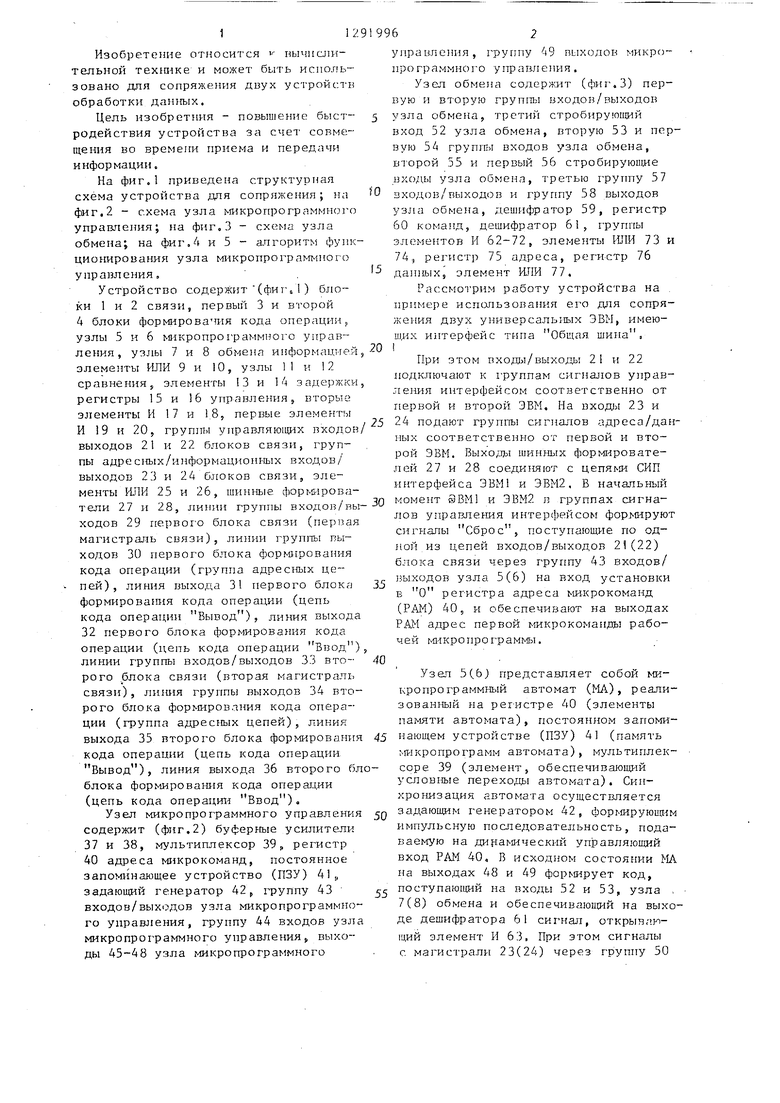

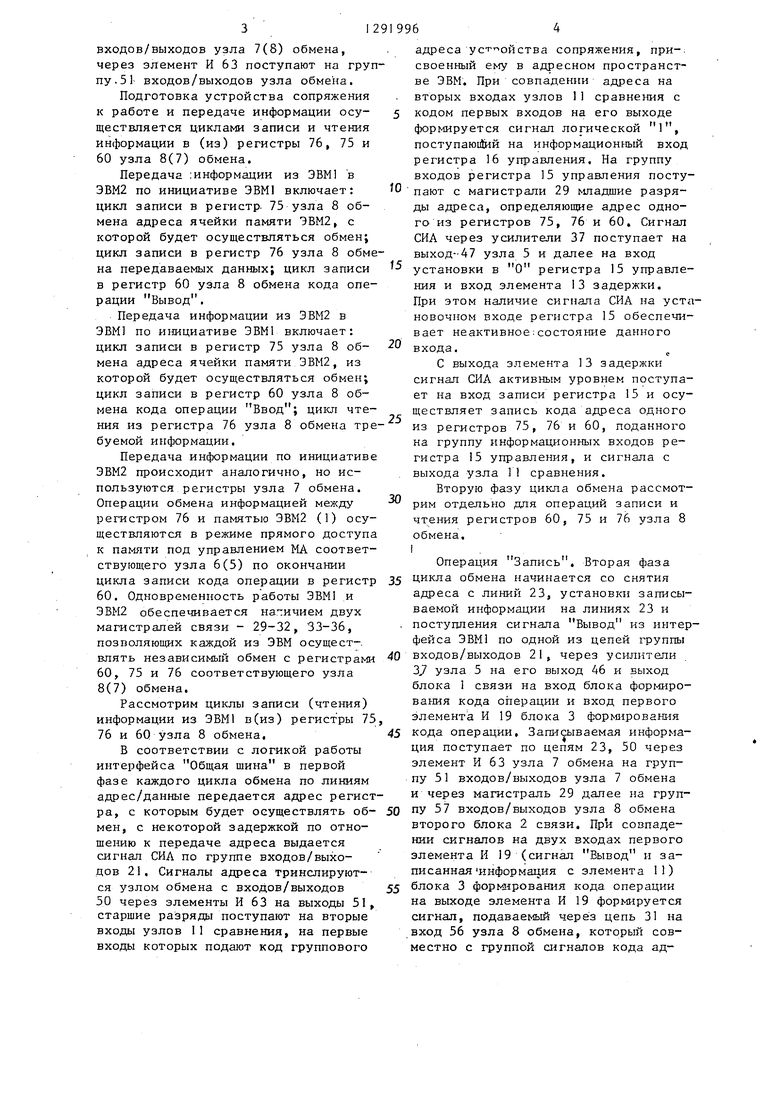

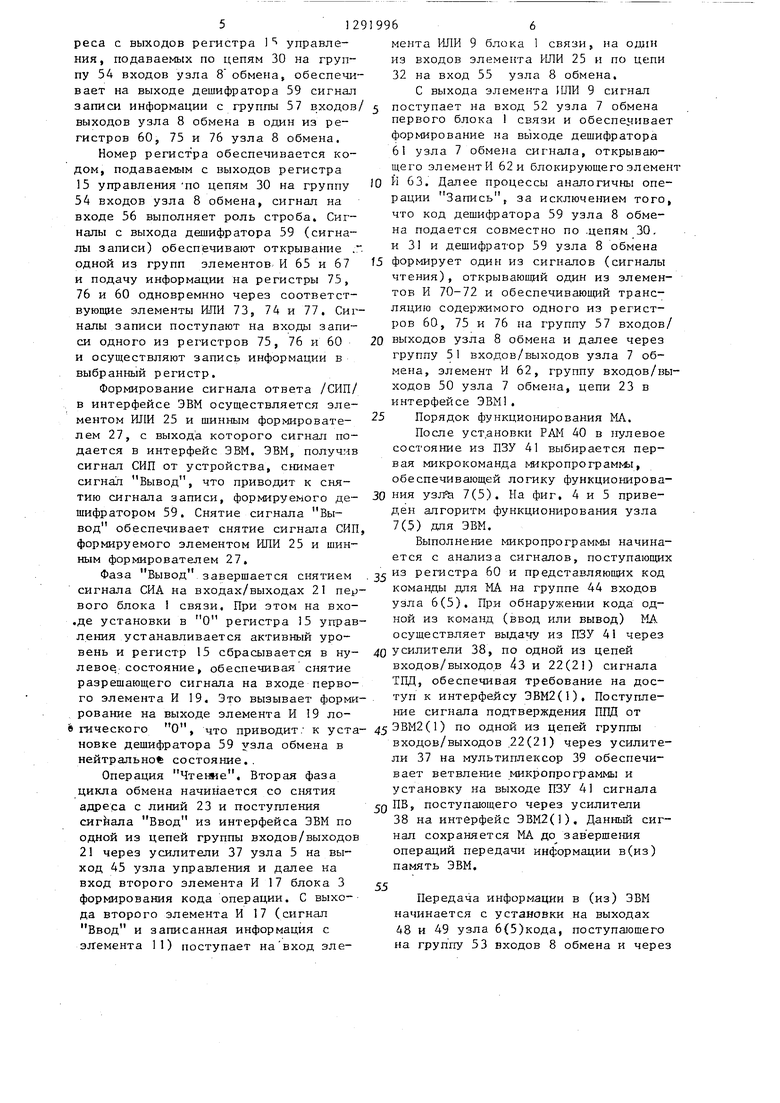

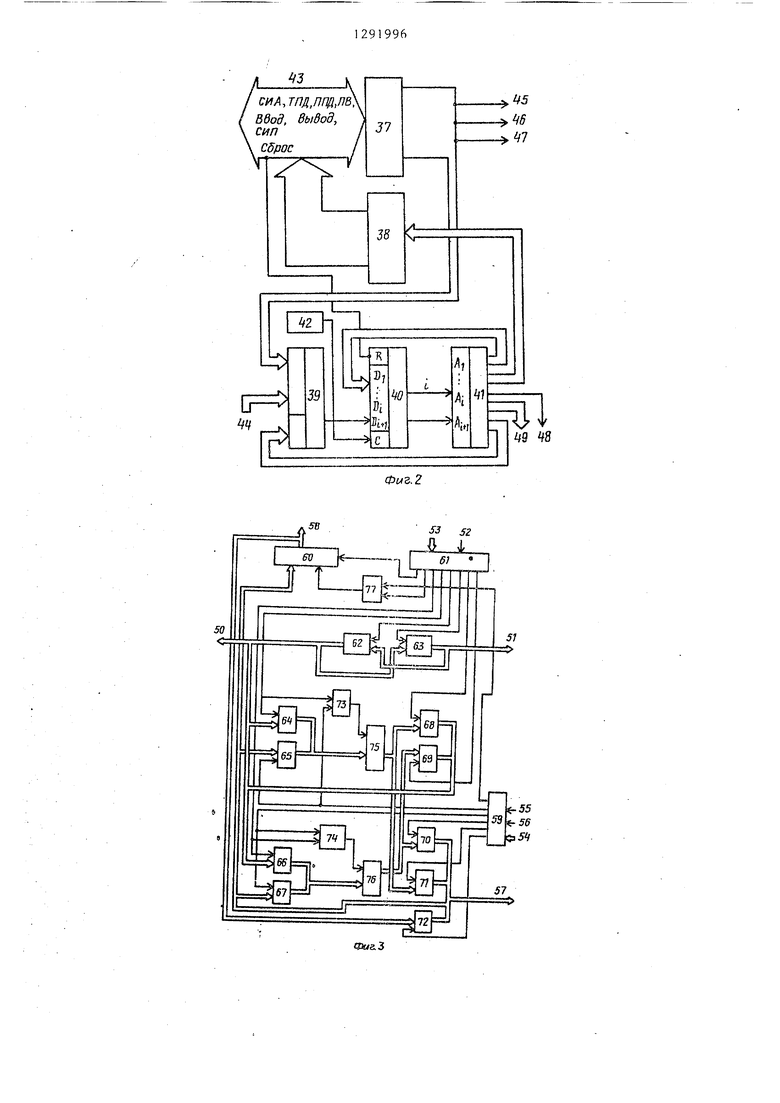

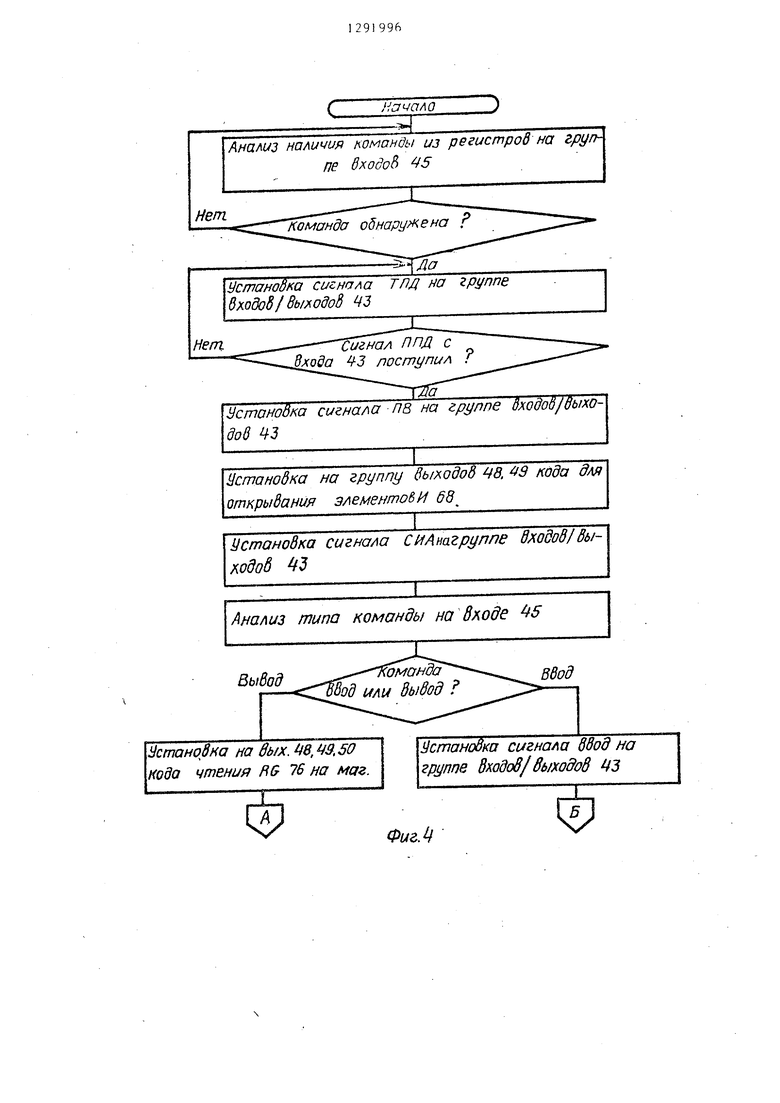

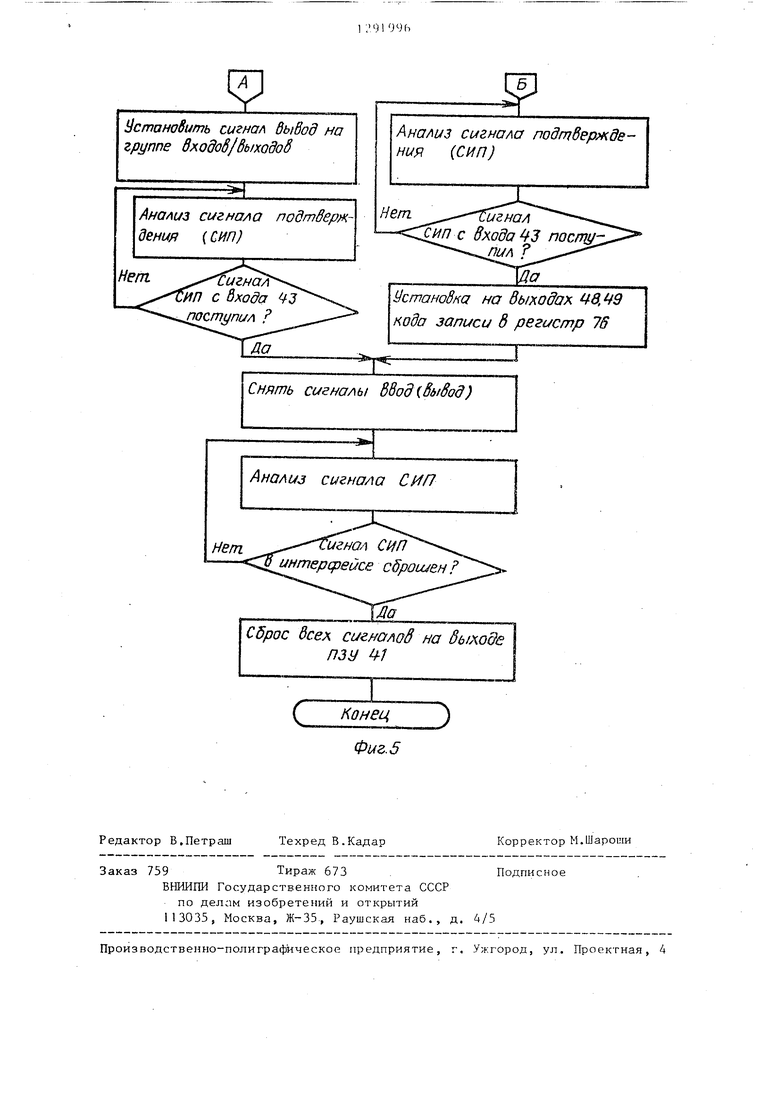

На фиг.1 приведена структурная схема устройства для сопряжения; на фиг.2 - схема узла NftiKponporpaMMHoro управления; на фиг.З - схема узла обмена; на фиг,4 и 5 - апгоритм функционирования узла микропрограм 5ного управления.

Устройство содержит (фиг-tl) блоки 1 и 2 связи, первый 3 и второй 4 блоки формирова шя кода операции, узлы 5 и 6 микропрограммного управления, узлы 7 и 8 обмена информаш-гей элементы ИЛИ 9 и 10, узлы 11 и 12 сравнения, элементы 13 и 14 задержки регистры 15 и 16 управления, вторые элементы И 17 и i.S, первые элементы И 19 и 20, группы управляющих входов выходов 21 и 22 блоков связи, группы адресных/информационных входов/ выходов 23 и 24 блоков связи, элементы ИЛИ 25 и 26, шинга)1е формирователи 27 и 28, линии группы входов/выходов 29 первог О блока связи (первая магистраль связи), ли}1ии группы выходов 30 первого блока формирования кода операции (группа адресных цепей), линия выхода 31 первого блока формирования кода операции (цепь кода операции Вывод), линия выхода 32 первого блока формирования кода операции (цепь кода операции Ввод) линии группы входов/выходов 33 ВТО- рого блока связи (вторая магистраль связи), линия группы выходов 34 второго блока формирования кода операции (группа адресных цепей), линия выхода 35 второго блока формирования кода операции (цепь кода операции Вывод), линия выхода 36 второго бл блока формирования кода опершдии (цепь кода операции Ввод),

Узел микропрограммного управления содержит (фиг,2) буферные усилители 37 и 38, мультиплексор 39, регистр 40 адреса микрокоманд, постоянное запом11нающее устройство (ПЗУ) 41., задающий генератор 42,, группу 43 входов/выходов узла микропрограммного уцравления, группу 44 входов узла микропрограммного управления выходы 45-48 узла микропрограммного

0

5

5

0 0

управления, группу 49 выходов микропрограммного управления.

Узел обмена содержит (фиг .З) первую и вторую группы входов/выходов узла обмена, третий стробирующий вход 52 узла обмена, вторую 53 и первую 54 групггы входов узла обмена, второй 55 и первый 56 стробирующие Бходь узла обмена, третью группу 57 входов/выходов и группу 58 выходов узла обмена, деш} фратор 59, регистр 60 команд, дешифратор 61, группы злементов И 62-72, элементы ИШ 73 и 74, periicTp 75 адреса, регистр 76 , элемент ИЛИ 77.

Рассмотрим работу устройства на примере испш1ьзования его для сопряжения двух универсалыых ЭВМ, имеющих интерфейс типа Общая шина. I

При этом входы/выходь 2 и 22 подключают к группам сигналов управления интерфейсом соответственно от первой и второй ЭВМ, На вход) 23 и 24 подают группы сигналов адреса/данных соответственно от первой и второй ЭВМ. Выходы шинных форм1-1ровате- лей 27 и 28 соединяют с цепями СИП интерфейса ЭВМ1 и ЭВМ2. В начальный момент SBM1 и ЭВМ2 л группах сигналов управлеьшя интерфейсом фор мруют сигналы Сброс, поступающие по одной из цепей входов/выходов 21(22) блока связи через группу 43 входов/ 5ыходов узла 5(6) на вход установки в О регистра адреса микрокоманд (РАМ) 40, и обеспечивают на выходах РАМ адрес первой микрокоманды рабочей микропрограммы.

0

5

Узел 5(Ь) представляет собой мк- кропрограммн1)1Й автомат (МА), реализованный на регистре 40 (элементы памяти автомата), постоянном запоминающем устройстве (ПЗУ) 41 (память микропрограмм автомата), мультиплексоре 39 (элемент, обеспечивающий условные переходы автомата). Синхронизация автомата осуществляется

задающим генератором 42, формируюиим импульсную последовательность, подаваемую на ди|-1амический управляющий вход РАМ 40, В исходном состоянии МА на выходах 48 и 49 формирует код,

поступающий на входы 52 и 53, узла , 7(8) обмена и обеспечиваюцщй на выходе дещифратора 61 сигнал, открывающий элемент И 63. При этом сигналы с магистрали 23(24) через группу 50

31

входов/выходов узла 7(8) обмена, через элемент И 63 поступают на группу. 51- входов/выходов узла обмена.

Подготовка устройства сопряжения к работе и передаче информации осу- ществляется циклами записи и чтения информации в (из) регистры 76, 75 и 60 узла 8(7) обмена.

Передача :информации из ЭВМ1 в ЭВМ2 по инициативе ЭВМ включает: цикл записи в регистр. 75 узла 8 обмена адреса ячейки памяти ЭВМ2, с которой будет осуществляться обмен; цикл записи в регистр 76 узла 8 обме

на передаваемых данных; цикл записи в регистр 60 узла 8 обмена кода операции Вывод.

Передача информации из ЭВМ2 в ЭВМ по инициативе ЭВМ1 включает: цикл записи в регистр 75 узла 8 обмена адреса ячейки памяти ЭВМ2, из которой будет осуществляться обмен; цикл записи в регистр 60 узла 8 обмена кода операции цикл чтения из регистра 76 узла 8 обмена требуемой информации.

Передача информации по инициативе ЭВМ2 происходит аналогично, но используются регистры узла 7 обмена. Операции обмена информацией между регистром 76 и памятью ЭВМ2 (1) осуществляются в режиме прямого доступа к памяти под управлением МА соответствующего узла 6(5) по окончании цикла записи кода операции в регистр 60. Одновременность работы ЭВМ1 и ЭВМ2 обеспечивается натичием двух магистралей связи - 29-32, 33-36, позволяющих каждой из ЭВМ осущест-. влять независимый обмен с регистрами 60, 75 и 76 соответствующего узла 8(7) обмена.

Рассмотрим циклы записи (чтения) информации из ЭВМ1 в (из) регист ры 75 76 и 6Q узла 8 обмена,

В соответствии с логикой работы интерфейса Общая шина в первой фазе каждого цикла обмена по линиям адрес/данные передается адрес регистра, с которым будет осуществлять об- мен, с некоторой задержкой по отношению к передаче адреса выдается сигнал СИЛ по группе входов/выходов 21. Сигналы адреса тринслируют- ся узлом обмена с входов/выходов 50 через элементы И 63 на выходы 51, старшие разряды поступают на вторые входы узлов I1 сравнения, на первые входы которых подают код группового

5

О

20

25

30

-5

45

0

35

0

5

адреса устройства сопряжения, при-: своенный ему в адресном пространстве ЭВМ. При совпадении адреса на вторых входах узлов 11 сравнения с кодом первых входов на его выходе формируется сигнал логической 1, поступаюи1;ий на информационный вход регистра 16 управления. На группу входов регистра 15 управления поступают с магистрали 29 младшие разряды адреса, определяющие адрес одного из регистров 75, 76 и 60. Сигнал СИЛ через усилители 37 поступает на выход-47 узла 5 и далее на вход установки в О регистра 15 управления и вход элемента 13 задержки. При этом наличие сигнала СИЛ на установочном входе регистра 15 обеспечивает неактивное:состояние данного входа.

С выхода элемента 13 задержки сигнал СИА активным уровнем поступает на вход записи регистра 15 и осуществляет запись кода адреса одного из регистров 75, 76 и 60, поданного на группу информационных входов регистра 15 управления, и сигнала с выхода узла 1 сравнения.

Вторую фазу цикла обмена рассмотрим отдельно для операций записи и чтения регистров 60, 75 и 76 узла 8 обмена. I

Операция Запись. Вторая фаза цикла обмена начинается со снятия адреса с линий 23, установки записываемой информации на линиях 23 и поступления сигнала Вывод из интерфейса ЭВМ1 по одной из цепей группы входов/выходов 21, через усилители 37 узла 5 на его выход 46 и выход блока 1 связи на вход блока фор1-1иро- ваьшя кода операции и вход первого элемента И 19 блока 3 фop 0 poвaния кода операции. Записываемая информация поступает по цепям 23, 50 через элемент И 63 узла 7 обмена на группу 51 входов/выходов узла 7 обмена и через магистраль 29 далее на группу 57 входов/выходов узла 8 обмена второго блока 2 связи. При совпадении сигналов на двух входах первого элемента И 19 (сигнал Вывод и записанная информао ия с элемента 11) блока 3 форьа€рования кода операции на выходе элемента И 19 формируется сигнал, подаваемый через цепь 31 на вход 56 узла 8 обмена, который совместно с группой сигналов кода ад

реса с выходов регистра 1 управления, подаваемых по цепям 30 на группу 54 входов узла 8 обмена, обеспечивает на выходе дешифратора 59 сигнал записи информации с группы 57 входов выходов узла 8 обмена в один из регистров 60, 75 и 76 узла 8 обмена,

Номер регистра обеспечивается кодом, подаваемым с выходов регистра 15 управления ПО цепям 30 на группу 54 входов узла 8 обмена, сигнал на входе 56 выполняет роль строба. Сигналы с выхода дешифратора 59 (сигналы записи) обеспечивают открывание . одной из групп элементов И 65 и 67 и подачу информации на регистры 75, 76 и 60 одновремнно через соответствующие элементы ИЛИ 73, 74 и 77, Сигналы записи поступают на входы записи одного из регистров 75, 76 и 60 и осуществляют запись информации в выбранный регистр.

Формирование сигнала ответа /СИП/ в интерфейсе ЭВМ осуществляется элементом ИЛИ 25 и шинным формирователем 27, с выхода которого сигнал подается в интерфейс ЭВМ. ЭВМ, получив сигнал СИП от устройства, С1шмает сигнал Вывод, что приводит к снятию сигнала записи, формируемого дешифратором 59. Снятие сигнала Вывод обеспечивает снятие сигнала СИП формируемого элементом ИЛИ 25 и шинным формирователем 27.

Фаза Вывод .завершается снятием сигнала СИА на входах/выходах 21 первого блока 1 связи. При этом на вхо- .де установки в О регистра 15 управ

Выполнение микропрограммы начин ется с анализа сигналов, поступающи из регистра 60 и представляющих код команды для МА на группе 44 входов узла 6(5), При обнаружении кода одной из команд (ввод или вывод) МА осуществляет выдачу из ПЗУ 41 через

Ленин устанавливается активный уровень и регистр 15 сбрасывается в ну- 40 усилители 38, по одной из цепей левое, состояние, обеспечивая снятиевходов/выходов 43 и 22(21) сигнала

разрешающего сигнала на входе первого элемента И 19. Это вызывает формирование на выходе элемента И 19 лоТПД, обеспечивая требование на доступ к интерфейсу ЭВМ2(1), Поступление сигнала подтверждения ПГЩ от

ё гического О, что приводит/ к уста- 45ЭВМ2(1) по одной из цепей группы

входов/выходов .22(21) через усилит ли 37 на мультиплексор 39 обеспечивает ветвление микропрограммы и установку на выходе ПЗУ 41 сигнала Q ПВ, поступающего через усилители

новке дешифратора 59 узла обмена в нейтрально состояние..

Операция Чтение, Вторая фаза цикла обмена начинается со снятия адрера с линий 23 и поступления сигйала Ввод из интерфейса ЭВМ по одной из цепей группы входов/выходо 21 через усилители 37 узла 5 на выход 45 узла управления и далее на вход второго элемента И 17 блока 3 формирования кода операции. С выхода второго элемента И 17 (сигнал Ввод и записанная информация с элемента 11) поступает на вход эле

мента ИЛИ 9 блока 1 связи, на один из входов элемента ИЛИ 25 и по цепи 32 на вход 55 узла 8 обмена,

С выхода элемента ИЛИ 9 сигнал поступает на вход 52 узла 7 обмена первого блока 1 связи и обеспечивает формирование на выходе дешифратора 61 узла 7 обмена сигнала, открывающего элемент И 62 и блокирующего элемент И 63. Далее процессы аналогичны операции Запись, за исключением того, что код дешифратора 59 узла 8 обмена подается совместно по .цепям 30. и 3 и дешифратор 59 узла 8 обмена формирует один из сигналов (сигналы чтения), открывающий один из элементов И 70-72 и обеспечивающий трансляцию содержимого одного из регистров 60, 75 и 76 на группу 57 входов/ выходов узла 8 обмена и далее через группу 51 входов/выходов узла 7 обмена, элемент И 62, группу входов/выходов 50 узла 7 обмена, цепи 23 в интерфейсе ЭВМ1.

Порядок функционирования МА.

После установки РАМ 40 в 1гулевое состояние из ПЗУ 41 выбирается первая микрокоманда №1кропрограммы, обеспечивающей логику функционирова- ния узл%1 7(5). На фиг, 4 и 5 приведен алгоритм функционирования узла 7(5) для ЭВМ.

Выполнение микропрограммы начинается с анализа сигналов, поступающих из регистра 60 и представляющих код команды для МА на группе 44 входов узла 6(5), При обнаружении кода одной из команд (ввод или вывод) МА осуществляет выдачу из ПЗУ 41 через

усилители 38, по одной из цепей входов/выходов 43 и 22(21) сигнала

усилители 38, по одной из цепей входов/выходов 43 и 22(21) сигнала

ТПД, обеспечивая требование на доступ к интерфейсу ЭВМ2(1), Поступление сигнала подтверждения ПГЩ от

45ЭВМ2(1) по одной из цепей группы

входов/выходов .22(21) через усилители 37 на мультиплексор 39 обеспечивает ветвление микропрограммы и установку на выходе ПЗУ 41 сигнала Q ПВ, поступающего через усилители

38 на интерфейс ЭВМ2(1). Данный сигнал сохраняется МА до зав ершения операций передачи информации в(из) память ЭВМ.

55

Передача информации в (из) ЭВМ начинается с установки на выходах 48 и 49 узла 6(5)кода, поступающего на групггу 53 входов 8 обмена и через

элемент ИЛИ 10 на вход 52 узла 8 обмена и обеспечивающего на выходе дешифратора 61 сигнал, открывающий элемент И 68. При этом содержимое регистра 75 адреса поступает через группу 50 входов/выходов на магистраль 24(23) адрес/данные ЭВМ2(1) и интерпретируется ЭВМ как адрес. Затем на выходе ПЗУ 41 формируется сигнал СИА, поступающий через усилители 38, входы/выходы 43, 22(21) в интерфейс ЭВМ2(1).,

После этого МА через мультиплексор 39 осуществляет анализ типа команды на группе 44 входов и переходит к выполнению операций Ввод ил Вывод, При обнаружении команды Вывод МА на выходах 48 и 49 формирует код, обеспечиваюгдий на выходе дещифратора 61 снятие сигнала, открывающего элементы И 68 и появлени сигнала, открывающего элемент И 69. При этом содержимое регистра 76 данных поступает через группу 50 вхо- дов/выходов узла 8(7) обмена в ЭВМ2(1). Одиовремнно из ПЗУ 41 чере усилители 38 на входы/выходы 43 и далее через входы/выходы 22(21) в ЭВМ выдается сигнал Вывод, затем МА осуществляет ожидание от ЭВМ2(1) сигнала подтверждения СИП, который поступает от ЭВМ2(1) по одной из цепей через усилители 37 к мультиплексору 39, При поступлении сигнала СИП МА снимает с выхода ПЗУ 41 ранее сформированный сигнал Вывод на выход 43, а на выходах 48 и 49 формирует код, обеспечивающий появление на выходе дешифратора 61 сигнала сброса регистра 60 команд.

Затем МА осуществляет анализ сигнала СИП, поступающего из интерфейса ЭВМ2, При сбросе в интерфейсе ЭВМ сигнала СИП МА осуществляет сброс всех ранее сформированных сигналов (конец выполнения цикла) и возвращается в исходное состояние. При обнаружении на входах 44 команды Ввод МА осуществляет выдачу из ПЗУ через усилители 38 сигнала Ввод на входы/выходы 22(21) устройства. Поступление от ЭВМ сигнала СИП, по одной из, цепей входов/выходов 21(22) через усилители 37 к мультиплексору 39 означает, что на цепи 24(23) подана требуемая информация. МА осуществляет формирование на выходе ПЗУ 41 и на выходах 48 и

91996 49

8

кода, «обеспечивающего снятие сигнала, открывающего элемент И 68, и появление на выходе дешифратора 61 сигнала, открывающего элемент 5 И 66 и ,через элемент ИЛИ 74 запись - вающего в регистр 76 данных информацию с входов/выходов 50, Далее МА завершает выполнение операции Ввод аналогично завершению опера- 0 ции Вывод,

Одновременно с рассмотренными операциями, выполняемыми первой ЭВМ, аналогичным образом осуществляется операция обмена по иьшциативе второй ЭВМ. При этом передача информации между блоками связи осуществляется по магистрали 33, управляющая информация передается по линиям 34- 36, т,е. осуществляется одновремен- 20 ная передача информационных слоев от первой и второй ЭВМ,

5

Ф

ормула изобретения

Устройство для сопряжения двух электронно-вычислительных машин (ЭВМ), содержащее два блока связи, причем каждый блок связи содержит узел микропрограммного управления, узел сравнения, при этом группы командных входов/выходов узла микропрограммного управления первого и второго блоков связи подключены к входным/выходным управляющим шинам

первой и второй ЭВМ соответственно, первые группы входов узлов сравнения первого и второго блоков связи подключены к группам адресных выходов первой и второй ЭВМ соответственно,отличающееся тем, что, с целью увеличе1-шя быстродействия, в него введены два блока формирования кода операции, каждый из которых содержит регистр управления,

элемент задержки, два элемента И, элемент ИЛИ, шинный формирователь, а в каждый блок введены узел обмена и элемент ИЛИ, .при этом первые группы информационных входов/выходов узлов обмена первого и второго блоков связи подключены к адресным/ информационным входным/выходным шинам первой и второй ЭВМ соответственно, выходы шинных формз рователей:

первого и второго блоков формирования кода операции подключены к син- ровходам первой и второй ЭВМ соответственно, причем вторая груцпа информационных входов/выходов узла обмена первого блока связи соединена с третьей группой информационных Bxo LioB/выходов узла обмена второго блока связи, вторая группа информационных входов/выходов узла обмена второго блока связи соединена с третьей группой информационных входов/выходов узла обмена первого ,блока связи, группа информационных Ыыходов регистра управления первого блока формирования кода операции соединена с первой группой информационных входов узла второг о блока связи, группа информационных выходов регистра управления второго блока формирования кода операции соединена с первой группой информа- цион11ых входов узла обмена первого блока связи, выход первого элемента И первого блока форь-ирования кода операции соединен с .первым входом элемента ИЛИ первого блока формирования кода операции и с первым стро бирующим входом узла обмена второго блока связи, выход первого элемента И второго блока формирования кода операции соединен с первым входом элемента ИЛИ второго блока формиро- ваш-1Я кода операции и с первым стро бирующим входом узла обмена первого блока связи, выход второго элемента И первого блока формирования кода операции соединен с первым входом элемента ИЛИ первого блока связиj с ВТОРЫМ входом элемента Ш1И первого блока формирования кода операции и с вторым стробирующимвходом узла обмена второго блока связи, выход второго элемента И второго блока форь ирования кода операции соединен с первым входом элемента ИЛИ второго блока связи, с вторым входом элемента ИЛИ второго блока формирования кода операции и с вторым стробирующим входом узла обмена первого блока связи, при этом старшие и младшие разряды информационных вы- ходов второй группы информационных входов/выходов y3Jla обмена первого блока связи соединены с второй группой входов узла сравнения первого блока связи и с группой информационных входов регистра управления пернего блока формирования кода операции соответственно, старшие и штад- шие разряды информационных выходов второй группы информационных входов выходов узла обмена второго блока связи соединены с второй Группой

5

91996 10

13ХОДОВ узла сравнения второго блока связи и с группой информационных входов регистра упраапения второго блока формгфования кода операции

5 соответственно, выходы узлов сравне- . ПИЯ первого и второго блоков евязи соединенгз с информационными входами peiTiCTpoB управления первого и второго блоков формирования кода опе0 рггции соответственно, первые и вторые кодовые выходы узлов микропро- ; граммного управления первого и второго блоков связи соединены с первыми входами Первого и второго элемен 5 тов И первого и второго блоков фор- -1ирования кода операции соответственно, третьи выходы узлов микропрограммного управления первого и вто- - рого блоков связи соединеШ) с вхо0 даш элементов задержки и нулевыми входами регистров управления первого и второго блоков фop иpoвaния код,ов операций соответственно, причем в каждом блоке связи группа информационных, выходов узла обмена соед1.{не на с-группой кодовых входов узла микропрограммного управления, группа кодовых выходов которого соединена; с второй группой информа

30 ционных входов уз.ла обмена, третий стробирующий выход которого соединен с 13ЫХОДОМ элемента ИЛИ, второй вход которого соединен с четвертым кодовым выходом узла NDiKponpoграммного

35 управления, при этом в калсдом блоке формирования кода операций выход элемента задержки соединен с входом записи регистра управления, информационный выход которого соединен с

.40 вторыми входами первого и второго эле1« ентов И, выход элемента ИЛИ соединен с входами шинного формирователя , причем узел обмена содержит два дешифратора, регистр команд, регистр

45 адреса, регистр данных, одиннадцать групп элементов И, три элемента ИЛИ, причем группа выходов элементов И первой, второй и третьей групп и группа первых входов элементов И чет50 вертой, пятой и шестой групП образуют первую группу информационных входов/выходов узла обмена, группа .выходов элемента И четвертой группы .и первые входы элементов И первой

55 группы образуют вторую группу информационных входов/выходов узла обмена, группа выходов элементов И седьмой, восьмой и девятой групп, первые входы элементов И десятой и одиннад

111

цатой групп и группа информационны входов регистра команд образуют третью группу информационных входов выходов узла обмена, группа информационных выходов регистра команд соединена с первыми входами элементов И девятой группы и образуют группу информационных выходов узла обмена, группы информационных входов первого и второго дешифраторов образуют первую и вторую группы информационных входов узла обмена соответственно, первый, второй стро бирующие входы первого дешифратора и стробирующий вход второго дешифра Tiopa являются первым, вторым и третьим стробируюшими входами узла обмена соответственно, при этом первый выход второго дешифратора соединен с нулевым входом регистра команд, вход записи которого соединен с выходом первого элемента ИЛИ, первый и второй входы которого соединены соответственно с первым выходом первого дешифратора и с вторым выходом второго дешифратора, третий выход которого соединен с вторыми входами элементов И пятой группы и с первым входом второго элемента ИЛИ, выход которого соединен с входом записи регистра адреса, группа информационных входов

которого соединена с выходами элементов И пятой группы и элементов И десятой группы, вторые входы коO

996

12

торых соединены с вторым входом второго элемента ИЛИ и с вторым выходом первого дешифратора, третий выход ко-, торого соединен с вторыми входами элементов И одиннадцатой группы и с первым входом третьего элемента ИЛИ, выход которого соединен с входом записи регистра данных, группа информационных входов которого соединена с группой выходов элемента И одиннад- . цатой группы и элементов И шестой группы, вторые входы которых соединены с вторым входом третьего элемент а.,ИЛИ и с четвертым выходом вто5 рого дешифратора, пятый выход которого соединен с первыми входами элементов И второй группы, первые входы которых соединены с 1 руппой выхо дов регистра адреса и с первыми входами элементов И восьмой группы, вторые входы которых соединены с четвертым выходом первого дешифратора, пятый выход которого соединен с первыми входами элементов И седьмой группы, вторые входы которых соединены с группой выходов регистра данных и первыми входами элементО5з И третьей группы, вторые входь которых соединены с шестым выходом второго

дешифратора, седьмой и восьмой выходы кот орого соединены с вторыми входами элементов И первой и четвертой групп соответственно, шестой выход первого дешифратора соединен с вто5 рыми входами элементов И девятой группы.

0

5

«к

СИ А, ТПЛ,ПП,ПВ

ввод, вывод, СИП

Сброс

pq ц

39

Lb

5

37

in

7

п

9 ад

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ | 1991 |

|

SU1837306A1 |

| Устройство для сопряжения двух электронно-вычислительных машин | 1988 |

|

SU1594555A2 |

| Устройство для сопряжения электронно-вычислительных машин | 1988 |

|

SU1580385A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для сопряжения двух ЭВМ | 1990 |

|

SU1798793A1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

Изобретение относится к вычислительной техгшке и может быть использовано для сопряжения двух устройств обработки данных. Целью изобретения является повышение быстродействия устройства за счет совмещения по времени приема и передачи информации при двунаправленном обмене информации между устройства1-1И обработки данных. Устройство содержит два блока связи, два блока формирования кода операции. 5 ил. сл с CD СО О5

51

Анализ HOAWU команды из регистров на г-руппе бходоВ 5

J

Непг

Установка сигнала ТПД на группе ВмдоЫВы одоК 3

Нет

Сигнал ППД с ,S.wda 3 поступил

стаиобка сигнала пз на дхоооо/выхо- дав 43

У с та над ка на группу вь/ходод 8. 9 кода для открыдания элементов И 68

Остановка сигнала СИАшгрдппе вводов/8&/ мдоб Ч

/Анализ типа команды на Входе 5

Вывод

станодна на вых. 8,В.50 кода чтений 8G- 76 на маг.

Ввод

станоВка сигнала ввод на гдуппе ЬмдоВ/ бымдоВ 3

ФигМ

А

v

-Эа

Остановить сигнал BbtBod на группе в)(одо8/дыходоб

Анализ сигнала подтверждения (СИП)

Анализ сигнала подтверждения (СИП)

Иет „. сигнаА

сип с входа 3 посщу:

УАУ/1

1а

Установка на Выходах 8,9 кода записи в регистр 75

Снять сигналы ВВод(Вы8од)

Анализ сигнала СИП

„ сигнал СИП

интердзвисе сброшен/

Сброс дсех сигнОАод на Выходе ПЗУ 1

( Конец }

Редактор В.Петраш

Техред В.Кадар

Заказ 759Тираж 673

БНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35., Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Фиг. 5

Корректор М.Шароши Подписное

| Устройство для сопряжения двух элект-РОННыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809147A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-06-21—Подача