Изобретение относится (в основном) к базирующимся на микропроцессорах компьютерным системам и, в частности, к схеме сброса в исходное состояние таких компьютерных систем.

Целью изобретения является расширение области применения за счет обеспечения возможности микропроцессору i 486 работать в компьютере, который первоначально работал с микропроцессором i 386.

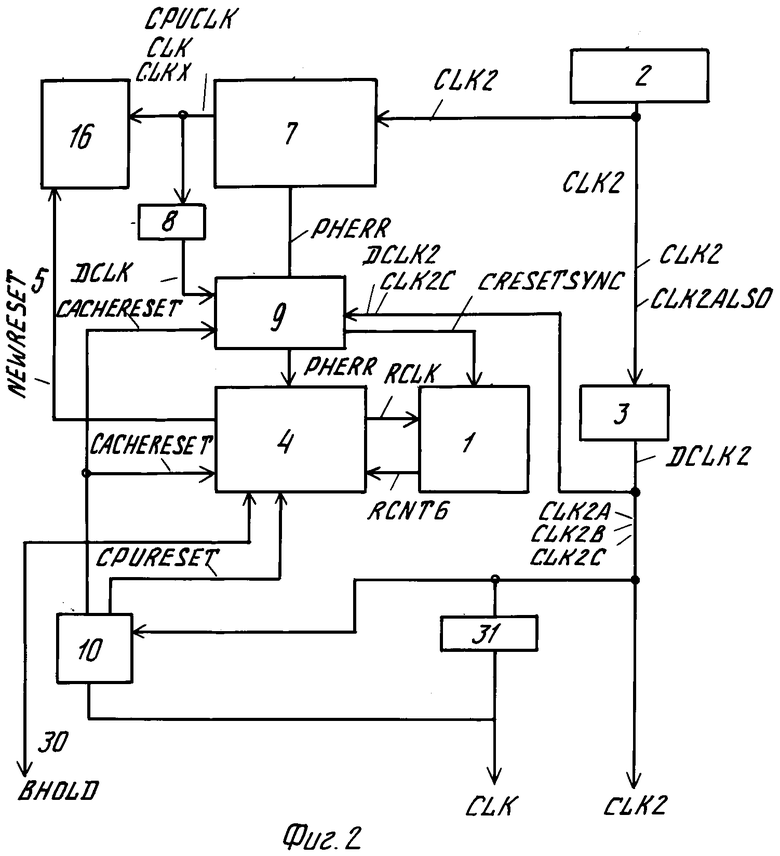

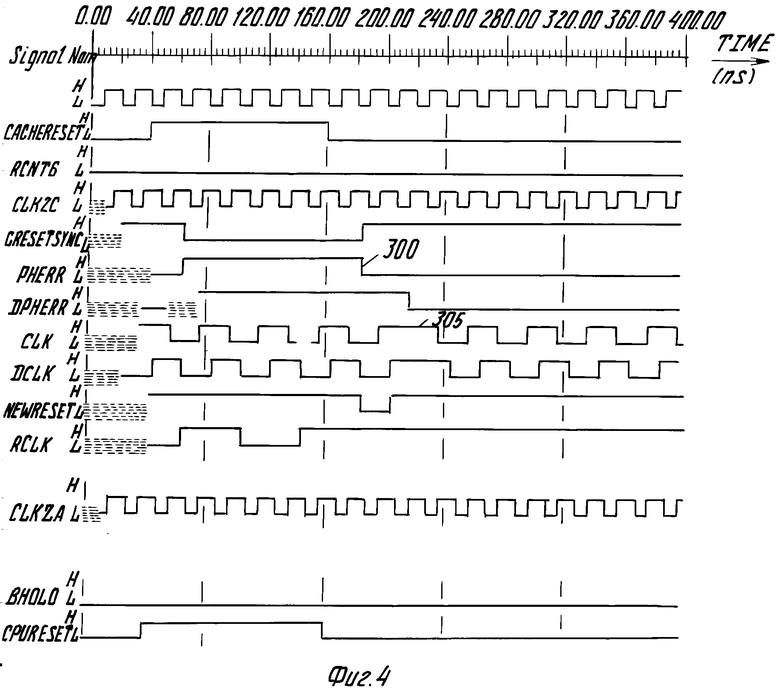

На фиг. 1 представлена блок-схема компьютерной системы; на фиг.2 - блок-схема сброса, являющаяся частью компьютерной системы; на фиг.3 - тактовая диаграмма, иллюстрирующая работу схемы сброса, когда нет фазового рассогласования; на фиг.4 - тактовая диаграмма, иллюстрирующая работу схемы сброса, когда имеет место фазовое рассогласование; на фиг.5 - тактовая диаграмма, имеющая ось "сжатого времени" и иллюстрирующая работу схемы сброса.

На фиг.1 и 2 показаны синхронизирующий элемент 1, генератор 2 тактовых импульсов, элемент 3 задержки, блок 4 регенерации сигналов сброса, выход 5 "Новый сигнал сброса" блока 4, вход 6 сброса блока 4, блок 7 коррекции фазового несовпадения, элемент 8 задержки, блок 9 обнаружения несовпадения фаз, блок 10 формирования сигналов сброса, выход 11 блока 10, блок 12 управления и синхронизации шины, выход 13 блока 7, вход 14 сброса микропроцессора, локальная шина 15 центрального процессорного устройства, микропроцессор 16, буфер 17, адресная шина 18, шина 19 данных, шина 20 управления, устройство 21 фиксации, буферирования и декодирования, планарная шина 22 ввода-вывода, периферийное устройство 23, локальная шина 24 системы, память 25 с контроллером, буфер 26, гнезда 27 для микроканалов, центральный арбитражный блок 28, контроллер 29 прямого доступа, выход 30 сигнала блокировки, делитель 31 частоты.

Схема сброса работает следующим образом. Когда на компьютер подается питание или когда блок 10 получает команду создать импульс сброса, он создает исходный импульс сброса RESET. Исходный импульс сброса RESET поступает на регенерируемый сигнал сброса блок 4, который пропускает этот исходный импульс RESET на микропроцессор 16 по линии NEWRESET. Исходный импульс RESET (сброса) заставляет микропроцессор 16 выполнить внутреннюю операцию его сброса в исходное состояние. Этот исходный импульс RESET поступает также на блок 9.

Логика, встроенная в схему сброса, выполняет операцию деления на два на блоке 7 по тактовому сигналу CLKZ генератора 2, работающего с удвоенной (двукратной) частотой, чтобы микропроцессор 16 получал на свой вход тактовый сигнал CPUCLK однократной частоты. Затем блок 9 определяет, есть или нет фазового рассогласования между сигналом CPUCLK и сигналом RESET, вырабатываемым блоком 10. Сигнал RESET несет признак фазы внешнего тактового сигнала CLK однократной частоты. Наличие несовпадения фаз является обычным явлением при включении питания микропроцессора. Если обнаружено несовпадение фаз, то блок 7 исправляет фазу сигнала CPUCLK. Однако, когда фаза сигнала CPUCLK таким образом корректируется и смещается, оказывается нарушенной спецификация синхронизации Intel, касающаяся стабильности тактирования i 486 (по спецификации t1а стабильность равна 0,1% максимального изменения между смежными тактовыми импульсами CPUCLK).

Если необходимо выполнить корректирующее смещение фазы сигнала CPUCLK, то регенерирующий сигнал сброса блок 4 создает новый импульс сброса NEWRESET, который поступает на вход MPRESET микропроцессора 16, чтобы микропроцессор вернулся в исходное состояние. Другими словами, если по причине обнаружения фазового несовпадения необходимо сдвинуть фазу CPUCLK, то вход MPRESET микропроцессора 16 переводится в активное состояние и удерживает в нем полную длительность сигнала сброса (приблизительно 1 мс), тем самым устраняя все внутренние ошибки микропроцессора 16, вызванные погрешностью фазы сигнала CPUCLK.

Ниже приведены работа схем сброса, представленных на фиг.1 и 2, а также разнообразные сигналы, используемые схемой сброса, представленной на фиг.2. Выходные сигналы CPUCLKA, CPUCKLB и CPUCLKC на фиг.2 являются задержанными по времени тактовыми сигналами, порождаемыми тактовым сигналом CLKZ генератора 2. Эти сигналы применяются для компенсации временных задержек, порождаемых блоком 7. Элемент 3, применяемый для создания этих сигналов, обеспечивает минимальность отклонений от требований синхронности в остальной части системной схемы.

CLK и CLKX на фиг.2 являются дублированными версиями разделенного на два или однократной частоты сигнала CPUCLK, который используется для тактирования микропроцессора 16. DCLK является задержанной версией CPUCLK, причем сигнал DCLK является одним из входных сигналов блока 9. DPHERR является логическим сигналом, используемым блоком 7 для установки правильной фазы сигналов CPUCLK, CLK или CLKX. Выход PHERR переходит на низкий уровень (становится активным), если обнаруживается фазовое рассогласование между сигналами CPUCLK (представленным DCLK и RESET) и CACHERESET), поступающими на блок 9. Сигнал несовпадения фаз PHERR применяется в регенерирующем сигнал сброса блоке 4 для подачи активного (высокого уровня) сигнала NEWRESET на вход микропроцессора 16, чтобы возвратить микропроцессор в исходное состояние.

Как видно на фиг.1, центральный арбитражный блок 28 имеет выход BHOLD для запроса блокировки шины. Когда обнаружено упомянутое выше фазовое несовпадение, зависящее от временного согласования сигнала BHOLD, выход RCLK выдает импульс низкого уровня, отражающий состояние сигнала BHOLD (инвертированного). Сигнал BHOLD, подаваемый на регенерирующий сигнал сброса блок 4, используется в качестве сигнала таймера. В конкретном варианте осуществления изобретения, в котором сигнал CPUCLK имеет частоту 25 МГц, импульсы сигнала BHOLD появляются приблизительно каждые 15,6 мкс. Импульсы BHOLD порождают импульсы на выходе RCLK, регенерирующие сигнал сброса блока 4. Это действие увеличивает на единицу содержимое счетчика в синхронизирующем элементе 1 каждые (приблизительно) 15,6 мкс. Содержимое этого счетчика возрастает до показания 27 за приблизительно 1 мс, после чего битовый разряд 27 счетчика, соединенный с RCNT6, становится активным. Когда бит RCNT6 этого элемента становится активным, он деактивирует сигнал NEWRESET. Таким образом, устанавливается и управляется длительность импульса NEWRESET (новый сигнал сброса). Когда сигнал NEWRESET становится неактивным, микропроцессор 16 и остальная часть компьютерной системы входят в синхронизм и может начаться работа компьютерной системы.

Сигналы CRESETSYNC и RCNTSYVC используются логикой PAL схемы сброса, представленной на фиг.2. Альтернативно CRESETSYNC используется для обнуления содержимого счетчика до его исходного (нулевого) состояния.

В приведенном выше описании раскрыт способ сброса (в исходное состояние) микропрцессора. Такой способ используется в компьютерной системе, имеющей микропроцессор, который имеет вход "Сброс" и вход для тактирующего сигнала. Компьютерные системы, в которых этот способ реализован, способны генерировать сигнал сброса микропроцессора. Более конкретно раскрыт способ сброса микропроцессора в подобной системе, включающий в себя шаг обнаружения фазового несовпадения между названным тактовым сигналом и сигналом сброса. Способ также включает в себя шаг настройки фазы тактового сигнала, если обнаружено несовпадение, с тем, чтобы существенно минимизировалось это фазовое несовпадение. Способ также содержит шаг, на котором новый сигнал сброса подается на вход "Сброс" микропроцессора в том случае, если происходит настройка фазы тактового сигнала.

Выше даны описания устройства и способа для сброса (в исходное состояние) входа "Сброс" в построенной на микропроцессорах компьютерной системе. Устройство и способ определяют схему сброса, которая в одном из вариантов осуществления позволяет микропроцессору i 486 работать в компьютере, который первоначально предназначался для работы с микропроцессором i 386. Устройство и способ позволяют создать схему сброса, которая требует минимального изменения компьютера на микропроцессоре i 386, когда такой компьютер усовершенствует с помощью микропроцессора i 486. В одном из вариантов осуществления изобретения эти устройство и способ позволяют преодолеть трудности синхронизации сброса, которые появляются в компьютерной системе, когда предпринимается попытка модернизировать процессор заменой микропроцессора i 386 на i 486.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ОБРАБОТКИ ЗАПРОСОВ НА ДОСТУП К ШИНЕ | 1990 |

|

RU2067314C1 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2072553C1 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2068578C1 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| УСТРОЙСТВО ДЛЯ ОПТИМИЗАЦИИ ОРГАНИЗАЦИИ ДОСТУПА К ОБЩЕЙ ШИНЕ ВО ВРЕМЯ ПЕРЕДАЧИ ДАННЫХ С ПРЯМЫМ ДОСТУПОМ К ПАМЯТИ | 1991 |

|

RU2110838C1 |

| ДИНАМИЧЕСКИЙ ВОЛНОВОЙ КОНВЕЙЕРНЫЙ ИНТЕРФЕЙС И СПОСОБ ЕГО ПРИМЕНЕНИЯ | 2000 |

|

RU2213992C2 |

| ЦИФРОВОЙ КОМПЬЮТЕР С ВОЗМОЖНОСТЬЮ ПАРАЛЛЕЛЬНОГО ВЫПОЛНЕНИЯ ДВУХ И БОЛЕЕ КОМАНД | 1991 |

|

RU2109333C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ПРЯМОГО ДОСТУПА (DASD) ЕМКОСТЬЮ БОЛЬШЕ 528 МЕГАБАЙТ И СПОСОБ ЕГО ВОПЛОЩЕНИЯ ДЛЯ ПЕРСОНАЛЬНЫХ КОМПЬЮТЕРОВ | 1994 |

|

RU2155369C2 |

| СХЕМНОЕ УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДВУХ ИЛИ БОЛЕЕ КОМАНД В ЦИФРОВОМ КОМПЬЮТЕРЕ | 1991 |

|

RU2111531C1 |

| ПЛАТА РАСШИРЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1990 |

|

RU2009539C1 |

Изобретение относится (в основном) к базирующимся на микропроцессорах компьютерным системам и, в частности, к схеме сброса в исходное состояние таких компьютерных систем. Цель изобретения - расширение области применения. Для этого система содержит микропроцессор, блок формирования сигналов сброса, генератор тактовых импульсов, блок коррекции фазового несовпадения, блок обнаружения несовпадения фаз и блок регенерации сигналов сброса. Схема сброса обеспечивает возможность микропроцессору i 486 работать в компьютере, который первоначально работал с микропроцессором i 386. 5 ил.

КОМПЬЮТЕРНАЯ СИСТЕМА, содержащая микропроцессор, блок формирования сигналов сброса и генератор тактовых импульсов, отличающаяся тем, что, с целью расширения области применения, дополнительно содержит блок коррекции фазового несовпадения, блок обнаружения несовпадения фаз и блок регенерации сигналов сброса, выход которого соединен с входом сброса микропроцессора, тактовый вход которого соединен с тактовым входом блока обнаружения несовпадения фаз и выходом блока коррекции фазового несовпадения, тактовый вход которого соединен с выходом генератора тактовых импульсов, выход блока обнаружения несовпадения фаз соединен с входами управления коррекцией блока коррекции фазового несовпадения, и блок регенерации сигналов сброса, вход сигнала сброса которого соединен с выходом блока формирования сигналов сброса и входом сигнала сброса блока обнаружения несовпадения фаз.

| Персональные компьютеры фирмы "IBM" | |||

| Киев; Наукова думка, 1991. |

Авторы

Даты

1994-09-30—Публикация

1990-06-18—Подача