(54) УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| Устройство параллельно-последователь-НОгО АНАлОгО-цифРОВОгО пРЕОбРАзОВА-Ния C САМОКОНТРОлЕМ | 1979 |

|

SU815904A1 |

| Параллельно последовательный анало-гО-цифРОВОй пРЕОбРАзОВАТЕль C CAMOKOH-ТРОлЕМ | 1978 |

|

SU813770A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| ДВУХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2251209C2 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388989A2 |

| Устройство парафазного цифроаналогового преобразования с самоконтролем | 1976 |

|

SU668087A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

Изобретение относится к вычислительной технике.и может быть ис- пользовано для построения прецезион ных аналого-цифровых преобразовател в информационно-измерительных систе мах, устройствах автоматизированног контроля и управления. Известно 5Я: Тройство контроля пос ледовательного аналого-цифрового преобразователя (АЦП), содержащее два дополнительных разряда, из которых один подсоединен к плюсу эталонного источника, другой - к его минусу 1. Однако такое устройство имеет ни кое быстродействие, так как конт ль АЦП производится за два такта и дополнительно требуется источник отрицательного эталонного напряжения. Известен параллельно-последовательный АЦП, содержащий т-разрядную схему R-2R, переключатели, регистр, нуль-органы, дешифратор, генератор импульсов, распределитель тактов, триггеры, источники эталонных напряжений, элементы И, ИЛИ, НЕ, схему задержки, операционный усилитель 12J. Однако такое устройство имеет большой объем оборудования, невысокие быстродействие и достоверность контроля. Цель изобретения - повышение достоверности и быстродействияконтроля. Указанная цель достигается тем, что в устройство аналогр.-цифрового преобразования, содержащее т-разрядную резистивную матрицу R-2R с подключенными к ней даухпозиционными переключателями, управлякяцие входы срторых соединены с выходами регистра, (т+1)-ый резистор 2R резистивной матрицы R-2R подключен к выходу первогоключа, управляющий вход которого соединен с единичным выходом триггера,единичный вход которого подключен к выходу распределителя тактов и через элемент задержки - к первому входу элемента И, выход которого соединен со входом логического блока, а второй вход через элемент ИЛИ подключен к выходам двух блоков сравнения, первые входы которых соединены с шиноП измеряемого напряжения, второй вход первого блока сравнения подключен к выходу т-разрлдной резистивной

матрицы Rr2R, выход первого блока сравнения через дешифратор соединен со входами установки в О регистра, генератор импульсов, подключенный через, распределитель тактов ко входу регистра и нулевому входу триггера и входам триггера знака, выходы которого соединены с управ;ляннцими. входа зи второго и третьего ключей, через которые источники эталонного напряжения положительной и отрицательной полярности подключены к аналоговым входам двухпозидионных переключателей и входу первого ключа, введены четвертый и пятый ключи и дополнительная т-разрядная резистийная матрица R-2R, входы которой соединены с выходами двухпозиционных переключателей, выход со вторым входом второго блока сравнения, (т4-1)-ый резистор 2R дополнительной резистивной матрицы R-2R подключен к выходам четвертого и пятого ключей, сигнальные входы которых соответственно соединены с источниками положительной и отрицательной полярности, управляющие входы - соответственно с единичным у нулевым выходс1ми триггера знака.

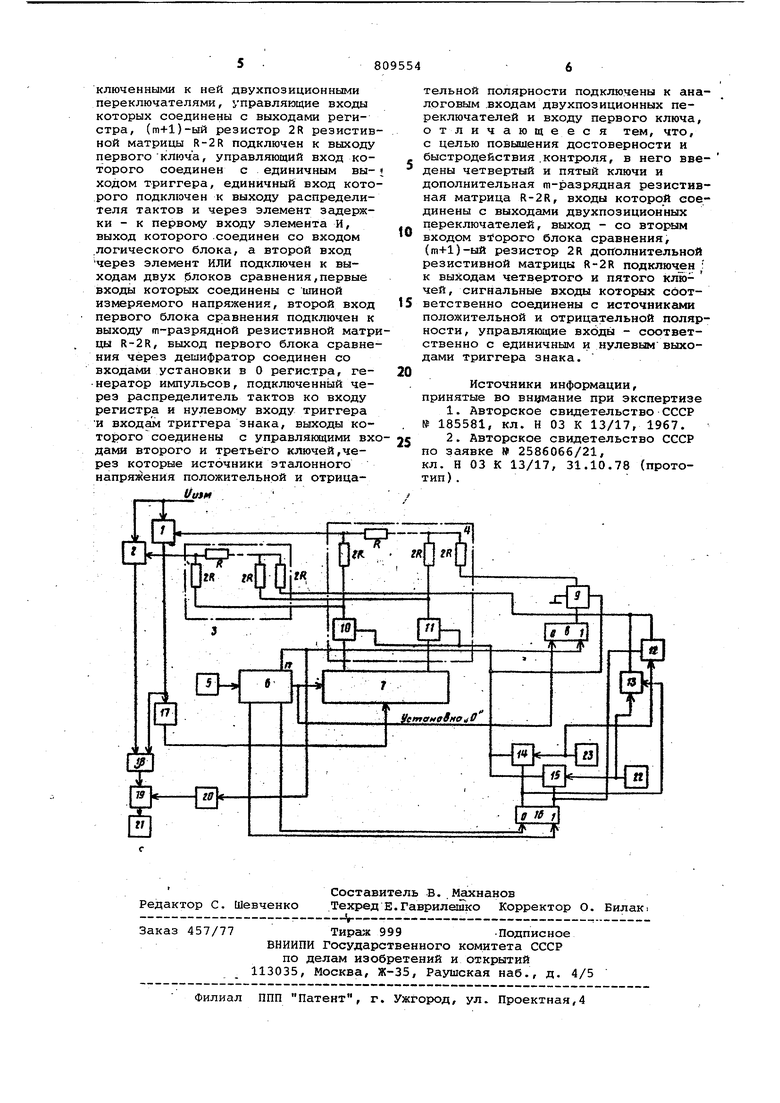

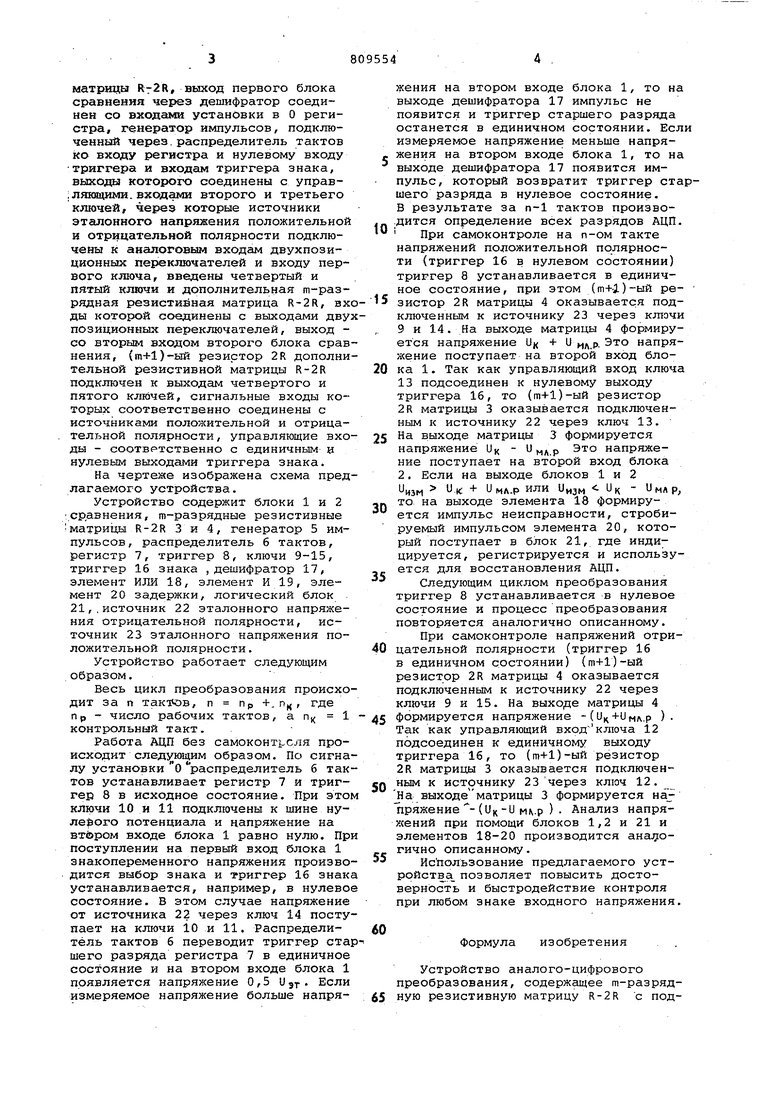

На чертеже изображена схема предлагаемого устройства,

Устройство содержит блоки 1 и 2 :сравнения, т-разрядные резистивные матрицы R-2R 3 и 4, генератор 5 импульсов, распределитель б тактов, регистр 7, триггер 8, ключи 9-15, триггер 16 знака , дешифратор 17, элемент ИЛИ 18, элемент И 19, элемент 20 задержки, логический блок 21,,источник 22 эталонного напряжения отрицательной полярности, источник 23 эталонного напряжения положительной полярности.

Устройство работает следующим образом.

Весь цикл преобразования происходит за п тактов, п Пр +,п, где Пр - число рабочих тактов, а п 1 контрольный такт.

Работа АЦП без самоконтроля происходит следующим образом. По сигналу установки о распределитель б тактов устанавливает регистр 7 и триггер 8 в исходное состояние. При этом ключи 10 и 11 подключены к шине нулевого потенциала и напряжение на втором входе блока 1 равно нулю. При поступлении на первый вход блока 1 знакопеременного напряжения производится выбор знака и триггер 16 знака устанавливается, например, в нулевое состояние. В этом случае напряжение от источника 22 через ключ 14 поступает на ключи 10 и 11. Распределитель тактов 6 переводит триггер стар шего разряда регистра 7 в единичное состояние и на втором входе блока 1 появляется напряжение 0,5 Ujr- Если измеряемое напряжение больше напряжения на втором входе блока 1, то на выходе дешифратора 17 импульс не появится и триггер старшего разряда останется в единичном состоянии. Есл измеряемое напряжение меньше напряжения на втором входе блока 1, то на выходе дешифратора 17 появится импульс, который возвратит триггер сташего разряда в нулевое состояние.

8результате за п-1 тактов произво.дится определение всех разрядов АЦП. При самоконтроле на п-ом такте напряжений положительной полярности {триггер 16 в нулевом состоянии) триггер 8 устанавливается в единичное состояние, при этом (т+1)-ый резистор 2R матрицы 4 оказывается подключенным к источнику 23 через ключи

9и 14. На выходе матрицы 4 формируется напряжение и« + . Это напряжение поступает на второй вход блока 1. Так как управляющий вход ключа 13 подсоединен к нулевому выходу триггера 16, то (т+1)-ый резистор

2Я матрицы 3 оказывается подключенным к источнику 22 через ключ 13. На выходе матрицы 3 формируется напряжение UK - U МЛ.Р Это напряжение поступает на второй вход блока 2. Если на выходе блоков 1 и 2 УИЗИ JK: + UMA.P или и„зм U - UMAP, то на выходе элемента 18 формируется импульс неисправности, стробируемый импульсом элемента 20, который поступает в блок 21, где индицируется, регистрируется и используется для восстановления АЦП.

Следующим циклом преобразования триггер 8 устанавливается в нулевое состояние и процесс преобразования повторяется аналогично описанному.

При самоконтроле напряжений отрицательной полярности (триггер 16 в единичном состоянии) (т+1)-ый резистор 2R матрицы 4 оказывается подключенным к источнику 22 через ключи 9 и 15. На выходе матрицы 4 формируется напряжение -(.р ) Так как управляющий входключа 12 подсоединен к единичному выходу триггера 16, то (т+1)-ый резистор 2R матрицы 3 оказывается подключенным к источнику 23 через ключ 12. На выходе матрицы 3 формируется на Ъряжение -(DH-и MN.p ) . Анализ напряжений при помощи блоков 1,2 и 21 и элементов 18-20 производится ана огично описанному.

Использование предлагаемого устройства позволяет повысить достоверность и быстродействие контроля при любом знаке входного напряжения.

Формула изобретения

Устройство аналого-цифрового преобразования, содержащее т-разрядную резистивную матрицу R-2R с под

Авторы

Даты

1981-02-28—Публикация

1979-04-16—Подача