(54) УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОГО

АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ

С САМОКОНТРОЛЕМ

ды сигнальными входами двухпозиционных переключателей, входы триггера знака соединень с вторым и третьим выходами распределителя, нулевой выход триггера - через третий и четвертый переключатели соединен соответственно с m + 1 резистором резистивных матриц, выход первого элемента И подключен ко входу логического блока 2.

Однако известное устройство имеет малые быстродействие и достоверность контроля.

Цель изобретения - повышение быстродействия и достоверности контроля.

Указанная цель достигается тем, что устройство параллельно-последовательного аналого-цифрового преобразования с самоконтролем, содержащее две m разрядные резистивные Матрицы R-2R с подключенными к ним двухпозиционными переключателями, управляющие входы которых соединены с прямыми и инверсными выходами регистра, выходы резистивных матриц R-2R соединены с первыми входами первого и второго нуль-органов и входами резистивного делителя из двух резисторов, выход которого соединен с первым входом третьего нуль-органа, выход второй резистивной матрицы R-2R подключен к инвертирующему входу операционного усилителя, выход которого соединен с первым входом четвертого нуль-органа, вторые входы нуль-органов подключены к щинё измеряемого напряжения, выходы первого, второго и третьего нуль-орггиов через дешифратор соединены с первым входом регистра, второй вход которого через распределитель тактов подключен к выходу генератора импульсов, выход четвертого нульоргана соединен с первым входом элемента ИЛИ, втарой вход которого подключен, к выходу первого нуль-органа, а выход к первому входу первого элемента И, второй вход которого через элемент задержки сое- динен с перрым выходом распределителя и единичным входом триггера, нулевой вход которого соединен с вторым входом регистра, триггер знака, выходы которого подключены к управляющим входам первого и второго переключателей, сигнальные входы которых соединены с соответствующими выходами источников эталонного напряжения положительной и отрицательной полярности, а выходы с сигнальными входами двухпозиционных переключателей, входы триггера знака соединены со вторым и- третьим выходами распределителя, нулевой выход триггера - через третий и четвертый переключатели соединен соответственно с m + 1 резистором резистивных матриц R-2R, выход первого элемента И подключен ко входу логического блока, введены четыре дополнительных переключателя, два дополнительных элемента И и два дополнительных источника эталонных напряжений, первый из которых соединен с сигнальным вхо дом первого дополнительного переключатеЛЯ, управляющий вход которого подключен к выходу первого дополнительного элемента И, первый вход которого соединен с единичным выходом триггера знака, вторые входы первого и второго дополнительных

элементов И соединены с единичным выходом триггера, второй дополнительный источник эталонного напряжения соединен с сигнальным входом второго дополнительного переключателя, управляющий вход которого подключен к выходу второго дополкительного элемента И, первый вход которого соединен с нулевым выходом триггера знака, выходы nepBOijo и второго дополнительных переключателей подключены к ш + 1 резистору второй резистивной матрицы R-2R, сигнальньш вход третьего дополнительного переключателя соединен с источником эталонного напряжения положительной полярности, управляющий вход - с выходом второго дополнительного элемента И, сигналЬный вход четвертого дополнительного переключателя. подключен к источнику эталонного напряжения отрицательной полярности, управляющий вход - к выходу первого дополнительного элемента И, в выходы третьего и четвертого дополнительных переключателей соединены с гп + 1 резистором

первой резистивной матрицы R-2R, неинвертирующий вход операционного усилителя подключен к выходам первого и второго переключателя.

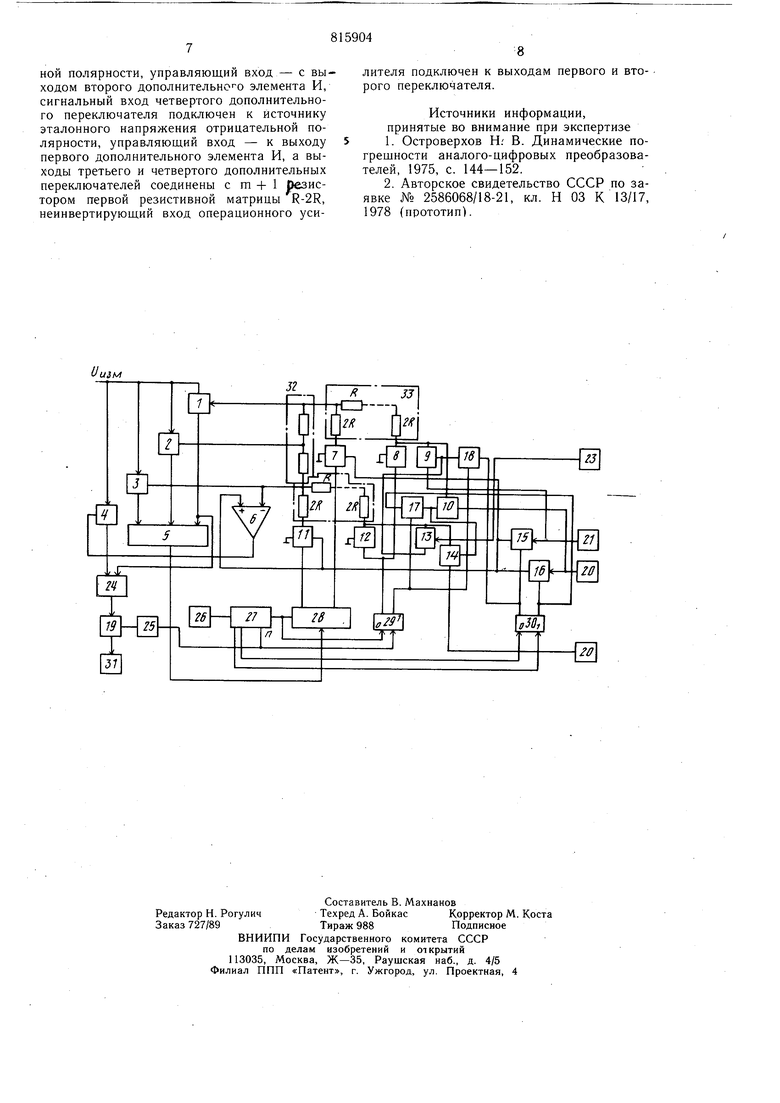

На чертеже изображена схема предлагаемого устройства.

Схема содержит нуль-органы 1 - 4, дешифратор 5, операционный усилитель 6, двупозиционные переключатели 7-16, элементы И 17-19, первый дополнительный источник 20 эталонного напряжения (источник

j; удвоенного эталонного напряжений положительной полярности), источник 21 эталонного напряжения положительной полярности, источник 22 эталонного напряжения отрицательной полярности, второй дополнительный источник 23 эталонного напряжения удвоенного эталонного напряжения отрицательной полярности), элемент ИЛИ 24, элемент 25 задержки, генератор 26 импульсов, распределитель .27, регистр 28, триггер 29, триггер 30 знака, логический блок 31 резистивный делитель 32, резистивные мат рицы R-2R 33, 34.

Устройство работает следующим образом.

Весь цикл преобразования происходит за п тактов, п iip-f п, где Пр - число

0 рабочих тактов; п 1 - контрольный такт. Например, в десятиразрядном АЦП Пр 5. По (Сигналу. «Установка нуля блок 27 устанавливает регистр 28, триггер 29 в исходное состояние. При этом на одном из двух входов трех нуль-органов появляются соответственно напряжения

и«, , и., Vjtr а. ia

f Ч

чЧй-,

01

Oi.

05

Тактовая частота от генератора 26 начинает поступать на распределитель 27 и с выходов нуль-органов 1-3 начинают посту, Х и X . в соответствии пать сигналы «3 с формулой , J1 при V3T(i-,J)IUkl при l73TU,})Vxl После дешифратора в соответствии с формулами у4 Хг, Уа. + Xj сигналы нуль-органов 1-3 поступают для управления блоком 28. На первом такте преобразования происходит включение двух триггеров старших разрядов. Соответственно происходит включение двух «единичных переключателей и выключение двух «нулевых переключателей старших разрядов. Далее происходит управление этих двух триггеров 28 регистра от дешифратора 5. На выходе двух резистивных матриц R-2R разность эталонных напряжений, вновь делится резистивным делителем 32 на четыре равные части и поступает на входы блоков 1-3. В результате за Пр тактов происходит определение всех разрядов АЦП. При самоконтроле на такте устанавливается в единичное состояние триггер 29 и в случае преобразования напряжений отрицательной полярности к напряжению на первом входе нуль-органа 1 U добавля ется напряжение отрицательной полярности, равное величине младшего разряда UMA.P. В результате к т +1-ому резистору первой резистивной матрицы R-2R подключается выходное напряжение источника 22. На входе блока 3 образуется напряжение LJj + 2им(щ в связи с тем, что вход элемента 14 подсое-, динен к источнику 20, а выход - к m + -оку резистору второй резистивной матрицы R2R. Это напряжение поступает на инвертирующий вход усилителя 6. На неинвертирующий (суммирующий) вход усилителя-6 поступает напряжение от источника 22 через переключатель 16. На выходе усилителя 6 образуется напряжение - (U - UMA.p)i Это напряжение поступает на вход нульоргана 4. Если на выходе нуль-органа 1 к 4 - (Ui - UMA.P) или -Ux - - (U-i - , TO на выходе элемента ИЛИ 24 формируется импульс неисправности, стробируемый сигналом, с выхода блока 25, который поступает на вход блока 31, где индуцируется, регистрируется, используется для восстановления АЦП и т. п. Следующигл циклом преобразования триггер 29 устанавливается в нулевое состояние и процесс; преобразования повторяется аналогично описанному. Формула изобретения Устройство параллельно-последовательного аналого-цифрового преобразования с самоконтролем, содержащее две m разрядные резистивные матрицы R-2R с подключенными к ним двухпозиционными переключателями, управляющие входы которых соединены с прямыми и инверсными выходами регистра, выходы резистивных матриц R2R соединены с первыми входами первого и второго нуль-органов и входами резистив - ного делителя из двух резисторов, выход которого соединен с первым входом третьего . нуль-органа, выход второй резистивной матрицы R-2R подключен к инвертируюшему входу операционного усилителя, выход которого соединен с первым входом четвертого нуль-органа, вторые входы нуль-органов подключены к шине измеряемого напряжения. выходы первого, второго и третьего нульорганов через дешифратор соединены с первым входом регистра, второй вход которого через распределитель подключен к выходу генератора импульсов, выход четвертого нуль-органа соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу первого нуль-органа, а выход к первому входу первого элемента И, второй вход которого через элемент задержки соединен с первым выходом распределителя и единичным входом триггера, нулевой вход которого соединен с вторым входом регистра, триггер знака, выходы которого подключены к управляющим входам первого и второго переключателей, сигнальные входы которых соединены с соответствующими выходами источников эталонного напряжения положительной и отрицательной поляр.ности, а выходы с сигнальными входами двухпозиционных переключателей, входы триггера знака соединены с вторым и третьим выходами распределителя, нулевой выход триггера - через третий и четвертый переключатели соединен соответственно с m + 1 резистором резистивных матриц R-2R, выход первого элемента И подключен ко входу логического блока, отличающееся тем, что, с целью повышения быстродействия и достоверности контроля, в него введены четыре дополнительных переключателя, два дополнительных элемента И и два дополнительных источника эталонных напряжений, первый из которых соединен с сигнальным входом первого дополнительного переключателя, управляющий вход которого подключен к выходу первого дополнительного элемента И, первый вход которого соединен с единичным выходом триггера знака, вторые входы первого и второго дополнительных элементов И соединены с единичным выходом триггера, второй дополнительный источник эталонного напряжения соединен с сигнальным входом второго дополнительного переключателя, управляющий вход которого подключен к выходу второго дополнительного элемента. И, первый вход которого соединен с нулевым выходом триггера знака, выходы первого и второго дополнительных переключателей подключены к m + 1 резистору второй резистивной матрицы R-2R сигнальный вход третьего дополнительного переключателя соединен с источником эталонного напряжения положительной полярности, управляющий вход - с выходом второго дополнительно-о элемента И, сигнальный вход четвертого дополнительного переключателя подключен к источнику эталонного напряжения отрицательной полярности, управляющий вход - к выходу первого дополнительного элемента И, а выходы третьего и четвертого дополнительных переключателей соединены с m + 1 резистором первой резистивной матрицы R-2R, неинвертирующий вход операционного усилителя подключен к выходам первого и второго переключателя. Источники информации, принятые во внимание при экспертизе 1. Островерхое Н; В. Динамические погрещности аналого-цифровых преобразователей, 1975, с. 144-152. 2 Авторское свидетельство СССР по заявке № 2586068/18-21, кл. Н 03 К 13/17, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобра-зОВАНия | 1979 |

|

SU809554A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| Параллельно последовательный анало-гО-цифРОВОй пРЕОбРАзОВАТЕль C CAMOKOH-ТРОлЕМ | 1978 |

|

SU813770A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| ДВУХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2251209C2 |

| Цифро-аналоговый перемножитель | 1975 |

|

SU598233A1 |

| Преобразователь кода в импульсы ступенчатой формы | 1981 |

|

SU974569A1 |

| Преобразователь напряжение-код с коррекцией динамической погрешности | 1975 |

|

SU898609A1 |

Авторы

Даты

1981-03-23—Публикация

1979-04-16—Подача