(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ

1

-

Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах/ устройствах автоматизированного контроля и управления.

По основному авт. св. № 809554 известен аналого-цифровой преобразбватель с самоконтролем, содержа1 1ий два блока сравнения, первые входы . которых соединены с шиной измеряемого напряжения, втЪрые входы - соответственно с выходами дзуХ. т-разряд ных резистивных матриц R-2R с подключенными к ним двухпозиционными ключгсми, управляющие входы которых соединены с выходами регистра, имеющего элементы переноса, сложения и :вычитания единицы, (пН-1)-ый резистор 2R первой резистивной матрицы R-2It подключен к выходу первого ключа, управляющий вход которого соединен с единичным выходом триггера, (nrt-l)-ый-резистор 2R второй резистйвиой матрицы R-2R подключен к выходам второго и третьего ключей, сигнгшьные входы которых соответственно соединены .с источниками положительной и отрицательной полярности, управляющие входы - соответствен; но с единичным и нулевым выходами

триггера знака, выход первого блока сравнения соединен с первым входом элемента ИЛИ и через дешифратор - с

триггеров .

выходами установки

t регистра, генератор импульсов, подключенный через распределитель тактов ко входу регистра, нулевому входу триггера к входам триггера зна-& ка, выходы которого соединены с уп10равляющими входами четвертого и пятого ключей/ через которые источники этсшонного напряжения положительной и отрицательной полярности подключены к аналоговым входам двухпозицион15ных ключей и входу первого ключа, выход второго блока сравнения соединен со вторым входом элемента ИЛИ/ выход которого соединен с первым входом первого злемента И, выход которого

20 подключен ко входу логического г блока }.

В известном устройстве отсутствует коррекция динамических погрешностей/ что приводит к потере достовер25ности контроля и малому быстродействию.

Цель изобретения - уменьшение динамических погрешностей, повышение достоверности контроля и быстро ей

30 ствия.

Цель достигается тем, что в аналого-цифровой преобразователь с самоконтролем введены дополнительные элементы И, ИЛИ и элемент задержки, вхо которого соединен с выходом основного элемента задержки, первым входом дополнительного элемента ИЛИ и первыми входами дополнительных элементов И, вторые входы которых подключены соответственно к выходшл первого и второго блоков сравнения, а выходы соединены соответственно со входами -сложения и вычитания единицы регистра, выход дополнительного элемента ИЛИ соединен со вторым входом элемента И, а выход логического блока подключен к шине считывания кода регистра.

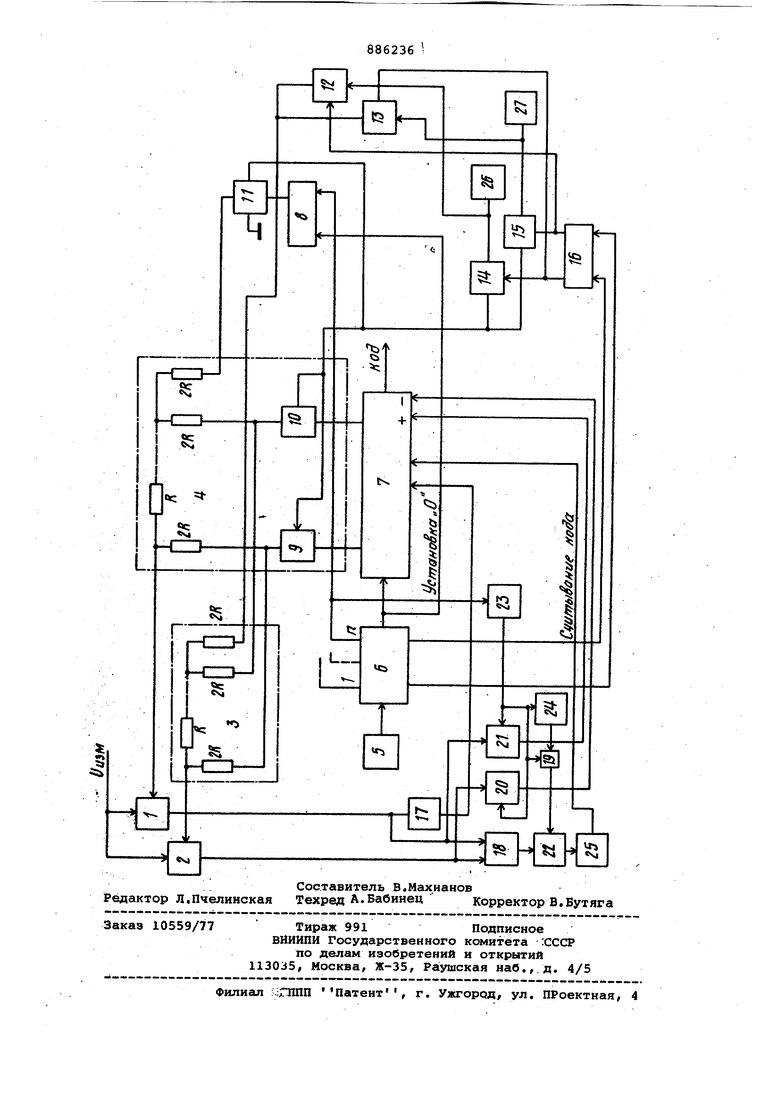

На чертеже изображена блон-схема предлагаемого устройства.

Устройство содержит блоки 1 и 2 сравнения, го-разрядную резистивную матрицы R-2R 3 и 4, генератор 5 им-, пульсов, распределитель б тактов, регистр 7, триггер 8, двухп&эицйонные переключатели 9 и 10, ключи 1115, триггер 16 знака, дешифратор 17, элементы ИЛИ 18 и 19, элементы И 2022, элементы 23 и 24 задержки, логич ский блок 25, источник 26 эталонного напряжения положительной полярности, источник 27 эталонного напряжения отрицательной полярности.

Предлагаемое устройство работает следующим образом, ,

Весь цикл преобразования происходит за п тактов (где п минус 1 - число рабочих тактов, а п - контрольный такт).

Работа АЦП без самоконтроля происходит следующим образом. По сигналу Установка О , распределитель 6 тактов устанавливает блоки и 8 в исходное состояние. При этом двухпозиционные переключатели 9 и 10 подключены к корпусной шине, и напряжение на втором входе блока 1 сравнения равно нулю. При поступлении, на первый вход блока Д сравнения знакопеременного напряжения производится выбор знака и триггер знака 16 устанавливается, например, в нулевое , состояние. В этом случае напряжение от источника 26 через ключ 14 поступает на переключатели 9 и 10. Распределитель 6 тактов переводит триггер, старшего разряда регистра 7 в единичное состояние, и на втором вхсзде блока 1 сравйения Появляется на1|ряжение О, SU . Если измеряемое напряжение больше компенсирующего напряжения, то на выходе дешифратора 17 импульс не появляется, и триггер старшего разряда остается в единичном состоянии. Если измеряемое напряжение меньше компенсирующего напряжения, то на выходе дешифратора 17 появляется импульс, который возвращает триггер старшего разряда

в нулевое состояние.. В результате за п-1 тактов производится определение всех разрядов АЦП.

При самоконтроле на п-ом такте триггер 8 устанавливается в единичное состояние, происходит срабатывание ключа 9 и источник 26 оказывается подключенным к (т+1)-му резистору 2R матрицы 4 (при преобразовании напряжений положительной полярности) . При этом на выходе матрио

цы 4 фор1мируется напряжение УЭТ «КА Р Это напряжение поступает на вход блока , (т+1)-ый резистор 2R матрицы 3 через ключ 13 оказывается подключенным к источнику 27. При этом на выходе матрицы 3 формируется напряжение . Производится проверка соотношений между изменяемым и компенсирующим напряжениями . ± - лллр- Если оказывается, что

I ° импульс с выхода блока 1 сравнения через элемент И 21 , опрашиваемого элементом задержки 23, производит увеличение кода в регистре 7 на единицу в младшем разряде. Если оказывается, что

то импульс с выхода блока 2 сравнения через элемент И 20, опрашиваемый элементом задержки 23, производит уменьшение кода в регистре 7 на единицу в младшем разряде. Производится анализ возможности считывания кода из регистра 7. Если на выходе элемента ИЛИ 18 имеется импульс, то в момент времени, определяемый задержкой элемента 24 залержки, на выходе элемента И 22 появляется импульс, который, заступив в логическийблок 25, формирует сигнал запрета на считывание кода из регистра 7.

при; иэт. |0из(у 1 /и9г-имлр|

элементы и 20 и 21 оказываются за- крытыми и изменение кода в регистре не производится. В этом случае на выходе элемента ИЛИ 18 не появляется импульс в момент времени, определяемый задержкой элемента 23 задержки, логический блок 25 формирует сигнал разрешения на считывание кода из регистра 7.

В случаях, когда осуществляется коррекция динамических погрешностей, то после ее проведения производится дополнительный контроль работы АЦП с целью повышения достоверности выдаваемой информации с регистра 7 в . устройства сопряжения. Если ,

/ 9тто элемент И 22 в момент

млр

времени, определяемый згщержкой элемента 24 задержки, выдает сигнал в логический блок 25, который формирует сигнал запрета на считывание кода из регистра 7. Если после проведения коррекции ) и т- идддр / / и ЧлдР элемент И 22 в момент времени, определяемый задержкой элемента 24 задержки, вьщает сигнал в логический блок 25, который формирует сигнал разрешения на считывание кода из регистра 7. При установке триггера знака 16 в единичное состояние (при контроле напряжений отрицательной полярности) самоконтроль АЦП производится аналогично вышеописанному. Формула изобретения ; Аналого-цифровой преобразователь с самоконтролем по авт-; св. 809554 отличающийся тем, что, с целью уменьшения динамических погрешностей, повышения достоверности контроля и быстродействия, в него введены дополнительные элементы И, ИЛИ и элемент задержки, вход которого соеди ней с выходом основного элемента задержки, первым входом дополнительно го элемента ИЛИ и первыми входами дополнительных элементов И, вторые входы которых подключены соответственно к выходам первого и второго блоков сравнения, а выходы соединены, соответственно, со входами сложения и вычитания единицы регистра, выход дополнительного элемента ИЛИ соединен со тторам входом элемеита И, а выход логического блока подключен к шине считывания кода регистра. Источники инфохячации принятые во внимание при экспертяэе 1. Авторское свидетельство СССР 809554, кл. Н 03 К 13/17,1979 (прототип) .- . .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобра-зОВАНия | 1979 |

|

SU809554A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Устройство параллельно-последователь-НОгО АНАлОгО-цифРОВОгО пРЕОбРАзОВА-Ния C САМОКОНТРОлЕМ | 1979 |

|

SU815904A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| Параллельно последовательный анало-гО-цифРОВОй пРЕОбРАзОВАТЕль C CAMOKOH-ТРОлЕМ | 1978 |

|

SU813770A1 |

| ДВУХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2251209C2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Двухканальный аналого-цифровой преобразователь поразрядного уравновешивания | 1978 |

|

SU718916A1 |

| Аналого-цифровой преобразователь с самокоррекцией | 1986 |

|

SU1341716A1 |

Авторы

Даты

1981-11-30—Публикация

1980-01-10—Подача