Изобретение относится к технике связи и предназначено для использования в аппаратуре передачи дискретной информации.

Известно /стройство для декодирования сверточных кодов, содержащее кодер, анализатор синдрома, блок запрета коррекции, блок обнаружения пакетов ошибок и другие элементы, позволяющие обнаруживать пакеты ошибок и прерывать на некоторое время коррекцию для прекращения возможного размножения ошибок. Его недостатком является низкая эффективность из-за неточного определения границ расположения пакета ошибок

Известно устройство для порогового декодирования сверточных кодов, содержащее регистры сдвига, сумматоры по модулю два, пороговый элемент и ключ, разрывающий обратную связь в синдромном регистре в случае возникновения эффекта размножения ошибок. В этом случае глубина размножения ограничивается длиной кодового ограничения используемого кода. Его недостатком является ограниченный класс кодов

для которых оно применимо (устройство предназначено в основйом для самоортогональных сверточных кодов).

Наиболее близким по технической сущности к предлагаёмому уЈтр ой ству является пороговый декодер сверточного кода, содержащий последовательно соединенные кодер, первый анализатор синдрома первый пороговый обнаружитель первый блок запрета коррекции. вы хоД которого подключен к соответствующему входу анализатора синдрома, а также блок обнаружения пакетов ошибок и последовательно соединенные второй пороговый обнаружитель и второй блок запрета коррекции, выход которого подключен к первому входу корректора ошибок, при этом к входу блока обнаружения пакетов ошибок подключен выход первого блока запрета коррекции, а выход блока обнаружения пакетов ошибок к входу управления коррекцией, выход которого подключен к второму входу первого блока запрета коррекции непосредственно и через блок задержки сигналов управления - ко

со

с

VI со

00

го ел

второму входу второго блока запрета коррекции, а выход второго блока запрета коррекции подключен к соответствующим входам дополнительного анализатора синдрома, при этом вход корректора ошибок соединен с выходом кодера через блок задержки информационной последовательности, а выходы кодера соединены с соответствующими входами блока задержки.

Недостатком устройства является его низкая помехоустойчивость ,

В известном устройстве вывод о возникновении эффекта размножения ошибок делается по частоте единичных символов на выходе порогового элемента формирующего символы вектора ошибок (символы коррекции). В случае превышения этой величиной некоторого порогового значения, как правило равного корректирующей способности кода, запрещается коррекция информационной последовательности, задержанной на некоторое время в регистре сдвига. Поскольку устройство может корректировать значительную часть ошибок, кратность которых превышает кратность гарантийно корректируемых ошибок, известное устройство в этом случае будет запрещать коррекцию и, по сути дела, вносить ошибку.

Целью изобретения является повышение помехоустойчивости за счет изменения алгоритма обнаружения пакетов ошибок.

Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные кодер, блок задержки информационной последовательности и корректор ошибок, а также первый анализатор синдрома, один из выходов которого подключен к соответствующему выходу кодера, а другой является входом устройства, при этом его выходы подключены к входам первого порогового обнаружителя, выход которого подключен к входу первого анализатора ошибок, а также второй анализатор синдрома, выходы которого подключены к соответствующим входам второго порогового обнаружителя, выход которого подключен к соответствующему входу второго анализатора синдрома, введен второй кодер, сумматор по модулю два и регистр сдв ига, при этом выход первого порогового обнаружителя подсоединен к соответствующему входу второго кодера, первый выход которого подсоединен к соответствующему входу второго анализатора синдрома, а второй его выход подсоединен к первому входу сумматора по модулю два и входу регистра сдвига, при этом второй вход сумматора по модулю два подсоединен к выходу второго порогового обнаружителя, а его выход подсоединен к соответствующим входам первого и второго анализаторов синдрома, второго кодера и регистра сдвига.

Достоверность достижения поставленной цели подтверждается следующим. В известном устройстве вывод о возникновении пакета ошибок, приводящего к их размножению, делается при увеличении частоты единичных символов коррекции, поступаю0 щихс выхода первого порогового обнаружителя. Если их число превышает некоторое пороговое значение N, фиксируется факт размножения ошибок и запрещается их коррекция в предварительно задержанной ин5 формационной последовательности. Проблема заключается в правильном выборе порогового значения N. Если его выбрать на единицу больше кратности гарантийно исправляемых ошибок.

0N J/2 + 1,

где J - число независимых ортогональных проверок в данном коде, устройство не позволяет исправлять значительную часть ошибок, которые могли бы быть исправле5 ны, так как при пороговом декодировании исправляется значительное число ошибок и более высокой кратности, конфигурацию которых учесть заранее практически невозможно. Если же выбрать значение порога N

0 несколько больше кратности гарантийно исправляемых кодом ошибок, декодер будет пропускать значительную часть размноженных ошибок.

Для подтверждения сказанного рас5 смотрим следующий пример ортогонализи- руемого кода, имеющего кодовую скорость R 1 /2 и образующий полином f(D) 1 + D6 + D7 + D9 + D10 + D11. На фиг.2 приведен фрагмент схемы устройства, включающий

0 некоторые блоки и связи между ними, являющиеся общими для известного и предлагаемогоустройства.Символы информационной последовательности 1(0) вместе с символами аддитивной шимовой

5 последовательности Ei(D) поступают на вход кодера 1 где происходит их умножение на образующий полином f(D). В результате получается последовательность Z(D) вида: Z(D)l(D)f(D) + Ei(D)f(D)

0 Эта последовательность поступает на вход анализатора синдрома 2, где складывается с символами проверочной последовательности P(D) и наложенной на ни аддивной шумовой последовательностью

5 E2(D), в результате чего получается последовательность символов синдрома S(D) вида

S(D) P(D) + E2(D) + l(D)f{D) + Ei(D)f(D). Учитывая, что F(D) l(D)f(D) ,

последовательность S(D) будет иметь вид; S(D)Ei(D)f(D)+E2(D)(1)

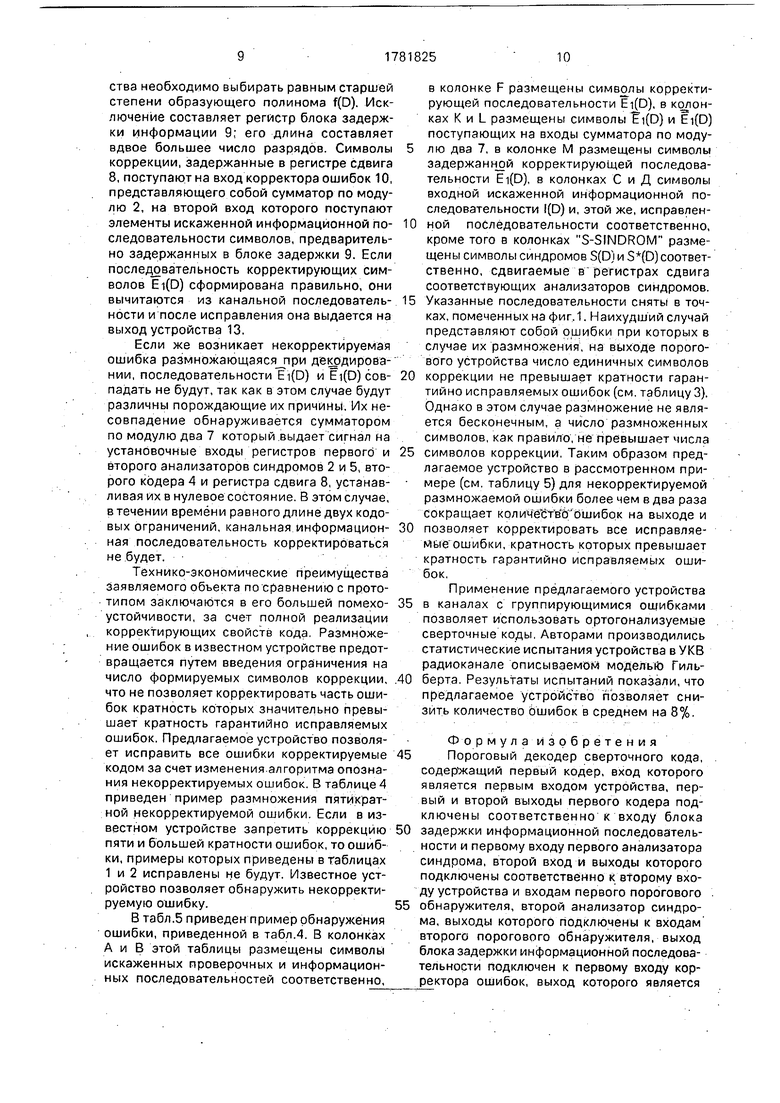

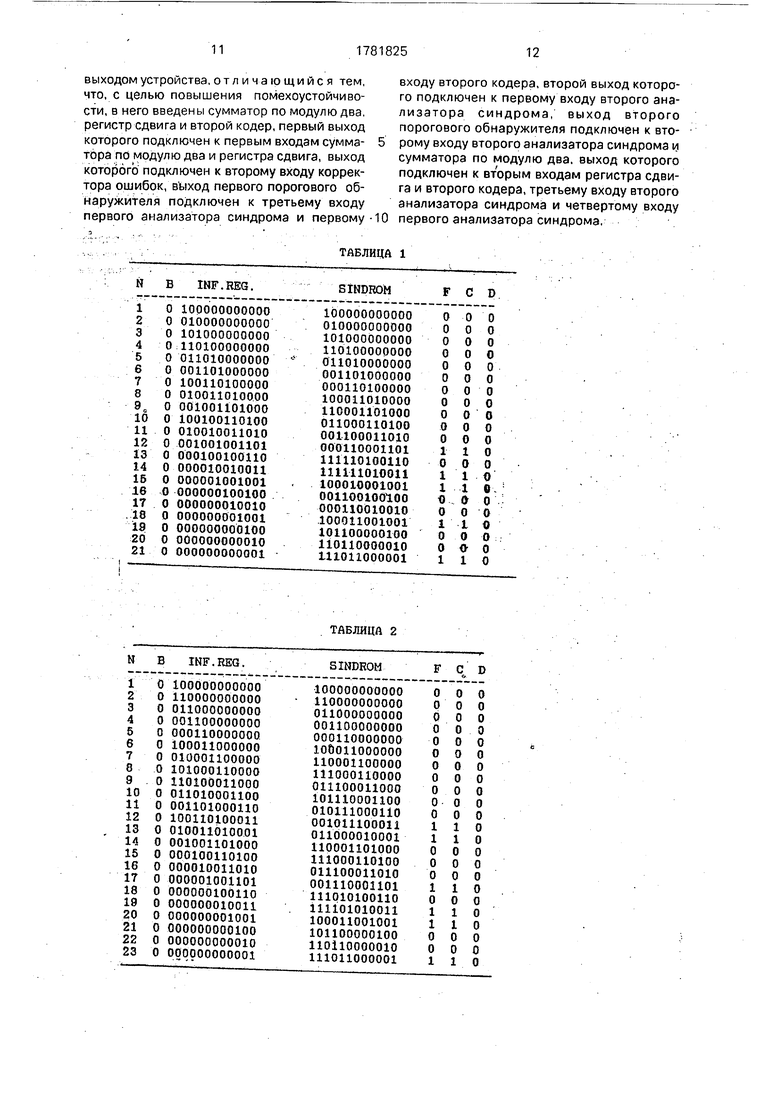

Символы этой последовательности объединяются в независимые проверки следующим образом: Ai S0; А2 Se; Аз S. Аз Sg; As Si + 5з + 5ю: Ае 84 + Se + Sn. Результаты проверок анализируются в первом пороговом обнаружителе 3. Поскольку для данного кода число независимых ортогональных проверок J 6, исправлены будут все ошибки до трехкратной включительно и некоторые ошибки более высокой кратности, Исправление происходит следующим образом: если на входах порогового обнаружителя присутствует более трех единичных символов, он генерирует единичный символ, поступающий с некоторой задержкой на вход инвертора, где складывается с последовательностью I(D) + Ei(D), также несколько задержанной по времени. В табл.1 и 2 приведены примеры исправляемых пяти и шести кратных ошибок в информационной последовательности исправляемых устройством. Колонка В в этих таблицах содержит последовательность символов Ea(D) накладываемых на проверочную последовательность P(D), в следующих 12-ти колонках таблицы размещаются последовательно сдвигаемые в информационном регистре символы вектора ошибки Ei(D), в следующих 12-ти колонках размещены последовательно сдвигаемые в синдромном регистре символы анализируемого отрезка последовательности S(D), в колонке F - размещается последовательность символов коррекции генерируемая первым пороговым обнаружителем, в колонках С и D размещаются символы выходной исправляемой и исправленной последовательности символов соответственно, В табл 3 приведен пример размноженной 5-ти кратной ошибки которая не обнаруживается устройством, так как при декодировании устройство генерирует лишь три символа коррекции (колонка F), что меньше корректирующей способности кода. В таблице 4 приводится пример 5-ти кратной ошибки, размножение которой может быть обнаружено. Таким образом необходимо, чтобы устройство с большей степенью достоверности отличало исправляемую ошибку большой кратности от размноженной неисправляемой ошибки,

В предлагаемом устройстве вывод о размножении ошибок делается не по факту увеличения частоты единичных символов коррекции, а на основании анализа этой последовательности Предположим, что в канале связи возникла ошибка, кратность которой превышает корректирующую способность кода, но исправляемая устройством. 8 этом случае, на выходе порогового обнаружителя будут появляться символы коррекции, последовательность которых E(D), в точности совпадает с последователь- 5 ностью Ei(D) накладываемых в канале связи на информационную последовательность I(D). При этом каждый единичный символ корректирующей последовательности Ei(D) по цепи обратной связи поступает на соответст0 вующие входы анализаторов синдрома, корректируя символы последовательности S(D). Если ошибка корректируема, значит единичные символы принадлежащие последовательности E2(D), в данном случае не

5 оказывают влияния на правильность формирования последовательности Ei(D), отсюда следует, что умножим ее на образующий полином f(D), мы получим новый синдром S (D), анализ которого дает тот же вектор Ei(D).

0 Этот синдром будет иметь видS(D) Ei(D)f(D).

Проанализировав этот синдром мы получим новую последовательность Ei(D), которая, в случае исправляемой ошибки будет совпа5 дать с последовательностью Ei(D) Если же ошибка некорректируема, неверно будет производится коррекция синдрома S(D) и возникшее размножение ошибок приведет к неравенству последовательностей Ei(D) и

0 Ei(D) и, следовательно, к .неравенству последовательностей Ei(D) и Ei(D). Сформиро- вав в предлагаемом., устройстве последовательности Ei(D) и Ei(D) и, сравнивая их поэлементно, мы сможем однозначно

5 выделить все корректируемые ошибки, в том числе и те, кратность которых превышает корректирующую способность кода.

Для реализации предложенного алгоритма в устройство введены: второй деко0 дер, производящий умножение последовательности Ei(D) на образующий полином f(D), регистр сдвига, задерживающий символы корректирующей последовательности Ei(D) на время анализа этой

5 последовательности и сумматор по модулю два, осуществляющий поэлементуре сравнение последовательности Ei(D)n Ei(D). Перечисленные блоки, введенные в устройство, позволяют осуществить зало0 женный в предлагаемом устройстве алгоритм коррекции ошибок и поэтому являются существенными отличиями.

Сущность изобретения состоит в повышении помехоустойчивости устройства за

5 счет изменения алгоритма обнаружения ошибок,

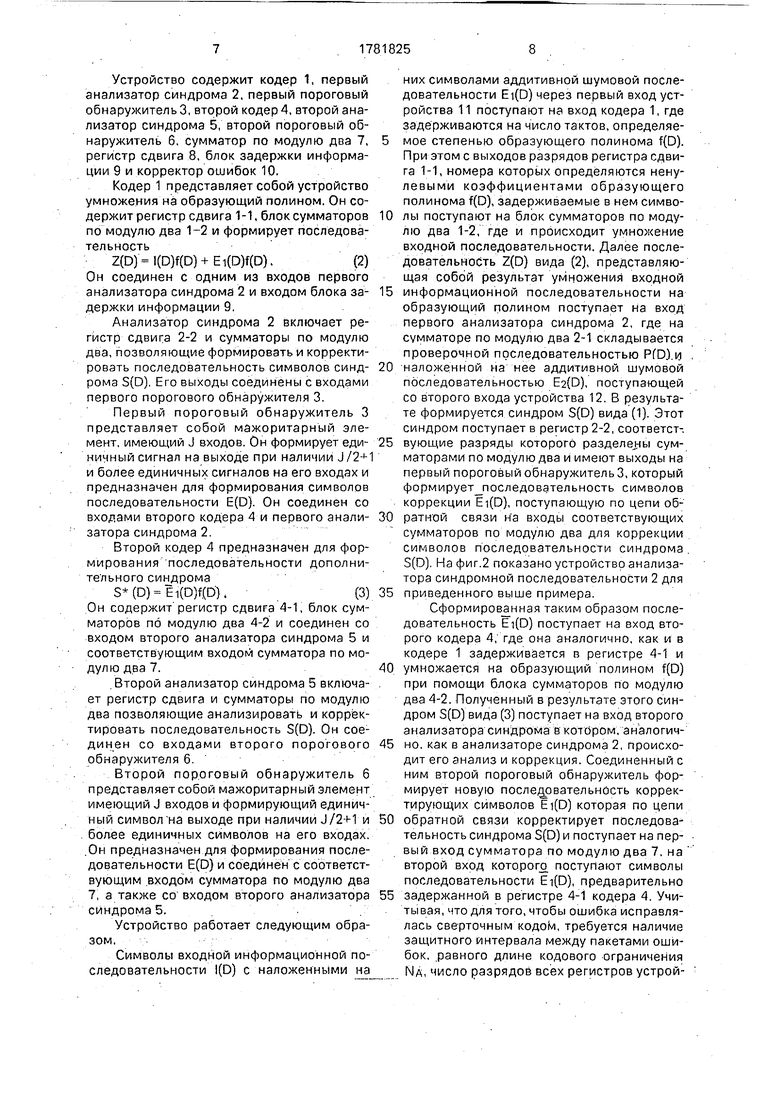

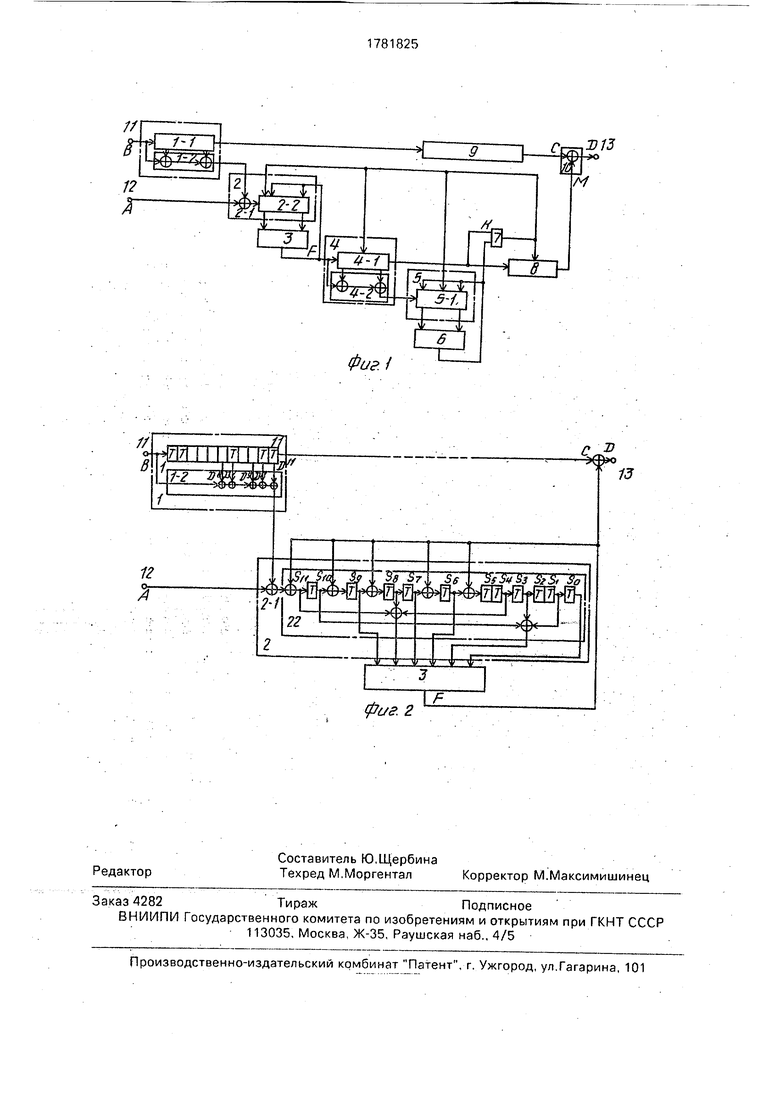

На фиг.1 представлена блок-схема порогового декодера сверточного кода; на фиг.2 - фрагмент предлагаемого устройства, поясняющий его работу.

Устройство содержит кодер 1, первый анализатор синдрома 2, первый пороговый обнаружитель 3, второй кодер 4, второй анализатор синдрома 5, второй пороговый обнаружитель б, сумматор по модулю два 7, регистр сдвига 8, блок задержки информации 9 и корректор ошибок 10.

Кодер 1 представляет собой устройство умножения на образующий полином. Он содержит регистр сдвига 1-1, блок сумматоров по модулю два 1-2 и формирует последовательность

Z(D) (D)f(D)+E1(D)f(D).(2)

Он соединен с одним из входов первого анализатора синдрома 2 и входом блока за- держки информации 9.

Анализатор синдрома 2 включает регистр сдвига 2-2 и сумматоры по модулю два, позволяющие формировать и корректировать последовательность символов синд- рома S(D). Его выходы соединены с входами первого порогового обнаружителя 3.

Первый пороговый обнаружитель 3 представляет собой мажоритарный элемент, имеющий J входов. Он формирует еди- ничный сигнал на выходе при наличии J/2-H и более единичных сигналов на его входах и предназначен для формирования символов последовательности E(D). Он соединен со входами второго кодера 4 и первого знали- затора синдрома 2.

Второй кодер 4 предназначен для формирования последовательности дополнительного синдрома

S(D)Ei(D)f(D)t(3)

Он содержит регистр сдвига 4-1, блок сумматоров по модулю два 4-2 и соединен со входом второго анализатора синдрома 5 и соответствующим входом сумматора по модулю два 7.

Второй анализатор синдрома 5 включает регистр сдвига и сумматоры по модулю два позволяющие анализировать и корректировать последовательность S(D). Он соединен со входами второго порогового обнаружителя 6.

Второй пороговый обнаружитель 6 представляет собой мажоритарный элемент имеющий J входов и формирующий единичный символ на выходе при наличии J/2+1 и более единичных символов на его входах. Он предназначен для формирования последовательности E(D) и соединен с соответствующим входом сумматора по модулю два 7, а также со входом второго анализатора синдрома 5.

Устройство работает следующим образом.

Символы входной информационной последовательности I(D) с наложенными на

них символами аддитивной шумовой последовательности Ei(D) через первый вход устройства 11 поступают на вход кодера 1, где задерживаются на число тактов, определяемое степенью образующего полинома f(D). При этом с выходов разрядов регистра сдвига 1-1, номера которых определяются ненулевыми коэффициентами образующего полинома f(D), задерживаемые в нем символы поступают на блок сумматоров по модулю два 1-2, где и происходит умножение входной последовательности. Далее последовательность Z(D) вида (2), представляющая собой результат умножения входной информационной последовательности на образующий полином поступает на вход первого анализатора синдрома 2, где на сумматоре по модулю два 2-1 складывается проверочной последовательностью PfD) и наложенной на нее аддитивной шумовой последовательностью E2(D), поступающей со второго входа устройства 12. В результате формируется синдром S(D) вида (1). Этот синдром поступает в регистр 2-2, соответствующие разряды которого разделены сумматорами по модулю два и имеют выходы на первый пороговый обнаружитель 3, который формирует последовательность символов коррекции Ei(D), поступающую по цепи обратной связи на входы соответствующих сумматоров по модулю два для коррекции символов последовательности синдрома S(D). На фиг.2 показано устройство анализатора синдромной последовательности 2 для приведенного выше примера.

Сформированная таким образом последовательность Ei(D) поступает на вход второго кодера 4, где она аналогично, как и в кодере 1 задерживается п регистре 4-1 и умножается на образующий полином f(D) при помощи блока сумматоров по модулю два 4-2. Полученный в результате этого синдром S(D) вида (3) поступает на вход второго анализатора синдрома в котором, аналогично, как в анализаторе синдрома 2, происходит его анализ и коррекция. Соединенный с ним второй пороговый обнаружитель формирует новую последовательность корректирующих символов Ei(D) которая по цепи обратной связи корректирует последовательность синдрома S(D) и поступает на пер- вый вход сумматора по модулю два 7. на второй вход которого поступают символы последовательности Ei(D), предварительно задержанной в регистре 4-1 кодера 4. Учитывая, что для того, чтобы ошибка исправлялась сверточным кодом, требуется наличие защитного интервала между пакетами ошибок, равного длине кодового ограничения NA, число разрядов всех регистров устройства необходимо выбирать равным старшей степени образующего полинома f(D). Исключение составляет регистр блока задержки информации 9; его длина составляет вдвое большее число разрядов. Символы коррекции, задержанные в регистре сдвига 8, поступают на вход корректора ошибок 10, представляющего собой сумматор по модулю 2, на второй вход которого поступают элементы искаженной информационной последовательности символов, предварительно задержанных в блоке задержки 9. Если последовательность корректирующих символов Ei(D) сформирована правильно, они вычитаются из канальной последовательности и после исправления она выдается на выход устройства 13.

Если же возникает некорректируемая ошибка размножающаяся при декодировании, последовательности Ei(D) и Ei(0) совпадать не будут, так как в этом случае будут различны порождающие их причины. Их несовпадение обнаруживается сумматором по модулю два 7 который выдает сигнал на установочные входы регистров первого и второго анализаторов синдромов 2 и 5, второго кодера 4 и регистра сдвига 8, устанавливая их в нулевое состояние. В этом случае, в течении времени равного длине двух кодовых ограничений, канальная информационная последовательность корректироваться не будет.

Технико-экономические преимущества заявляемого объекта по сравнению с прототипом заключаются в его большей помехоустойчивости, за счет полной реализации корректирующих свойств кода. Размножение ошибок в известном устройстве предотвращается путем введения ограничения на число формируемых символов коррекции, что не позволяет корректировать часть ошибок кратность которых значительно превышает кратность гарантийно исправляемых ошибок. Предлагаемое устройство позволяет исправить все ошибки корректируемые кодом за счет изменения алгоритма опознания некорректируемых ошибок. В таблице 4 приведен пример размножения пятикратной некорректируемой ошибки. Если в известном устройстве запретить коррекцию пяти и большей кратности ошибок, то ошибки, примеры которых приведены в таблицах 1 и 2 исправлены не будут. Известное устройство позволяет обнаружить некорректируемую ошибку.

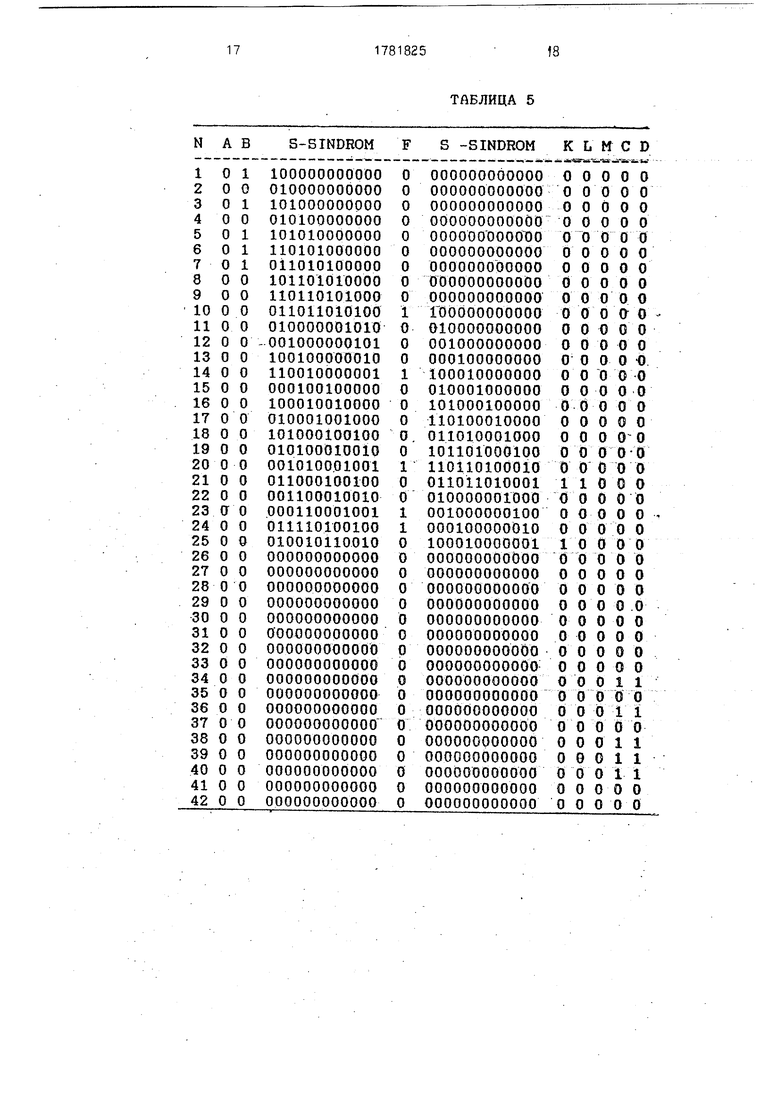

В табл.5 приведен пример обнаружения ошибки, приведенной в табл.4. В колонках А и В этой таблицы размещены символы искаженных проверочных и информационных последовательностей соответственно.

в колонке F размещены символы корректирующей последовательности Ei(D), в колонках К и L размещены символы Ei(D) и Ei(D) поступающих на входы сумматора по моду- 5 лю два 7, в колонке М размещены символы задержанной корректирующей последовательности Ei(D), в колонках С и Д символы входной искаженной информационной последовательности I(D) и, этой же, исправлен0 ной последовательности соответственно, кроме того в колонках S-SINDROM размещены символы синдромов S(D) и S(D) соответственно, сдвигаемые в регистрах сдвига соответствующих анализаторов синдромов.

5 Указанные последовательности сняты в точках, помеченных на фиг. 1. Наихудший случай представляют собой ошибки при которых в случае их размножения, на выходе порогового устройства число единичных символов

0 коррекции не превышает кратности гарантийно исправляемых ошибок (см. таблицу 3). Однако в этом случае размножение не является бесконечным, а число размноженных символов, как правило, не превышает числа

5 символов коррекции. Таким образом предлагаемое устройство в рассмотренном примере (см. таблицу 5) для некорректируемой размножаемой ошибки более чем в два раза сокращает количество ошибок на выходе и

0 позволяет корректировать все исправляе- Мые ошибки, кратность которых превышает кратность гарантийно исправляемых ошибок,

Применение предлагаемого устройства

5 в каналах с группирующимися ошибками позволяет использовать ортогонализуемые сверточные коды. Авторами производились статистические испытания устройства в УКВ радиоканале описываемом моделыЬ Гиль0 берта. Результаты испытаний показали, что предлагаемое устройство позволяет снизить количество ошибок в среднем на 8%.

Формула изобретения 5 Пороговый декодер сверточного кода, содержащий первый кодер, вход которого является первым входом устройства, первый и второй выходы первого кодера подключены соответственно к входу блока 0 задержки информационной последовательности и первому входу первого анализатора синдрома, второй вход и выходы которого подключены соответственно к второму входу устройства и входам первого порогового 5 обнаружителя, второй анализатор синдрома, выходы которого подключены к входам второго порогового обнаружителя, выход блока задержки информационной последовательности подключен к первому входу корректора ошибок, выход которого является

выходом устройства, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены сумматор по модулю два регистр сдвига и второй кодер, первый выход которого подключен к первым входам сумматора по модулю два и регистра сдвига, выход которого подключен к второму входу корректора ошибок, выход первого порогового обнаружителя подключен к третьему входу

входу второго кодера, второй выход которого подключен к первому входу второго анализатора синдрома, выход второго порогового обнаружителя подключен к второму входу второго анализатора синдрома и сумматора по модулю два. выход которого подключен к вторым входам регистра сдвига и второго кодера, третьему входу второго анализатора синдрома и четвертому входу

и

928L8a

El

ТАБЛИЦА 4

Si

92818M

Z.L

13

(риг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1837385A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Кодер несистематического сверточного кода | 1990 |

|

SU1695516A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Пороговый декодер сверточного кода | 1981 |

|

SU964999A1 |

| Пороговый декодер сверхточного кода | 1976 |

|

SU586571A1 |

Изобретение относится к технике связи и предназначено для использования в аппаратуре передачи дискретной информации Целью изобретения является повышение помехоустойчивости устройства. Устройство содержит кодеры, анализаторы синдрома, пороговые обнаружители, сумматор по модулю два, регистр сдвига, блок задержки информационной последовательности и корректор ошибок. Это позволяет полностью использовать его для широкого класса как самоортогональных, так и ортогонализй р уе мы х сверточных кодов. 2 ил 5 табл.

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Пороговый декодер сверточного кода | 1981 |

|

SU964999A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-15—Публикация

1991-01-22—Подача