4.2

6 5

Изобретение относится к аппаратуре для приема дискретных сообщений и может быть использовано для исправления ошибок в 2-символьном коде. Цель изобретения - расширение области применения путем исправления ошибок в 2-символьном коде.

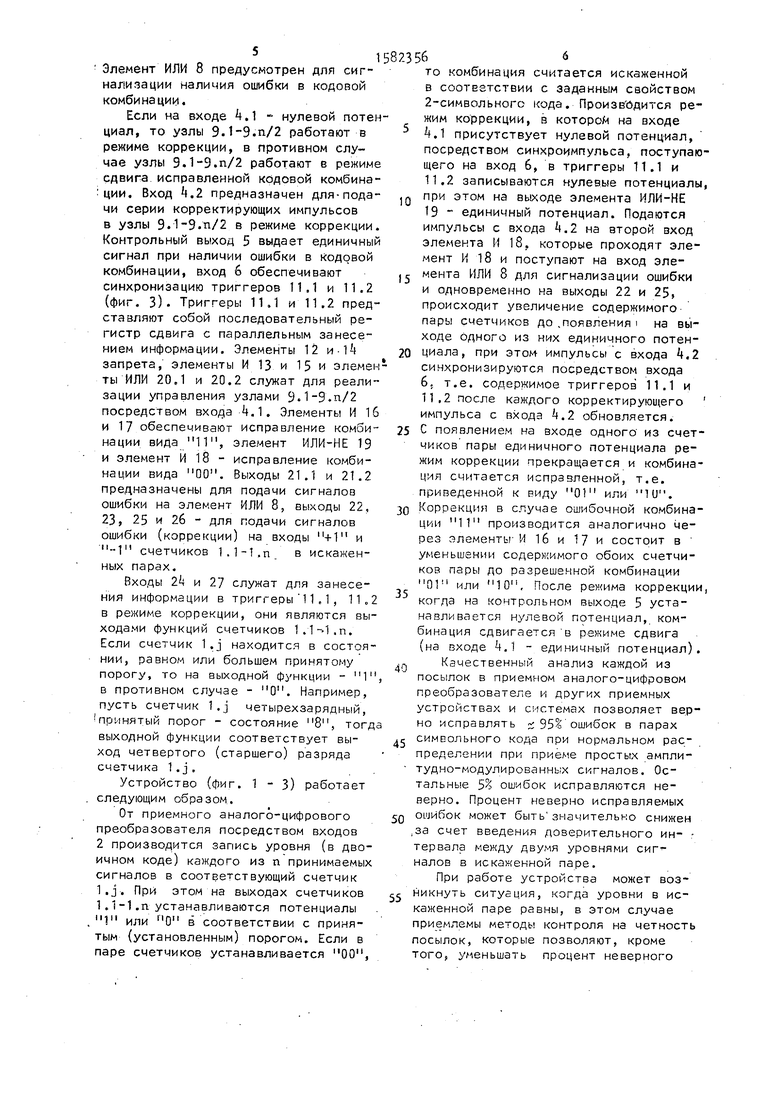

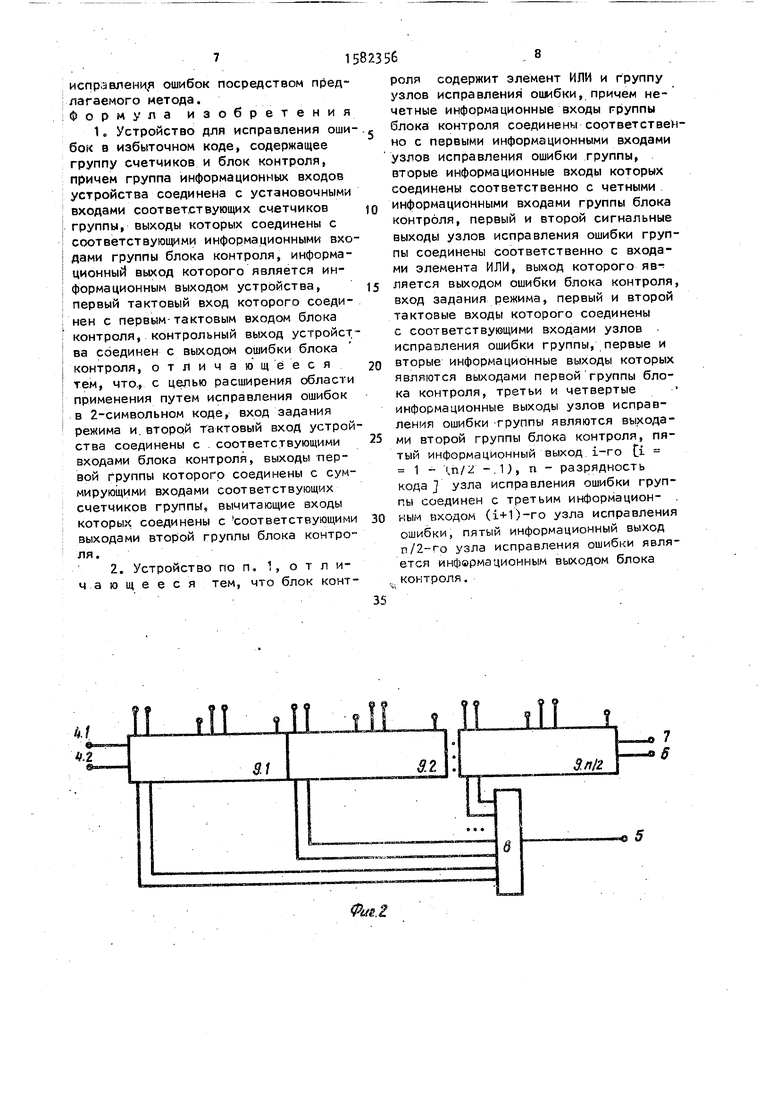

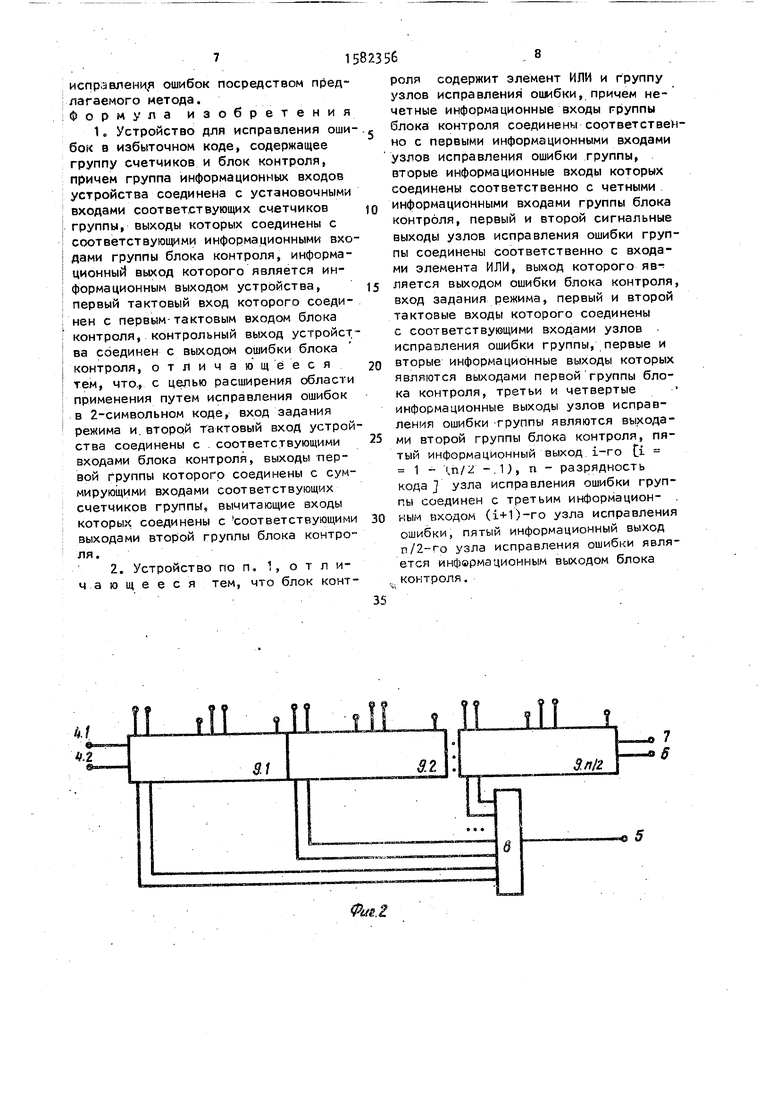

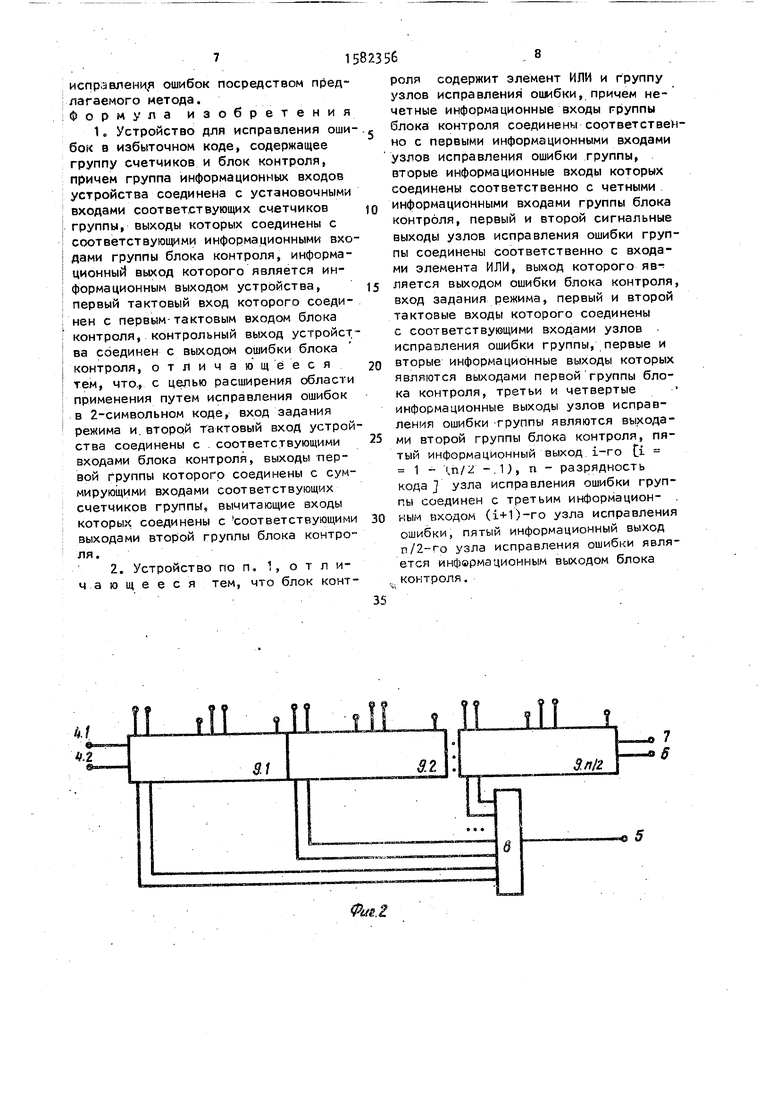

На фиг. 1 представлена схема устройства для исправления ошибок в избыточном коде на фиг. 2 - схема блока контроля; на фиг. 3 схема узла исправления ошибки.

УстрЬйство (фиг. 1) содержит группу счетчиков 1.1-1.П (п - разрядност кода), группу информационных входов 2 устройства, блок 3 контроля, вход $.1 задания режима устройства, первый тактовый вход .2 устройства, контрольный выход 5 устройства, второй тактовый вход 6 устройства и информационный выход 7 устройства.

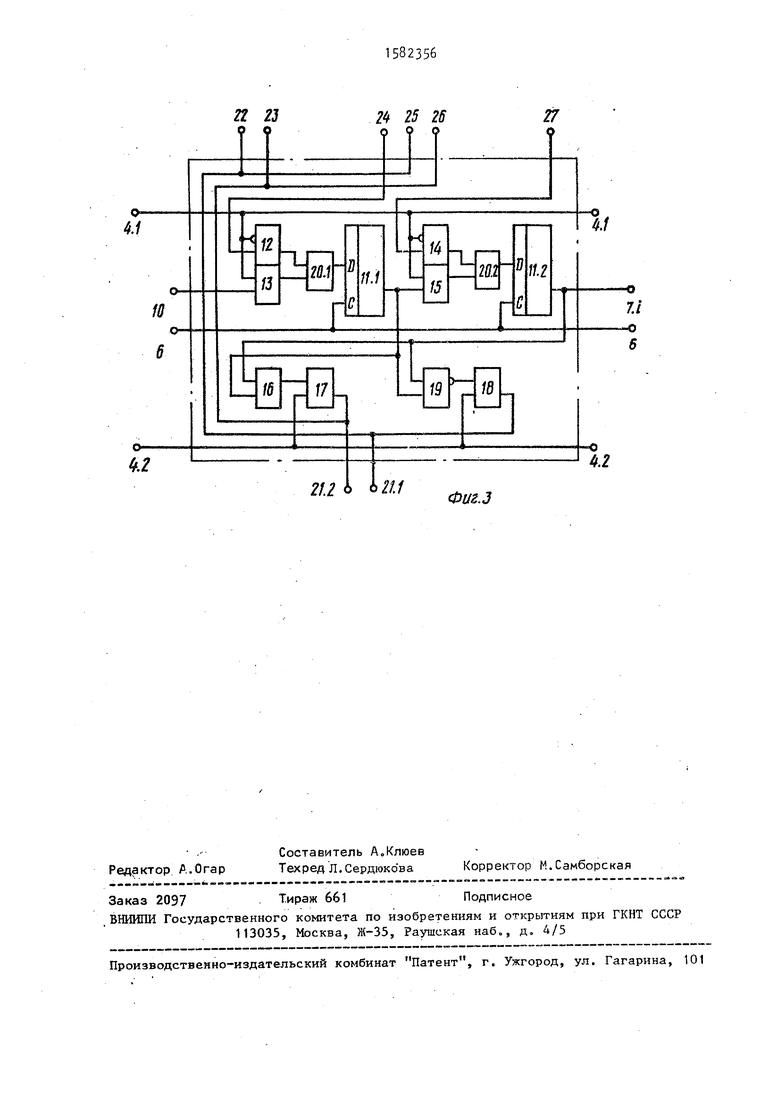

Блок 3 контроля (фиг. 2) образуют элемент ИЛИ 8 и группа узлов 9.1 - 9.п/2 исправления ошибки.

Узел 9Л исправления ошибки (фиг. 3) включает третий информационный вход 10 узла исправления ошибки, первый и второй триггеры 11.1 и 11.2 первый элемент 12 запрета, первый элемент И 13, второй элемент 1 зап- .рета, с второго по пятый элементы И 15 18, элемент ИЛИ-НЕ 19, первый и второй элементы ИЛИ 20.1 и 20.2, первый и второй сигнальные выходы 21.1 и 21.2 узла исправления ошибки, первый и третий информационные выходы 22 и 23 узла исправления ошиб ки, первый информационный вход 2k узла исправления ошибки, второй и четвертый информационные выходы 25 и 26 узла исправления ошибки, второй информационный вход 27 узла исправления ошибки, причем вход .1 соединен с управляющими входами элементов 12 и 1А запрета, с первыми входа . ми элементов И 13 и 15, выходы элемента 12 запрета и элементы И 13 соединены с первым и вторым входами элемента ИЛИ 20.1, выход которого соединен с информационным входом триггера 11.1, выход которого соединен с вторыми входами элементов И 15 и 16, ИЛИ-НЕ 19, выходы элемента Ik запрета и элемента И 15 сое-1, динены с первым и вторым входами элемента ИЛИ 20.2, выход которого соединен с информационным входом триггера 11.2, выход которого соеди

0

5

нен с первыми входами элементов И 16 и ИЛИ-НЕ 19, с пятым информационным выходом узла справления ошибок, вход 10 которого соединен с вторым входом элемента И 13, вход 6 соединен с синхровходами триггеров 11.1 и 11.2, выход элемента И 16 соединен с первым входом элемента И 17 выход которого является выходами 21.2, 23 и 26, выход элемента ИЛИ-НЕ 19 соединен с первым входом элемента И 18, выход которого является выходами 21.1, 22 и 25, вход .2 соединен с вторыми входами элементов И 17 и 18, входы 2k и 27 соединены с информационными входами элементов 12 и 1 запрета соответственно.

В 2-символьном коде единица представляется как 10, а ноль - как 01. При однократной ошибке в паре 10 или 01 типа перехода 0-1

,или 1-0 возникает запрещенная комбинация 00 или 11. 00 свиде-- тельствует об ошибке 1-0, а 11 - об ошибке 0-1. Если при приеме элементарной посылки не принимать однозначное решение О или 1, а привести преобразование уровня CHI- нала в двоичный код, то далее в реверсивных счетчиках можно осуществить операцию сравнения двух кодов (уровней) для простых амплитудно-модули- рованных сигналов (для других видов посыпок приемлемо использование различных весовых коэффициентов). При сравнении кодов (уровней) элементов искаженных посылок 00 и 11 приходят к решению какая комбинация из разрешенных 01 и 10 наиболее близка к искаженной. На принципе сравнения путем вычета или сложения в паре счетчиков последовательности единиц искаженных кодов (уровней) основана работа устройства.

Группа счетчиков 1.1-1.П предназначена для занесения кодов (уровней, весовых коэффициентов) сигналов О или 1 с целью последующего сравнения (коррекции) их в искаженных парах 11 и 00. Входы 2 (2.11-2.nk) предназначены для занесения в счетчики f.f - t.n кодов сигналов параллельным способом. Узлы 9-1 9-п/2

исправления ошибки служат для коррекции (исправления) сигналов в искаженных парах и последующего последовательного считывания исправленной кодовой комбинации через выход 7.

0

5

0

5

0

Элемент ИЛИ 8 предусмотрен для сигнализации наличия ошибки в кодовой комбинации.

Если на входе 4.1 - нулевой потенциал, то узлы 9.1-9-П/2 работают в режиме коррекции, в противном случае узлы 9..п/2 работают в режиме сдвига исправленной кодовой комбинации. Вход 4.2 предназначен для-подачи серии корректирующих импульсов в узлы 9.1-9.П/2 в режиме коррекции. Контрольный выход 5 выдает единичный сигнал при наличии ошибки в кодовой комбинации, вход 6 обеспечивают синхронизацию триггеров 11.1 и 11.2 (фиг, 3). Триггеры 11.1 и 11.2 представляют собой последовательный регистр сдвига с параллельным занесением информации. Элементы 12 и 14 запрета, элементы И 13 и 15 и элементы ИЛИ 20.1 и 20.2 служат для реализации управления узлами 9..п/2 посредством входа 4.1. Элементы И 16 и 17 обеспечивают исправление комбинации вида 11, элемент ИЛИ-НЕ 19 и элемент И 18 - исправление комбинации вида 00. Выходы 21.1 и 21.2 предназначены для подачи сигналов ошибки на элемент ИЛИ 8, выходы 22, 23, 25 и 26 - для подачи сигналов ошибки (коррекции) на входы +1 и -1 счетчиков 1.1-1,п в искаженных парах.

Входы 2k и 27 служат для занесения информации в триггеры 11.1, 11 . 2 в режиме коррекции, они являются выходами функций счетчиков 1..п. Если счетчик 1,j находится в состоянии, равном или большем принятому порогу, то на выходной функции - 1,

158

в противном случае - О. Например, пусть счетчик l.j четырехзарядный, поднятый порог - состояние 8, тогда выходной функции соответствует выход четвертого (старшего) разряда счетчика 1.j„

Устройство (фиг. 1 - 3) работает следующим образом.

От приемного аналого-цифрового преобразователя посредством входов 2 производится запись уровня (в двоичном коде) каждого из п принимаемых сигналов в соответствующий счетчик 1.j. При этом на выходах счетчиков 1 .1 -1 .п устанавливаются потенциалы 1 или О в соответствии с принятым (установленным) порогом. Если в паре счетчиков устанавливается 00,

82356

10

то комбинация считается искаженной в соответствии с заданным свойством 2-символьного кода. Производится режим коррекции, в которой на входе 4.1 присутствует нулевой потенциал, посредством синхроимпульса, поступающего на вход 6, в триггеры 11.1 и 11.2 записываются нулевые потенциалы, при этом на выходе элемента ИЛИ-НЕ 19 единичный потенциал. Подаются импульсы с входа 4.2 на второй вход элемента И 18. которые проходят элемент И 18 и поступают на вход элеjr мента ИЛИ 8 для сигнализации ошибки и одновременно на выходы 22 и 25, происходит увеличение содержимого пары счетчиков до .появления i на выходе одного из них единичного потенциала, при этом импульсы с входа 4.2 синхронизируются посредством входа 6; т.е. содержимое триггеров 11.1 и 11.2 после каждого корректирующего импульса с входа 4.2 обновляется. С появлением на входе одного из счетчиков пары единичного потенциала режим коррекции прекращается и комбинация считается исправленной, т.е. приведенной к РИДУ 01 или 1U.

Зо Коррекция в случае ошибочной комбинации 11 производится аналогично через элементы И 16 и 17 и состоит в уменьшении содержимого обоих счетчиков пары до разрешенной комбинации

20

25

5

0

5

0

5

ОТ1 или 10, После режима коррекции, когда на контрольном выходе 5 устанавливается нулевой потенциал, комбинация сдвигается в режиме сдвига (на входе 4.1 - единичный потенциал).

Качественный анализ каждой из посылок в приемном аналого-цифровом преобразователе и других приемных устройствах и системах позволяет верно исправлять 95% ошибок в парах символьного кода при нормальном распределении при приеме простых ампли- тудно-модулированных сигналов. Остальные 5% ошибок исправляются неверно. Процент неверно исправляемых ошибок может быть значительно снижен ,за счет введения доверительного ин- тервала между двумя уровнями CHI- налов в искаженной паре.

При работе устройства может возникнуть ситуация, когда уровни в искаженной паре равны, в этом случае приемлемы методы контроля на четность посылок, которые позволяют, кроме того, уменьшать процент неверного

исправления ошибок посредством предлагаемого метода,

Формула изобретения 1„ Устройство для исправления ошибок в избыточном коде, содержащее группу счетчиков и блок контроля, причем группа информационных входов устройства соединена с установочными входами соответствующих счетчиков группы, выходы которых соединены с соответствующими информационными входами группы блока контроля, информационный выход которого является информационным выходом устройства, первый тактовый вход которого соединен с первым тактовым входом блока контроля, контрольный выход устройства соединен с выходом ошибки блока контроля, отличающееся тем, что, с целью расширения области применения путем исправления ошибок в 2-символьном коде, вход задания режима и второй тактовый вход устройства соединены с соответствующими входами блока контроля, выходы первой группы которого соединены с суммирующими входами соответствующих счетчиков группы, вычитающие входы которых соединены с соответствующими выходами второй группы блока контроля.

2. Устройство по п.

отличающееся тем, что блок контроля содержит элемент ИЛИ и группу узлов исправления ошибки, причем нечетные информационные входы группы блока контроля соединены соответственно с первыми информационными входами узлов исправления ошибки группы, вторые информационные входы которых соединены соответственно с четными

информационными входами группы блока контроля, первый и второй сигнальные выходы узлов исправления ошибки группы соединены соответственно с входами элемента ИЛИ, вых-од которого является выходом ошибки блока контроля, вход задания режима, первый и второй тактовые входы которого соединены с соответствующими входами узлов исправления ошибки группы, первые и

вторые информационные выходы которых являются выходами первой группы блока контроля, третьи и четвертые информационные выходы узлов исправления ошибки группы являются выходами второй группы блока контроля, пятый информационный выход 1-го Ц. 1 - {п/2 - 1), п - разрядность кода J узла исправления ошибки группы соединен с третьим информационкым входом (i+1)-ro узла исправления ошибки, пятый информационный выход п/2-го узла исправления ошибки является информационным выходом блока контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В СИМВОЛЬНОМ КОДЕ | 1991 |

|

RU2021644C1 |

| Устройство для контроля текстовой информации | 1983 |

|

SU1328817A1 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Устройство для контроля передачи информации | 1987 |

|

SU1525702A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1751762A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

Изобретение относится к вычислительной технике и аппаратуре для приема дискретных сообщений и может использоваться для исправления ошибок в 2-х символьном коде. Цель изобретения - расширение области применения за счет исправления ошибок в 2-х символьном коде. Эта цель достигается в устройстве, содержащем группу счетчиков 1.1 - 1.N и блок 3 контроля с соответствующими связями. Устройство может быть применено в любых системах передачи дискретных сообщений, в которых решаются задачи распознавания сигналов и последующего исправления ошибок. 1 з.п. ф-лы, 3 ил.

II ill ill ll

Э.П/2

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-30—Публикация

1988-07-13—Подача