pa сигналов сброса соединен со сбросовым входом триггера управления синхронизацией, выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента НЕ а выход соединен с первым входом втог рого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход второго элемента И соединен с входом тактовой частоты блока синхронизации и входом имитатора накопителя, выход данных которого соединен с соответствующим входом второго блока приемопередатчиков, третий и четвертьй информационные входы первого блока приемопередатчиков соединены соответственно с выходами триггеров запоминания дина-гмических сигналов, входы которого соединены с выходом коммутатора контролируемых сигналов, информационные входы коммутатора сигналов сброса и коммутатор контролируемых сигналов являются соответственно первой и второй группами входов сигналов контрольных точек устройства, входы сигналов начала и конца передачи данных имитатора накопителя соединены с соответствующими выходами второго блока приемопередатчиков и блока регистров соответственно, причем имитатор накопителя содержит первьш и второй триггеры, блок постоянной памяти, счетчик, первый, второй, третий, че вертьй, пятьй и шестой эле-,менты И, сумматор по модулю два, группу элементов И, дешифратор, элемент ИЛИ, причем установочные входы первого и второго триггеров являются

входами сигналов начала и конца передачи данных имитатора накопителя, сбросовьп вход первого триггера соединен с выходом второго триггера и первым входом первого элемента И, а выход первого триггера соединен с первым входом второго элемента И, вторые входы первого и второго элементов И, первые входы третьего и четвертого элементов И образуют вход та ктовой частоты имитатора накопителя, выход первого элемента И соединен со счетным входом счетчика, выходы младших разрядов которого соединены с соответствующими входами дешифратора, выходы старших разрядов счетчика соединены с соответствующими входами дешифратора и образуют перву группу адресных входов блока постоянной памяти, вторую группу адресных входов которого образуют первый, второй и третий входы .группы адресных входов имитатора накопителя, а выходы блока постоянной памяти соединены с первыми входами элементов И группы и входами сумматора по модулю два, выход которого соединен с первым входом пятого элемента И, а выходы элементов И группы образуют выхрд данных имитатора накопителя, выходы дешифратора соединены соответственно со сбросовым входом второго триггера и вторыми входами третьего и четвертого элементов И, выходы которых и выход первого элемента И соединены с входами элемента ИЛИ, выход которого соединен с первым входом шестого элемента И, второй вход которого является четвертым входом адресной группы входов имитатора накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительного комплекса с накопителем на магнитной ленте | 1987 |

|

SU1418721A2 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Устройство для управления обменом информацией накопителя на магнитной ленте с электронно-вычислительной машиной | 1983 |

|

SU1128245A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА С НАКОПИТЕЛЕМ EIA МАГНИТНОЙ ЛЕНТЕ, содержащее первьй и второй блоки приемопередатчиков,, блок регистров, блок циклического контроля, блок хранения признаков состояния, генератор тактовых импульсов, блок синхронизации,причем первьй информационньй вход первого блока приемопередатчиков соединен с входной шиной устройства, а информационный выход соединен с выходной шиной устройства и первым информационным входом блока регистров, второй информационньй вход которого соединен с выходом блока хранения признаков состояния, а информационный выход блока регистров соединен с вторым и первым информационными входами соответственно первого блока приемопередатчиков и блока циклического контроля, второй информационный вход которого соединен с выходом данных второго блока приемопередатчиков и входной шиной накопителя, выход данных блока циклического контроля соединен с информационными входами блока хранения признаков состояния и второго блока приемопередатчиков и третьим информационным входом блока регистров, вход данных второго блока приемопередатчиков соединен с выходной шиной накопителя, выходы блока синхронизации соединены соответственно с первым и вторым входами синхросигналов блока циклического контроля и блока хранения признаков состояния и с входом синхросигналов второго блока приемопередатчиков, отличающееся тем, что, с (Л целью повышения точности локализации неисправности, в него введены р 2гистр хранения режимов контроля, управления синхронизацией, имитатор накопителя, коммутатор контролируемых сигналов, блок триггеров запоминания динамических сигналов, ком42 мутатор сигналов сброса, блок управto ления синхронизацией, содержащий пер00 вьй и второй элементы И, элемент НЕ, оо элемент ИЛИ, причем группа входов UD регистра хранения режимов контроля и установочный вход триггера управления синхронизацией соединены с информационным выходом первого блока приемопередатчгчков, группа выходов регистра хранения режимов контроля соединена с группами адресных входов коммутатора контролируемых сигналов, коммутатора сигналов сброса, группой адресных входов имитатора накопителя, входом элемента НЕ и первым входом первого -элемента И, выход коммутато

Изобретение относится к вычислительной технике, а именно к устройствам управления накопителями на магнитной ленте.

Известно устройство связи вычислительной машины с блоком памяти на магнитной ленте, содержащее блок связи с вычислительной машиной, автоматический селектор плотности записи

информации, постоянную память и блок формирователэй СОНедостатком известного устройства является отсутствие аппаратно-программных средств, обеспечивающих надежную диагностику и отыскание неисправностей.

Известен также блок управления периферийными устройстиами, содержащий

интерфейсньй блоЛ связи с вычислительной системой, формирователи имитационных сигналов,, схему управления устройство приема интерфейсных сигналов из замкнутых шин и имитационных сигналов из разомкнутых шин и схем формирования комбинированных сигналов Г21.

Однако количество аппаратуры,используемой для организации самодиагностики достаточно велико, а достоверность отыскания неисправности недостаточно высока.

Наиболее близким к предлагаемому по технической сущности является контроллер устройства внешней памяти на магнитной ленте, содержащий блок связи с системной шиной, адресуемые регистры, блок обработки данных,блок признаков состояния, генератор и делитель частоты, синхронизатор записи, синхронизатор воспроизведения, синхронизатор работы накопителей, блок связи с накопителями и блок проверки контроллера в автономных режимах функционирования Гз.

Недостатками этого контроллера устройства внешней памяти на магнитной ленте являются относительно невысокая надежность из-за низконадежных аппаратурных средств (в основной переключателей), используемых для обеспечения проверки функционирования контроллера в автономном режиме, а также недостаточная достоверность контроля неисправностей, так как не предусмотрен останов синхронизатора контроллера при обнаружении неисправностей и нет аппаратуры, анализирующей характер и место неисправности.

Цель изобретения - повьшение точности локализации неисправности.

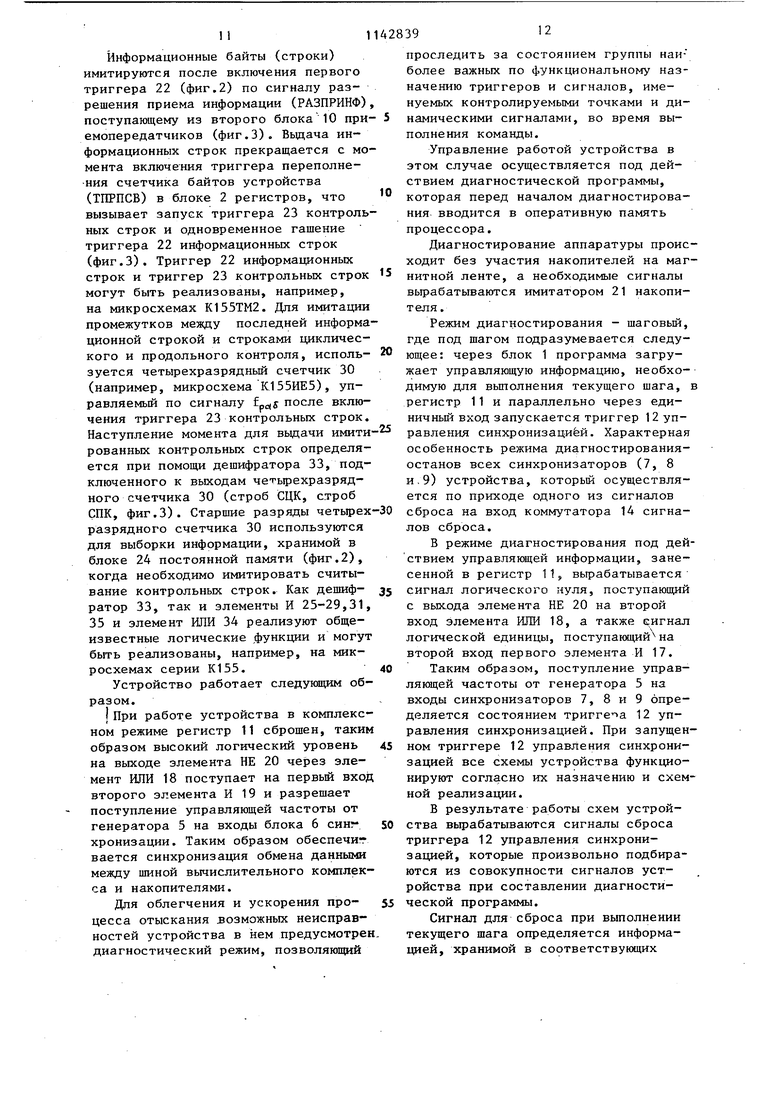

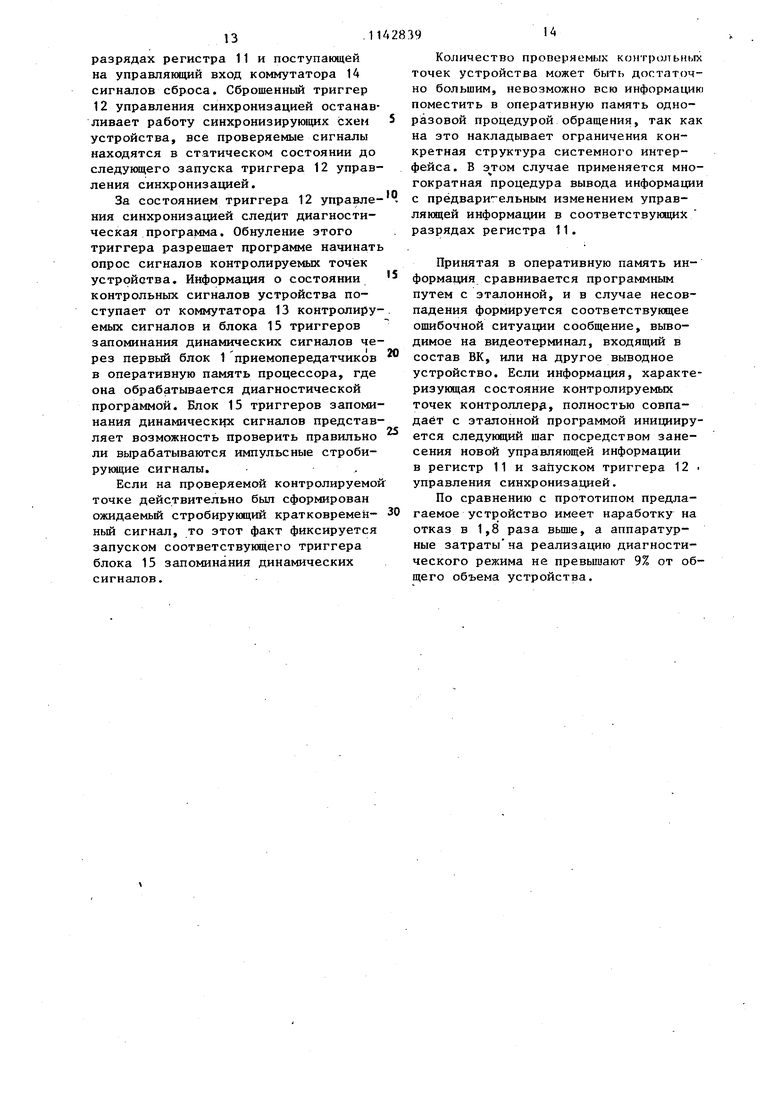

Поставленная цель достигается тем, что в устройство для сопряжения вычислительного комплексас накопите лем на магнитной ленте, содержащее первый и второй блоки приемопередатчиков, блок регистров, блок циклического контроля, блок хранения признаков состояния, генератор тактовых импульсов, блок синхронизации, причем первьй информационный вход первого блока приемопередатчиков соединен с входной шиной устройства, а информационный выход соединен с выходной шиной устройства и первым информационным входом блока регистров, второй информационный вход которого соединен с соответствующим выходом блок хранения признаков состояния, а информационный выход блока регистров соединен с первым и вторым информационными входами соответственно первого блока приемопередатчиков и блока циклического контроля, второй информационный вход которого соединен с выходом данных второго блока приемопередатчиков и входной шиной накопителя, выход данных блока циклического контроля соединен с информационными входами блока хранения признаков состояния и второго блока приемопередатчиков и третьим информационным входом блока регистров, вход данных второго блока приемопередатчиков соединен с выходной шиной накопителя, выходы блока синхронизации соединены соответственно с первым и вторым входами синхросигналов блока циклического контроля и блока хранения признаков состояния и с входом синхросигналов второго блока прием9передатчиков, введены регистр хранения режимов контрооля, триггер управления синхронизацией, имитатор накопителя, коммутатор контролируемых сигналов, блок триггеров запоминания динамических сигналов, коммутатор сигналов сброса, блок управления синхронизацией, содержащий первый и второй элементы И, элемент НЕ, элемент ИШ1, причем группа входов регистра хранения режимов контроля и установочный вход триггера управления синхронизацией соединены с информационным выходом первого блокд приемопередатчиков, группа выходов регистра хранения режимов контроля соединена с группами адресных входов коммутатора контролируемых сигналов, коммутатора сигналов сброса, группой адресных входов имитатора накопителя входом элемента НЕ и первым входом первого элемента И, выход коммутатора сигналов сброса соединен со сбросовым входом триггера управления синхронизацией, выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента НЕ,а выход соединен с первым входом второго элемента И, второй вход которого соединен с выходом генератора тактовых импульсов,.выход второго элемента И,соединен с входом тактовой частоты блока синхронизации и входом имитатора накопителя, выход данных которого соединен с соответствуищим входом второго блока приемопередатчиков, третий и четвертьш информадионные входы первого блока приемопере датчиков соединены соответственно с выходами триггеров запо шнания динамических сигналов, входы которого соединены с выходом коммутатора конт ролируемых сигналов, информационные входы коммутатора сигналов сброса и коммутатора контролируемых сигналов являются соответственно первой и второй группами входов сигналов конт рольных точек устройства, входы сигналов начала и конца передачи данных имитатора накопителя соединены с соответствующими выходами второго блока приемопередатчиков и блока регист ров соответственно. Кроме того, имитатор накопителя содержит первьй и второй триггеры, блок постоянной памяти, счетчик, первый, второй, третий, четвертый, пятый и шестой элементы И, сумматор по модулю два, группу элементов И, деышфратор, элемент ИЛИ, причем установочные входы nepBoio и второго триггеров являются входами сигналов начала и конца передачи данных имитатора накопителя, сбросовьш вход первого триггера соединен с выходом второго триггера и первым входом пер вого элемента И, а выход первого триггера соединен с первым входом второго элемента И, вторые входы пер вого и второго элементов И, первые входы третьего и четвертого элементов И образуют вход тактовой частоты имитатора накопителя, выход первого элемента И соединен со счетным вход счетчика, выходы младших разрядов которого соединены с соответствующим входами дешифратора, выходы старших разрядов счетчика соединены с соответствукндими входами дешифратора и образуют первую группу адресных входов блока постоянной памяти, вторую группу адресных входов которого образуют первьй, второй и третий входы группы адресных входов имитатора накопителя, а выходы блока постоянной памяти соединены с первыми входами элементов И группы и входами сумма- тора по модулю два, выход которого, соединен с первым входом пятого элемента И, вторые входы элементов И группы соединены с выходом шестого элемента И, а выходы элементов И группы образуют выход данных имитатора накопителя, выходы дешифратора соединены соответственно со сбросовым входом второго триггера и вторыми входами третьего и четвертого элементов И, выходы которых и выход первого элемента И соединены с входами элемента ИЛИ, выход которого соединен с первым входом шестого элемента И, второй вход которого является четвертым входом адресной группы входов имитатора накопителя. На фиг.1 представлена структурная схема устройства для сопряжения вычислительного коьшлекса с накопителем на магнитной ленте-, на фиг. 2 функциональная схема имитатора накопителя-, на фиг.З - временная диаграмма работы имитатора накопителя. Устройство для сопряжения содержит первьй блок 1 приемопередатчиков, блок 2 регистров, блок 3 цикли еского контроля, блок 4 хранения признаков состояния, генератор 5 тактовых импульсов, блок 6 синхронизации,включающий в себя синхронизатор 7 записи, синхронизатор 8 воспроизведения, синхронизатор 9 работы накопителей, второй блок 10 приемопередатчиков регистр 11 хранения режимов контроля, триггер 12 управления синхронизацией, коммутатор 13 контролируемых сигналов, коммутатор 14 сигналов сброса, блок 15 триггеров запоминания динамических сигналов, блок 16 управления синхронизацией, первьй элемент И 17, элемент ШШ 18, второй элемент И 19, элемент НЕ 20 и имитатор 21 накопителя. Имитатор накопителя содержит триггер 22 информационных строк, триггер 23 контрольных строк, блок 24 посто-. янной памяти, первьй 25, второй 26, третий 27s четвертьй 28 элементы И, группу элементов И 29, счетчик 30, пятьй элемент И 31, сумматор 32 по , модулю два, дешифратор 33, элементно, модулю два, дешифратор 33, элемент ИЛИ 34, шестой элемент И .35. Блок 1 предназначен для электрического обеспечения связей между предлагаемым устройством и электронно-вычислительным комплексом. Он содержит узлы приемников и узлы передатчиков, дешифратор адреса, формирователь сигналов обмена с ЭВК, коммутатор, причем второй, третий и четвертьи информационные входы блока соединены с информационными входа ми коммутатора, п.ервые информационные выходы и вход соединены с выхода ми узлов передатчиков и приемников соответственно. Блок 10 предназначен для приема и передачи сигналов устройства накопителю и обратно. Он содержит узлы приемников и передатчиков. Блок 3 циклического контроля пред назначен для контроля принимаемых из накопителя данных с помощью методов циклического контроля, а также для формирования байтов циклического контроля при передаче данных в накопитель. Блок состоит из регистра перекоса, регистра продольного контроля, комбинационной схемы продольно го контроля, первого и второго регистров циклического контроля, входной логики первого и второго регистров циклического контроля, схем определения образцов согласования в первом и втором регистрах циклического контроля, схемы формирования сигналов обмена с накопителем, входы которой являются входами синхросигналов блока, выходы регистров перекоса и циклического контроля, схемы формирования сигналов обмена и сигна лы ошибок со схем контроля образуют выход блока. Информационный вход входной логики первого регистра циклического Контроля является входом блока. Блоки 1-10.могут быть вьтолнены, например, по схемам серийно выпускаемого контроллера СМ5002. Регистр 11 хранения режимов контроля РК (0:9) предназначен для хране ния управляющей информации, необходи мой для вьшолнения определенной части диагностической программы, назьгваемой шагом. РК (0:9) представляет собой десятиразрядный регистр, построенньй на динамических триггерах (К155ТМ2)о На информационные входы (входы D) поступают сигналы из вычис лительного комплекса через первый

блок 1 приемопередатчиков. Запись информации в регистр производится , по положительному фронту сигнала ВНР (занесение в регистр), которьй посту-55 пает из вычислительного комплекса через первый блок 1 приемопередатчиков на входы С всех разрядов РК (0-9) 1

синхронизацией сбрасьшается сигналом сброса, поступающим из процессора через блок 1 приемопередатчиков.

Коммутатор 13 контролируемых сигналов предназначенДЛЯ обеспечения выборки определенной части контролируемых сигналов и передачи их значе98во время обращения процессора вычислительного комплекса по адресу, присвоенному рассматриваемому регистру 11 РК (0-9). Все разряды регистра 11 РК (0-9) могут быть обнулены по инициативе процессора вычислительного комплекса интерфейсным сигналом сброса, что всегда имеет место в комплексном режиме работы. Выходы регистра 11 имеют следующее функциональное назначение. РК (0) - единичное состояние данного разряда, указывает, что происходит диагностирование аппаратуры устройства, РК (0) поступает на вход элемента И 17 и способствует останову синхронизирующих схем устройсхва после сброса триггера 12 управления синхронизацией. В комплексном режиме рабо-. ты нулевое значение РК (0) через элемент ИЛИ 18 обеспечивает непрерывную синхронизацию схем устройства. РК (j) nocTjmaeT на имитатор 21 накопителя и разрешает формирование сигналов, имитирующих интерфейсные сигналы накопителя. РК (2:4) - разряды, поступают на имитатор 21 накопителя и определяют информацию, имитирующую сигналы на шинах воспроизведения накопителя. РК (5:7) поступают на управляющие входы коммутатора 13 контролируемых сигналов. РК (8:9) являются управляющими входами коммутатора 14 сигналов сброса. Триггер 12 управления синхронизацией предназначен для запуска и останова синхронизирующих схем устройства в диагностическом режиме и является динамическим триггером,.реализованным на микросхеме К155ТМ2, D-вход триггера подключен к блоку 1. Занесение информации в триггер происходит по сигналу ЗНРК, поступающему на С-вход триггера. При единичном положении триггера синхронизаторы контроллера приводятся в действие. Триггер 12 управления

НИИ в процессор вычислительного комплекса для их обработки диагностической программой. Коммутатор 13 контролируемых сигналов может быть реализован на шести коммутаторах, содержа щих по восемь входов на один выход со стробированием (К155КП7). На управляющие входы поступает информация хранимая в РК (5:7). К информационны входам от 1 до N () подключаются конкретные контролируемые сигналы (например, выходы характерных триггеров, комбинационных схем и т.д.).

Коммутатор 14 сигналов сброса предназначен для сброса триггера управления синхронизацией и реализован на микросхеме К155КП7. Коммутатор управляется под действием информации, хранимой в РК (8:9), которая поступает на управляющие его входы. К информационным входам от 1 до К (в конкретном случае ) подключаются характерные сигналы, вырабатьгоаемые схемами устройства, определяющие момент проверки. Сигналы, поступаклцие на информационные входы коммутаторов 13 и 14, выбираются свободно и учитываются при составлении диагностической программы.

Блок 15 триггеров запоминания динамических сигналов предназначен для запоминания динамических сигналов, так как среди совокупности контролируемых сигналов некоторые схемы вьфабатывают кратковременные импульсные сигналы, используемые для стробирования и управления работой триггеров и регистров устройства.

С целью проверки, вьфабатываются ли в проверяемых цепях нужные динамические сигналы, введен блок 15 триггеров запоминания динамических сигналов, реализованный на триггерах DC-типа (микросхемах К155ТМ2) К информационным входам (D-входам) триггеров подведен уровень логической единицы. На С-входы каждого триггера блока 15 триггеров запоминания динамических сигналов поступают сигналы с выходов коммутатора 13 контролируемых сигналов.

Указанная связь осуществляется только для тех коммутаторов, которые предназначены для обслуживания динамических сигналов.

Таким образом, динамические сигналы, которые проверяются во время выполнения текущего шага диагностической программы сначала запоминаются на соответствующих триггерах блока 15 триггеров запоминанргя динами4edKHX сигналов. Выходы блока 15 триггеров запоминания динамических сигналов параллельно с выходами коммутатора 13 контролируемых сигналов через первый блок 1 приемопередатчиков поступают в процессор вычислительного кошлекса. Все триггеры обнуляются при занесении информации в адресуемый регистр диагностики по .сигналу ЗНРК.

Имитатор 21 накопителя предназначен для имитации интерфейсных сигналов накопителя в диагностическом режиме работы контроллера.

Основное функциональное назначени имитатора 21 накопителя - имитироват сигналы, поступаюоще в устройство по щинам воспроизведения. Имитируемые информационные и контрольные строки извлекаются из 24 постоянной памяти (например, микросхема К155РЕЗ При имитации информационных строк формируется зона, где все байты имеют одинаковые коды (одинаковую конфигурацию единиц) в пределах данной зоны.

В зависимости от значений регистра 11 хранения режимов контроля имитируются зоШ)1 с информацией:

а),, , ...

б)55,55,55,

в)АА,АА,АА, ...

г)80,80,80,

Строки циклического контроля СЦК и строки продольного контроля СПК определены для каждого вида информации для зон длиной и байтов. Все выходы блока 24 постоянной памяти поступают на входы сумматора 32 по модулю два (например, микросхема К155ИП2), на выходе которой формируется контрольный разряд считываемого байта.

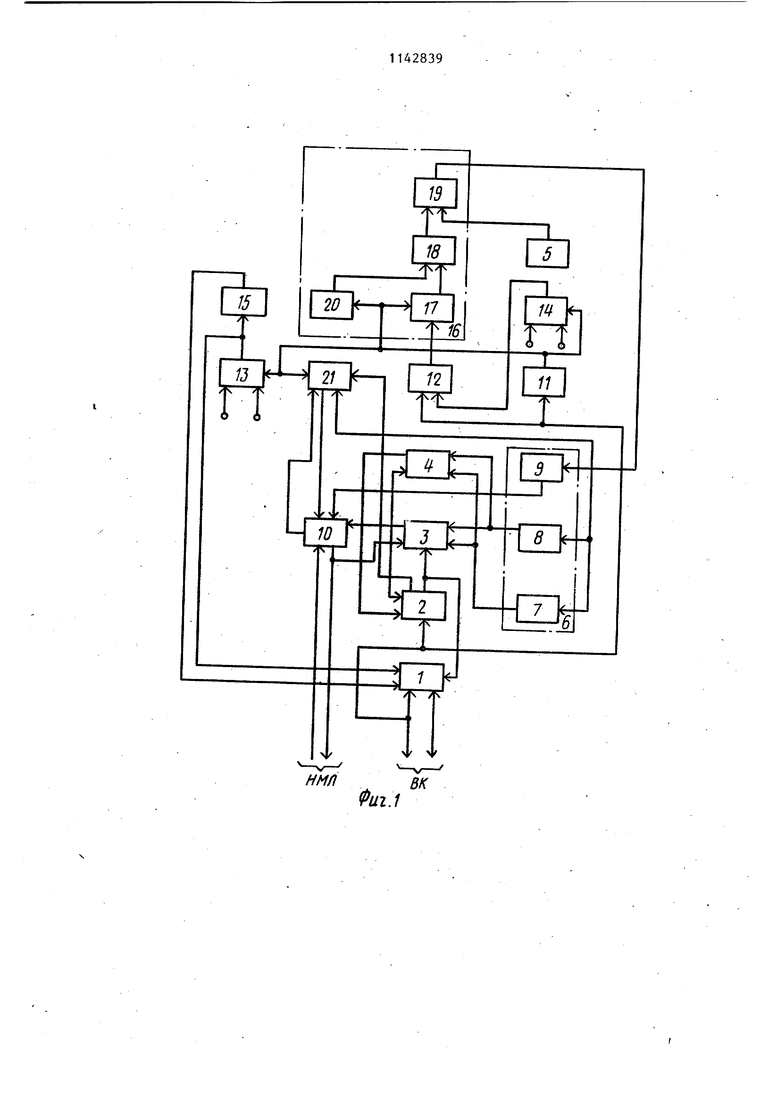

Вьщача информационных и контрольных строк происходит под управлением сигналов рдр и „цф , вьфабатываемы устройством. Временная диаграмма работы имитатора накопителя представлена на фиг.З. Час-тота сигналов fpo, и соответствует частоте следования считанных сигналов на шинах воспроизведения накопителя ШВ (0:7,К 111 Информационные байты (строки) имитируются после включения первого триггера 22 (фиг.2) по сигналу разрешения приема информации (РАЗПРИНФ) поступающему из второго блока 10 при емопередатчиков (фиг.З), Вьщача информационных строк прекращается с мо мента включения триггера переполнения счетчика байтов устройства (ТПРПСВ) в блоке 2 регистров, что вызывает запуск триггера 23 контроль ных строк и одновременное гашение триггера 22 информационных строк (фиг.З). Триггер 22 информационных строк и триггер 23 контрольных строк могут быть реализованы, например, на микросхемах К155ТМ2. Для имитации промежутков между последней информа ционной строкой и строками циклического и продольного контроля, используется четырехразрядный счетчик 30 (например, микросхема К155ИЕ5), управляемый по сигналу fpos после включения триггера 23 контрольных строк. Наступление момента для вьщачи имити

рованных контрольных строк определяется при помощи дешифратора 33, подключенного к выходам четырехразрядного счетчика 30 (строб СЦК, строб СПК, фиг.З). Старшие разряды четырех-30

разрядного счетчика 30 используются для выборки информации, хранимой в блоке 24 постоянной памяти (фиг.2), когда необходимо имитировать считывание контрольных строк. Как дешифратор 33, так и злементы И 25-29,31, 35 и элемент ИЛИ 34 реализуют общеизвестные логические функции и могут быть реализованы, например, на микросхемах серии К155.

Устройство работает следующим образом.

I При работе устройства в комплексном режиме регистр 11 сброшен, таким образом высокий логический уровень на выходе элемента НЕ 20 через элемент ИЛИ 18 поступает на первьй вход второго элемента И 19 и разрешает поступление управляющей частоты от генератора 5 на входы блока 6 синг хронизации. Таким образом обеспечит вается синхронизация обмена данными между шиной вычислительного комплекса и накопителями.

Для облегчения и ускорения процесса отыскания возможных неисправностей устройства в нем предусмотрен диагностический режим, позволяющий

особенность режима диагностированияостанов всех синхронизаторов (7, 8 и,9) устройства, которьй осуществляется по приходе одного из сигналов

лов сброса.

В режиме диагностирования под действием управляющей информации, занесенной в регистр 11, вырабатывается сигнал логического нуля, поступающий с выхода элемента НЕ 20 на второй вход элемента ИЛИ 18, а также сигнал логической единицы, поступающий на второй вход первого элемента И 17.

Таким образом, поступление управ- лякнцей частоты от генератора 5 на входы синхронизаторов 7, 8 и 9 определяется состоянием триггера 12 управления синхронизацией. При запущенном триггере 12 управления синхронизацией все схемы устройства функционируют согласно их назначению и схемной реализации.

В результате работы схем устройства вырабатываются сигналы сброса триггера 12 управления синхронизацией, которые произвольно подбираются из совокупности сигналов устройства при составлении диагностической программы.

Сигнал для сброса при выполнении текущего шага определяется информацией, хранимой в соответствующих 39 проследить за состоянием группы наиболее важных по функциональному назначению триггеров и сигналов, именуемых контролируемыми точками и динамическими сигналами, во время выполнения команды. Управление работой устройства в этом случае осуществляется под действием диагностической программы, которая перед началом диагностирования вводится в оперативную память процессора. Диагностирование аппаратуры происходит без участия накопителей на магнитной ленте, а необходимые сигналы вырабатываются имитатором 21 накопителя . Режим диагностирования - шаговый, где под шагом подразумевается следующее: через блок 1 программа загружает управляющую информацию, необходимую для вьшолнения текущего шага, в регистр 11 и параллельно через единичньш вход запускается триггер 12 управления синхронизацией. Характерная сброса на вход коммутатора 14 сигнаразрядах регистра 11 и поступающей на управляющий вход коммутатора 14 сигналов сброса. Сброшенный триггер 12 управления синхронизацией останавливает работу синхронизирующих схем устройства, все проверяемые сигналы находятся в статическом состоянии до следующего запуска триггера 12 управления синхронизацией. За состоянием триггера 12 управления синхронизацией следит диагностическая nporpaNiMa. Обнуление этого триггера разрещает программе начинать опрос сигналов контролируемых точек устройства. Информация о состоянии контрольных сигналов устройства поступает от коммутатора 13 контролируемых сигналов и блока 15 триггеров запоминания динамических сигналов через первый блок 1 приемопередатчиков в оперативную память процессора, где она обрабатывается диагностической программой. Блок 15 триггеров запоминания динамическфс сигналов представляет возможность проверить правильно ли вьфабатываются импульсные стробирукмцие сигналы.. Если на проверяемой контролируемой точке действительно был сформирован ожидаемьй стробирующий кратковременный сигнал, то этот факт фиксируется запуском соответствуняцего триггера блока 15 запоминания динамических сигналов. Количество проперяемых контрольных точек устройства может быть достаточно большим, невозможно всю информацию поместить в оперативную память одноразовой процедурой обращения, так как на это накладывает ограничения конкретная структура системного интерфейса. В случае применяется многократная процедура вывода информации с прёдвари ельным изменением управлякнцей информации в соответствующих разрядах регистра 11. Принятая в оперативную память информация сравнивается программным путем с эталонной, и в случае несовпадения формируется соответствующее ошибочной ситуации сообщение, выводимое на видеотерминал, входящий в состав ВК, или на другое выводное устройство. Если информация, характеризунщая состояние контролируемых точек контроллеру, полностью совпадает с эталонной программой инициируется следующий шаг посредством занесения новой управляющей информации в регистр 11 и запуском триггера 12 управления синхронизацией. По сравнению с прототипом предлагаемое ус тр ойство имеет наработку на отказ в 1,8 раза вьше, а аппаратурные затратына реализацию диагностического режима не превьииают 9% от общего объема устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ХИРУРГИЧЕСКОЙ КОРРЕКЦИИ СЛОЖНЫХ КОМБИНИРОВАННЫХ СОЧЕТАННЫХ ДЕФЕКТОВ КОСТИ И МЯГКИХ ТКАНЕЙ ГОЛЕНИ | 2006 |

|

RU2318461C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Автоматический телефонный распределитель | 1926 |

|

SU5002A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-02-28—Публикация

1983-01-26—Подача