Изобретение относится к .цифровой вычислительной технике и может быть использовано в многомашинных вычислительных системах для организации межмашинного взаимодействия.. .

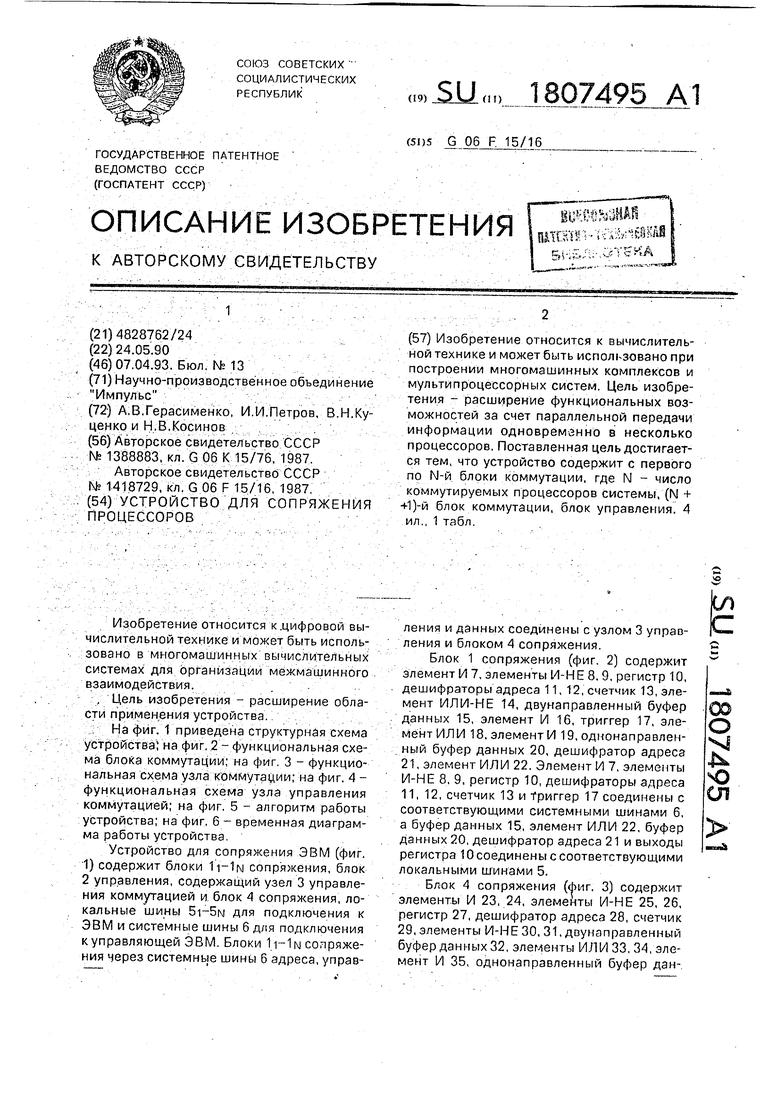

, Цель изобретения - расширение области применения устройства.. ; На фиг. 1 приведена структурная схема устройст фиг, 2 - функциональная схема блока коммутации; на фиг. 3 - функциональная схема узла коммутации; на фиг. 4 - функциональная схема узла управления коммутацией; на фиг. 5 - алгоритм работы устройства; на фиг. 6 - временная диаграмма работы устройства.

Устройство для сопряжения ЭВМ (фиг. 1) содержит блоки 11-1 N сопряжения, блок 2 управления, содержащий узел 3 управления коммутацией и. блок 4 сопряжения, локальные шины 5i-5r i для подключения к ЭВМ и системные шины 6 для подключения управляющей ЭВМ. Блоки II-IN сопряжения через системные шины 6 адреса, управления и данных соединены с узлом 3 управления и блоком 4 сопряжения.

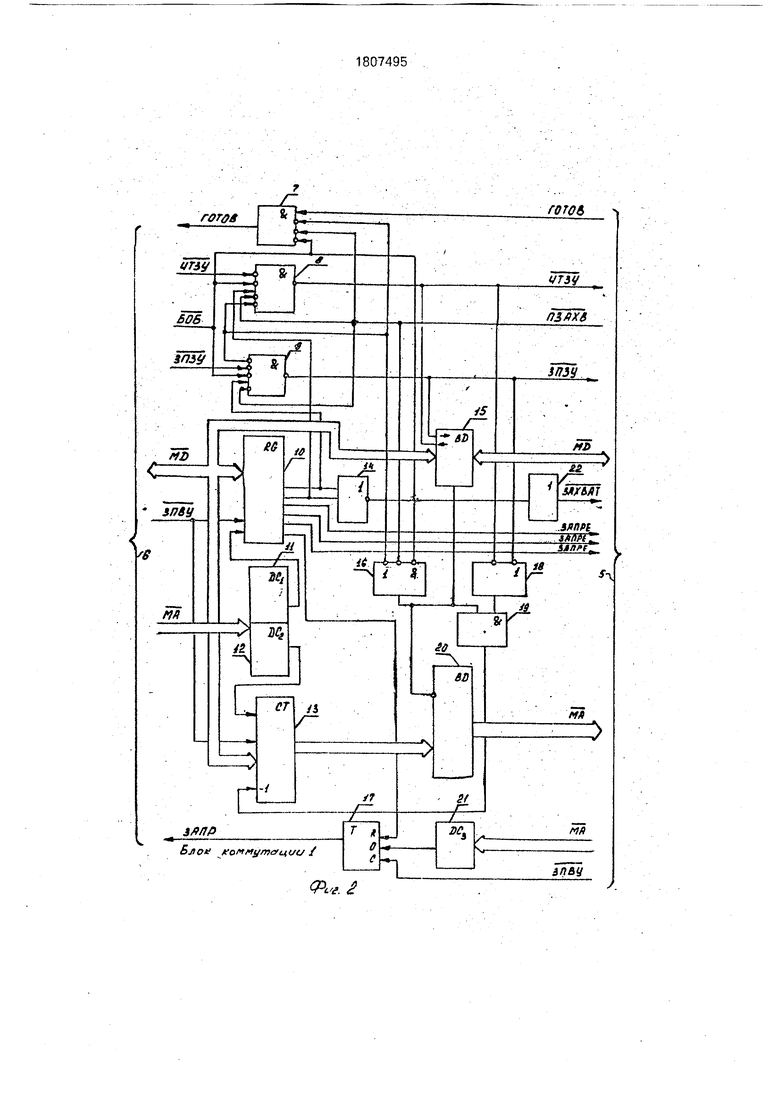

Блок 1 сопряжения (фиг. 2) содержит элемент И 7, элементы И-НЕ 8, 9, регистр 10, дешифраторы адреса 11, 12,счетчик .элемент ИЛИ-НЕ 14, двунаправленный буфер данных 15, элемент И 16, триггер 17, элемент ИЛИ 18, элемент И 19, однонаправленный буфер данных 20, дешифратор адреса 21, элемент ИЛИ 22. Элемент И 7, элементы И-НЕ 8, 9, регистр 10, дешифраторы адреса 11, 12, счетчик 13 и Триггер 17 соединены с соответствующими системными шинами 6, а буфер данных 15, элемент ИЛИ 22, буфер Данных 20, дешифратор адреса 21 и выходы регистра 10 соединены с соответствующими локальными шинами 5.

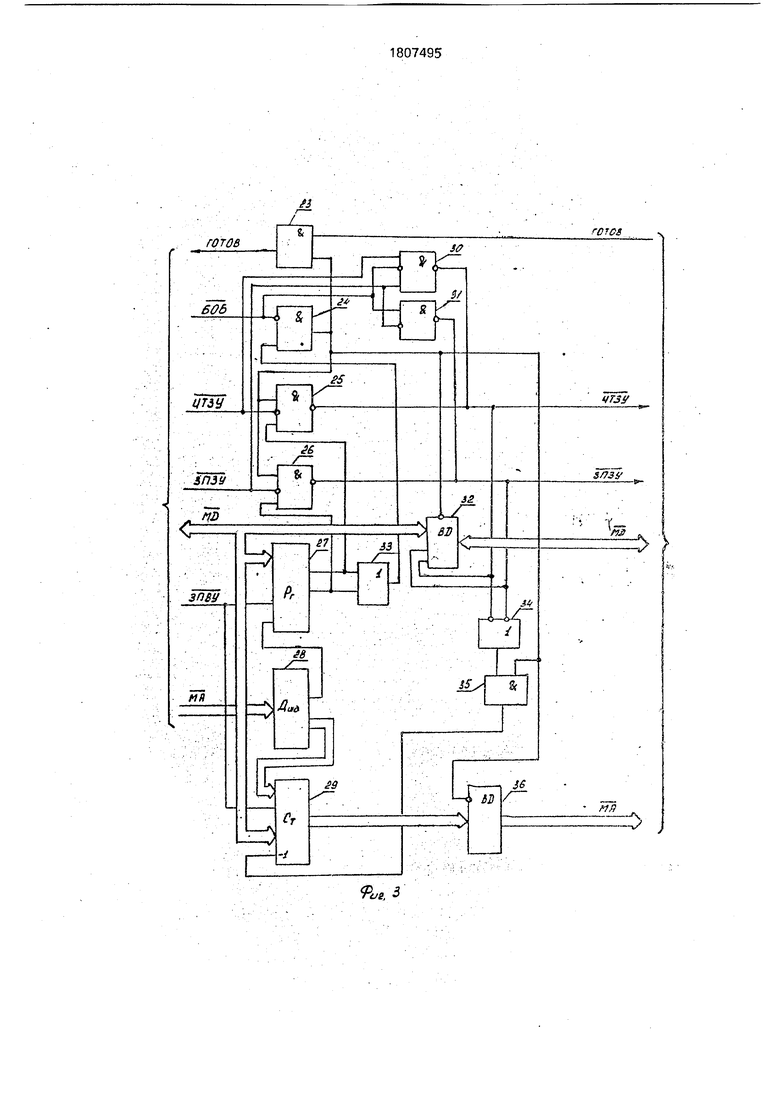

Блок 4 сопряжения (фиг. 3) содержит элементы И 23, 24, элементы И-НЕ 25, 26, регистр 27, дешифратор адреса 28, счетчик 29, элементы И-НЕ 30, 31, двунаправленный буфер данных 32, элементы ИЛИ 33, 34, элемент И 35, однонаправленный буфер данО х|

Ю

«™s

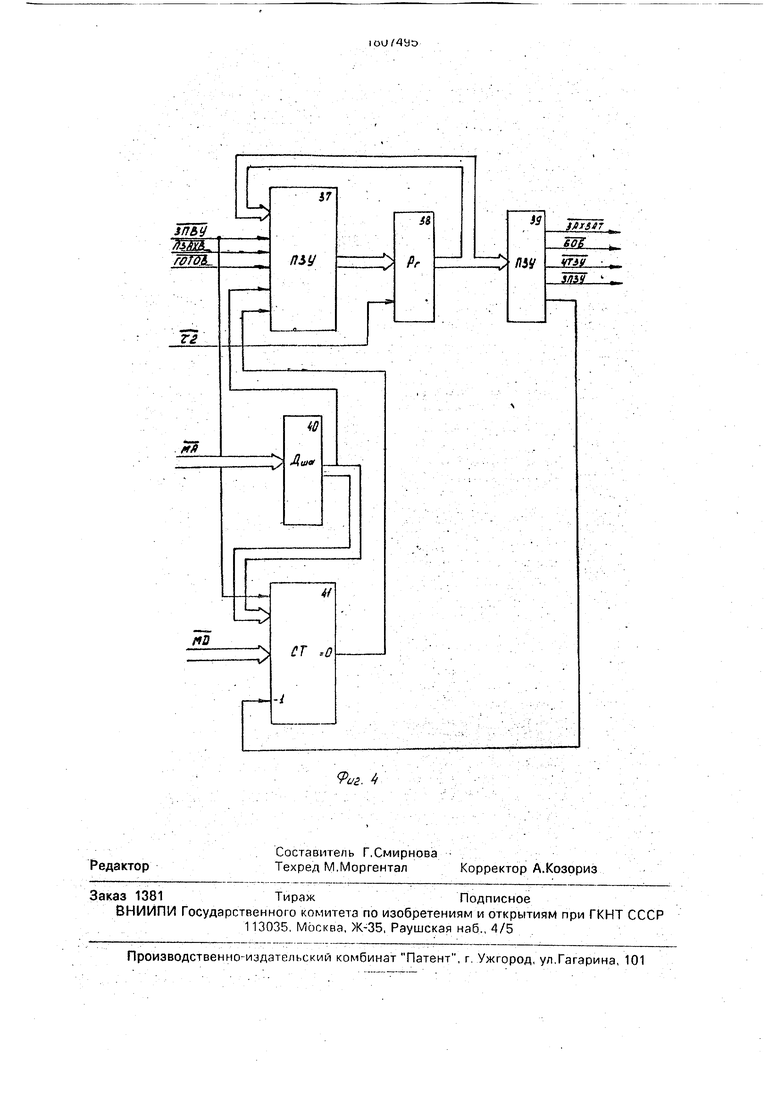

ных 36. Элементы 23-26, регистр27, дешифратор адреса 28, счетчик 29 соединены с соответствующими шинами управляющей ЭВМ, а элементы 30, 31, буфер данных 32, элементы 34, 35 и буфер данных 36 - с соответствующими шинами 6. Узел управления коммутацией (фиг. 4) содержит постоянное запоминающее устройство (ПЗУ) 37, регистр 38, ПЗУ 39, дешифратор адреса 40, счетчик 41. Выходы регистра 38 соединены с входами ПЗУ 37, 39, дешифратор адреса 40 соединен с входом счетчика 41. Устройство для сопряжения ЭВМ через локальные шины 5 и системные шины б подключается к группе ЭВМ, между которыми необходимо реализовать обмен информацией.

Устройство работает следующим образом.

Устройство обеспечивает два режима работы:

- передача информации с системных шин 6 параллельно во все локальные шины 5, к которым подключены ЭВМ-приемники, причем передача информации осуществляется в режиме прямого доступа к памяти как передающей, так и принимающей ЭВМ:

- передача информации в режиме прямого доступа к памяти с одной из локальных шин 5 параллельно во все остальные локальные шины 5 и, кроме того, в системные шины 6.

Первый режим работы реализуется следующей последовательностью:

1. ЭВМ через системные шины 6 загружает начальный адрес памяти, в которой находится информация для передачи, в счетчик 29 узла 4 коммутации.

2. ЭВМ через системные шины 6 последовательно загружает начальные адреса в счетчики 13 необходимых бликов 1 сопряжения, связанных через локальные шины 5 с ЭВМ-приемниками.

3. Каждый блок 1 сопряжения через шины 6 настраивается на режим записи информации в память ЭВМ-приемника.

4. Узел 4 сопряжения через шины 6 настраивается на режим чтения массива информации из памяти ЭВМ-передатчика.

5. В счетчик 41 узла 3 управления коммутацией записывается через шины 6 число байт массива передаваемой информации.

6. Управление обменом информацией передается узлу 3 управления коммутацией, который выставляет на управляющие системные шины 6 сигнал ЗАХВАТ, переводит процессор ЭВМ-передатчика в третье состояние и берет на себя организацию обмена (логика работы иллюстрируется фиг. 5 и 6).

7. После конца обмена (т.е. когда содержимое счетчика 41 узла 3 управления коммутацией станет равным нулю) снимается сигнал ЗАХВАТ и ЭВМ-передатчик выдает 5 команды через блоки 1 Запустить функциональную программу и затем продолжает выполнение своей программы.

Получив сообщение о завершении выполнения программы с переданной ранее 0 информацией приемом соответствующих сигналов Запрос прерываний на системные шины 6с локальных шин 5через дешифратор адреса 21 и триггер 17, управляющая ЭВМ через шины 6 приступает к подготовке 5 обмена информацией между локальными шинами в соответствии с необходимым алгоритмом обмена. :

Управляющая ЭВМ определяет ЭВМ- передатчик и ЭВМ-приемники и проводит: .0 1. Загрузку начального адреса располо- . жения ийформации в блок 1, подключенный к ЭВМ-передатчику и настройку его на ре- жим чтения.

2. Загрузку начальных адресов во всех 5 блоках 1 сопряжения, которые будут подключены к ЭВМ-приемникам, и настройку их на режим записи.

3. При необходимости параллельной записи информации через шины 6 в систем- 0 ную память управляющей ЭВМ аналогично проводит подготовку блока 4 сопряжения.

4. Запись в счетчик 41 узла 3 управления коммутацией длины массива передаваемой информации.

5 После этого узел 3 управления коммутацией обеспечивает параллельно -быструю передачу информацией между ЭВМ.

Остановимся подробно на работе блока 1 сопряжения (фиг. 2).

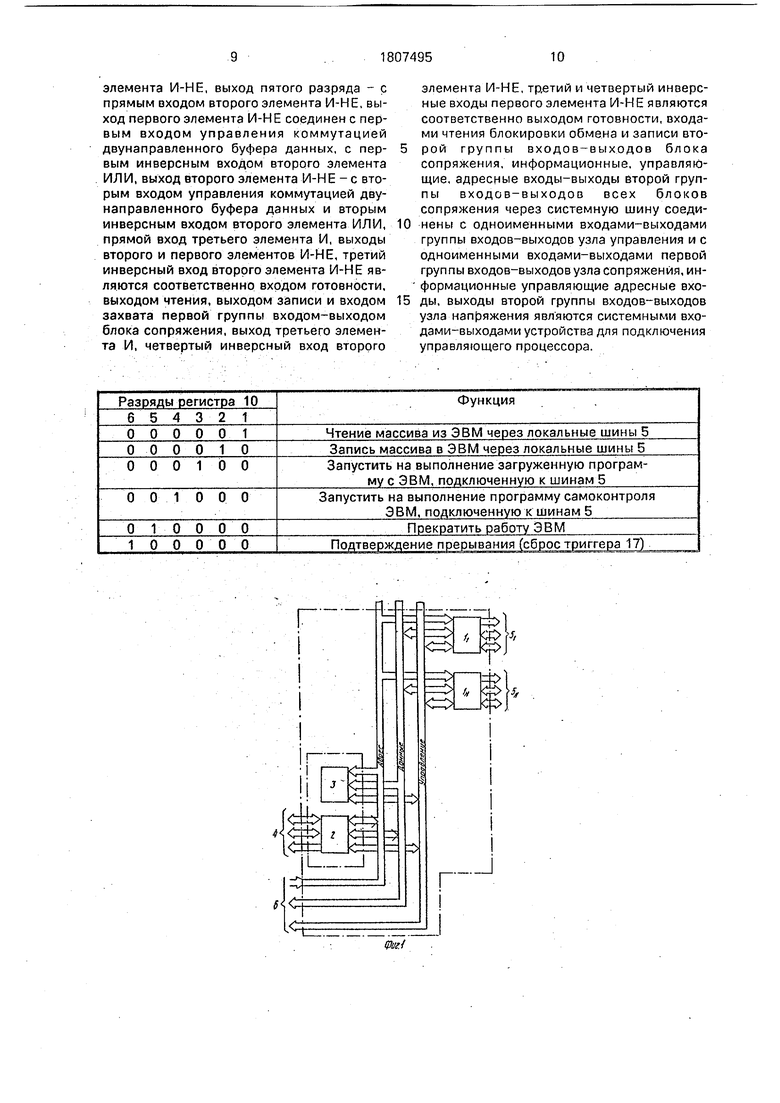

0 Настройка блока 1 производится от управляющей ЭВМ через системные шины 6 путем записи в регистр 10 требуемого кода согласно таблице. В этой таблице приведен один из воз- 5 можных вариантов управления системой.

Если выполняются функции обмена из памяти ЭВМ на выходе элемента ИЛИ 22 вырабатывается сигнал ЗАХВАТ, который поступает в.ЭВМ. После получения от ЭВМ 0 сигнала Подтверждение захвата (ПЗАХВ) из шины 5 элементы И 7, 8 и буферы 15, 20 подготовлены к работе.

Кроме загрузки регистра 10, перед началом обмена управляющая ЭВМ загружает в 5 счетчик 13 начальный адрес памяти.

Обмен начинается, с выдачи сигнала БОБ (быстрый обмен). В этом случае элемент 1/1 16 выдает сигнал разрешения в буфер 20, который подключает адрес с выхода Счетчика 13 к магистрали адреса локальной

шины 5, и в буфер 15, который соединяет магистраль данных системной 6 и локальной шин 5. Если будет выполняться запись информации, то системный сигнал Запись .ЗУ (ЗП ЗУ) через элемент И 9 будет прохо- дить на локальную линию ЗП ЗУ и в то же время будет ориентировать буфер 15 в на- правлении системная магистраль данных - локальная магистраль данных. Если будет выполняться чтение с шины 5, то уже сие- темный сигнал ЧТ ЗУ будет передаваться на локальную линию ЧТ ЗУ через элемент 8. В обеих этих операциях локальная линия ГОТОВ будет подключена через вентиль 7 к системной линии ГОТОВ для анализа в уп- равляющей ЭВМ.

По заднему фронту каждого импульса ЧТ ЗУ или ЗП ЗУ вырабатывается сигнал на входе -1 счетчика 13, и каждое следующее обращение к памяти производится по слё- дующему по порядку адресу. (Здесь учиты- вается, что шина адреса инверсная). Это обеспечивается элементом ИЛИ 18 и элементом И 19.

Триггер 17 и дешифратор адреса 21 обеспечивает возможность локальной ЭВМ сообщить управляющей ЭВМ через выходы шины 6с помощью сигналов ЗАПРЕТ о завершении текущего задания.

Рассмотрим подробно работу узла 4 со- пряжения (фиг. 3).

Она во многом аналогична описанной выше работе блока 1 сопряжения.

Настройка блока 4 сопряжения производится управляющей ЭВМ путем записи в регистр 27 требуемого кода:

-....

При этом схема ИЛИ 33 вырабатывает разрешающий потенциал на схему И 24. Кроме того, в счетчик 29 должен быть загружен начальный адрес массива данных, кото- рый считывается из памяти или записывается в нее. Во время быстрого обмена, управляемого узлом 3, вырабатывается потенциал БОБ, с помощью которого схемой И 24 вырабатывается разрешение для прохождения сигналов ЧТ ЗУ через схе- му И 25 или ЗП ЗУ через схему И 26 соответственно при чтении или записи информации. Кроме того, выход схемы И 24 разрешает работу буфера данных 32 и буфера адреса 36.

5 0 5

0

5

0

5

0

5

0 5

После чтения или записи очередного байта информации из содержимого счетчика 29 вычитается единица (схемы 34 и 35). Формула изобретения Устройство для сопряжения процессоров, содержащее группу из блоков сопряжения, каждый из которых содержит два элемента И, два элемента ИЛИ, элемент ИЛИ-НЕ, регистр, три дешифратора адреса, двунаправленный и однонаправленный буферы данных, счетчик, триггер, причем информационные, управляющие, адресные входы-выходы первой группы входов-выходов 1-го (1 1, .... N) блока сопряжения являются одноименными входами-выходами устройства, информационные, управляющие, адресные входы-выходы второй группы входов-выходов i-ro блока сопряжения через одноименную системную шину соединены с одноименными входами-выходами второй группы входов-выходов (i + 1)-го блока сопряжения, в каждом блоке сопряжения выход элемента ИЛИ-НЕ соединен с первым инверсным входом первого элемента И, входом первого элемента ИЛИ, выходы первого и второго разрядов регистра соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, выход первого дешифратора адреса соединен с входом режима регистра, выход второго дешифратора адреса - с одноименным входом режима счетчика, информационные выходы которого соединены с одноименным входом одно- .направленного буфера данных, выход третьего разряда регистра сосДинен с входом сброса триггера, информационный вход которого соединен с выходом третьего дешифратора адреса, выход перзого элемента И соединен с входом разрешения однонаправленного буфера данных, с первым входом второго элемента И и с входом разрешения двунаправленного буфера данных, выход второго элемента ИЛИ соединен с вторым входом второго элемента И, выход которого соединен со счетным входом счетчика, выход первого элемента ИЛИ, выходы четвертого, пятого и шестого разрядов регистра, выходы однонаправленного буфера данных являются соответственно выходом захвата, первым, вторым и третьим выходами запроса прерывания, выходом адреса первой группы входов-выходов блока сопряжения, вход записи внешнего устройства первой группы входов-выходов блока сопряжения соединен с синхронизирующим входом триггера, адресные вход первой группы входов блока сопряжения соединен с входом третьего дешифратора адреса, первые информационные входы- выходы двунаправленного буфера данных

соединены с информационными входами- выходами первой группы входов-выходов блока сопряжения, адресные входы второй группы входов-выходов блока сопряжения соединены с входами первого и второго дешифраторов адреса, системные двунаправленные информационные входы-выходы второй группы входов-выходов блока напряжения соединены с вторыми входами- выходами двунаправленного буфера данных, с информационными входами регистра, с информационными входами счетчика, выход триггера является выходом запроса второй группы входов блока сопряжения, вход записи внешнего устройства второй группы входов-выходов блока сопряжения соединен с входами синхронизации регистра и счетчика, отличающее- с я тем, что, с целью расширения области применения за счет обеспечения параллельной передачи однотипной информации одновременно в несколько ЭВМ, в него введены узел управления композицией и узел сопряжения, а в каждый блек сопряжения - третий элемент И и два элемента И-НЕ; узел управления коммутацией содержит два постоянных запоминающих блока, регистр, дешифратор адреса, счетчик; узел сопряжения содержит три элемента И,; четыре элемента И-НЕ, двунаправленный буфер данных, регистр, два элемента ИЛИ, дешифратор адреса, счетчик, однонаправленный буфер данных: в узле управления выход первого постоянного запоминающего блока со- единен с информационным входом регистра, выход которого соединен с адресными входами первого и второго постоянных запоминающих блоков, первый выход дешифратора адреса узла управления соединен с входом первого разряда адреса управления, первого постоянного запоминающего блока, выходы дешифратора адреса соединены с первым информационным входом счетчика, первый выход второго постоянного запоминающего блока соединен со счетным входом счетчика, выход переполнения которого соединен с входом второго разряда адреса первого постоянного блока, входы третьего, четвертого и пятого разрядов адреса первого постоянного запоминающего блока, вход режима регистра, информационный вход дешифратора, второй информационный вход счетчика, второй-пятый выходы второго постоянного запоминающего устройства являются соответственно входами записи высшего устройства, захвата, готовности, запроса адреса, данных, выходами записи, чтения блокировки обмена и захвата группы входов-выходов узла управления, в узле сопряжения выход первого элемента И соединен с первыми входами второго элемента И, первого и второго элементов И-НЕ, третьего элемента И, с управляющим входом однонаправленного буфера данных, с первым управляющим входом двунаправленного буфера данных, первый выход регистра соединен с вторым входом первого элемента И-НЕ, с первым входом первого элемента

0 ИЛИ, второй выход регистра - с вторыми входами второго элемента И-НЕ и первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выход первого элемента И-НЕ соединен с выходом

5 третьего элемента И-НЕ, с первым входом управления коммутацией двунаправленного буфера данных, с первым инверсным входом элемента ИЛИ, выход второго элемента .. И-НЕ - с выходом четвертого элемента И0 НЕ, с вторым входом управления коммутацией двунаправленного буфера данных, с первым инверсным входом элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И, выход которого соеди5 нен со счетным входом счетчика, второй вход первого элемента И соединен с первыми входами третьего и четвертого элементов И-НЕ, третий вход первого элемента И-НЕ - с вторым входом третьего элемента.

0 И-НЕ, третий вход второго элемента И-НЕ - с третьим входом третьего и вторым входом четвертого элементов И-НЕ, выход дешифратора адреса соединен с входом режима регистра, группа выходов дешифратора ад5 реса - с первой группой информационных входов счетчика, второй вход второго элемента И, выходы первого и второго элементов И-НЕ,первый информационный вход-выход двунаправленного буфера дан-.

0 ных, выход однонаправленного буфера данных является соответственно входом готовности, выходом чтения, выходом записи, входом-выходом данных, выходом адреса первой группы входов-выходов узла

5 сопряжения, выход второго элемента И, инверсные входы первого, и четвертого элементов И, второй информационный вход-выход двунаправленного буфера, вход режима регистра и вход дешифратора адре0 са являются соответственно выходом готовности, входом блокировки обмена, входом чтения, входом.записи, входом-выходом данных, входом записи внешнего устройства и входом адреса второй группы входов5 выходов узла сопряжения блока сопряжения, выход элемента ИЛИ-НЕ соединен с первыми инверсными входами третьего элемента И и первого и второго элементов И-НЕ, выход шестого разряда регистра соединен с прямым входом первого

элемента И-НЕ, выход пятого разряда - с прямым входом второго элемента И-НЕ, выход первого элемента И-НЕ соединен с первым входом управления коммутацией двунаправленного буфера данных, с первым инверсным входом второго элемента ИЛИ, выход второго элемента И-НЕ - с вторым входом управления коммутацией двунаправленного буфера данных и вторым инверсным входом второго элемента ИЛИ, прямой вход третьего элемента И, выходы второго и первого элементов И-НЕ, третий инверсный вход второго элемента И-НЕ являются соответственно входом готовности, выходом чтения, выходом записи и входом захвата первой группы входом-выходом блока сопряжения, выход третьего элемента И, четвертый инверсный вход второго

элемента И-НЕ, тр,етий и четвертый инверсные входы первого элемента И-НЕ являются соответственно выходом готовности, входами чтения блокировки обмена и записи второй группы входов-выходов блока сопряжения, информационные, управляющие, адресные входы-выходы второй группы входов-выходов всех блоков сопряжения через системную шину соеди0 нены с одноименными входами-выходами

группы входов-выходов узла управления и с

одноименными входами-выходами первой

группы входов-выходов узла сопряжения, ин формационные управляющие адресные вхо5 ды, выходы второй группы входов-выходов узла напряжения являются системными входами-выходами устройства для подключения управляющего процессора.

п.

С

Ј8

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ УСТРОЙСТВАМИ | 1991 |

|

RU2024052C1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ ОБЪЕКТАМИ | 1993 |

|

RU2018944C1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения ЭВМ в вычислительной системе с децентрализованным арбитром магистрали | 1984 |

|

SU1291997A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многомашинных комплексов и мультипроцессорных систем. Цель изобретения - расширение функциональных возможностей за счет параллельной передачи информации одновременно в несколько процессоров. Поставленная цель достигается тем, что устройство содержит с первого по N-й блоки коммутации, где N - число коммутируемых процессоров системы, (N + +1)-й блок коммутации, блок управления. 4 ил., 1 табл.

МЯ

д

чд

m

sa

с

Ст

-У

J6

ю

мд

it

eoS

углу

замv -

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство для сопряжения ЭВМ | 1987 |

|

SU1418729A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-04-07—Публикация

1990-05-24—Подача