Изобретение относится к вычислительной технике и может быть использовано при построении двухтактных синхронных схем (регистровых схем типа М-S) преимущественно для схемотехники КМОП БИС.

Цель изобретения - повышение быстродействия и функциональной устойчивости при разветвлении тактовых сигналов.

Ограниченные значения коэффициентов разветвления по выходу для логических элементов и для усилителей-формирователей, как правило, не позволяют построить двухтактные синхронные (регистровые) схемы требуемой разрядности без разветвления синхросигналов с помощью формирователей. Включение специального элемента задержки несколько повышает функциональную устойчивость при снижении быстродействия (тактовой частоты). Известные технические решения устраняют влияние существенных состязаний, но при этом также снижается быстродействие.

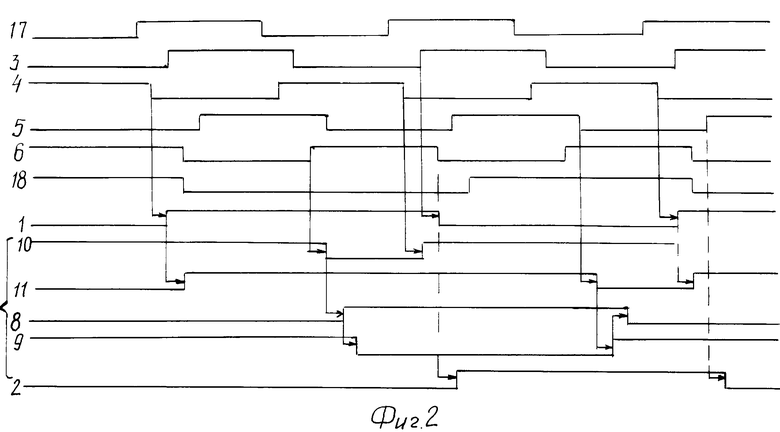

На фиг. 1 приведен предлагаемый регистр сдвига; на фиг.2 представлены временные диаграммы, поясняющие его работу.

Регистр сдвига содержит двухступенчатый 1 и одноступенчатый 2 триггеры и четыре тактовые шины 3, 4, 5 и 6, причем первая 4 и вторая 3 тактовые шины соединены соответственно с первым и вторым синхровходами двухступенчатого триггера 1, третья 6 и четвертая 5 тактовые шины соединены соответственно с первым и вторым синхровходами одноступенчатого триггера 2. Информационный вход двухступенчатого триггера 1 является информационным входом регистра. В регистр сдвига введены RS-триггер 7, выполненный на двух элементах И-НЕ 8 и 9, элемент И-НЕ 10 и элемент ИЛИ 11, причем выход двухступенчатого триггера 1 соединен с первыми входами элементов И-НЕ 10 и ИЛИ 11, выходы которых соединены соответственно с S- и R-входами RS-триггера 7, выход RS-триггера 7 соединен с информационным входом одноступенчатого триггера 2. Второй и третий входы элемента И-НЕ 10 соединены соответственно с первыми синхровходами двухступенчатого 1 и одноступенчатого 2 триггеров, а второй и третий входы элемента ИЛИ 11 соединены соответственно с вторыми синхровходами двухступенчатого 1 и одноступенчатого 2 триггеров.

На фиг.1 показаны включение формирователей (усилителей) 12, 13, 14, 15 и 16 сигналов тактовых шин, общего тактового входа 17, а также подключение информационного входа 18 регистра к информационному входу двухступенчатого триггера 1.

Временные диаграммы (фиг.2) поясняют работу регистра сдвига (фиг.1) для информации 1010... на информационном входе 18 регистра при условии, что формирователи 14 и 15 имеют меньшую задержку, чем формирователи 12 и 13. Порядок переключения элементов показан стрелками. В исходном состоянии (фиг. 2) триггеры 1, 2 и 7 находятся в состоянии логического "0". Первый срез импульса на первой тактовой шине 4 вызывает переключение в логическую "1" сигнала на первом выходе триггера 1 и затем элемента ИЛИ 11 в логическую "1". Первый фронт импульса на третьей тактовой шине 6 вызывает переключение элемента И-НЕ 10 в логический "0" и затем переключение в логическую "1" RS-триггера 7 (элемента И-НЕ 8 в логическую "1" и элемента И-НЕ 9 в логический "0"). После среза второго импульса на первой тактовой шине 4 элемент И-НЕ 10 переключается в логический "0". Фронт второго импульса на второй тактовой шине 3 вызывает переключение в логический "0" сигнала на первом выходе триггера 1. Второй срез импульса на третьей тактовой шине 6 вызывает переключение в логическую "1" сигнала на первом выходе триггера 2. После появления среза второго импульса на четвертой тактовой шине 5 переключаются последовательно элемент ИЛИ 11 в логической "0" и RS-триггер 7 в логический "0" (элемент И-НЕ 9 в логическую "1" и элемент И-НЕ в логический "0"). Третий срез импульса на тактовой шине 4 вызывает переключение в логическую "1" сигнала на первом выходе триггера 1 и затем элемента ИЛИ 11 в логическую "1". Фронт третьего импульса на четвертой тактовой шине 5 вызывает переключение в логический "0" сигнала на первом выходе триггера 2.

Таким образом, предложенный регистр сдвига работает функционально устойчиво (без "проскоков" информации вперед) при разбросах фаз импульсов на тактовых шинах (разбросах задержек формирователей тактовых сигналов), а минимальный период следования тактовых импульсов для предложенного регистра меньше, чем у прототипа, на величину задержки элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный счетчик | 1985 |

|

SU1257838A1 |

| Сдвигающее устройство | 1989 |

|

SU1686480A1 |

| Регистр сдвига | 1977 |

|

SU705522A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ ПО ДАННЫМ И ФАЗОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2711752C2 |

| Счетчик-сдвигающий регистр | 1987 |

|

SU1517128A1 |

| Синхронный счетчик | 1987 |

|

SU1451851A1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2661328C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2665241C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении двухтактных синхронных схем преимущественно для схемотехники КМОП БИС. Регистр сдвига содержит двухступенчатый 1 и одноступенчатый 2 триггеры и четыре тактовые шины 3,4,5 и 6, RS-триггер 7, выполненный на двух элементах И - НЕ 8, 9. Элемент И - НЕ 10, элемент ИЛИ 11. Регистр сдвига работает функционально устойчиво при разбросах фаз импульсов на тактовых шинах. 2 ил.

РЕГИСТР СДВИГА, содержащий двухступенчатый и одноступенчатый триггеры и четыре тактовые шины, причем первая и вторая тактовые шины соединены соответственно с первым и вторым синхровходами двухступенчатого триггера, третья и четвертая тактовые шины соединены соответственно с первым и вторым синхровходами одноступенчатого триггера, информационный вход двухступенчатого триггера является информационным входом регистра, а выход одноступенчатого триггера - выходом регистра, отличающийся тем, что в него введены RS-триггер, выполненный на двух элементах И-НЕ, элемент И-НЕ, элемент ИЛИ, причем выход двухступенчатого триггера соединен с первыми входами элементов И-НЕ и ИЛИ, выходы которых соединены соответственно с S- и R-входами RS-триггера, выход RS-триггера соединен с информационным входом одноступенчатого триггера, второй и третий входы элемента И-НЕ соединены соответственно с первыми синхровходами двухступенчатого и одноступенчатого триггеров, а второй и третий входы элемента ИЛИ соединены соответственно с вторыми синхровходами двухступенчатого и одноступенчатого триггеров.

| Будинский Я | |||

| Логические цепи в цифровой технике | |||

| Пер | |||

| с чешс | |||

| М.: Связь, 1977, с.230, 392, рис.6.73. |

Авторы

Даты

1994-11-30—Публикация

1990-12-25—Подача