Изобретение относится к радиотехнике.

При отсутствии прямой передачи тактов при приеме дискретных сигналов для корректного стробирования данных и синхронизации по времени необходимо подстраивать тактовую частоту по данным при определенном фазовом сдвиге.

Известен способ подстройки частоты [1] по переключениям данных. Переключения данных происходят в два раза чаще, чем фронты. Способ [1] имеет большой фазовый шум и низкое быстродействие. В единую временную сетку не попадают фазы фронтов и срезов, а также сигналы дополнительных каналов, имеющих разные задержки, что увеличивает фазовый шум и снижает устойчивость петли.

Известны быстродействующие способы подстройки тактовой частоты по фронтам (или срезам) данных [2, 3].

Способ подстройки тактовой частоты по фронтам данных [2], в котором сигналы первом и втором выходах детектора управляют подключением первого и второго двухполярных сигналов для суммирования, двухполярные сигналы суммируют, фильтруют, полученным сигналом управляют частотой генератора, частоту генератора делят и формируют такты, причем на первом выходе детектора формируют сигнал от фронта данных до следующего за ним переключения тактов, если фронт данных поступит позже центра зоны удержания, то после окончания сигнала на первом выходе детектора формируют сигнал на втором выходе детектора сигнал от фронта тактов до среза тактов.

При подстройке частоты по переменной частоте сравнения (по перепадам данных) способы [1. 2. 3] имеют меньшую устойчивость, чем в режиме работы на средней «постоянной» частоте сравнения. Время ожидания переключений данных Т:

где Тс - период тактов (Тс=1/Fc), Fc - тактовая (символьная) частота; m=2, 3,…

Переменное время ожидание переключения данных влияет на коэффициент усиления и полосу петли. Петля, устойчивая на средней частоте следования фронтов, может некорректно работать на больших интервалах между фронтами данных Т≥mкр×Тс, где mкр - критическое значение m, начиная с которого могут, возможна потеря устойчивости и выход из режима удержания. Максимальные значения число периодов ожидания переключений (фронтов) данных и mкр для способов [1. 2. 3] одинаковы.

Наиболее близкими к предлагаемым являются способ и фазовый детектор [2] (прототипы).

Известен фазовый детектор [2], содержащий детектор и формирователь двухполярных сигналов, причем входы детектора соединены попарно соответственно со входами опорной частоты и входом тактов.

Цель изобретения (технический результат) - повышение устойчивости в режиме удержания при сохранении быстродействия. Технический результат достигается тем, что:

- считают число фронтов тактов, прошедших после поступления предшествующего фронта данных, а в области регулирования при увеличении числа подсчитанных фронтов тактов амплитуды двухполярных слагаемых снижают;

- устанавливается фиксированное отношение амплитуды первого двухполярного сигнала к амплитуде второго двухполярного сигнала, это отношение сохраняется при изменении амплитуд двухполярных сигналов, после окончания сигнала на первом выходе детектора всегда формируют сигнал на втором выходе детектора от фронта до среза тактов;

- фиксированное отношение амплитуд первого и второго двухполярных сигналов равное двум;

- фазовый детектор дополнительно содержит три D-триггера, два элемента И, элемент ИЛИ, счетчик, преобразователь кода и цифро-аналоговый преобразователь, причем тактовый вход соединен с С-входами трех D-триггеров и счетчика, вход опорной частоты соединен с D-входом первого триггера и первым входом первого элемента И, выход первого элемента И соединен со входом сброса счетчика и первым входом элемента ИЛИ, выход первого D-триггера соединен с D-входом второго D-триггера, выход которого соединен с первым входом второго элемента И и с D-входом третьего D-триггера, инверсный выход которого соединен с другими входами первого и второго элементов И, выход переноса счетчика соединен с другим входом элемента ИЛИ, выход которого соединен с СЕ входом счетчика, выходы которого соединены попарно соответственно со входами преобразователя кода, выходы которого соединены попарно соответственно со входами цифро-аналогового преобразователя, выход которого соединен с управляющим входом формирователя двухполярных сигналов;

- причем С - вход второго D-триггера - прямой, а С-входы первого и третьего D-триггеров и счетчика - инверсные.

Группа изобретений связана общим замыслом и удовлетворяет требованию единства изобретения, т.к. фазовый детектор является частью устройства для осуществления предложенного способа. При анализе уровня техники и новизны заявляемых объектов не обнаружены аналоги с перечисленной совокупностью вышеназванных признаков. Следовательно, описанное техническое решение соответствует критерию "новизна".

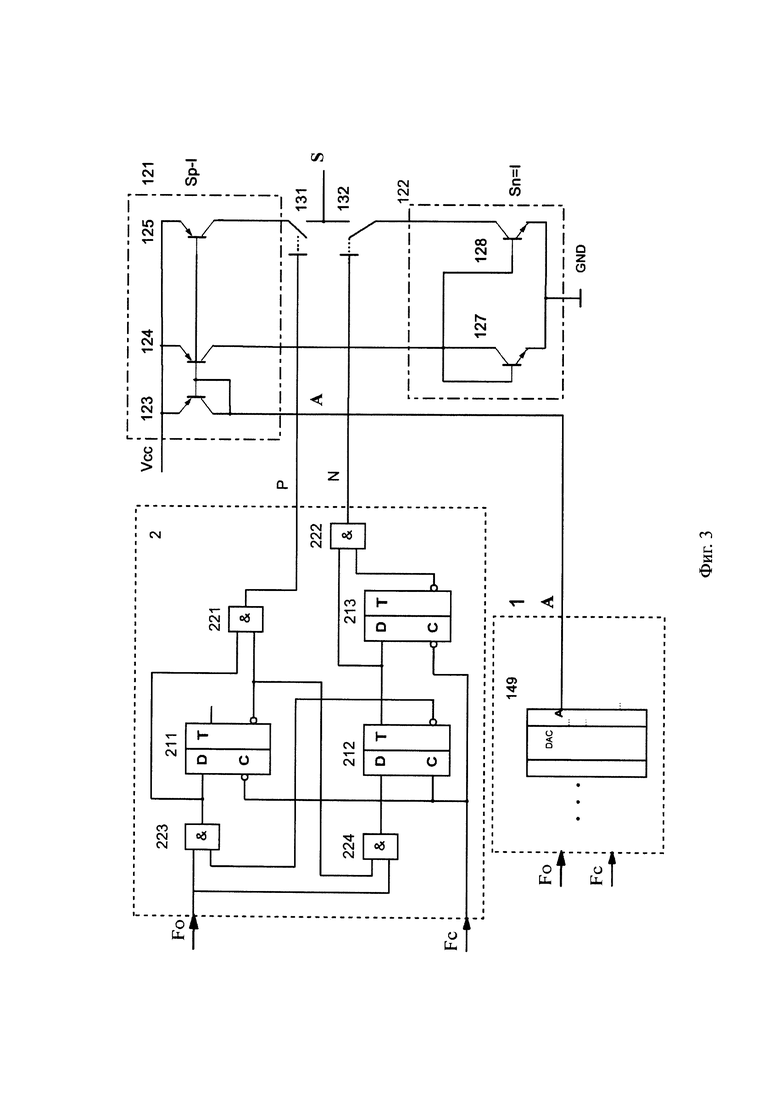

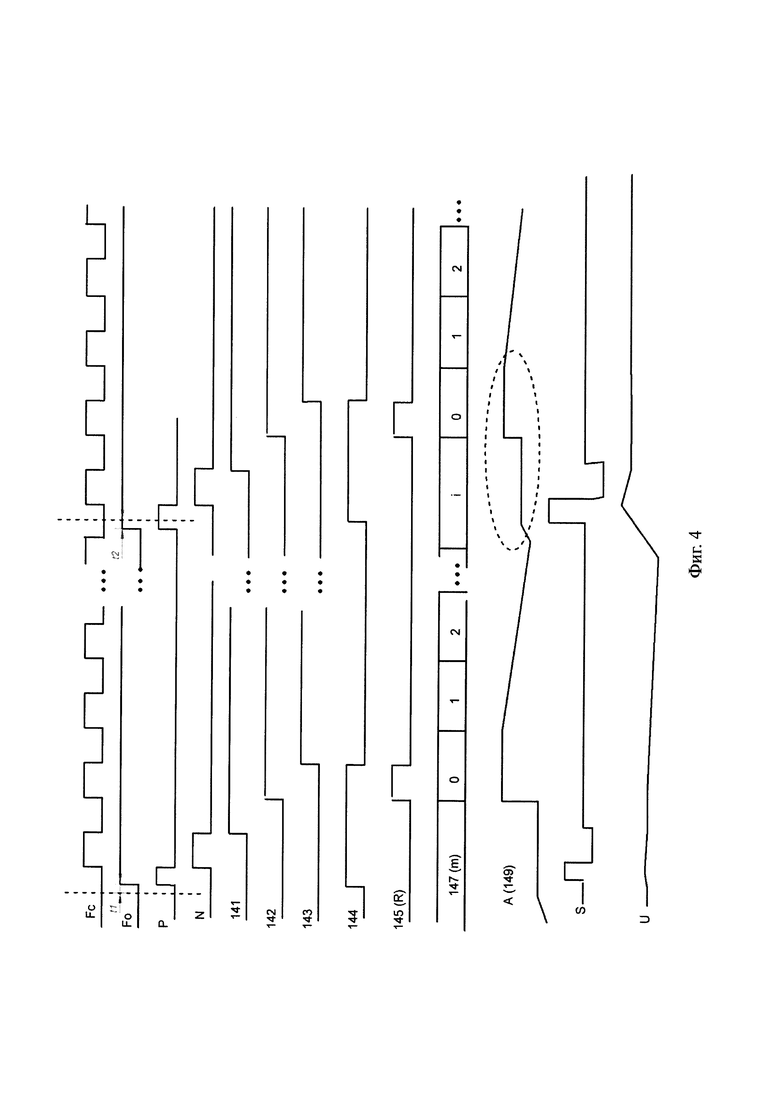

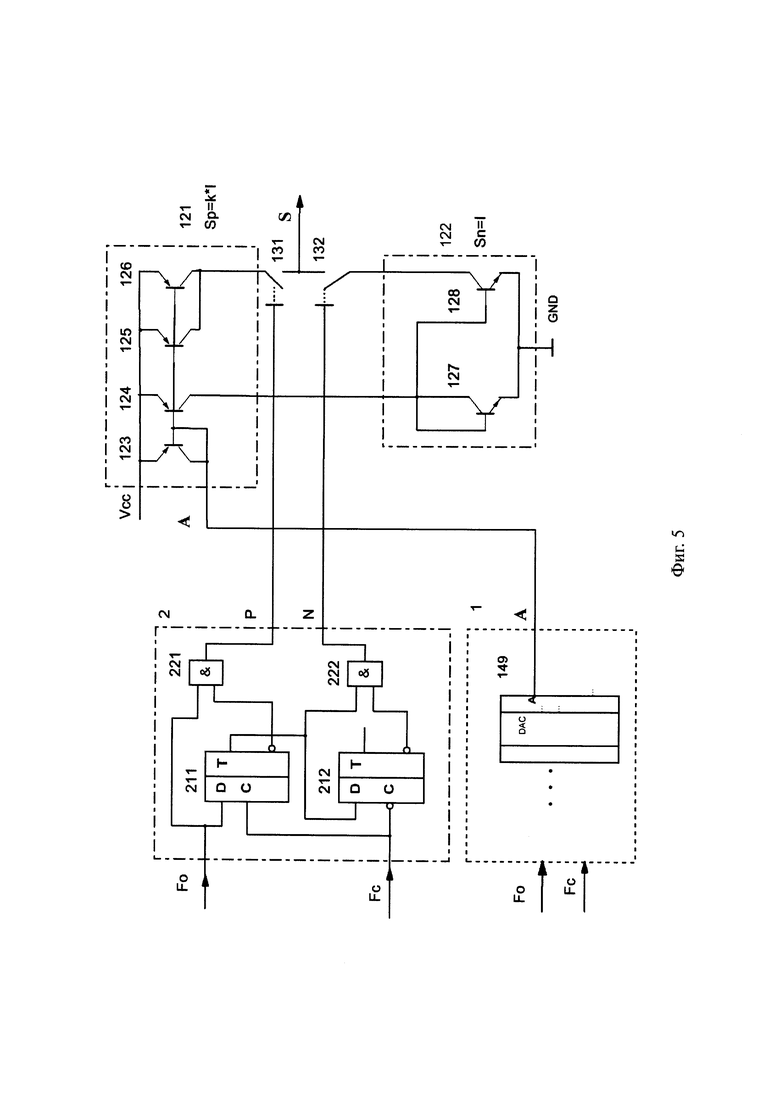

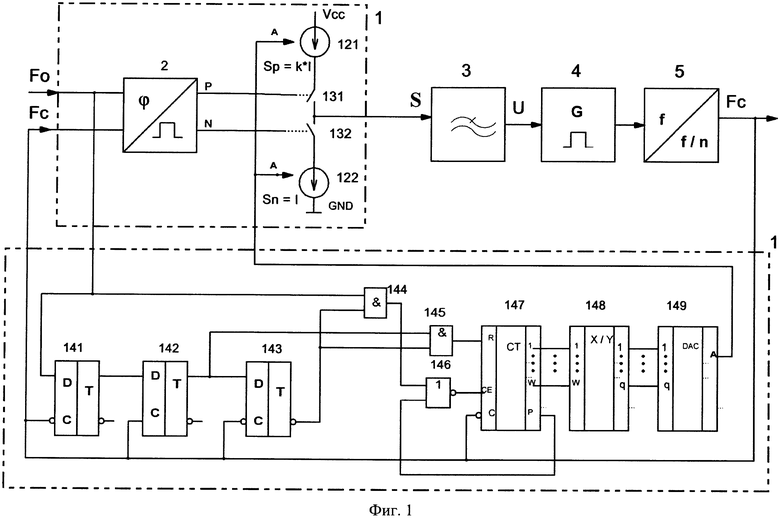

На фиг. 1. представлен способ подстройки частоты и фазовый детектор. Временная диаграмма работы с центром зоны удержания по срезу тактов приведена на фиг. 2, а соответствующий детектор и пример управления амплитудой двухполярных сигналов - на фиг. 3. Временная диаграмма работы с центром зоны удержания, смещенным относительно среза тактов, приведена на фиг. 4, соответствующий детектор и пример управления амплитудой двухполярных сигналов и - на фиг. 5. На временных диаграммах фиг. 2 и 4 также приведены сигналы на выходах элементов фазового детектора. Примеры управления амплитудами двухполярных сигналов (фиг. 3 и 5), реализованы на «токовых зеркалах» для n-p-n и p-n-р биполярных транзисторах. Функционально аналогичные токовые схемы на КМОП транзисторах требуют большего числа элементов для обеспечения низкого остаточного напряжения и смещения затворных токов.

Способ подстройки тактовой частоты Fc по фронтам данных Fo (фиг. 1 и 2), в котором сигналы на первом Р и втором N выходах детектора 2 управляют подключением двухполярных сигналов Sp и Sn (источники 121, 122 и ключи 131, 132) для суммирования, суммируют S, фильтруют 3, полученным сигналом U управляют частотой генератора 4, частоту генератора делят и формируют такты Fc, причем на первом выходе Р детектора 2 формируют сигнал от фронта данных Fo до следующего за ним переключения тактов Fc, причем если фронт данных Fo поступит позже центра зоны удержания, то после окончания сигнала на первом выходе детектора формируют сигнал на втором выходе детектора сигнал от фронта тактов Fc до среза тактов Fc, при этом считают 147 число фронтов тактов Fc прошедших после поступления предшествующего фронта данных Fo, при увеличении числа подсчитанных фронтов тактов 147 амплитуды двухполярных сигналов снижают А (149).

В быстродействующей фазовой автоподстройки частоты (ФАПЧ) в режиме удержания должна происходить отработка частотной ошибки Δω, где {Δω=2π×(Fc-Fo)}, причем с некоторой перерегулировкой за несколько периодов опорной частоты (перепадов данных).

Пусть в режиме удержания при поступлении фронта данных в момент времени tj, где j=1, 2…, детектор 2 обнаруживает сдвиг Δtj и фазовую ошибку Δϕj. Частота ГУН 4 Fc изменяется в соответствии с переходной характеристикой фильтра низких частот (ФНЧ) 3. При поступлении (j+1)-го фронта данных при t(j+i)=tj+m(j+1)×TC фазовая ошибка Δϕ(j+1) составит исходную (Δϕj) за вычетом интеграла от изменения частоты ГУН 4 за время ожидания j+1-го фронта данных..

Для устойчивости ФАПЧ необходимо и достаточно, что бы на каждом шаге:

где α - коэффициент, 0<α<1.

С учетом необходимого запаса для приема данных с шумом и аппаратные потери лучше выбрать α: α≤0,5÷0,7

В последовательности двоичных данных фронту соответствует переход 0→1. В каналах передачи дискретных данных символы скремблированы и некоррелированные, поэтому вероятности появления двоичных 0 и 1 равны 1/2. Вероятность появления фронта в данном периоде тактов Рф=1/4. Средняя частота фронтов данных Fcp:

В последовательности двоичных данных переходу 0→1 через m бит соответствует время ожидания фронта (период следования фронтов) Т длительностью Т=m × Тс.

Вероятность реализации последовательности данных с периодом следования переходов m бит Pm определяется по формуле:

где (m-1) - число вариантов последовательностей данных с периодом переходов 0→1 m.

Ф(m) - вероятность появления фронта данных за m периодов тактов. Ф(m) с ростом m быстро приближается к 1, так, например, Ф(7)=0,94 и Ф(16)=0,995. Учитывая скорость передачи данных и длительную работу, необходимо обеспечить устойчивость петли, несмотря на низкую вероятность появления критических интервалов.

Снижение амплитуд слагаемых по предложению исключит опасную перерегулировку и выход из зоны удержания на критических интервалах. Низкая вероятность появления опасных времен ожидания перепадов данных позволит, снижая коэффициент усиления в петле только для критических интервалов, сохранить высокую скорость («широкую» полосу) ФАПЧ.

Полярность слагаемых S (Sp и Sn) предполагает повышение частоты генератора 4 при увеличении напряжения U. При опережении центра зоны удержания фронтом данных Fo частоту тактов Fc уменьшают, а при отставании фронта данных Fo от центра зоны удержания частоту тактов Fc увеличивают. Двухполярные сигналы могут быть получены при подключении источников 121 и 122 к однополярному питанию Vcc и общему проводу GND (фиг. 1, 3 и 5). На временных диаграммах фиг. 2 и 4 дополнительно показаны переключения триггеров 141, 142, 143 и первого элемента И 144 (R).

На временной диаграмме (фиг. 2) после m тактов, подсчитанных после предшествующего фронта данных Fo, при управляющем сигнале А (149), который соответствует т, раньше центра зоны удержания на время t1 поступает фронт данных Fo. По фронту данных Fo формируют первый сигнал детектора Р и для суммы S положительное слагаемое, амплитуда которого управляется сигналом А (149). В результате напряжение U несколько увеличивается. В процессе нового подсчета числа тактов до следующего фронта данных ступенчато уменьшается сигнал А (149). Следующий фронт данных приходит после i тактов (i=1, 2,…) и на время t2 позже центра зоны удержания. По фронту данных формируют сигналы на выходе детектора 2 Р и N, и соответственно слагаемые, амплитудой которых управляет сигнал А (149). В результате напряжение U несколько уменьшается. Отметим, что во время формирования суммы S, результат подсчета и управляющий сигнал А не изменяются.

Синхронное снижение амплитуд двухполярных сигналов в рабочей области может осуществляться, например, как функция от числа периодов тактов, которая обратно пропорциональна интегралу от переходной характеристики ФНЧ или ее аппроксимация.

На фиг. 3 приведен пример управления амплитудами двухполярных сигналов от токового втекающего сигнала А ЦАП 149. Источники 121, 122 выполнены на биполярных транзисторах р-n-р 123 - 125 и. n-р-n 127, 128. Для транзисторов с равными площадями эмиттеров и большими коэффициентами h21 (β) можно считать, что коллекторные токи равны (см. например, с. 75 рис. 4-2, 4-3 [4]). Амплитуды двухполярных сигналов равны и регулируются. Детектор 2 для центра зоны удержания по срезу тактов построен на D-триггерах 211, 212 и 213 и элементах И 221-224. Все D-триггера двухступенчатые. Функционирование аналогичного детектора 2 для центра зоны удержания по фронту тактов приведено в [2].

На временной диаграмме фиг. 4 показано, что после m тактов, подсчитанных от предшествующего фронта данных Fo, немного позже центра зоны удержания, (в паузе импульсов тактов) поступает фронт данных Fo (на фиг. 4 - время t1). Управляющий сигнал А (149) соответствует m. По фронту данных формируют сигналы детектора Р и N, и для суммы S два (двухполярных) слагаемых, амплитудами Sp и Sn (Sp=k×1 и Sn=I), которыми управляет сигнал А (149). В результате напряжение U несколько снижается. Следующий фронт данных Fo приходит через i тактов (i=1, 2,…) и на время t2 раньше центра зоны удержания. После фронта данных формируют сигналы детектора Р и N, и слагаемые суммы S (Sp и Sn), амплитудами которых управляет сигнал А (149). В результате напряжение U несколько увеличивается.

Пример управления амплитудами двухполярных источников 121, 122 от втекающего тока с выхода А ЦАП 149 (фиг. 5) Источники 121, 122 выполнены на биполярных транзисторах р-n-р 123 - 126 и n-р-n 127, 128. При равных площадях эмиттеров и большими коэффициентами h21 (β) можно считать, что коллекторные токи транзисторов равны. Амплитуда положительного сигнала равна удвоенной амплитуде отрицательного сигнала (k=2) и обе регулируются.

Детектор 2 построен на D-триггерах 211, 212 и элементах И 221, 222 для смещенного центра зоны удержания, относительно среза тактов, Работа детектора описана в [3].

Фазовый детектор 1 (фиг. 1), содержит детектор 2 и формирователь двухполярных сигналов причем первый Р и второй N выходы детектора 2 соединены со входами формирователя двухполярных сигналов (источники 121, 122 и ключи. 131, 132), а входы детектора 2 соединены попарно соответственно со входами опорной частоты Fo и тактов Fc, дополнительно содержит три D-триггера 141, 142 и 143, два элемента И 144 и 145, элемент ИЛИ 146, счетчик 147, преобразователь кода 148 и цифро-аналоговый преобразователь 149, тактовый вход Fc соединен с С-входами трех D-триггеров и счетчика 147, вход опорной частоты соединен Fo с D-входом первого триггера 141 и входом первого элемента И 144, выход первого элемента И 144 соединен со входом элемента ИЛИ 146, выход первого D-триггера 141 соединен с D-входом второго D-триггера 142, выход которого соединен со входом второго элемента И 145 и с D-входом третьего D-триггера 143, инверсный выход которого соединен с другими входами первого и второго элементов И 144 и 145, выход второго элемента И 145 соединен со входом сброса счетчика 147, выход переноса счетчика 147 соединен с другим входом элемента ИЛИ 146, выход которого соединен с СЕ входом счетчика 147, выходы которого соединены попарно соответственно со входами преобразователя кода 148, выходы которого соединены попарно соответственно со входами цифро-аналогового преобразователя 149, выход которого соединен с управляющим входом формирователя двухполярных сигналов.

С-входы первого 141, третьего 143 D-триггеров, и счетчика 147 -инверсные, а С-вход второго D-триггера 142 - прямой.

Счетчик 147 считает фронты тактов, а сигналы на его выходах переключается по срезу тактов. При переполнении счетчика 147 с помощью СЕ-входа осуществляется его остановка и исключается переход счетчика в «0» (до сброса по входу R). Преобразователь 148 может быть выполнен в виде постоянного запоминающего устройства (ПЗУ) или как логический (комбинационный) преобразователь.

Разрядность счетчика 147 должна быть не менее 6. Фазовый детектор (фиг. 1) может работать с разными детекторами и центрами зон удержания. При другой полярности (кодировании логических уровней) для С-входов счетчика и триггеров (включая детектор 2) центры зон удержания сдвигаются на π.

Таким образом, способ и фазовый детектор по предложению обладают устойчивостью при высоком быстродействии.

Источники информации

1. Патент US 6421404, кл. 375/354, 16.07.2002

2. Патент РФ 2622628, МПК H03D 13/00, 03.08.2016

3. Патент РФ 2665241, МПК H03D 13/00, 13.10.2017

4. Гребен А.Б. Проектирование аналоговых интегральных схем, пер. с англ. М., «Энергия» 1976

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2665241C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2016 |

|

RU2622628C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2661328C1 |

| Сдвигающее устройство | 1989 |

|

SU1686480A1 |

| СЧЕТЧИК | 1991 |

|

RU2028028C1 |

| Фазовый детектор | 1989 |

|

SU1737700A1 |

| Счетное устройство | 1983 |

|

SU1228268A1 |

| Реверсивный счетчик | 1982 |

|

SU1066039A2 |

| Счетчик в коде грея | 1984 |

|

SU1225011A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

Изобретение относится к способу подстройки тактовой частоты по фронтам данных и фазовому детектору. Технический результат заключается в повышении устойчивости в режиме удержания при сохранении быстродействия. Способ заключается в том, что сигналы на первом и втором выходах детектора управляют подключением первого и второго двухполярного сигналов для суммирования, двухполярные сигналы суммируют, фильтруют, полученным сигналом управляют частотой генератора, частоту генератора делят и формируют такты, причем на первом выходе детектора формируют сигнал от фронта данных до следующего за ним перепада тактов, причем если фронт данных поступит позже центра зоны удержания, то после окончания сигнала на первом выходе детектора формируют сигнал на втором выходе детектора от фронта тактов до среза тактов, при этом считают число фронтов тактов, прошедших после поступления предшествующего фронта данных, а в области регулирования при увеличении числа подсчитанных фронтов тактов амплитуды первого и второго двухполярных сигналов снижают. 2 н. и 3 з.п. ф-лы, 5 ил.

1. Способ подстройки тактовой частоты по фронтам данных, в котором сигналы на первом и втором выходах детектора управляют подключением первого и второго двухполярного сигналов для суммирования, двухполярные сигналы суммируют, фильтруют, полученным сигналом управляют частотой генератора, частоту генератора делят и формируют такты, причем на первом выходе детектора формируют сигнал от фронта данных до следующего за ним перепада тактов, причем если фронт данных поступит позже центра зоны удержания, фронт данных поступил позже центра зоны удержания, то после окончания сигнала на первом выходе детектора формируют сигнал на втором выходе детектора, сигнал от фронта тактов до среза тактов, отличающийся тем, что считают число фронтов тактов, прошедших после поступления предшествующего фронта данных, а в области регулирования при увеличении числа подсчитанных фронтов тактов амплитуды первого и второго двухполярных сигналов снижают.

2. Способ по п. 1, отличающийся тем, что устанавливается фиксированное отношение амплитуды первого двухполярного сигнала к амплитуде второго двухполярного сигнала, это отношение сохраняется при изменении амплитуд двухполярных сигналов, после окончания сигнала на первом выходе детектора на втором выходе детектора всегда формируют сигнал от фронта тактов до среза тактов.

3. Способ по п. 2, отличающийся тем, что отношение амплитуды первого двухполярного сигнала к амплитуде второго двухполярного сигнала равно двум.

4. Фазовый детектор, содержащий детектор и формирователь двухполярных сигналов, причем первый и второй выходы детектора соединены со входами формирователя двухполярных сигналов, а входы детектора соединены попарно соответственно со входом опорной частоты и входом тактов, отличающийся тем, что дополнительно содержит три D-триггера, два элемента И, элемент ИЛИ, счетчик, преобразователь кода и цифро-аналоговый преобразователь, причем тактовый вход соединен с С-входами, трех D-триггеров и счетчика, вход опорной частоты соединен с D-входом первого D-триггера и входом первого элемента И, выход первого элемента И соединен со входом элемента ИЛИ, выход первого D-триггера соединен с D-входом второго D-триггера, выход которого соединен с входом второго элемента И и с D-входом третьего D-триггера, инверсный выход которого соединен с другими входами первого и второго элементов И, выход второго элемента И соединен со входом сброса счетчика, выход переноса счетчика соединен с другим входом элемента ИЛИ, выход которого соединен с СЕ входом счетчика, выходы которого соединены попарно соответственно со входами преобразователя кода, выходы которого соединены попарно соответственно со входами цифро-аналогового преобразователя, выход которого соединен с управляющим входом формирователя двухполярных сигналов.

5. Фазовый детектор по п. 4, отличающийся тем, что С-входы счетчика, первого и третьего D-триггеров - инверсные, а С-вход второго D-триггера - прямой.

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2665241C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2661328C1 |

| СПОСОБ АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ ПОДСТРАИВАЕМОГО ГЕНЕРАТОРА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2047273C1 |

| US 8975924 B2, 10.03.2015 | |||

| US 6421401 B1, 16.07.2002. | |||

Авторы

Даты

2020-01-21—Публикация

2019-06-26—Подача