Изобретение относится к радиотехнике.

Известен способ подстройки частоты [1], в котором импульсы на первом и втором выходах фазового детектора преобразуют соответственно в разнополярные сигналы одной амплитуды, эти сигналы суммируют, фильтруют и управляют частотой генератора, частоту генератора делят и формируют такты, причем на первом и втором выходах фазового детектора формируют импульсы соответственно по фронту опорного сигнала или по фронту тактов, после появления последнего импульса формируют срезы импульсов на обоих выходах фазового детектора.

Известны работающие по способу [1] фазовые детекторы, содержащие два D-триггера и логические элементы И (см. например, [1, 2]). При любом фазовом сдвиге опорной частоты и тактов при сбросе D-триггеров в фазовом детекторе возникают опасные состязания, которые в «медленном» триггере могут привести к опасным для способа [1] эффектам: пропуску сброса, колебательной или метастабильной аномалиям [3].

Способ [1] имеет следующие недостатки:

- в режиме удержания работает только с сигналами равных частот и не может подстраивать такты по фронтам принятых данных;

- при любом фазовом сдвиге опорной частоты и тактов появляются опасные состязания.

Известен способ подстройки частоты [4], в котором импульсы на первом и втором выходах фазового детектора преобразуют соответственно в разно полярные сигналы одной амплитуды. Эти сигналы суммируют, фильтруют и управляют частотой генератора, частоту генератора делят и формируют такты, после появления фронта опорного сигнала формируют фронт импульса на первом выходе фазового детектора, ждут любого переключения тактов и формируют срез импульса на первом выходе фазового детектора. Импульс на втором выходе фазового детектора формируют при условии, когда фронт опорного сигнала появляется позже фронта тактов, при этом фронт импульса на втором выходе фазового детектора формируют по срезу тактов после фронта опорного сигнала, ждут появления фронта тактов и формируют срез импульса на втором выходе фазового детектора.

Этот способ может работать при кратных частотах и с переменной скважностью сигнала опорной частоты, что позволяет использовать его для подстройки тактовой частоты по фронтам данных при приеме дискретных сигналов.

Известен фазовый детектор [4], содержащий три D-триггера и четыре логических элемента И. В центре области удержания при небольших отставаниях фронта тактов от фронта сигнала опорной частоты, когда переключение сигнала на D-входе опережает фронт импульса на С-входе триггера на время, которое меньшее времени переключения триггера, но большее его половины, находится временной интервал, в котором возможен «арбитраж» в первом D-триггере. При «арбитраже» возможны пропуск переключения, увеличение времени переключения, колебательная аномалия или метастабильная аномалия [3]. Опасными для этого способа являются колебательная и метастабильная аномалии, которые с учетом вероятности приводят к увеличению фазового шума в режиме удержания.

Наиболее близкими к предлагаемым являются способ и фазовый детектор [4] (прототипы).

Цель изобретения (технический результат) - повышение функциональной устойчивости (устранение влияния опасных состязаний) в режиме удержания.

Технический результат достигается тем, что:

1) В способе подстройки частоты, в котором опорный сигнал поступает на первый вход фазового детектора в устройстве сравнения фаз, в котором сигналы на двух выходах фазового детектора с помощью двух ключей управляют подключением и отключением двух разнополярных источников постоянного тока для суммирования. Далее суммарный сигнал фильтруют и полученным сигналом управляют частотой генератора, частоту генератора делят и формируют такты, которые поступают на второй вход фазового детектора в устройстве сравнения фаз. Первый источник подключают по каждому фронту опорного сигнала. Подключенный первый источник отключают по первому фронту тактов, поступившему после фронта опорного сигнала, или по срезу опорного сигнала, если он поступит раньше первого фронта тактов после фронта опорного сигнала. Второй источник, подключают после фронта опорного сигнала по фронту тактов, если он поступит раньше среза опорного сигнала, подключенный второй источник отключают по первому срезу тактов.

2) Отношение сигнала второго источника к сигналу первого источника устанавливают равным (или меньшим) 1/2 отношения наименьшего из значений длительности импульса опорной частоты или периода тактов к длительности импульса тактов.

3) В фазовом детекторе, содержащий два D-триггера, два элемента И, дополнительно второй вход первого элемента И соединены с вторым выходом первого триггера. Тактовый вход соединен с инверсным С-входом второго триггера, вход опорной частоты соединен с D-входом первого триггера, первый выход первого триггера соединен с D-входом второго триггера,

4) Фазовый детектор содержит дополнительно два элемента ИЛИ-НЕ. Вход опорной частоты соединен с первыми входами элементов ИЛИ-НЕ, вторые входы первого и второго элементов ИЛИ-НЕ соединены попарно соответственно со вторым выходом второго триггера и первым выходом первого триггера. Выходы первого и второго элементов ИЛИ-НЕ соединены попарно соответственно с входами сброса первого и второго триггеров.

5) Фазовый детектор имеет дополнительно вход разрешения, который соединен с третьими входами первого и второго элементов ИЛИ-НЕ.

Группа изобретений связана общим замыслом и удовлетворяет требованию единства изобретения, т.к. фазовый детектор является частью устройства для осуществления предложенного способа. При анализе уровня техники и новизны заявляемых объектов не обнаружены аналоги с перечисленной совокупностью вышеназванных признаков. Следовательно, описанное техническое решение соответствует критерию "новизна".

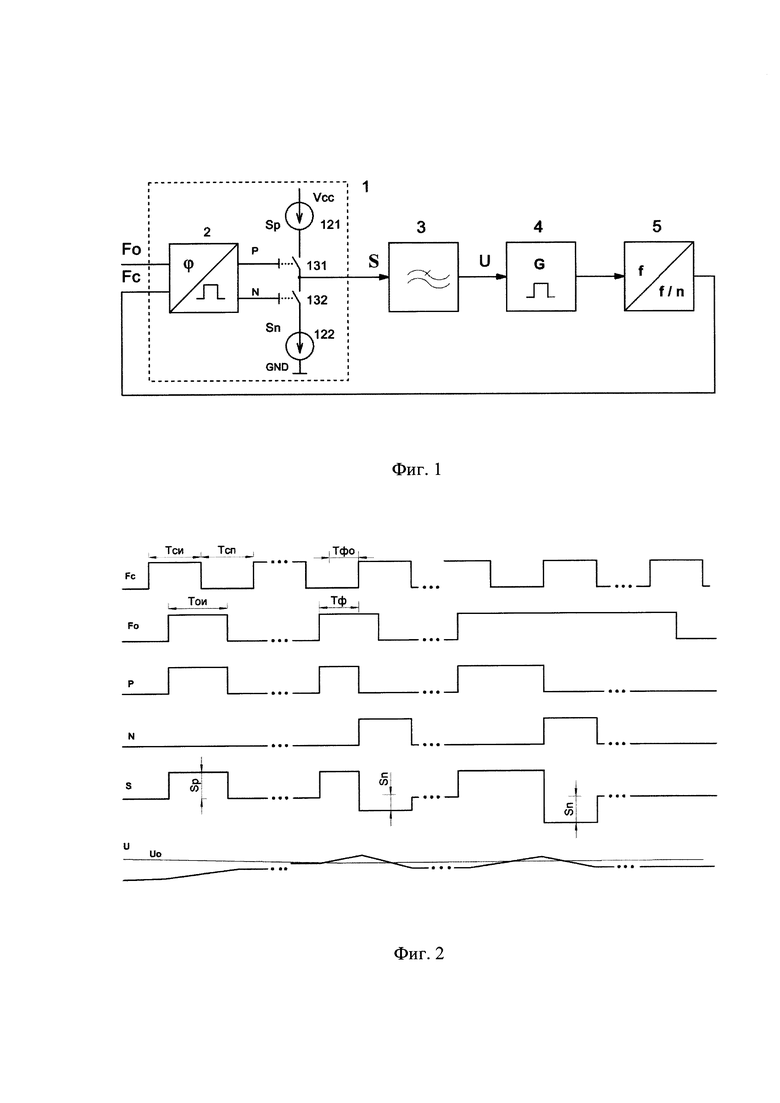

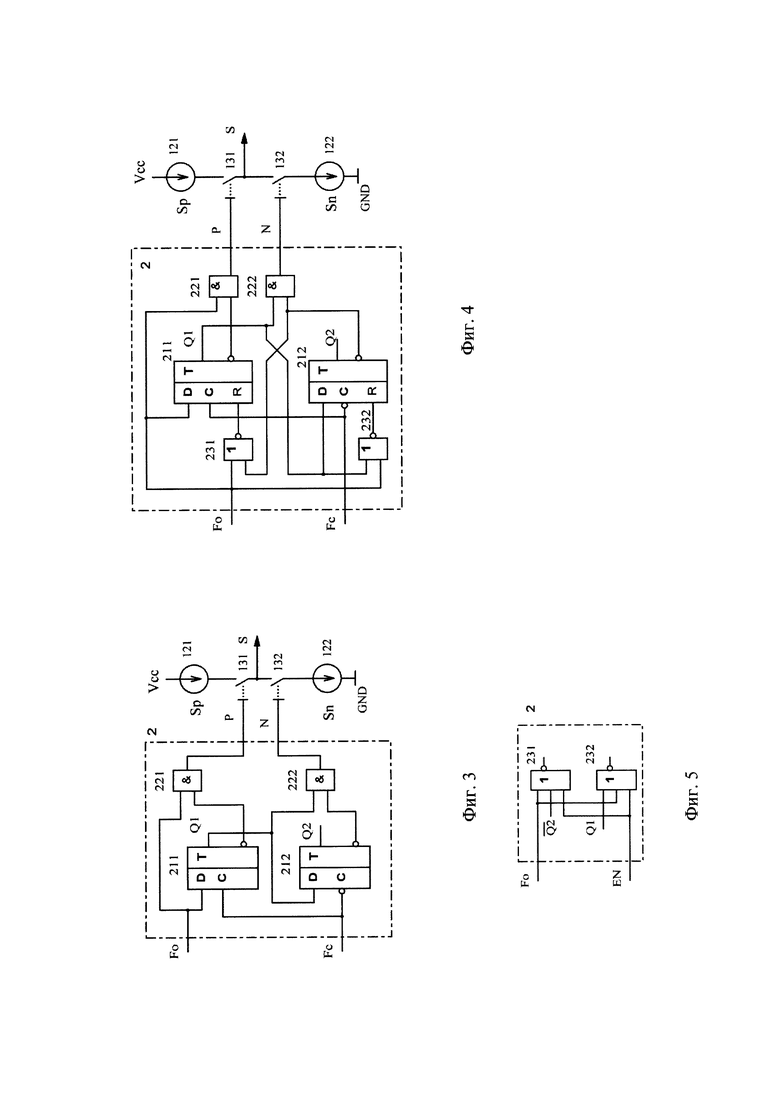

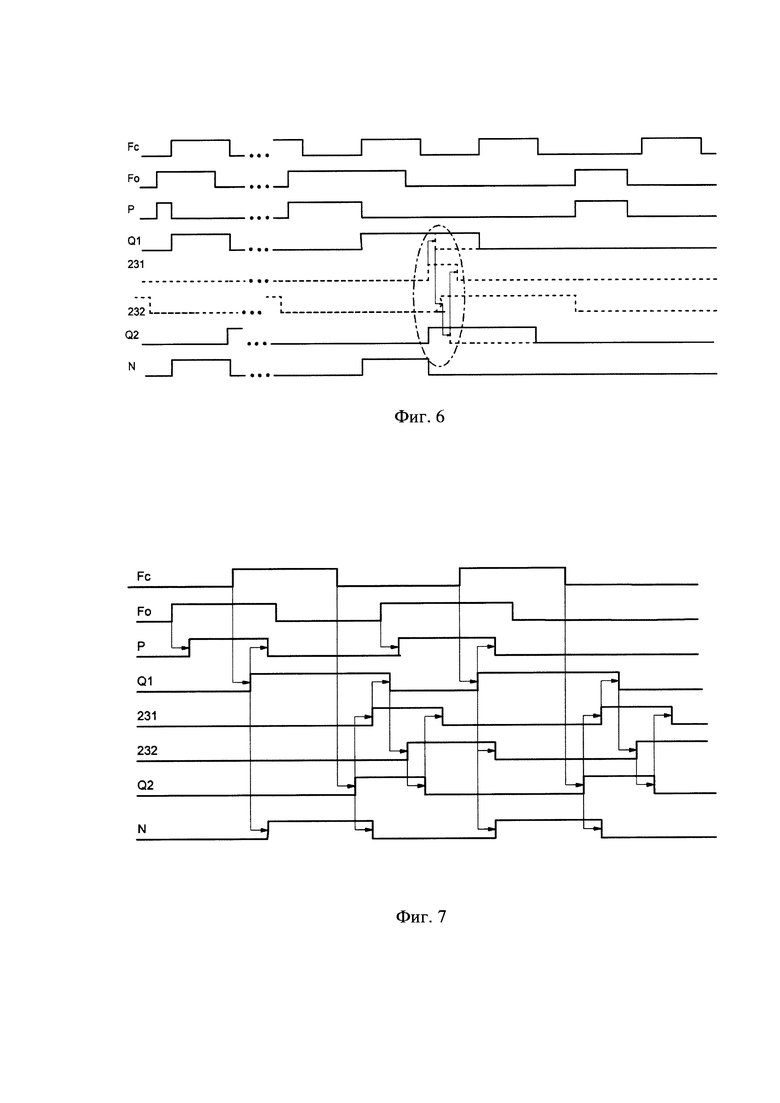

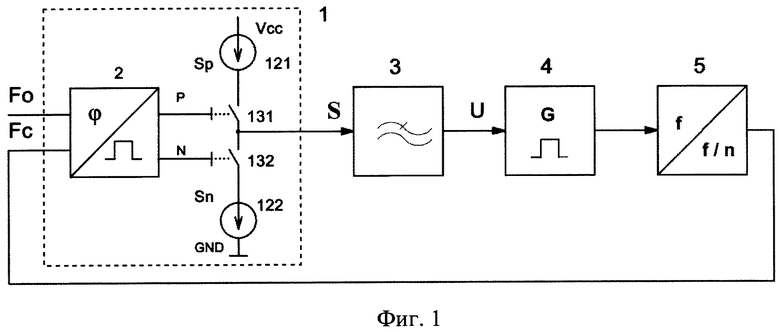

Способ подстройки частоты представлен на фиг. 1 и 2. На фиг. 3, 4 и 5, приведены схемы фазовых детекторов, а на фиг. 6 и 7 - временные диаграммы их работы.

Опорный сигнал Fo (фиг. 1 и 2) поступает на первый вход фазового детектора 2 в устройстве сравнения фаз 1, в котором сигналы на двух выходах Р и N фазового детектора 2 с помощью двух ключей 131 и 132 управляют подключением и отключением двух разнополярных источников постоянного тока 121 и 122 для суммирования. Далее суммарный сигнал S фильтруют 3 и полученным сигналом U управляют частотой генератора 4, частоту генератора 4 делят 5 и формируют такты, которые поступают на второй вход Fc фазового детектора 2 в устройстве сравнения фаз 1. По каждому фронту опорного сигнала Fo подключают первый источник 121, Подключенный первый источник 121 отключают по первому фронту тактов Fc, поступившему после фронта опорного сигнала Fo, или по срезу опорного сигнала Fo, если он поступит раньше первого фронта тактов Fc после фронта опорного сигнала Fo. Второй источник 122 подключают по фронту опорного сигнала тактов Fc, если он поступит раньше среза опорного сигнала Fo. Подключенный второй источник 122 отключают по первому срезу тактов Fc. На фиг. 1 также показано подключение источников к питанию Vcc и общему проводу GND.

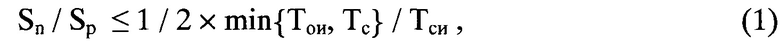

Отношение сигнала второго источника Sn к сигналу первого источника Sp устанавливают согласно формуле:

где Тси - длительность импульсов тактов;

Тсп - длительность паузы тактов;

Тои - длительность импульса опорного сигнала;

Тс - длительность периода тактов (Тс=Тси+Тсп).

На временной диаграмме фиг. 2 также используются обозначения:

Uo - средний уровень напряжения на входе генератора 4;

Тф - текущий сдвиг между фронтами сигнала опорной частоты и тактов;

Тфо - номинальное значение сдвига между фронтами сигнала опорной частоты и тактов в режиме удержания.

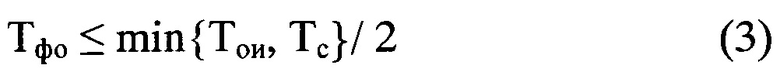

Номинальное значение сдвига между фронтами сигнала опорной частоты и тактов в режиме удержания Тфо определяется по формуле;

Для значений Sn и Sp в соответствии с (1) формула (2) приводится к условию;

Полярность слагаемых Р и N предполагает повышение частоты генератора 4 при увеличении напряжения U. При опережении фронтом опорного сигнала Fo фронта тактов Fc на время меньше Тфо, то частоту тактов уменьшают, а если это время больше Тфо, то частоту тактов увеличивают.

Для первых двух импульсов (фиг. 2) Тои<Тс и Тфо≤Тои/2. Подстройка при кратных периодах поясняется третьим импульсом на временной диаграмме фиг. 2, для которой можно выбрать Тфо≤Тс/2, если не требуется работа в первом режиме.

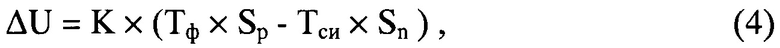

Линейная работа устройства сравнения фаз 1 осуществляется в области значений Тф меньших Тои. При угловом представлении линейная область расположена от 0 до 2π×Тои/Тс и в ней после отработки фронта опорной частоты сдвига на Тф по завершению всех переходных процессов изменение постоянной составляющей напряжения на выходе фильтра ΔU определяется по формуле:

где К коэффициент передачи фильтра.

В зоне от 0 до 2π×Тфо/Тс получается отрицательное ΔU (второй импульс), а в диапазоне от 2π×Тфо/Тс до 2π - положительное (первый и третий импульс). Если Тои<Тс, то появляется нелинейная зона от 2π×Тои/Тс до 2π, в которой ΔU положительно, постоянно и равно:

Устойчивость петли обеспечивается параметрами фильтра.

После захвата в зоне удержания переключения сигнала опорной частоты и тактов разнесены на время Тфо, что обеспечивает функциональную устойчивость способа (как возможность построения устройства свободного от влияния опасных состязаний).

Фазовый детектор (фиг. 3) содержит два триггера 211 и 212, два элемента И 221 и 222. Тактовый вход устройства Fc соединен с С-входом первого триггера 211. Первый Р и второй N выходы фазового детектора 2 соединены попарно соответственно с выходами первого 221 и второго 222 элементов И, первый вход первого элемента И 221 соединен с D-входом первого триггера 211, входы второго элемента И 222 соединены попарно соответственно с D-входом и вторым выходом второго триггера 212. Второй вход первого элемента И 221 соединен с вторым выходом первого триггера 211, тактовый вход Fc соединен с инверсным С-входом второго триггера 212, вход опорной частоты Fo соединен с D-входом первого триггера 211, первый выход Q1 первого триггера соединен с D-входом второго триггера 212. Кроме того, на фиг.3 также приведены элементы устройства сравнения фаз 1: ключи 131, 132 и разно полярные источники 121, 122.

Оба D-триггера - двухступенчатые.

Дополнительно к схеме (фиг. 3) фазовый детектор (фиг. 4) содержит два элемента ИЛИ-НЕ 231 и 232, вход опорной частоты Fo соединен с первыми входами элементов ИЛИ-НЕ 231 и 232. Вторые входы первого и второго элементов ИЛИ-НЕ 231 и 232 соединены попарно соответственно со вторым выходом второго триггера 212 и первым выходом Q1 первого триггера 211. Выходы первого и второго элементов ИЛИ-НЕ 231 и 232 соединены попарно соответственно с входами сброса первого и второго триггеров 211 и 212. Входы сброса обоих триггеров асинхронные.

На фиг. 5 представлено дополнение к фазовому детектору (фиг. 4.), в котором дополнительный вход разрешения EN соединен с третьими входами первого и второго элементов ИЛИ-НЕ 231 и 232.

На фиг. 6 сплошными линиями показаны временные диаграммы всех сигналов схемы (фиг. 3), а пунктиром - сигналов Q1, Q2, сигналов на выходах элементов ИЛИ-НЕ 231 и 232 схемы (фиг. 4).

В схеме, приведенной на фиг. 3, после фронта Fo (фиг. 6) переключается в лог. 1 первый элемент И 221 (выходной сигнал Р). Если срез импульса Fo появится раньше фронта тактов (третий импульс Fo диаграмме на фиг. 6), то первый элемент И 221 (выходной сигнал Р) переключается в лог. 0, а триггер 211 остается в состоянии лог. 0. Если раньше появится фронт тактов срез импульса Fo (первый и второй импульс Fo диаграмме на фиг. 6), то первый триггер 211 (обозначение на диаграммах - Q1) переключается в лог. 1, затем первый 221 и второй 222 элементы И (выходные сигналы Р и N) переключатся соответственно в лог. 0 и 1. Далее по срезу тактов второй триггер 212 (обозначение на диаграммах - Q2) переключится в лог.1, затем второй 222 элемент И переключится в лог. 0. Первый фронт тактов после среза импульса Fo приведет к переключению первого триггера 211 Q1 в лог. 0, затем по следующему срезу тактов в лог. 0 перейдет второй триггер 212 Q2.

При равных номинальных частотах опорной частоты и тактов первый триггер 211 не успевает восстановиться, поэтому схема (фиг. 3) может применяться для подстройки по опорным частотам Fo, период которых кратен периоду тактов в 2 или более раз.

Функциональная устойчивость устройства (фиг. 3) обеспечивается смешением переходных процессов в триггерах на половину периода тактов.

Работа схемы (фиг. 4) на кратных периодах поясняется диаграммой (фиг .6) с учетом пунктирных линий. До момента переключения в лог.1 второго триггера 212 Q2 при сигнале лог. 0 на входе Fo схемы, приведенные на фиг. 3 и 4, работают одинаково (сплошные линии на фиг. 6). После этого переключения параллельно с переключением в лог. 0 второго элемента И 222 происходит переключение первого элемента ИЛИ-НЕ 231 в лог.1 (пунктирные линии на фиг. 6), после этого асинхронно сбрасывается триггер 211 Q1. Затем последовательные переключение второго элемента ИЛИ-НЕ 232 в лог. 1, асинхронный сброс второго триггера 212 Q2 и переключение первого элемента ИЛИ-НЕ 231 в лог. 0. Второй элемент ИЛИ-НЕ 232 переключится в лог. 0 только после фронта Fo. По диаграмме фиг. 6 видно, что несмотря отличия в некоторых переключениях триггеров выходные сигналы для схем, приведенных на фиг. 3 и 4, одинаковы.

Фазовый детектор (фиг. 4) может работать при равных номинальных частотах. Временная диаграмма (фиг. 7) поясняет его работу в этом режиме. Последовательность переключений на временной диаграмме показана стрелками. По срезу импульса тактов Fc происходят последовательные переключения второго триггера 212 Q2 в лог. 1 и затем первого элемента ИЛИ-НЕ 231 в лог. 1. После выполняются асинхронный сброс триггера 211 Q1, затем переключение второго элемента ИЛИ-НЕ 232 в лог. 1. Затем выполняется асинхронный сброс второго триггера 212 Q2 и переключение первого элемента ИЛИ-НЕ 231 в лог. 0. После этих переключений в паузу до фронта тактов должен успеть переключится вспомогательный триггер в составе первого триггера. Длительность паузы тактов должна быть больше суммы задержек 3-х элементов, асинхронного сброса 2-х триггеров и записи в D-триггер.

Фазовый детектор (фиг. 4) функционально устойчив (устойчив к состязаниям), т.к. элементы для последовательного асинхронного сброса триггеров не вносят опасных состязаний и работа схемы не зависит от разброса задержек.

Фазовый детектор (фиг. 5) при лог. 0 на входе EN работает также как схема (фиг. 4), с любой кратностью периода опорной частоты к периоду тактов. При лог. 1 на входе EN он работает аналогично схеме (фиг. 3).

Таким образом, предложенные способ и фазовый детектор функционально устойчивы (свободны от влияния состязаний), работают с опорным сигналом с любой кратностью периода к периоду тактов, могут подстраивать частоту тактов по фронтам данных.

Источники информации

1. Патент US 5892380, кл. 337/172, 06.04.1999.

2. Патент US 8975924, кл. 337/12, 10.03.2015.

3. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах/ Под ред. В.И. Варшавского. - М.: Наука Гл. ред. физ-мат. лит., 1986. - 400 с. (глава 9)

4. Патент РФ 2622628, МПК H03D 13/00, 08.08.2016.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ ПО ДАННЫМ И ФАЗОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2711752C2 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2016 |

|

RU2622628C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2661328C1 |

| РЕГИСТР СДВИГА | 1990 |

|

RU2024075C1 |

| СЧЕТЧИК | 1991 |

|

RU2028028C1 |

| Синхронный счетчик | 1984 |

|

SU1190520A1 |

| Апериодическое импульсное устройство | 1980 |

|

SU940283A1 |

| Синхронный счетчик | 1985 |

|

SU1257838A1 |

| Фазовый детектор | 1989 |

|

SU1737700A1 |

| Счетное устройство | 1983 |

|

SU1228268A1 |

Изобретение относится к радиотехнике. Технический результат – повышение функциональной устойчивости (устранение влияния опасных состязаний) в режиме удержания. Для этого предусмотрен способ подстройки частоты, в котором сигналы на двух выходах фазового детектора (ФД) управляют подключением и отключением двух разнополярных источников. Далее суммарный сигнал фильтруют и им управляют генератором, первый источник подключают по фронту опорного сигнала (ОС), первый источник отключают по первому поступившему фронту тактов или срезу ОС, второй источник подключают после фронта ОС по фронту тактов, если он поступит раньше среза ОС, второй источник отключают по первому срезу тактов. 2 н. и 3 з.п. ф-лы, 7 ил.

1. Способ подстройки частоты, в котором опорный сигнал поступает на первый вход фазового детектора в устройстве сравнения фаз, в котором сигналы на двух выходах фазового детектора с помощью двух ключей управляют подключением и отключением двух разнополярных источников постоянного тока для суммирования, далее суммарный сигнал фильтруют и полученным сигналом управляют частотой генератора, частоту генератора делят и формируют такты, которые поступают на второй вход фазового детектора в устройстве сравнения фаз, первый источник подключают по каждому фронту опорного сигнала, отличающийся тем, что подключенный первый источник отключают по первому фронту тактов, поступившему после фронта опорного сигнала, или по срезу опорного сигнала, если он поступит раньше первого фронта тактов после фронта опорного сигнала, второй источник подключают после фронта опорного сигнала по фронту тактов, если он поступит раньше среза опорного сигнала, подключенный второй источник отключают по первому срезу тактов.

2. Способ по п. 1, отличающийся тем, что отношение сигнала второго источника к сигналу первого источника устанавливают равным или меньшим 1/2 отношения наименьшего из значений длительности импульса опорной частоты или периода тактов к длительности импульса тактов.

3. Фазовый детектор, содержащий два D-триггера, два элемента И, причем тактовый вход соединен с прямым С-входом первого триггера, первый и второй выходы фазового детектора соединены попарно соответственно с выходами первого и второго элементов И, первый вход первого элемента И соединен с D-входом первого триггера, входы второго элемента И соединены попарно соответственно с D-входом и вторым выходом второго триггера, отличающийся тем, что второй вход первого элемента И соединены с вторым выходом первого триггера, тактовый вход соединен с инверсным С-входом второго триггера, вход опорной частоты соединен с D-входом первого триггера, первый выход первого триггера соединен с D-входом второго триггера,

4. Фазовый детектор по п. 3, отличающийся тем, что содержит два элемента ИЛИ-НЕ, вход опорной частоты соединен с первыми входами элементов ИЛИ-НЕ, вторые входы первого и второго элементов ИЛИ-НЕ соединены попарно соответственно с вторым выходом второго триггера и первым выходом первого триггера, выходы первого и второго элементов ИЛИ-НЕ соединены попарно соответственно с входами сброса первого и второго триггеров.

5. Фазовый детектор по п. 4, отличающийся тем, что имеет дополнительно вход разрешения, который соединен с третьими входами первого и второго элементов ИЛИ-НЕ.

| СПОСОБ И УСТРОЙСТВО ДЛЯ УМЕНЬШЕНИЯ ФАЗОВЫХ СКАЧКОВ ПРИ ПЕРЕКЛЮЧЕНИИ ИСТОЧНИКОВ СИНХРОНИЗАЦИИ | 2002 |

|

RU2288543C2 |

| CN 101572527 A, 04.11.2009 | |||

| CN 102751984 B, 22.04.2015 | |||

| CN 101924540 B, 04.07.2012 | |||

| CN 105934884 A, 07.09.2016. | |||

Авторы

Даты

2018-08-28—Публикация

2017-10-13—Подача