Изобретение относится к вычислительной технике и может быть использовано для хранения и сдвига информации.

Цель изобретения - упрощение устройства.

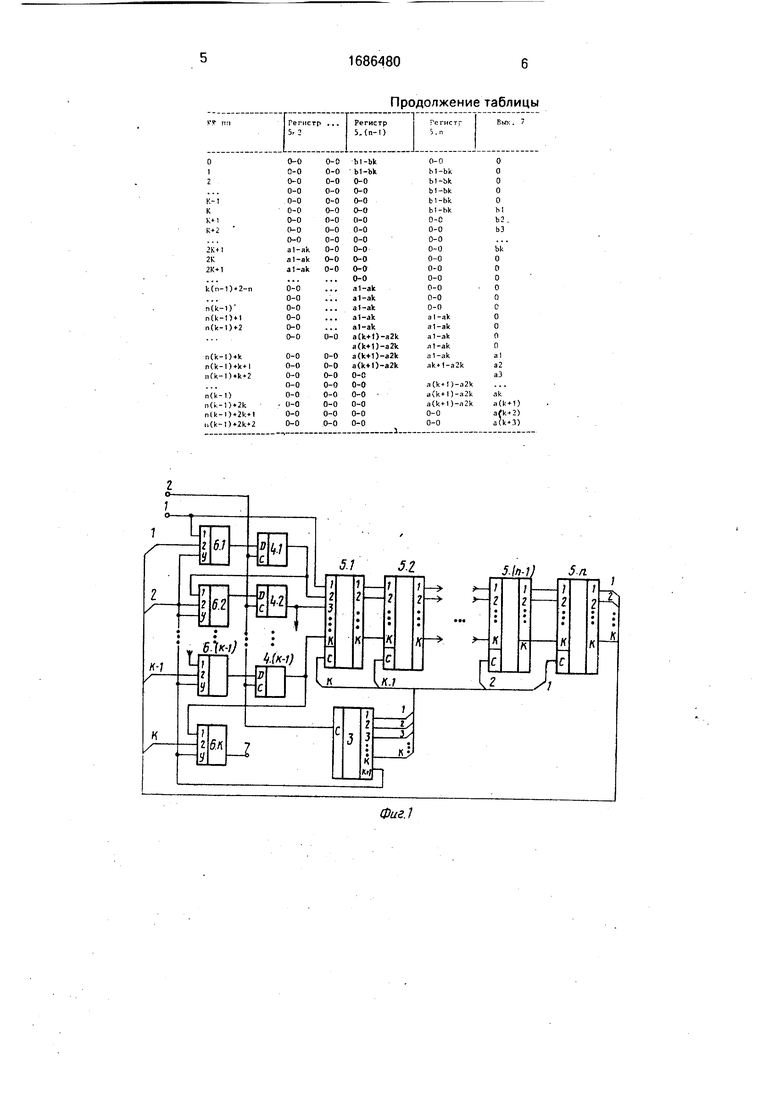

На фиг. 1 приведена схема устройства; на фиг.2 - временная диаграмма его работы.

На схеме (см.фиг. 1) обозначены информационный вход 1 устройства, синхровход 2, распределитель 3, К-1 триггер 4 1, 4.2,...4.(К-1), п регистров 5.1,5.2,...5(п-1), 5п,

К мультиплексоров 6.1, 6.26К и выход 7

устройства. Схема приведена для случая, когда

n - km,

,2,...; К 2; п 2.

Распределитель 3 может быть выполнен либо на базе сдвигового резистора, либо как счетчик с дешифратором. Триггеры 4.14.(К-1) - двухступенчатые. Каждый регистр 5.1,.,,5.п содержит К одноступенчатых триггеров. Функционирование устройства (см.фиг. 1) поясняется таблицей, в которой использованы следующие обозначения:

1)а1, .,a2L и Ыbk логические переменные

2)d1-dk - состояние k-разрядного регистра.

В качестве терма dj используют переменные aj, bj,

3)0-0 - состояние логического нуля на всех выходах k-разрядного регистра.

Временные соотношения между сигналами показаны на диаграмме (см.фиг.2), на которой показань- (акты с (к-1)-го по(2Н 1)-й (см. таблицу). Для принятой на фиг 2 полярности сигналов распределителя 3 выходной сигнал каждого мультиплексора 6 соответствует сигналу на первом (втором) входе при сигнале логического О (1) на управляющем входе. Начальные состояния элементов устройства приведены в таблице строка 0. На вход 1 подается последовательность a1,...a2k и, начиная с k-ro такта, с выхода 7 считывается последовательность Ы,.. ,bk. По фронту импульса на входе 2 в каждом триггере происходит перезапись информации из первой ступени во вторую и на выход

сл

с

о оо

о

Јь

00

трипера. После (k-1)-ro такта на выходах

триггеров 4.14.(К-1) устанавливается код

а(К-1)а1. Этот код и бит ak с входа 1 по

фронту импульса с k-ro выхода распределителя 3 записывается в регистр 5.1. На выход каждого мультиплексора 6 передается сигнал с второго входа, так как на (К+1)-м выходе распределителя 3 установлена логическая 1. На выход 7 передается символ Ы с k-ro выхода регистра 5.п. Одновременно остальные мультиплексоры

6.16.(К-1) передают код Ь2Ь(К-1) на

входы первых ступеней триггеров 4.(k- 1)4.1, Запись этой информации осуществляется по срезу импульса на входе 2. В следующем (k+1)-M такте по фронту импульса на входе 2 код b2-b(k-1) устанавливается на выходах триггеров 4.(k-1),...,4.1 благодаря перезаписи информации из первых ступеней во вторые. Сигнал переноса распределителя 3 устанавливается в логической О и выход 7 коммутируется с выходом триггера 4,(k-1). По срезу импульса на входе 2 в первые ступени триггеров 4.1,..,4.(k-1)

записывается код a(k-1), bkЬЗ, который

появляется на выходах этих триггеров по фронту импульса на входе 2 в следующем такте и т.д. в соответствии с таблицей и диаграммой (см.фиг.2). В р-й регистр

() код а1-аК запишется в k+(P-1) (K1)-м такте, а в n-й регистр этот код запишется в k+(n-1) (k-1)n(k-1)+1-M такте. В общем случае для сдвигающего устройства при

.k-g (,2 ,1k-1) считывание

первого символа из n-го регистра на выход произойдет через (k-g-1) тактов после записи в n-й регистр.

Эффективная разрядность сдвигающего устройства определяется по формуле

(k-1)+1-k-g-1-1 n(k-1)+k-g-1(n+1Xk-1)-g При последний регистр избыточен. Наиболее эффектно устройство при , когда разрядность равна (n-И) (k-1). 5По сравнению с прототипом экономия

оборудования составляет К двухступенчатых (2К одноступенчатых) триггеров.

10

Формула изобретения

Сдвигающее устройство, содержащее распределитель, К-1 триггер, К 2, п регистров, n m-K-g, где ,2... и ,1K-1, a

(п+1ХК-1)-д1 - разрядность устройства, и К

5 мультиплексоров, причем 1-й выход распределителя, ,К, соединен с синхровходом 1К-{1+1)-го регистра, ,2,31-й выход каждого регистра, кроме n-го, соединен с i-м информационным входом последующего регистра, выход 1-го триггера соединен с первым информационным входом (1+1-го мультиплексора, 1-й выход n-го регистра соединен с вторым информационным входом 1-го мультиплексора, выход которого соеди5 нен с информационным входом 1-го триггера, синхровходы триггеров и вход распределителя являются синхровходом устройства, (К+1)-й выход распределителя соединен с управляющими входами

0 мультиплексоров, отличающееся тем, что, с целью упрощения устройства, первый информационный вход первого мультиплексора и первый информационный вход первого регистра являются информационным

5 входом устройства, выход 1-го триггера соединен с (1+1)-м информационным входом первого регистра, а выход K-ro мультиплексора является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

| Устройство для контроля мультиплексоров | 1987 |

|

SU1511749A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Сдвигающее устройство | 1989 |

|

SU1679556A1 |

| Устройство управления микропрограммной ЭВМ | 1989 |

|

SU1691840A1 |

| Устройство для возведения в квадрат М-разрядных двоичных чисел | 1986 |

|

SU1399733A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1737461A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения регистров сдвига. Цель изобретения - упрощение устройства достигается тем, что в устройстве, содержащем К мультиплексоров 6, триггеры 4, К регистров 5 и распределитель 3, триггер 4 используется как для последовательного приема, так и для последовательной выдачи информации. Это позволяет получить экономию оборудования в виде 2 К одноступен- ,-пых триггеров. 2 ил.

П 11 - О -п

п . - 1 I

r(k-n«Jk ч (k - i .V ч

О

О

о о о

О

о

MU-1)

ak

О О

о

J ( к . I

j(k-3

0-0 0-0

П-Л 0-0 0-0 (1-е

0-0

0-0

0-0 0-0

о-е

Р-С

О-С;

Продолжение таблицы

к+1 /с+2

2к-1 . 2к 2л

PLh.

ц,ам)( а« fa/ft) )(a(K Z))(a(K-u {at2x-l)(a2K

,71

к- к

П

W а(г)а(к-1( бк %a(K t)Ya(afti(-2)fo(2K-i)} ич-г о()а(к-2))(&(к-1)( Вк Xefr Q Xo/fr-z;

) / Q yg2 Xg3 Л8 Вк Ка()

S-1 Ц

а; - ак

us-n 61-Вк д

7 ХдГТаГУдГТдТХдГХ

Фиг. 2

2к-1 . 2к

л

П

J(QM)-(J2K

| Майоров С.А. | |||

| Новиков Г.И | |||

| Структура электронных вычислительных машин, Л.: Машиностроение | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Регистр сдвига | 1987 |

|

SU1464216A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-10-23—Публикация

1989-09-29—Подача