Изобретение относится к устройствам передачи дискретной информации и может быть использовано в системах автоматической локомотивной сигнализации, автоблокировки и других устройствах железнодорожной автоматики и телемеханики.

Известно устройство декодирования, являющееся наиболее близким к предложенному и содержащее сдвиговый регистр, генератор импульсов, запоминающий блок, элемент ИЛИ, дополнительный источник импульсов.

Недостатком этого устройства является низкая информативность, так как декодирование осуществляется только по одному каналу.

Цель изобретения - повышение информативности устройства за счет одновременного декодирования по двум каналам.

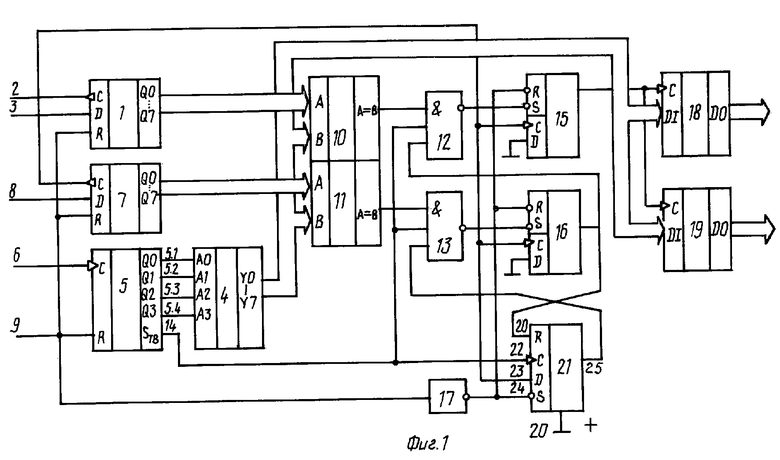

На фиг.1 приведена блок-схема устройства; на фиг.2 - пример выполнения селектора сигнала цикловой синхронизации; на фиг.3 - пример выполнения пересчетного блока.

Устройство содержит (фиг.1) первый регистр сдвига 1, тактовый вход 2, первый информационный вход 3, блок 4 памяти, пересчетный блок 5, синхровход 6, второй регистр сдвига 7, второй информационный вход 8, вход 9 установки в начальное состояние, блоки 10, 11 сравнения, элементы И-НЕ 12, 13, шину 14 нулевого потенциала D-триггеры 15, 16, инвертор 17, буферные регистры 18, 19, положительную шину питания 20, селектор 21 сигнала цикловой синхронизации.

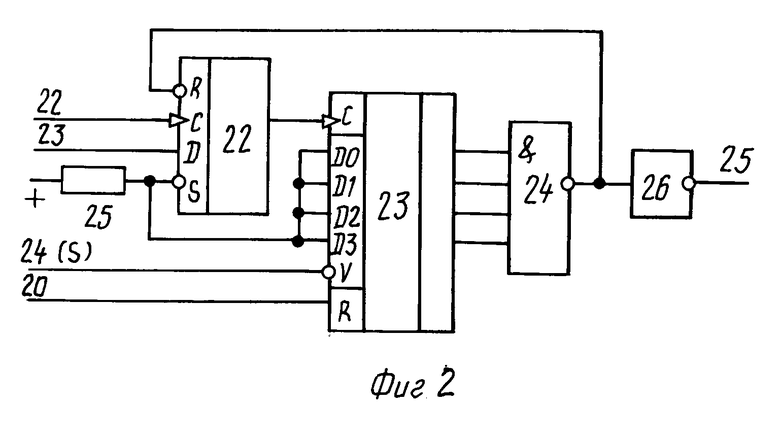

Селектор 21 сигнала цикловой синхронизации (фиг.2) содержит D-триггер 22, четырехразрядный двоичный счетчик 23, четырехвходовой элемент 24 И-НЕ, токозадающий элемент (резистор) 25 и инвертор 26.

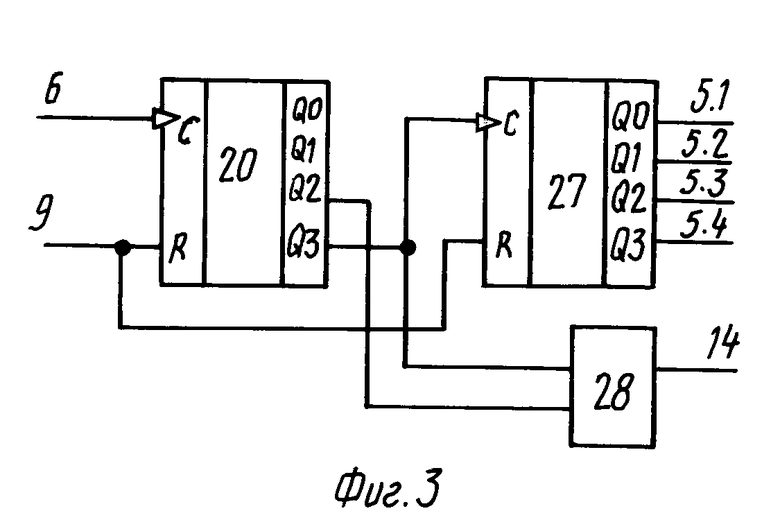

Пересчетный блок 5 (фиг.3) содержит второй четырехразрядный двоичный счетчик 27, элемент 28 И, первый счетчик 29.

Устройство работает следующим образом.

На тактовый вход 2 регистра 1 поступает сигнал частотой Fm, период этого сигнала равен длительности элементарного бита, последовательности которых поступают на входы 3 и 8 регистров 1 и 7. Допустим, что на входы 3 и 8 поступают восьмиразрядные кодовые комбинации группового кода (в частности, кода Бауэра или кода Эмминга), содержащие четыре информационных разряда и четыре проверочных разряда. Задний фронт тактового импульса по времени приходится на середину элементарного бита. Кодовые комбинации синхронизированы на передающей стороне друг относительно друга, поэтому начало и конец кодовых комбинаций по двум подканалам 3 и 8 совпадают. Предполагается, что кодовые комбинации, поступающие на вход 8, имеют приоритет перед кодовыми комбинациями, поступающими на вход 3, т.е. производить декодирование по входу 3 разрешается только в случае правильного декодирования по входу 8. Устройство предназначено для использования в системах с циклической передачей постоянной информации, смена которой происходит не чаще, чем через временной интервал в пять-десять временных интервалов передачи одной кодовой комбинации, а также от разных передатчиков, переключение которых носит случайный характер, в частности, например, данное устройство может быть использовано в каналах передачи информации системы автоматической локомотивной сигнализации.

Во-первых, рассмотрим ситуацию, когда передается постоянная информация от одного передатчика. Тогда в худшем случае за восемь тактов (относительно заднего фронта) сигнала Fm, поступающего на вход 2 на выходах регистров 1 и 7, будут установлены в параллельном коде принятые кодовые комбинации. При четырех информационнных разрядах возможно шестнадцать разрешенных кодовых комбинаций, которые хранятся в запоминающем блоке 4. Счетчик 5 тактируется частотой 1024*Fm, что обеспечивает за время сдвига одного бита информации в регистрах 1 и 7 четырехкратной перебор всех разрешенных кодовых комбинаций из запоминающего блока 4. Принятые кодовые комбинации с выходов регистров 1 и 7 поступают на первый 10 и второй 11 блоки сравнения, где непрерывно сравниваются с набором разрешенных кодовых комбинаций, поступающих в параллельном коде с выходов запоминающего блока 4 на вторые входы первого 10 и второго 11 блоков сравнения. В момент совпадения принятой кодовой комбинации с одной из разрешенных на выходе блока сравнения появляется единичный импульс. При этом информация, поступающая на вход 8, имеет высший приоритет по сравнению с информацией на входе 3, поэтому сигнал совпадения с выхода блока 10 на выход элемента И-НЕ 12 поступит только в том случае, когда был сформирован сигнал совпадения с выхода блока 11 с помощью элемента И-НЕ 13, D-триггера 16 и блока выделения сигнала цикловой синхронизации 21. Так как по двум подканалам информация в общем случае различна, то моменты совпадения разрешенных кодовых комбинаций по разным подканалам не совпадают, поэтому для запоминания факта совпадения в устройство введены триггеры 15 и 16, S-входы которых подключены к выходам элементов И-НЕ 12, 13. Нулевым сигналом на выходе элемента И-НЕ 12 триггер 16 устанавливается в единичное состояние, в котором он будет находиться до момента прихода очередного фронта тактового импульса Fm, поступающего на С-вход триггера 16 и записывающего в него нуль с D-входа, подключенного к общей шине. За время нахождения триггера 16 в единичном состоянии происходит сравнение кодовой комбинации, принятой по первому подканалу 2, с разрешенной кодовой комбинацией, и в триггер 15 будет записана логическая единица. Момент появления логической единицы на выходе триггера 15 соответствует правильной принятой информации, поэтому этот сигнал записывает в буферные регистры 18 и 19 информационные разряды соответствующих кодовых комбинаций (в рассматриваемом случае четыре разряда; в общем случае, если дальнейшая обработка ведется в избыточном кодировании, то в регистры записываются кодовые комбинации с информационными и проверочными разрядами). Для того, чтобы исключить появление ложных импульсов сравнения на выходах элементов И-НЕ 12, 13, вызванных логическими состязаниями в блоках 10, 11, 4, на входы элементов И-НЕ 12, 13 подается стробирующий сигнал единичного уровня с выхода 14 (STB) блока 5, причем фронты этого сигнала не совпадают с моментами изменения сигналов на входах 5.1-5.4 блока 5. Вход 9 устройства декодирования предназначен для установки в начальное состояние всех блоков устройства. Единичный импульс на этом входе устанавливает блоки 1, 5, 7, 15 и 16 в нулевое состояние, блок 21 - в единичное состояние. При этом блоки 15, 16 и 21 устанавливаются сигналы нулевого уровня с выхода инвертора 17.

Пересчетный блок 5 (фиг.3) делит частоту 1024*Fm с помощью двух четырехразрядных двоичных счетчиков 29 и 27. Сигналы с двух старших разрядов счетчика 29 подаются на входы элемента И 28, выход которого 14 является стробирующим выходом блока 5.

Блок выделения сигнала цикловой синхронизации 21 (фиг.2) предназначен для формирования сигнала разрешения выдачи сигнала сравнения кодовых комбинаций на выходе элемента И-НЕ 13.

Данный блок работает следующим образом.

При поступлении сигнала начальной установки нулевого уровня в двоичный четырехразрядный счетчик 23 записывается единица во все разряды, на выходе элемента И-НЕ 24 формируется нулевой сигнал, который устанавливает триггер 29 в нулевое состояние и запрещает прохождение тактовых импульсов Fm с выхода блока на С-вход счетчика 23. На выходе инвертора 26 формируется единичный сигнал, который разрешает поступление сигнала сравнения с выхода блока 11 на S-вход триггера 16 через элемент И-НЕ 13. Как только сигнал сравнения установит триггер 16 в единичное состояние, счетчик 23 устанавливается в нулевое состояние, в результате чего на выходе элемента И-НЕ 24 формируется единичный сигнал, который разрешает прохождение тактовых импульсов Fm на С-вход двоичного счетчика 23. На выходе инвертора 26 формируется сигнал логического нуля, который запрещает формирование сигнала сравнения кодовых комбинаций, поступающих на вход 8 устройства. Сигнал разрешения на выходе блока 21 появится только через шестнадцать тактовых импульсов Fm. Это сделано для того, чтобы исключить ложный прием кодовой комбинации, полученной при смене информации в канале связи, когда часть разрядов кодовой комбинации относится к старой информации, а часть разрядов - к новой информации. Например, передавалась кодовая комбинация кода Бауэра 00011111, которая изменилась на кодовую комбинацию 11100000. Последняя в дальнейшем циклически повторяется не менее пяти раз. Из-за поразрядного сдвига информации в регистре 7 импульс сравнения формируется на выходе блока 11 на четвертом бите новой кодовой комбинации, который соответствует ложной кодовой комбинации 11111110, а еще через три - бита формируется истинный импульс сравнения, соответствующий кодовой комбинации 11100000.

Исходя из этого можно было формировать сигнал разрешения на выходе блока 21 через восемь тактовых импульсов. Однако возможна ситуация при случайной смене, например, кодовой комбинации 01001010 на 00101100 на пятом бите, тогда на девятом тактовом импульсе появляется ложный импульс сравнения, соответствующий кодовой комбинации 10011000, которая в данное время не передается. В общем случае в такой ситуации ложный импульс сравнения может появиться через число тактов от 8 до 15 после получения предыдущего импульса сравнения.

Таким образом, блок 21 позволяет исключить ложный прием, не передаваемых в данный момент разрешенных кодовых комбинаций.

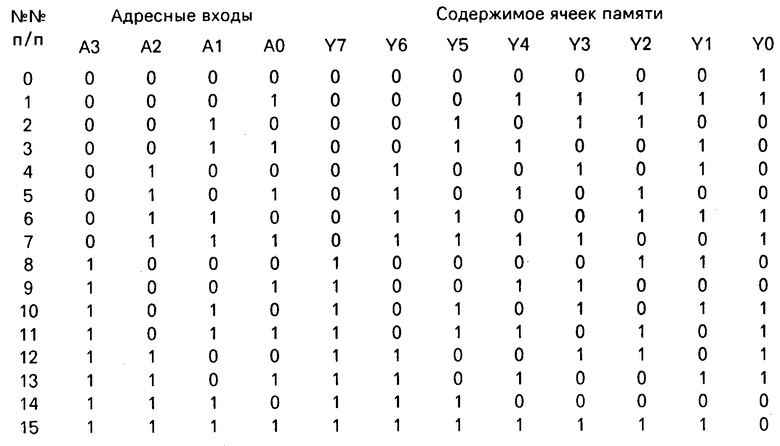

Блок 4 может быть выполнен в виде комбинационной схемы, построенной на основе следующих соотношений (для кода Бауэра):

Y7=A3; Y6=A2; Y5=A1; Y4=A0;

Y3=A1+A2+A3;

Y2=A0+A2+A3;

Y1=A0+A1+A3;

Y0=A0+A1+A2,

при этом для реализации этих логических выражений потребуется два корпуса микросхем типа К555ЛП5, содержащих в своем составе двухвходовые элементы Исключающее ИЛИ, и один инвертор, например, микросхема К555ЛН1.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОНТРОЛЯ УРОВНЯ БОДРСТВОВАНИЯ ОПЕРАТОРА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2087358C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| ВЫЧИСЛИТЕЛЬ РАНГОВОЙ СТАТИСТИКИ | 1997 |

|

RU2122746C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Кодирующее устройство | 1987 |

|

SU1481899A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ ПРИ МАНЕВРОВОЙ РАБОТЕ НА ЖЕЛЕЗНОДОРОЖНОЙ СТАНЦИИ | 1999 |

|

RU2179518C2 |

Изобретение относится к устройствам передачи дискретной информации и может быть использовано в системах автоматической локомотивной сигнализации, автоблокировки и других устройствах железнодорожной автоматики. Цель изобретения - повышение информативности устройства за счет одновременного декодирования по двум каналам. Для достижения этого в устройство, содержащее регистр 1 сдвига, блок 4 памяти, введены пересчетный блок 5, регистр 7, первый 10 и второй 11 блоки сравнения, первый 12 и второй 13 элементы И - НЕ, первый 15 и второй 16 D-триггеры, инвертор 17, первый 18 и второй 19 буферные регистры, селектор 21 сигнала цикловой синхронизации. Пересчетный блок 5 содержит первый, второй четырехразрядные двоичные счетчики и элемент И. Селектор 21 сигнала цикловой синхронизации содержит D-триггер, четырехразрядный двоичный счетчик, четырехвходовой элемент И - НЕ, токозадающий элемент и инвертор. 2 з.п.ф-лы, 3 ил., 1 табл.

| Темников Ф.Е | |||

| и др | |||

| Теоретические основы информационной техники | |||

| М.: Энергия, 1971, стр.128, рис.3-24. |

Авторы

Даты

1994-12-15—Публикация

1990-06-07—Подача