Изобретение относится к области железнодорожной автоматики, в частности к устройствам контроля за скоростью движения.

Известны устройства измерения скорости посредством скоростемера СЛ-2М (Казаков А.А. и др. Системы интегрального движения поездов. М.: Транспорт, 1986, с. 290), измерителя скорости БИС (с. 266-268).

Недостатки известных устройств - сравнительно невысокая точность и искажение информации о скорости при буксовании.

Наиболее близким по технической сущности к заявляемому устройству является выбранное в качестве прототипа устройство, которое содержит последовательно соединенные блок измерения скорости, который состоит из генератора, делитель опорной частоты, суммирующий элемент, элементы совпадения, фазовый дискриминатор и логические ключи, блоки памяти о скорости, ускорении и пройденном пути и пороговое устройство определения буксования.

Недостатком известного устройства является то, что при буксовании колесной пары с осевого датчика пути и скорости на выходе скоростемера появляется ложная информация.

Использование одновременно нескольких аналогичных устройств не дает желаемого результата, т.к. возможно синхронное буксование двух и более колесных пар.

Цель изобретения - увеличение точности за счет более раннего определения буксования.

Указанная цель достигается тем, что устройство для контроля параметров движения, содержащее генератор импульсов, соединенный с делителем частоты, блоки определения пути, ускорения и скорости, последний из которых содержит счетчик и блоки импульсов, входами которого образованы входы блока, к одному из которых подключен выход делителя частоты, блоки памяти о пройденном пути, скорости и ускорении в условиях буксования и пороговый блок определения буксования, дополнительно снабжено приемником импульсов, выход которого соединен с другим входом блока определения скорости, снабженного последовательно соединенными тремя модулями-регистрами, первый из которых входом соединен с выходом счетчика импульсов, а вторыми выходами первого и второго модулей-регистров образованы соответственно первый и второй выходы блока, которые соединены соответственно с первым и вторым входами порогового блока определения буксования, имеющего последовательно включенные элемент памяти, входами которого образованы первый и второй входы блока, элемент запрета, триггер буксования, вторым входом которого образован третий вход блока, и счетчик буксования, на выходе которого включен элемент ИЛИ. Выходами третьего модуля-регистра образованы третий и четвертый выходы блока определения скорости, а первым выходом второго модуля-регистра - пятый выход, соединенный с одним из входов блока памяти скорости в условиях буксования, другой вход которого соединен с третьим выходом блока определения скорости, а выход через элемент запрета - с третьим входом порогового блока определения буксования. Четвертый выход блока определения скорости подключен к первому входу блока определения пройденного пути, второй вход которого соединен с информационным выходом блока памяти пройденного пути. Первый вход блока определения ускорения подключен к четвертому выходу блока определения скорости, а второй вход соединен с выходом блока памяти ускорения в условиях буксования через элемент задержки.

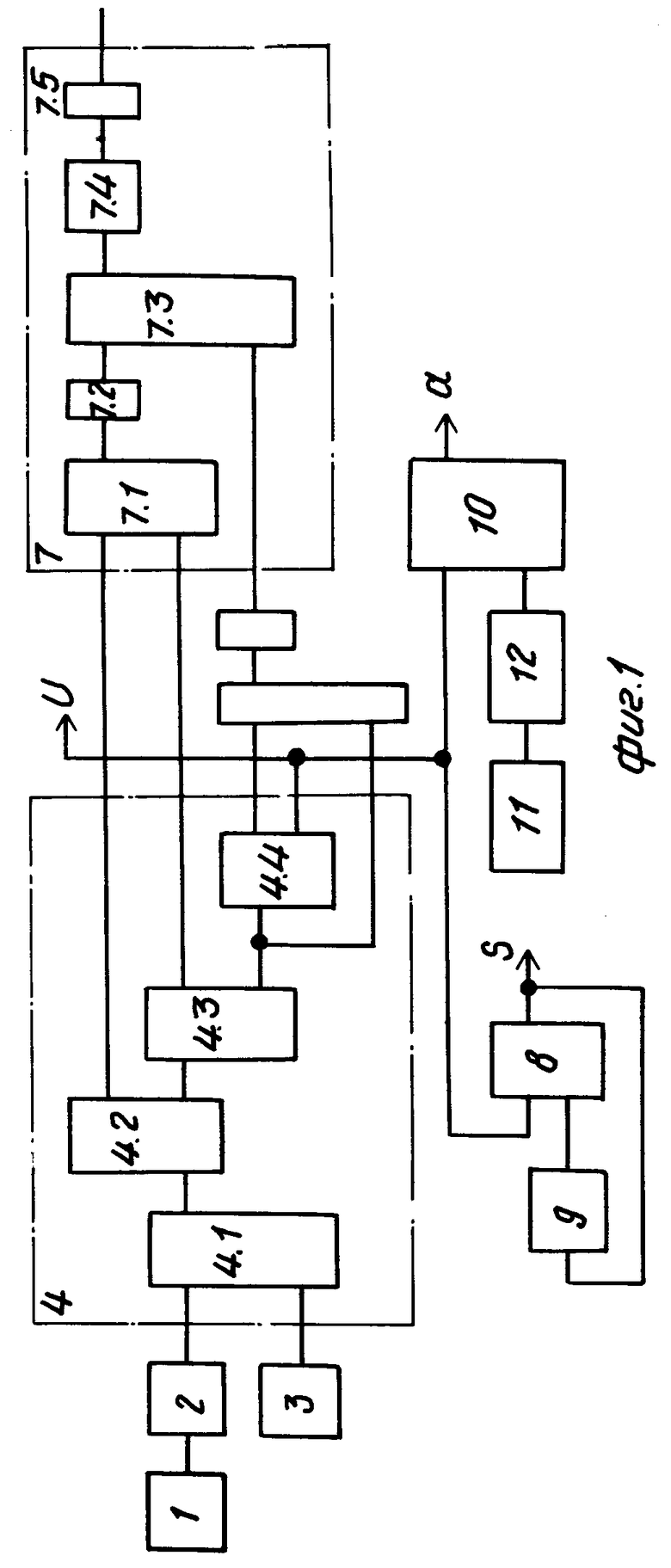

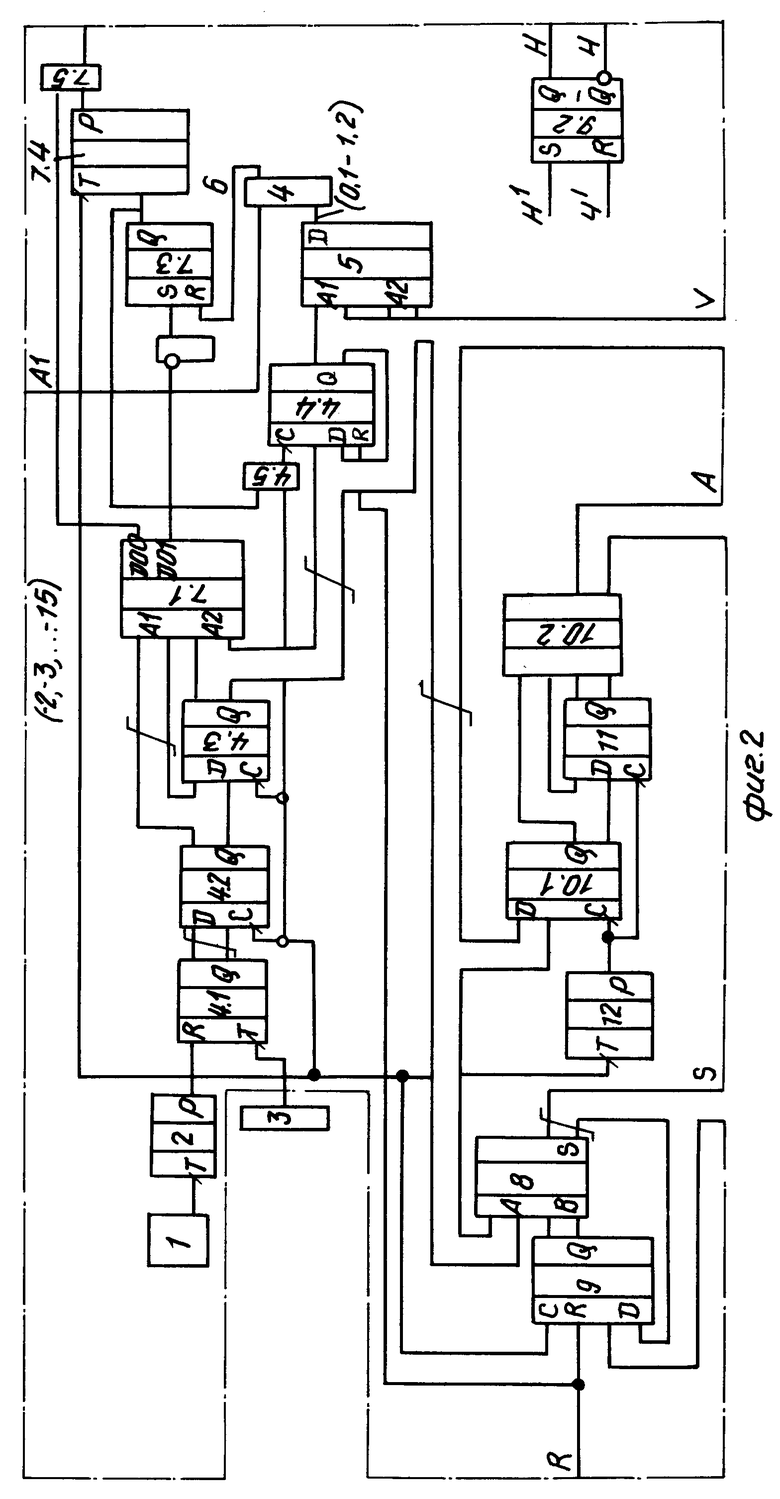

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - развернутая схема.

Генератор тактовых импульсов 1 посредством делителя частоты 2 и приемник 3 импульсов связаны с входом блока определения скорости 4, имеющему счетчики 4.1 импульсов и модули-регистры 4.2, 4.3 и 4.4. Оба входа блока 4 являются входами счетчика 4.1, выход которого соединен с первым модулем-регистром 4.2, который соединен с модулем-регистром 4.3. Блок 5 памяти скорости в условиях буксования соединен с элементом 6 запрета, который подключен к пороговому блоку 7 определения буксования, который имеет элемент памяти 7.1, второй вход которого соединен с выходом третьего модуля 4.4, второй выход которого соединен с входом блока 8 определения пройденного пути, соединенного с блоком 9 памяти пройденного пути и входом блока определения ускорения 10. Второй вход блока 10 соединен с блоком 11 памяти ускорения в условиях буксования через элемент 12 задержки. Выход блока памяти через элемент И соединен с входом триггера буксования 7.3, второй вход которого через инвертор 7.2 соединен с выходом элемента памяти 7.1, а выход - с входом счетчика буксования, выход которого соединен с входом логического элемента 7.5.

К выходу генератора 1 через делитель 2 подсоединены входы счетчика 7.4 и элемент 12 задержки, вход R счетчика 4.1, входы С блока памяти пути 9, первого модуля 4,3 и вход элемента 4.5. К выходу приемника 3 подсоединен вход Т счетчика 4.1. Выходы счетчика соединены с входами первого модуля 4.2, выход которого соединен с входом элемента 7.1 и входами D второго модуля 4.3, выходы которого соединены с входами элемента 7.1, входами D третьего модуля 4.4 и входами А2 блока памяти 5, входы А1 которого соединены с выходами третьего модуля 4.4, входами А блока определения пути 8, D регистра 10.1 блока определения ускорения. Входы А1 регистра 10.2 соединены с выходами Q регистра 10.1 и входами D регистра 11, вход С регистров 10.1 и 11 - с выходом Р элемента 12 задержки. Выход S блока 8 соединен с входом D блока 9, выходы которого соединены с входами В блока 8. Выходы регистра 11 соединены с входами А2 регистра 10.2. К выходу D00 элемента 7.1 подсоединен вход элемента 7.5, выход которого подсоединен к выходу АВ (аварийный) блока 9, а второй вход - к выходу Р счетчика 7.4, вход R которого подсоединен к выходу Q триггера 7.3 и второму входу элемента 4.5. К входу S триггера 7.3 через инвертор 7.2 подсоединен выход D01 элемента 7.1 и вход элемента 6, выход которого подсоединен к входу R триггера 7.3, а второй вход - к выходу блока 5. Вход С регистра 10,1 соединен с выходом Р счетчика 12 и входом С регистра 10.1.

При получении сигналов на выходе приемника 3 появляются короткие импульсы постоянного тока, которые отсчитывают счетчик 4.1 до получения на вход R положительного потенциала с генератора 1. Генератор коротких импульсов (1 мкс) сбрасывает счетчик 4.1, предварительно обеспечивая перенос информации из модуля 4.3 в модуль 4.4, из модуля 4.2 в модуль 4.3 и из счетчика 4.1 в модуль 4.2.

Количество импульсов с приемника 3, поступивших на вход Т счетчика в интервале между импульсами с генератора 1 (время цикла опроса локомотива), пропорционально скорости движения. Информация о скорости, полученная в двух смежных циклах опроса, хранится в модуле 4.2 и 4.3. Так как время цикла опроса составляет 1 с, в ускорение (замедление) не превышает 1 м/с2, то в модулях 4.2 и 4.3 информация не отличается более чем на 1 единицу. Например, в регистре 4.2 хранится число 0010, а в регистре 4.3-0011, или в модулях 4.2 и 4.3 хранится одно и то же число 0011. Элемент памяти 7.1 имеет два выхода, на одном из них (D01) потенциал повышен, если содержимое модулей 4.2 и 4.3 отличается не более, чем на единицу (0, +1, -1). При юзе, когда содержимое модуля 4.3 существенно больше содержимого модуля 4.2, повышается потенциал на втором выходе (D00), что соответственно повышает потенциал и на аварийном выходе АВ через элемент 7.5. При отсутствии логической единицы на выходе D01 происходит буксование. Устанавливается триггер 7.3, благодаря чему снимается повышенный потенциал с входа R счетчика 7.4 и входа элемента 4.5, который исключает запись информации в третий элемент 4.5. При этом в модуле 4.4 сохраняется информация о скорости движения, предшествующей началу буксования. В этот же момент счетчик 7.4 начинает отсчитывать время буксования (импульсы с генератора 1). Если время буксованияя превышает заданный интервал (коэффициент деления счетчика 7.4), то также появляется аварийный сигнал АВ. При кратковременном буксовании (до 15 с) счетчик не успевает отсчитывать полный цикл (16 импульсов с делителя 2) и сигнал АВ не подается. В момент буксования возможны три случая изменения скорости: сохранилась прежняя, незначительно возросла, незначительно упала. Блок памяти 5 устанавливает факт незначительного изменения скорости (сравнивается содержимое модулей 4.3 и 4.4) и посредством элемента 6 сбрасывается триггер 7.3. При этом проверяется, что новые замеры скорости после буксования в смежных циклах опроса не отличается более чем на единицу.

Итак, если не подается сигнал АВ, то на выходе третьего модуля в двоичном коде присутствует число, достаточно точно отражающее фактическую скорость маневрового состава. Эта информация поступает на входы А блока 8, входы D регистра 10.1 и входы А1 регистра 10.2. На входы В блока 8 поступает содержимое блока 9, в котором накапливается сумма всех предшествующих замеров скорости по сигналам через каждую секунду с делителя 2. В регистре 9 и блоке 8 появляются значения, пропорциональные проходимому пути (происходит интегрирование). При новом отсчете пути посредством входа R блока 9 осуществляется сброс регистра 4.4 и блока 9. Ускорение определяется посредством регистра 10.2, на вход которого через интервал времени, определяемый счетчиком 12 (делитель 1:8), подается значение скорости с регистра 11 (старое значение скорости) и 10.1 (новое значение скорости). Разность скоростей на фиксированный промежуток времени является ускорением, значение которого определяется регистром 10.2.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗАПОЛНЕНИЯ ПУТИ | 1991 |

|

RU2022854C1 |

| УСТРОЙСТВО ДЛЯ ОТСЛЕЖИВАНИЯ ДВИЖЕНИЯ ПОЕЗДА | 1991 |

|

RU2025360C1 |

| Устройство для контроля скорости подвижного состава | 1989 |

|

SU1648812A1 |

| РЕЛЬСОВАЯ ЦЕПЬ | 1991 |

|

RU2025361C1 |

| Устройство для приема на локомотиве информации с пути | 1990 |

|

SU1776597A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗА ДВИЖЕНИЕМ ПОЕЗДА | 1991 |

|

RU2028239C1 |

| СПОСОБ КОНТРОЛЯ СВОБОДНОСТИ ПУТЕВОГО УЧАСТКА И ФАЗОЧУВСТВИТЕЛЬНАЯ РЕЛЬСОВАЯ ЦЕПЬ | 1991 |

|

RU2025362C1 |

| Устройство для определения координаты локомотива | 1990 |

|

SU1832093A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ НА ПОДВИЖНОМ СОСТАВЕ | 1989 |

|

RU2022856C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МЕСТОНАХОЖДЕНИЯ МАНЕВРОВОГО ЛОКОМОТИВА | 1990 |

|

RU2026223C1 |

Использование: в области железнодорожной автоматики. Сущность изобретения: устройство содержит генератор тактовых импульсов, делитель частоты, приемник импульсов, блок определения скорости, блок памяти скорости в условиях боксования, элемент запрета, пороговый блок определения буксования, блок определения ускорения, элемент задержки, блок памяти ускорения в условиях буксования, блок определения пройденного пути, блок памяти пройденного пути. 2 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ ДВИЖЕНИЯ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТНОГО СРЕДСТВА, содержащее генератор импульсов, соединенный с делителем частоты, блоки определения пройденного пути, ускорения и скорости, последний из которых содержит счетчик импульсов, входами которого образованы входы блока, к одному из которых подключен выход делителя частоты, блоки памяти пройденного пути, скорости и ускорения в условиях боксования и пороговый блок определения боксования, отличающееся тем, что оно снабжено приемником импульсов, выход которого соединен с другим входом блока определения скорости, снабженного соединенными последовательно тремя модулями-регистрами, первый из которых входом соединен с выходом счетчика импульсов, а вторыми выходами первого и второго модулей-регистров образованы соответственно первый и второй выходы блока, которые соединены соответственно с первым и вторым входами порогового блока определения боксования, имеющего последовательно включенные элемент памяти, входами которого образованы упомянутые первый и второй входы блока, элемент запрета, триггер боксования, вторым входом которого образован третий вход блока, и счетчик боксования, на выходе которого включен элемент ИЛИ, причем выходами третьего модуля-регистра образованы третий и четвертый выходы блока определения скорости, а упомянутым первым выходом второго модуля-регистра - пятый выход, соединенный с одним из входов блока памяти скорости в условиях боксования, другой вход которого соединен с третьим выходом блока определения скорости, а выход через элемент запрета соединен с третьим входом порогового блока определения боксования, при этом четвертый выход блока определения скорости подключен к первому входу блока определения пройденного пути, второй вход которого соединен с информационным выходом блока памяти пройденного пути, первый вход блока определения ускорения подключен к четвертому выходу блока определения скорости, а второй вход соединен с выходом блока памяти ускорения в условиях боксования через элемент задержки.

| Никифоров Б.Д | |||

| и др | |||

| Автоматизация управления торможением поездов | |||

| М.: Транспорт, 1985, с.169-171, 199-202. |

Авторы

Даты

1994-12-30—Публикация

1990-06-28—Подача