Изобретение касается построения узлов цифровой техники и дискретной автоматики на логических элементах (преимущественно КМОП) и может быть реализовано в виде ИС.

Многоразрядные устpойства широко используются в управляющем режиме работы.

Известно N-разрядное счетное устройство, котоpое содержит L=разрядный счетчик с параллельным переносом и (M-L)-разрядный синхронный счетчик с последовательным переносом, каждый разряд которого выполнен на трех RS-триггерах (триггер Вебба).

Это устройство выполнено в монофункциональном базисе логических элементов и отличается небольшими аппаратурными затратами в ЭСЛ и ИИЛ, но имеет следующие недостатки:

минимальный период следования счетных импульсов Тmin составляет 6.tздрср;

задержка распространения переноса составляет 2.tздрср на один разряд, поэтому в режиме предельного быстродействия значение L определяется из условия

L ≥ log2{(N-L)/3-1};

для реализации синхронного счетчика с последовательным переносом требуются логические элементы И-НЕ (ИЛИ-НЕ) с Коб=5, которые отсутствуют в сериях К561(КМОП), К555(ТТЛШ) и др., а также в ячейках базовых матричных кристаллов (БМК), например, К1515ХМ1;

при построении (если не ограничивать Коб) одного разряда синхронного счетчика с последовательным переносом на КМОП логике требуется большое число транзисторов - 34;

счетное устройство не может быть реализовано на типовых триггерах, имеющихся в составе ряда серий ИМС, и библиотечных ячейках БМК.

Известен синхронный счетчик с последовательным переносом, каждый разряд которого содержит Т-триггер (или универсальный JK-триггер) и элемент И. В данном синхронном счетчике с последовательным переносом может быть использован любой Т-триггер (или универсальный JK-триггер), в т.ч. и счетный триггер на четырех логических элементах И-ИЛИ-НЕ с Тmin=4 . tздрср.

Однако данный синхронный счетчик с последовательным переносом имеет следующие недостатки:

несмотря на то, что перенос распространяется через один элемент и данный счетчик имеет низкое быстродействие:

Tmin=(n-2) . tзди+Ттр,

где Тmin - минимальный период следования счетных импульсов;

tзди - задержка элемента И;

Ттр - минимальный период следования импульсов для одного триггера;

поскольку в большинстве серий ИМС отсутствуют элементы И, то потребуется использовать два элемента: И-НЕ и И, тогда

tзди=2 . tздрср;

в тех сериях ИМС, где имеется элемент И tзди ≥ tздрср, так как элемент И является составным (см., например, ИС К155ЛИ1).

Наиболее близким к предлагаемому является счетное устройство, которое содержит L-разрядный счетчик с параллельным переносом и (N-L)-разрядный синхронный счетчик с последовательным переносом, каждый разряд содержит счетный триггер и один логический элемент. Причем счетные разряды имеют по 2-3 СЕ-входа, и могут быть выполнены на базе другого логического элемента и JK-триггера, который выполняется на двух D-триггерах и одном логическом элементе.

Это счетное устройство отличается высоким быстродействием, реализуется на элементах с Коб=3 в большинстве серий ИМС и БМК, но имеет следующие недостатки:

относительно большие аппаратурные затраты;

нереализуемость на логических элементах с Коб=2;

отсутствие выходного сигнала переноса.

Цель изобретения - упрощение и расширение функциональных возможностей счетчика: формирование сигнала переноса и включение дополнительного СЕ-входа.

Для этого в счетчике, содержащем в каждом разряде первый и второй D-триггеры, а каждом разряде, кроме младшего, первый и второй логические элементы, причем синхровход первого D-триггера соединен с синхровходами вторых D-триггеров всех разрядов и с синхровходами первых D-триггеров всех разрядов, кроме первого, а выход первого логического элемента каждого разряда соединен с D-входом второго D-триггера этого разряда, второй выход второго D-триггера младшего и каждого четного разрядов соединен с D-входом первого D-триггера этого разряда, выход второго логического элемента каждого разряда соединен с первым входом второго логического элемента следующего разряда, второй вход второго элемента каждого четного разряда соединен с первым выходом первого D-триггера этого разряда, второй вход второго логического элемента каждого нечетного разряда соединен с вторым выходом первого D-триггера этого разряда, первый выход первого триггера каждого нечетного разряда подключен к соответствующему выходу устройства, а в качестве второго логического элемента в четных и в нечетных разрядах использованы логические элементы И-НЕ и ИЛИ-НЕ соответственно. Выход второго логического элемента каждого разряда соединен с первым входом первого логического элемента этого разряда и с вторым входом первого логического элемента следующего разряда, первый выход второго D-триггера каждого нечетного разряда, кроме младшего, соединен с D-входом первого D-триггера этого разряда, второй вход второго логического элемента каждого разряда соединен с третьим входом первого логического элемента и с первым выходом первого D-триггера этого разряда, второй выход первого триггера каждого нечетного разряда подключен к соответствующему выходу устройства, в качестве первого элемента в нечетных разрядах использован элемент (1-2)И-2ИЛИ-НЕ, а в четных разрядах использован элемент (1-2)ИЛИ-2И-НЕ.

Кроме того, счетчик содержит дополнительно СЕ-вход, первый логический элемент ИЛИ-НЕ, выход которого соединен с синхровходом первого D-триггера младшего разряда, а первый и второй входы логического элемента ИЛИ-НЕ соединены попарно соответственно с синхровходом и входом СЕ.

Кроме того, счетчик содержит дополнительный вход переноса, дополнительный D-триггер и второй логический элемент такого типа как второй логический элемент предпоследнего разряда, причем выход второго логического элемента соединен с D-входом дополнительного D-триггера, первый вход второго логического элемента соединен с выходом второго логического элемента старшего разряда, второй вход логического элемента соединен с дополнительным входом переноса счетчика, а синхровход дополнительного D-триггера соединен с первым входом первого логического элемента ИЛИ-НЕ.

Существенные признаки обеспечивают поставленную цель. Сравнение существенных признаков с прототипом позволило установить их соответствие критерию "Новизна". При этом отличительные признаки не вытекают очевидным образом из современного состояния данного и смежных направлений техники и поэтому соответствуют критерию "Существенные отличия".

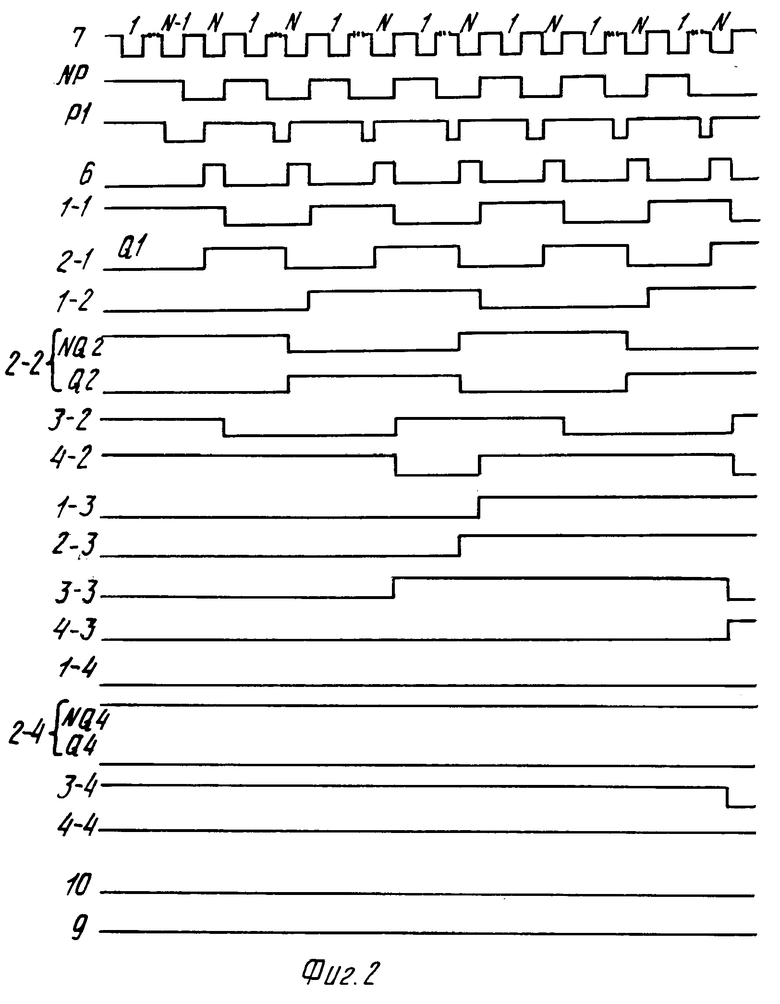

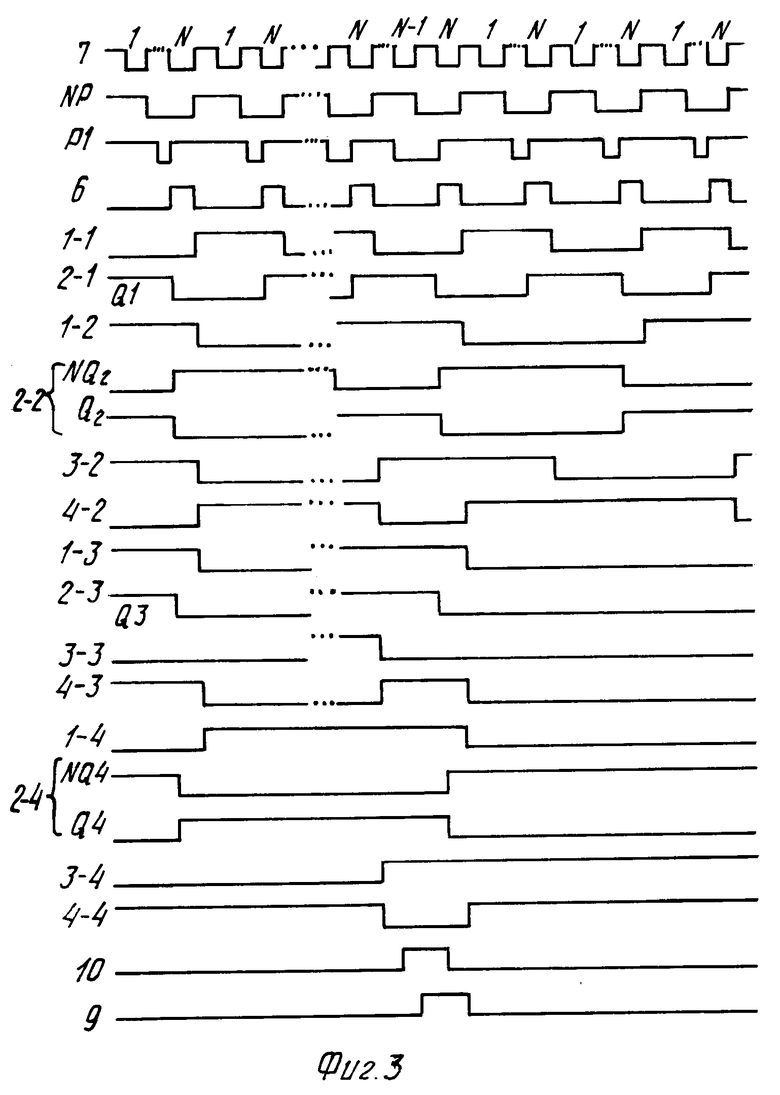

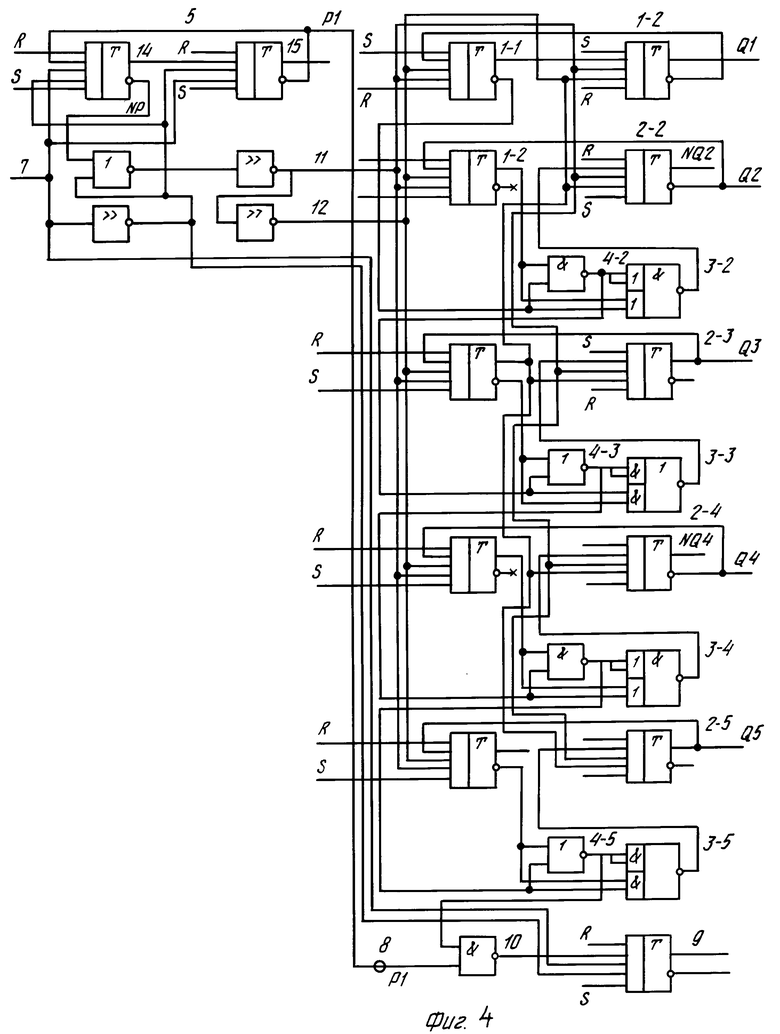

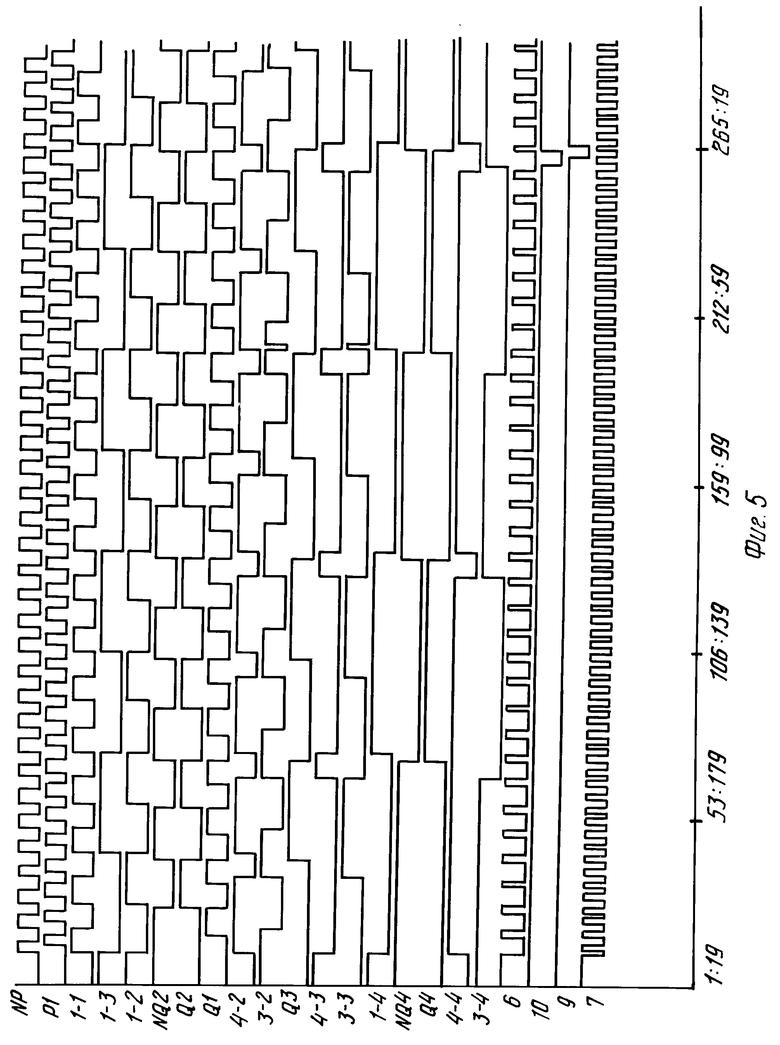

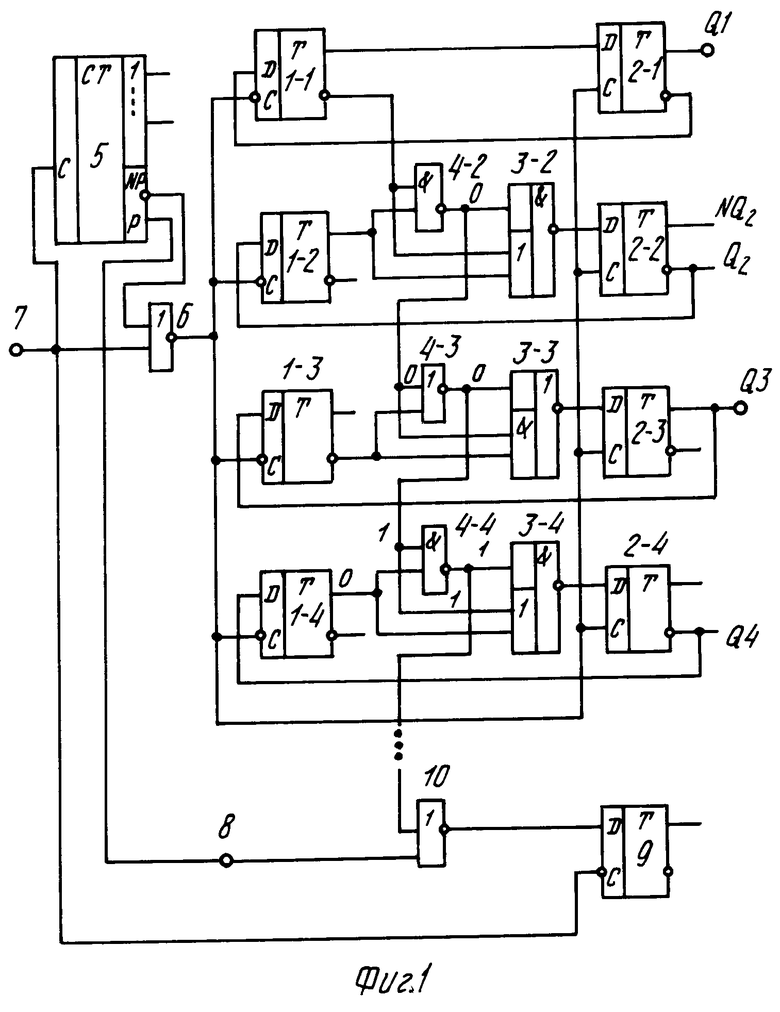

На фиг. 1 изображено счетное устройство, содержащее четырехразрядный предлагаемый счетчик; на фиг.2 - временная диаграмма работы счетного устройства, изображенного на фиг. 1; на фиг.3 - продолжение фиг.2; на фиг.4 - пример реализации на ячейках КМОП БМК К1515ХМ1 пятиразрядного предлагаемого счетчика в составе счетного устройства, где в качестве дополнительного счетчика использован одноразрядный счетчик - T-триггер; на фиг.5 - временная диаграмма работы счетного устройства, изображенного на фиг.3, полученная с помощью САПР РСАD IBM PC/AT.

Счетчик (см. фиг.1) содержит в каждом разряде первый 1-1...1-4 и второй 2-1. ..2-4 D-триггеры, в каждом разряде, кроме младшего, первый 3-2...3-4 и второй 4-2...4-4 логические элементы, синхровод первого D-триггера 1-1 соединен с синхровходами вторых D-триггеров всех разрядов 2-1...2-4 и с синхровходами первых D-триггеров всех разрядов, кроме первого, 1-2...1-4, а выход первого логического элемента 3-2...3-4 каждого разряда соединен с D-входом второго D-триггера 2-2....2-4 этого разряда, второй выход второго D-триггера младшего и каждого четного разрядов 2-1 и 2-4 соединен с D-входом первого D-триггера 1-1 и 1-4 этого разряда, выход второго логического элемента 4-2, 4-3, 4-4 каждого разряда соединен с первым входом второго логического элемента 4-3, 4-3 следующего разряда, второй вход второго элемента 4-2, 4-4 каждого четного разряда соединен с первым выходом первого D-триггера 1-2, 1-4 этого разряда, второй вход второго элемента 4-3 каждого нечетного разряда соединен с вторым выходом первого D-триггера 1-3 этого разряда, первый выход первого D-триггера 1-3 каждого нечетного разряда подключен к соответствующему выходу счетчика, а в качестве второго логического элемента 4-2, 4-4 в четных и 4-3 в нечетных разрядах использованы логические элементы И-НЕ и ИЛИ-НЕ соответственно. Выход второго логического элемента 4-2, 4-3, 4-4 каждого разряда соединен с первым входом первого логического элемента 3-2, 3-3, 3-4 этого разряда и с вторым входом первого логического элемента 3-2, 3-3, 3-4 следующего разряда, первый выход второго D-триггера 2-3 каждого нечетного разряда, кроме младшего, соединен с D-входом первого D-триггера 2-3 этого разряда, второй вход второго логического элемента 4-2, 4-3, 4-4 каждого разряда соединен с третьим входом первого логического элемента 3-2, 3-3, 3-4 и с первым выходом первого D-триггера 1-2, 1-3, 1-4 этого разряда, второй выход первого D-триггера 1-3 каждого четного разряда подключен к соответствующему выходу счетчика, в качестве первого элемента 3-3 в нечетных разрядах использован элемент (1-2)И-2ИЛИ-НЕ, а в четных разрядах 3-2, 3-4 использован элемент (1-2)ИЛИ-2И-НЕ.

Для анализа работы предлагаемого счетчика в составе счетного устройства на фиг. 1 также показан счетчик 5. Кроме того, счетчик содержит первый логический элемент ИЛИ-НЕ 6, выход которого соединен с синхровходом первого D-триггера 1-1 младшего разряда, а первый и второй входы логического элемента ИЛИ-НЕ 6 соединены попарно соответственно с синхровходом 7 и входом СЕ счетчика. Вход СЕ подключен к выходу переноса счетчика 5.

Кроме того, счетчик содержит дополнительный вход переноса В, дополнительный D-триггер 9 и второй логический элемент 10 такого типа, как второй логический элемент 4-3 предпоследнего разряда. Причем выход второго логического элемента 10 соединен с D-входом дополнительного D-триггера 9, первый вход логического элемента 10 соединен с выходом второго логического элемента 4-4 старшего разряда, а второй вход логического элемента 10 соединен с дополнительным входом переноса 8 счетчика, а синхровход дополнительного D-триггера 9 соединен с первым входом первого логического элемента ИЛИ-НЕ 6, Дополнительный вход переноса 8 счетчика соединен в счетном устройстве с дополнительным выходом переноса счетчика 5.

Функционирование счетного устройства (фиг.1) из начального состояния лог.0 на выходах разрядов (установка начального состояния описана в примере на фиг. 4) поясняется временной диаграммой (фиг.2 и 3), на которой для D-триггеров приведены сигналы на их первых выходах, а для вторых D-триггеров четных разрядов 2-2, 2-4 приведены сигналы на обоих выходах. Импульсы на входе 7 пронумерованы по модулю N- где N - коэффициент пересчета счетчика 5. Из-за ограниченных размеров временной диаграммы (фиг.2) на ней не показаны задержки элементов и все переключения сигналов, вызванные фронтом (срезом) импульса на входе 7, изображены как действующие одновременно с этим же фронтом (срезом). Сигналы на выходах переноса счетчика 5: основной NP и дополнительный Р1 изменяются соответственно по фронту и срезу импульса на синхровходе 7. По фронту (срезу) импульса на синхровходе первого D-триггера 1-1 (он же на выходе элемента 6) переключаются первые (вторые) D-триггера 1-1, 1-2, 1-3, 1-4, (2-1, 2-3, 2-4).

Для достоверной работы счетчика должно выполняться условие:

N.T-tп ≥ Ттр + К . tздрср,

где Т - период следования синхроимпульсов на входе 7;

tп - длительность паузы синхроимпульсов на входе 7;

К - число разрядов предложенного счетчика (К=4 для счетчика на фиг.1).

В случае, если скважность синхроимпульсов на входе 7 равна 2 и Ттр= 3tздср, то:

(N-0,5) .T ≥ (K + 3) . tздрср.

Учитывая, что при построении счетчика 5 на таких же триггерах собственное быстродействие ограничено условием Т ≥ 6tздрср, получим: (N-0,5) .6.tздрср ≥ (K+3) .tздрср.

Отсюда следует неравенство: 6 . (N-1) ≥K, при выполнении которого сохраняется предельное быстродействие счетного устройства. Для предельного быстродействия при К ≅5N ≥2, следовательно, в качестве счетчика 5 достаточно использовать Т-триггер (см. пример фиг.4).

В свою очередь счетчик 5 может быть реализован как декомпозиция в соответствии с п.п. 2 и 3 формулы. Для этого служат элементы 6, 10 и триггер 9. На временной диаграмме (фиг.2) приведены сигналы на этих выходах и дополнительном выходе переноса Р1 счетчика 5. Сигнал на дополнительном выходе переноса Р1 счетчика 5 имеет активный уровень лог. 0 (1) для четных (нечетных) значений К и опережает сигнал переноса NP на полпериода импульсов по входу 7. Из-за нелинейного масштаба по оси времени (оси импульсов по входу 7) на временной диаграмме фиг. 2 искажена длительность активного уровня сигнала на дополнительном выходе переноса Р1.

При построении многоразрядного счетного устройства предельного быстродействия можно использовать Т-триггер и предлагаемый пятиразрядный счетчик по п.п.2 и 3 в качестве счетчика 5 в составе счетного устройства, содержащего предлагаемый К-разрядный счетчик: по п.1 формулы. В этом случае N=32 и значение К должно удовлетворять неравенству К ≅120 (31, 5.6-3=120).

Таким образом, изобретение позволяет строить на двувходовых логических элементах многоразрядные счетные устройства предельного быстродействия с общей разрядностью 126. Кроме того, по сравнению с прототипом предлагаемый счетчик обеспечивает экономию одного логического элемента в каждом разряде.

На фиг. 4 изображен пример реализации на ячейках КМОП БМК К1515ХМ1 пятиразрядного счетчика по изобретению в составе счетного устройства, где в качестве дополнительного счетчика использован один Т-триггер. Все D-триггеры (v2v4) имеют по два синхровхода С и NC. Кроме того, в отличии от счетного устройства (фиг. 1) счетное устройство (фиг.4) содержит инверторы (w3) 11-13. В качестве логического элемента (1-2)И-2ИЛИ-НЕ использован элемент (2-2)И-2ИЛИ-НЕ - ячейка w15, а в качестве логического элемента (1-2)ИЛИ-2ЛИ-2И-НЕ использован элемент (2-2)ИЛИ-2И-НЕ - ячейка w14. Счетчик 5 здесь выполнен как одноразрядный Т-триггер, который в свою очередь построен на двух D-триггерах 14 и 15. Кроме того, счетное устройство на входе S=0, а по входу R в начале подается импульс установки.

На фиг.5 приведена временная диаграмма работы счетного устройства (фиг. 4), полученная с помощью САПР РСАD IBM PC/AT. Эта диаграмма учитывает задержки элементов и поэтому на ней видны некритичные логические состязания (в комбинационной схеме) на выходах элементов 3-2, 3-3. Эти состязания не приводят к сбоям элементов памяти при условии выполнения введенных выше ограничений по быстродействию.

Таким образом, предлагаемый счетчик упрощен по сравнению с прототипом и может быть реализован на двувходовых логических элементах, кроме того, он обеспечивает расширение функциональных возможностей по дополнительным СЕ-входам выходу переноса. Изобретение позволяет строить многоразрядные счетные устройства предельного быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетное устройство | 1988 |

|

SU1529445A1 |

| 2К-разрядный счетчик в коде Грея | 1990 |

|

SU1707761A1 |

| Счетное устройство | 1980 |

|

SU953741A1 |

| Счетчик с последовательным переносом | 1985 |

|

SU1269257A1 |

| Реверсивный счетчик | 1979 |

|

SU824449A1 |

| Реверсивный счетчик | 1982 |

|

SU1066039A2 |

| Счетчик с последовательным переносом информации | 1977 |

|

SU782163A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Синхронный счетчик | 1985 |

|

SU1257838A1 |

| Счетчик в коде либау-крейга | 1977 |

|

SU660264A1 |

Изобретение касается импульсной техники и может быть использовано при построении узлов цифровой техники и дискретной автоматики на логических элементах (преимущественно КМОП). Счетчик содержит логический элемент ИЛИ - НЕ 6, дополнительный D-триггер 9, логический элемент 10, в каждом разряде два D-триггера 1,1-1,4, 2.1-2.4, в каждом разряде кроме младшего два логических элемента 3.2-3.4, 4.2-4.4. 2 з.п.ф-лы, 5 ил.

| Счетное устройство | 1988 |

|

SU1529445A1 |

Авторы

Даты

1995-01-27—Публикация

1991-11-21—Подача