Изобретение относится к цифровой вычислительной технике, преимущественно на интегральных логических элементах, выполненных, например, по КМОП - технологии.

В цифровых устройствах широко применяются в коде Грея (рефлексном, соседнем), которые могут использоваться в преобразователях, так как при воздействии счетного импульса с недостаточной длительностью ошибка не превысит инкремента счета 1. Кроме того, соседнее кодирование обеспечивает снижение динамической составляющей потребляемой мощности.

Известен n-рззрядный счетчик в коде Грея, содержащий (п + 1) TV (УК) триггеров. Это устройство имеет следующие недостатки: неоднородность структуры. Число V(l, К) входов линейно растет до значения п; большие аппаратурные затраты. Так при использовании КМОП-технологии для построения одного IK-триггера требуется 30 транзисторов, на входную логику затрачен (п-1) логический элемент с суммарным числом

л(п+ 1)

входов, - -г--1

чем п (п+1) - 4 КМОП транзисторов. Общее число транзисторов составляет п + 31п - 4; низкое быстродействие в делительном режиме, связанное дополнительными задержками во входной логике IK-триггеров, которые зависят от разрядности.

Наиболее близким к предложенному является n-разрядный счетчик в коде Грея, со . что требует не менее,

XJ

О

XJ XI

О

держащий (2п-1) Т-триггеров, в качестве каждого из которых можно использовать D- триггер, второй выход которого соединен с его информационным входом, Это устройство обладает однородностью и регулярно- стью, хорошо реализуется на однотипных КМОП ИМС (например, К561ТМ2). Обладает высоким быстродействием в делительном режиме, однако имеет следующие недостатки: большие аппаратурные затраты (число D-триггеров (2п-1); низкое быстродействие в управляющем режиме, характеризуемое задержкой nD-триггеров.

Цель изобретения - упрощение и повышение быстродействия в управляющем ре- жиме.

Цель достигается тем, что в 2К-разряд- ном счетчике в коде Грея, содержащем вх од, 2К выходов, где К 1,2....,(ЗК-1) триггеров, причем вход счетчика соединен с синхров- ходом первого триггера, первый выход каждого 2Р-го, где Р 1, 2,...,(К-1) триггера соединен с синхровходом (2К-|-1)-го триггера, второй выход каждого 2Р-го триггера соединен с синхроеходом (2Р+1)-го тригге- ра, первый и второй выходы каждого (2К+ + Р)-го триггера соединены попарно соответственно с 2Р-м выходом счетчика и информационным входом (2Р+Р)-го триггера, а первый выход 2К-го триггера соеди- нен с 2К-выходом счетчика, синхровход каждого (2Р-1)-го триггера соединен с синхровходом 2Р-го триггера, синхровход (2К-1)-го триггера соединен с синхровходом 2К-го триггера, первый выход каждого (2Р-1)-го триггера соединен с (2Р-1)-м выходом счетчика и с первым информационным входом 2Р-го триггера, первый выход (2К-1)- го триггера соединен с (2К-1)-м выходом счетчика и информационным входом 2К-го триггера, второй выход которого соединен с информационным входом (2К-1)-го триггера, второй выход каждого 2Р-го триггера соединен с информационным входом (2Р-1)- го триггера.,

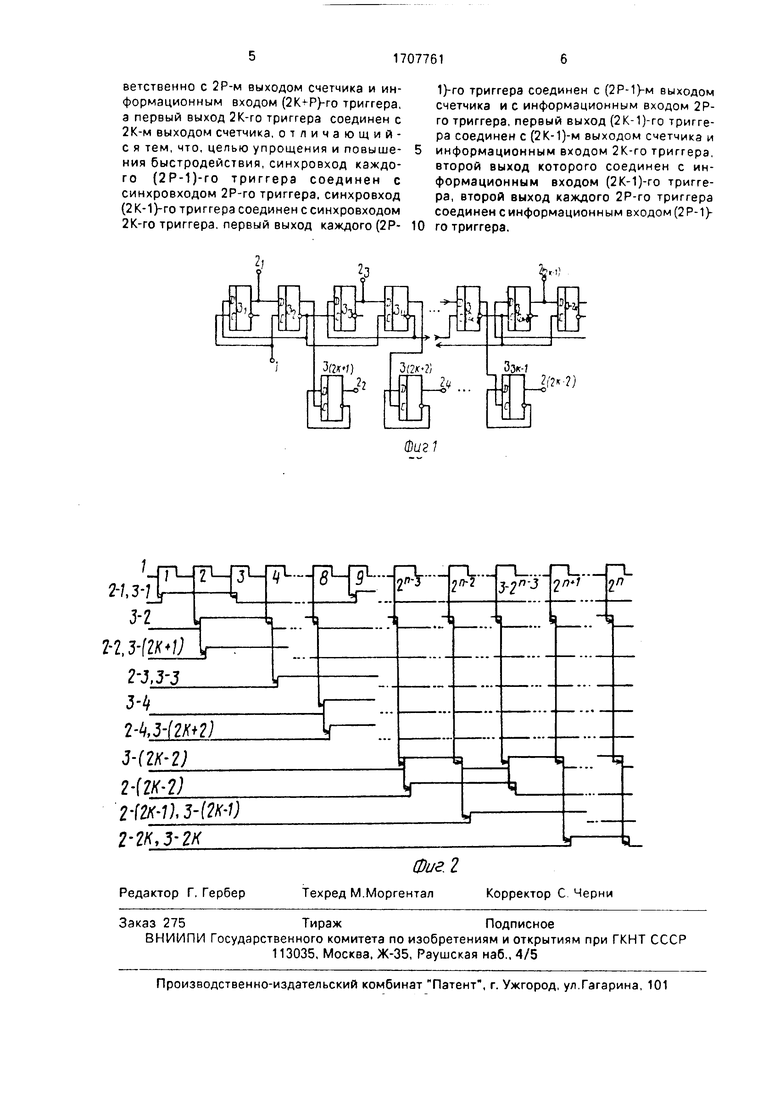

На фиг.1 изображен предлагаемый счетчик; на фиг.2 - временная диаграмма работы счетчика.

Счетчик содержит вход 1, 2К выходов (К 1. 2,..). 2-1. 2-2. 2-3. 2-4, .... 2-(2К-2).

2-{2К-1), 2-2К. (ЗК-1)триггеровЗ-1....,3-(ЗК-1): причем вход 1 счетчика соединен с синхровходом первого триггера 3-1, первый выход каждого 2Р-го, где Р 1, 2...,(К-1) триггера

3-Р соединен с синхровходом (2К+Р)-го триггера. 3-(2ЮР) второй выход каждого 2р- го триггера 3-2Р соединен синхровходом (2Р+1)-го триггера 3-(2Р+1) первый и второй выходы каждого ()-го триггера ЗЧ2К+Р) соединены попарно соответственно с 2Р-м

выходом счетчика 2-2Р и информационным входом (2К+Р)-го триггера ЗЧ2К+Р).

Первый выход 2К-го триггера 3-2К соединен с 2К-м выходом счетчика 2-2К. Синхровход каждого (2Р-1)-го триггера 3-(2Р-1) соединен с синхровходом 2Р-го триггера 3- 2Р. Синхровход (2К-1)-го триггера 3-(2К-1) соединен с синхровходом 2К-го триггера 3-2К, первый выход каждого (2Р-1)-го триггера 3-(2Р-1) соединен с (2Р-1)-м выходом счетчика 2-{2Р-1) и с информационным входом 2Р-го триггера 3-2Р, первый выход (2К-1)-го триггера 3-(2К-1) соединен с (2К-1 м выходом счетчика 2-(2К-1) и первым информационным входом 2К-го триггера 3-2К, второй выход которого соединен с информационным входом (2К-1)-го триггера 3-(2К-1) второй выход каждого 2Р-го триггера 3-2Р соединен с информационным входом (2Р-1)-го триггера 3-(2Р-1).

Функционирование счетчика поясняется временной диаграммой (фиг.2). Пусть в исходном состоянии все триггера 3-1...,3- (ЗК-1) установлены в состояние логического нуля. Установочные R-входы на фиг.1 не показаны, но могут быть при необходимости введены в счетчик. Каждый триггер 3-1 .....3-(ЗК-1) переключается по фронту импульса на его синхровходе. На диаграмме показан сигнал на входе 1, состоящий из импульсов: 1, 2, 3, 4,...,8, 9 ..... 2П Г ....3-2П 3.....2П 1.....2П. (п - 2К). Приведены осциллограммы выходов счетчика и первых выходов всех триггеров (фиг.1).

Таким образом, предложенный 2К-рэз- рядный счетчик содержит (ЗК-1) D-тригге- ров что на К ( на 25%) меньше, чем в известном. В управляющем режиме работы минимальный период следования импульсов по входу 1 определяется задержкой ()-го триггера, что в два раза меньше, чем у известного. Предложенный счетчик обладает более высоким быстродействием в де- лительном режиме, характеризуется регулярностью структуры, что при построении на библиотечных элементах КМОП БИС обеспечивает меньшие аппаратурные затраты.

Формула изобретения 2К-разрядный счетчик в коде Грея, содержащий вход. 2К выходов, где К 1, 2...,(ЗК-1)триггеров, вход счетчика соединен с синхровходом первого триггера, первый выход каждого 2Р-го, где Р 1. 2....(К-1)-го триггера соединен с синхровходом (2 К+Р)-го триггера, второй выход каждого 2Р-го триггера соединен с синхровходом (2Р-И)-го триггера, первый и второй выходы каждого (2К+Р)-го триггера соединены попарно соответственно с 2Р-м выходом счетчика и информационным входом (2К-Ф}-го триггера, а первый выход 2К-го триггера соединен с 2К-м выходом счетчика, отличающий- с я тем, что, целью упрощения и повышения быстродействия, синхровход каждого (2Р-1)-го триггера соединен с синхровходом 2Р-го триггера, синхровход (2К-1)-го триггера соединен с синхровходом 2К-го триггера, первый выход каждого (2Р

1}-го триггера соединен с (2Р-1}-м выходом счетчика и с информационным входом 2Р- го триггера, первый выход (2К-1)-го триггера соединен с (2К-1)-м выходом счетчика и информационным входом 2К-го триггера, второй выход которого соединен с информационным входом (2К-1)-го триггера, второй выход каждого 2Р-го триггера соединен с информационным входом (2Р-1)- го триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| (2К+1)-разрядный счетчик в коде Грея | 1990 |

|

SU1725391A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для выборки блоков памяти | 1990 |

|

SU1737457A1 |

| Счетчик в коде Грея | 1984 |

|

SU1202050A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Устройство формирования счетных импульсов многоканального счетчика | 1984 |

|

SU1164879A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для перебора сочетаний | 1986 |

|

SU1374243A1 |

| Счетчик | 2017 |

|

RU2698431C2 |

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для съема в коде Грея. Цель изобретения - упрощение и повышение быстродействия счетчика на четное число разрядов. Счетчик содержит (ЗК - 1) триггеров 3-1 - З+зк-1. синхровход каждого (2Р-1)-го триггера соединен с синхровходом 2Р-го триггера, синхровход (2К - 1)-го триггера соединен с синхровходом 2К-го триггера, первый выход каждого (2Р-1)-го триггера соединен с (2Р-1)-м выходом счетчика и с первым информационным входом 2Р-го триггера, первый выход (2К-1)-го триггера соединен с (2К-1)-м выходом счетчика и информационным входом 2К-го триггера, второй выход которого соединен с информационным входом (2К-1)-го триггера, второй выход каждого 2Р-го триггера соединен с информационным входом (2Р-1)-го триггера. 2 ил. СП С

2;

2J

«)

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| Изд | |||

| - М.: Советское радио, 1975, с.305 - 306 | |||

| Проектирование микроэлектронных цифровых устройств | |||

| - М.: Советское радио, 1977 | |||

| Паровоз с приспособлением для автоматического регулирования подвода и распределения топлива в его топке | 1919 |

|

SU272A1 |

| СПОСОБ КРЕПЛЕНИЯ СЪЕМНЫХ ДНИЩ ПОРШНЯ | 1924 |

|

SU3562A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

Авторы

Даты

1992-01-23—Публикация

1990-03-19—Подача