Изобретение относится к измерению времени и может быть использовано для создания аудио-часов, а также различного рода приборов, в которых может присутствовать как одна из функций - аудио-индикация времени, как абсолютного, так и относительного. К таким приборам могут быть отнесены радиоприемники, электронные игры, электронные термометры и т.д.

Известны говорящие часы [1], состоящие из процессоров, ПЗУ1, ПЗУ2, ОЗУ, динамика, коммутатора ввода - вывода, устройства декодирующего, цифроаналогового преобразователя, дисплея, коммутационной группы (набора клавиш, обеспечивающие, кроме цифровой, дополнительную аудиоиндикацию времени и календаря).

Недостатком данного устройства является использование высокопроизводительного процессора для решения задач счета времени, опроса коммутационной группы и управлением аудио-выходом, а также затраты оборудования на ОЗУ и дополнительно ПЗУ.

Известно также говорящее устройство времени [2], состоящее из устройства управления (однокристального микропроцессора), часовой схемы синтеза цепи (цифроаналогового преобразователя), устройства, усиливающего звук, дисплея, коммутационной группы (переключателей различного типа) динамика, ПЗУ.

Функционирование прибора строится на совместном функционировании двух вычислителей, объединяющего одни и те же коммутационные группы.

Цель изобретения - уменьшение оборудования и снижение стоимости изделия.

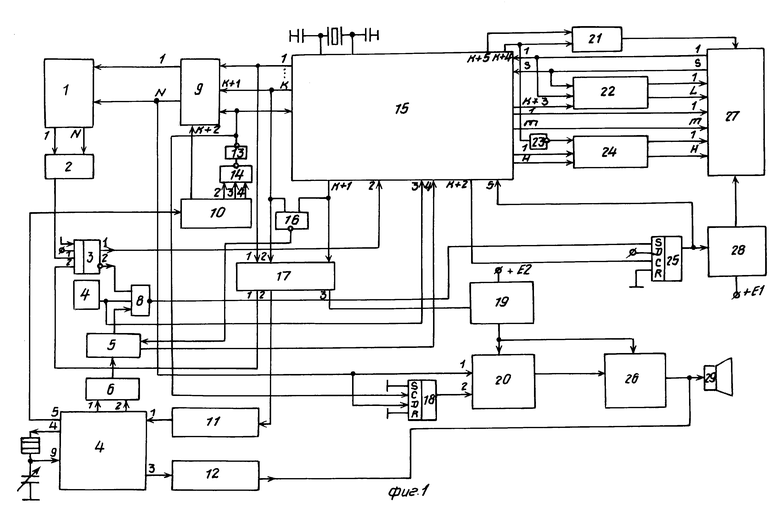

Это достигается тем, что в устройство, состоящее из коммутационной группы, двух диодных сборок, часовой схемы, схемы начальной установки, двух преобразователей уровня, однокристального микропроцессора, буферного регистра, двух регистров адреса, схемы ИЛИ, инвертора, полупостоянного запоминающего устройства (ПЗУ), цифроаналогового преобразователя, формирователя звукового сигнала, динамика, так, что выходы коммутационной группы соединены со входами первой диодной сборки, первый и второй выходы часовой схемы подключены к входам второй диодной сборки, третий выход часовой схемы соединен с входом второго преобразователя уровня; с первого по К-ый выходы микропроцессора соединены соответственно с первого по К-ый входами буферного регистра, второй выход которого подключен к выходу первого преобразователя уровня, выход которого соединен с первым входом часовой схемы, выход схемы начальной установки подключен к третьему входу микропроцессора, К+5-ый выход которого соединен с первым входом схемы ИЛИ, второй вход которой соединен с К+4-ым выходом микропроцессора и входом инвертора, а выход подключен к первому входу полупостоянного запоминающего устройства, S-выходов которого соединены с S-входами микропроцессора и S-входами первого регистра адреса, (К+3)-ый выход микропроцессора подключен к (S+1)-входу первого регистра адреса, выходы которого соединены с L-входами полупостоянного запоминающего устройства, М-входы которого подключены к М-выходам микропроцессора. Выход инвертора соединен с первым входом второго регистра адреса, последующие входы которого подключены к Н-выходам микропроцессора, а выходы - к Н-выходам ППЗУ, выход цифроаналогового преобразователя соединен с вторым входом формирователя звукового сигнала, первый вход которого соединен с третьим входом цифроаналогового преобразователя, а выход подключен к входу динамика и выходу второго преобразователя уровня.

В устройство дополнительно введены регистр сдвига, счетчик, три триггера, двухвходовая схема ИЛИ-НЕ, две трехвходовые схемы И-НЕ, второй инвертор, узел формирования интервала времени, два ключа, причем N-входов коммутационной группы подключены к N-выходам регистра сдвига, N-ый выход которого соединен с первым входом цифроаналогового преобразователя и D-входом второго триггера, выход которого подключен к второму входу ЦАПа, выход первой диодной сборки соединен с С-входом первого триггера, R-вход которого подключен к первому выходу буферного регистра. Прямой выход триггера соединен с вторым входом микропроцессора, а инверсный выход - с первым входом первой трехвходовой схемы И-НЕ, второй вход которой соединен с выходом схемы начальной установки, а третий - с первым выходом узла формирования интервала времени, второй выход которого подключен к четвертому входу микропроцессора, а первый вход - к выходу второй диодной сборки. Пятый выход часовой схемы соединен с входом счетчика, первый выход которого подключен к К+2-ому входу регистра сдвига, второй, третий и четвертый выходы счетчика соединены с первым, вторым и третьим входами второй трехвходовой схемы И-НЕ, выход которой подключен к входу первого инвертора, выход которой соединен с первым входом микропроцессора, с (К+1)-ым входом регистра сдвига и С-входом второго триггера. Выход первый трехвходовой схемы И-НЕ подключен к S-входу третьего триггера, С-вход которого соединен с (К+2)-м выходом микропроцессора, а выход - с пятым входом микропроцессора и первым входом второго ключа, выход которого соединен с входом питания ППЗУ, К-ый выход микропроцессора подключен к первому входу схемы ИЛИ-НЕ, второй вход которой соединен с (К+1)-м выходом микропроцессора, а выход которой подключен к второму входу узла формирования интервала времени, первый вход первого ключа соединен с третьим выходом буферного регистра, а первый выход подключен к третьему входу ЦАПа.

Новым по сравнению с прототипом является то, что в устройство введены регистр сдвига, счетчик, три триггера, двухвходовая схема ИЛИ-НЕ, две трехвходовые схемы И-НЕ, инвертор, узел формирования интервала времени, два ключа с соответствующей совокупностью связей.

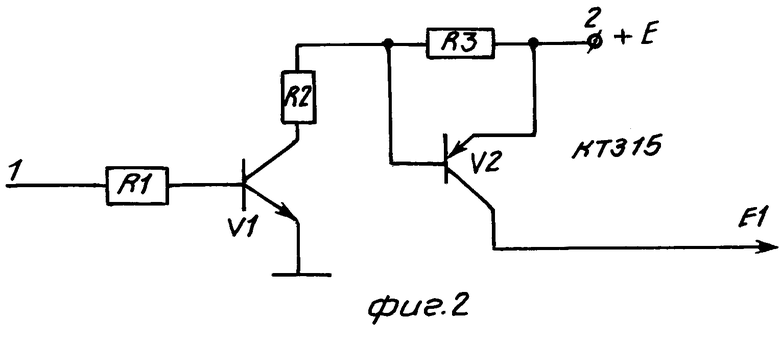

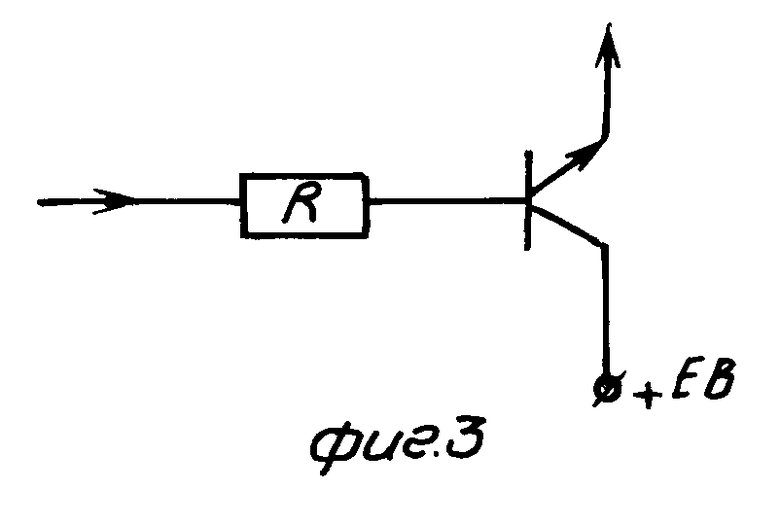

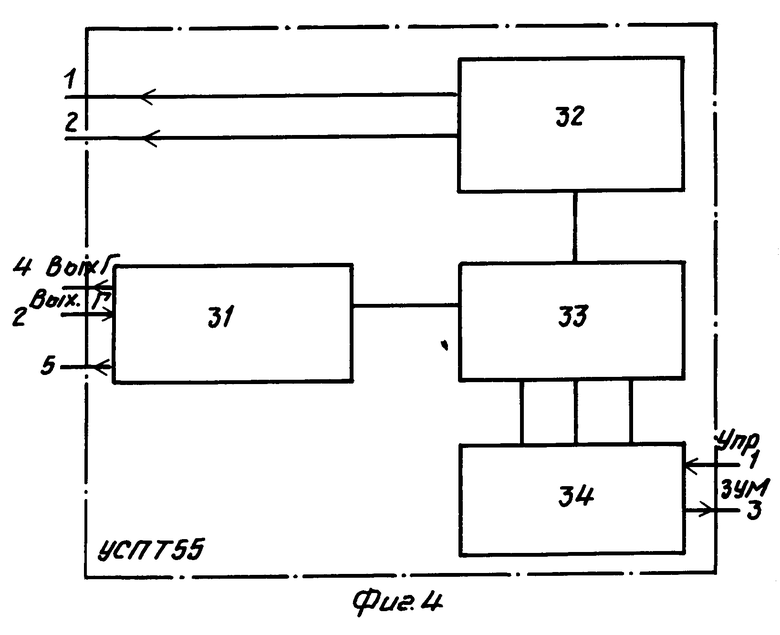

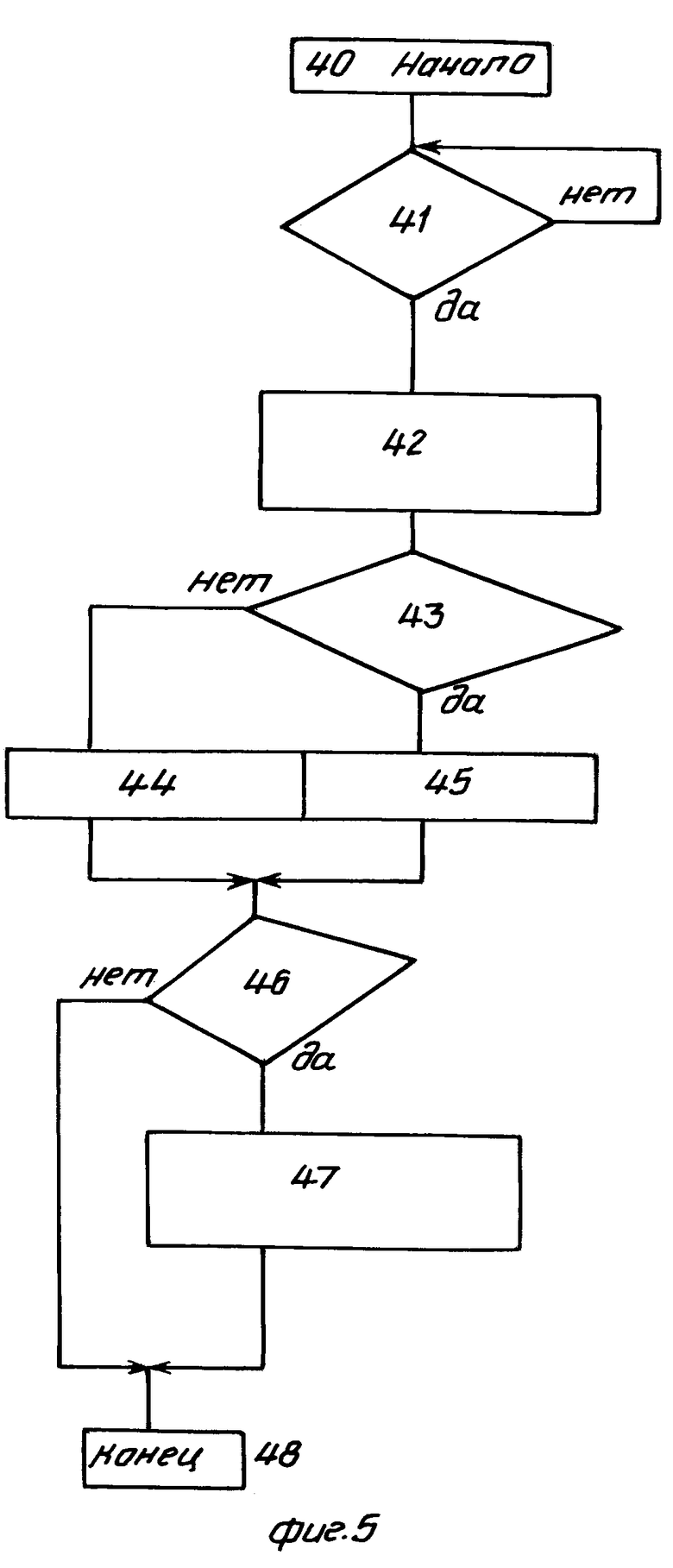

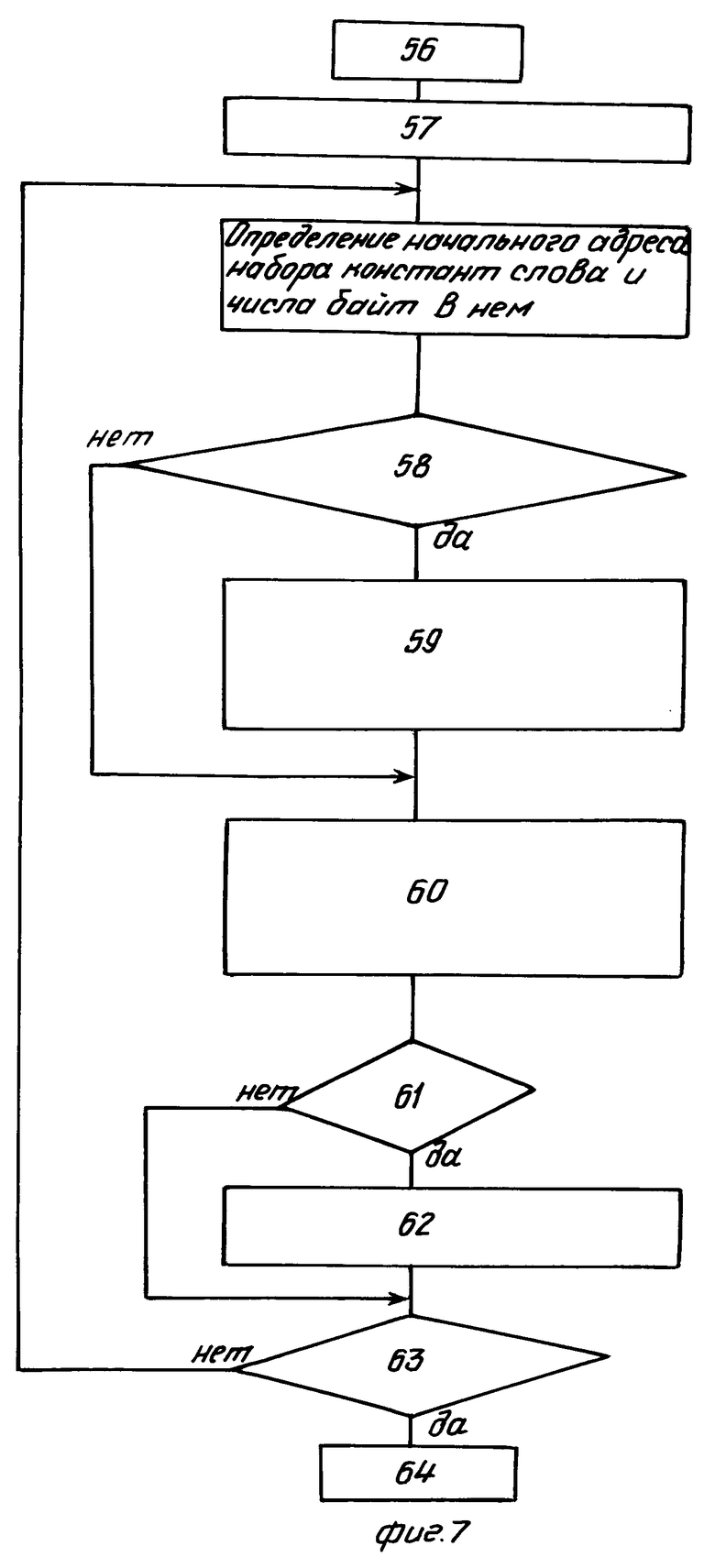

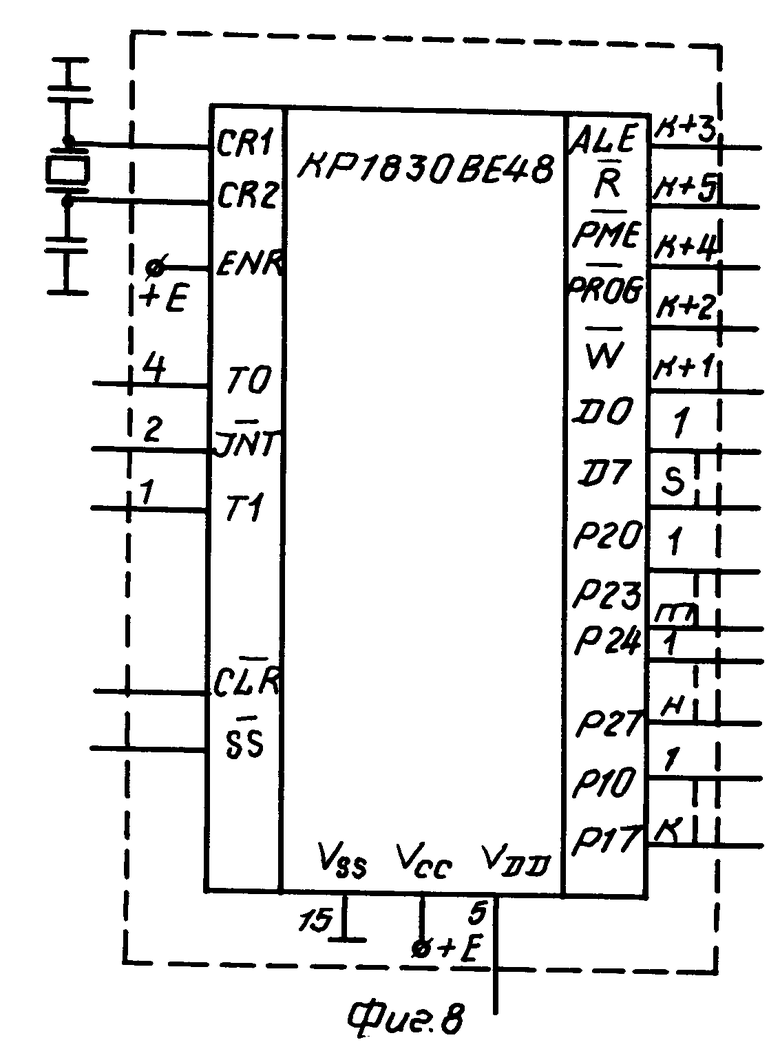

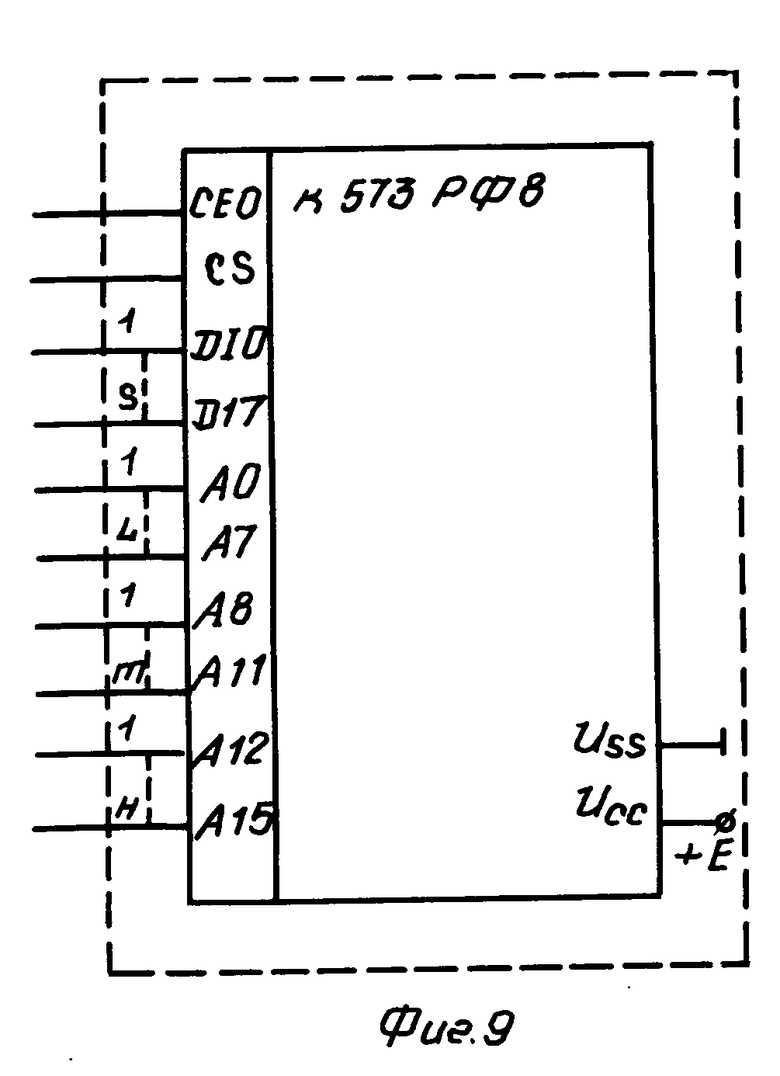

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - конкретная реализация ключа; на фиг. 3 - схема преобразователя уровня; на фиг. 4 - пример конкретной реализации часовой схемы; на фиг. 5 - алгоритм счета времени; на фиг. 6 - алгоритм реакции на сигнал коммутационной группы; на фиг. 7 - алгоритм речевого оповещения; на фиг. 8 - пример конкретной реализации однокристального микропроцессора; на фиг. 9 - пример конкретной реализации полупостоянного запоминающего устройства.

Устройство содержит коммутационную группу 1, диодные сборки 2 и 6, триггеры 3, 18, 25, схему 4 начальной установки, узел 5 формирования интервала времени, часовую схему 7; трехвходовые схемы И-НЕ 8, 14, регистр 9 сдвига, счетчик 10, преобразователи уровня 11, 12, инверторы 13, 23, однокристальный микропроцессор 15, схему ИЛИ-НЕ 16, буферный регистр 17, ключи 19, 28, ЦАП 20, схему ИЛИ 21, регистры адреса 22, 24, формирователь 26 звукового сигнала, ППЗУ 27, динамик 29.

Работа электронных часов с речевым оповещением построена на следующих технических принципах.

Реализация основных алгоритмов осуществляется однокристальным микропроцессором 15 с ограниченной внутренней памятью и программой, хранимой в полупостоянном запоминающем устройстве 27 (ППЗУ).

Индикация работы однокристального микропроцессора 15 производится либо сигналом счета времени, либо сигналами коммутационной группы 1.

Обеспечение "хода" осуществляется часовой схемой 7, работающей от кварцевого генератора с частотой 32 кГц.

Речевое оповещение происходит при синхронной работе однокристального микропроцессора 15, побайтно выбирающего речевые контакты из ПЗУ 27 и далее побайтно считываемые из специального сдвигового регистра 9, синхронизируемого от часовой схемы 7.

Однокристальный микропроцессор 15 и ППЗУ 27 отключается от источников питания в паузах между обработкой сигналов счета временных и сигналов коммутационной группы 1.

Условно работу электронных часов с речевым оповещением можно представить в виде трех режимов: счета времени, режим реакции на сигналы коммутационной группы, режим речевого оповещения.

В первых двух режимах устройство находится постоянно, циклически реагируя на сигналы счета времени, поступающие от часовой схемы 7, через диодную сборку 6 и узел 5 формирования интервалов времени. Сигналы с коммутационной группы 1, возникающие при нажатии кнопок или клавиши, также вызывают цепь управляющих действий однокристального микропроцессора 15.

На фиг. 5-7 представлены укрупненные алгоритмы функционирования устройства в каждом из режимов отдельно. Полный алгоритм работы устройства является сочетанием выполнения представленных алгоритмов в их взаимосвязи.

Работа электронных часов с речевым оповещением в режиме счета времени осуществляется в постоянной циклической выработке часовой схемы 7 сигналов счета времени, которые поступают с частотой 2 Гц через диодную сборку 6 на узел формирования интервала времени. В конкретной реализации узел 5 может быть счетным триггером на 2, в этом случае интервал счета времени будет равен 1 с.

Сигнал с узла 5 через трехвходовую схему И-НЕ 8 воздействует на триггер 25, который позволяет через ключ 28 подать питание на ППЗУ 27. Одновременно сигнал с триггера 25, поступая на вход 5 однокристального микропроцессора 15, приводит его из режима микропотребления в режим реализации микропрограммы. Микропроцессор 15 производит модификацию счетчиков времени, находящихся в его памяти. Счетчики содержат временные реквизиты секунд, минут, часов, дней недели, месяца, числа, интервала будильника, таймера и т.д. При достижении счетчиками будильника заданной уставки "побудки" однокристальной микропроцессор воздействует через выходы "К" на входы будущего регистра 17, а через выход 2 буферного регистра 17 и преобразователя уровня 11 - на часовую схему 7, которая через преобразователь уровня 12 выдает сигнал зуммера на динамик 29. При этом звучит зуммер, оповещая о срабатывании будильника.

Возможна выдача сигналов "побудки" речевыми звуками, что будет описано в режиме речевого оповещения.

Режим счета времени является наиболее приоритетным режимом. Он не может быть прерван другими режимами, так как нельзя "потерять" сигнал счета времени, что может привести к потери точности "хода" часов. Алгоритм функционирования часов с речевым оповещением организуется таким образом, что сигнал счета времени не может быть "потерян".

Сигналы коммутационной группы 1 генерируются при нажатии пользователем часов кнопок, клавиш, переключателей или любых других органов управления при необходимости вызвать индикацию времени, либо ввести корректировку времени, либо при желании прервать речевое оповещение. При появлении любого из N сигналов коммутационной группы 1 устройство переходит в режим реализации на сигналы коммутационной группы. Любой из N сигналов коммутационной группы 1 через диодную сборку 2 запоминается на триггере 3 и с выхода 2 триггера 3 через трехвходовую схему 8 И-НЕ включает питание на ППЗУ 27, а также переводит однокристальный микропроцессор 15 из режима микропотребления в режим работы. Микропроцессор 15 выполняет при этом микропрограмму анализа сигналов путем пересылки по К шинам кода в сдвиговой регистр 9.

Меняя код в регистре 9, микропроцессор 15 определяет какой именно сигнал коммутационной группы поступил и в зависимости от этого определяет алгоритм последующих действий. Действия могут заключаться либо в переходе в режим речевого оповещения текущего времени, календаря, даты, либо в прерывании выдачи речевого сообщения, либо в отработке алгоритмов корректировки любого из временных реквизитов. Выполнение любого из действий, вызванных реакцией на сигналы коммутационной группы 1, прерываются на обработку алгоритмов счета времени.

Можно определить так: режим счета времени будет вписываться в режим реакции на сигналы коммутационной группы. Наличие триггера 3, а также расчет циклов работы микропроцессора 15 в каждом из режимов позволяет синхронизировать работу устройства в обоих режимах одновременно.

В режим речевого оповещения устройство может перейти либо при достижении уставки в процессе счета времени, либо при нажатии кнопки (клавиши) пользователем часов. Речевое оповещение заключается в выполнении однокристальным микропроцессором 15 микропрограммы побайтного считывания речевых констант из ППЗУ 27 с шины S сменной адреса на регистрах 22, 24 и шинах "1...М", под действием управляющих сигналов с выходов через двухпроводную (двухвходную) схему ИЛИ 21, воздействующих на вход 1 ППЗУ 27 и 3 выхода однокристального микропроцессора 15, воздействующего на вход регистра 22 адреса.

Для обеспечения звучания микропроцессора 15 заносит по шинам К код в буферный регистр 17, на выходе 3 появляется сигнал, включающий через ключ 19 питание на ЦАП 20 и формирователь усилитель 26 однокристальный процессор 15 формирует "порцию" (слово или слог) речевого сообщения длительностью не больше интервала времени счета (например, 1 с) путем указания начального адреса и количества байт в речевой "порции".

Необходимость выдачи речевых сообщений "порциями" диктуются требованием не "потерять" сигнал счета времени, который в период выдачи речевой "порции" сохраняется в узле 5 формирования интервала времени. Каждый байт речевой константы по шинам "К" поступает из микропроцессора 15 в регистр сдвига 9. Счетчик 10 под действием сигналов с частотой 32 кГц, поступающей на его вход с выхода 3 часовой схемы 7, обеспечивает побитный сдвиг речевых констант через триггер 18 в ЦАП 20 и даже через формирователь звукового сигнала 26 на динамик 29.

По окончании выдачи последнего бита текущего байта на выходе трехвходовой схемы И-НЕ 14 и инвертора 13 формируется сигнал окончания выдачи байта, который, воздействуя на вход однокристального микропроцессора, приводит в действие алгоритм выдачи очередного байта. При этом микропроцессор постоянно производит отсчет числа байтов и определяет последний байт в текущей "порции" речевого сообщения.

Появление любого сигнала с коммутационной группой 1 через диодную сборку 2 на выходе триггера 3 может перевести однокристальный микропроцессор 15 в режим микропотребления и тем самым прерывать выдачу речевого сообщения. После выдачи каждой "порции" речевого сообщения микропроцессор 15 переходит в режим счета времени, а затем продолжает выдачу очередного "порции" до окончания выдачи всего речевого сообщения.

По окончании выдачи речевого сообщения в буферный регистр 17 записывается по шинам "К" код, который с выхода 1 воздействует на триггер 3. На выходе триггера 3 появляется сигнал, воздействующий на вход микропроцессора, переводя его в состояние микропотребления.

В качестве примеров конкретной реализации для ряда узлов устройства речевого оповещения могут быть выбраны стандартные микросхемы широкого применения серии К 561, в том числе: счетчик 10 К561 ИЕ10, узел формирования интервала времени К561 ТМ2, регистр сдвига К561 ИР6.

На фиг. 2 представлена конкретная реализация ключей 19 и 28.

Ключ выполнен на транзисторах V1 и V2, резисторах R1, R2, R3. Сигнал управления поступает на вход 1, внешнее питание + Е - на вход 2. Управляемое напряжение Е1 снимается с коллектора транзистора V2.

На фиг. 3 представлена конкретная реализация преобразователя уровня, который выполнен на резисторе и транзисторе. Входной сигнал подается на резистор, выходной снимается с эмиттера транзистора.

На фиг. 4 представлен пример конкретной реализации часовой схемы на базе серийно выпускаемой УСП Т55. К шинам вход и выход генератора подключается кварцевый резонатор. Выход с генератора поступает на вход счетчика, преобразующего частоту 32 кГц в частоту 2 Гц, которая поступает на формирователь сигналов шагового двигателя, выдающего сигналы ШД1 и ШД2, которые имеют скважность 50 при частоте 2 Гц.

Частоты 1, 16, 2000 Гц поступают на формирователь сигнала зуммера, который улавливается внешним сигналом с входа УПР. Выходной сигнал ЗУМ является смесью трех частот.

На фиг. 5 представлен алгоритм режима счета времени, состоящий из операторов действия: начало 40, сквозная модификация счетчиков времени 42, выключатель зуммер 44, включить зуммер 45, модификация счетчиков синхроконтроля 47 конец, и операторов условных переходов, анализа фронта сигнала 41 времени, анализа значения текущего времени на равенство константе будильника 43, анализа счетчика синхроконтроля времени 46.

На фиг. 6 приведен алгоритм реализации на сигналы коммутационной группы, представленный операторами действия начала 49, отсчета 51 интервала дребезга, анализа кода 53 нажатия клавиши и выполнения действия по каждой из клавиш, конца 55 и операторами условных переходов, анализа фронта нажатия 50 клавиш до и после дребезга, анализа сопровождения действий 54.

На фиг. 7 приведен алгоритм речевого оповещения, представленный операторами действия, начала 56, выбора 57 речевого реквизита и определения начального адреса и числа байтов речевого реквизита, определения характеристик второй части речевого реквизита 59, последовательной передачи 60 речевых констант, перехода в режим счета времени 62, конца 64 и операторами условных переходов: анализ первой или второй составляющих речевого реквизита 58, анализ наличия фронта сигнала 1 с - 61, определение конца выдачи речевого реквизита, конец 64.

На фиг. 8 представлен пример реализации однокристального микропроцессора - КР1830ВЕ48 и соответствие входов выходов КР1830ВЕ48 входам - выходам блока 15 фиг. 1.

На фиг. 9 представлен пример реализации полупостоянно запоминающего устройства К573РФ8 и показано соответствие входов - выходов К573РФ8 входам- выходам блока 27 фиг. 1.

Предлагаемое техническое решение при его использовании позволяет создать электронные часы с речевым оповещением на микросхемах широкого применения, обеспечив при этом высокую точность "хода" часов, высокую автономность работы от батарейных источников питания при минимальном числе электронных компонентов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Блок выборки для интегральных запоминающих устройств с переменной длиной слова | 1977 |

|

SU686084A1 |

| Устройство электронного синтеза мелодии для часов | 1987 |

|

SU1499309A1 |

| Источник питания часовой интегральной схемы | 1989 |

|

SU1742971A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1999 |

|

RU2160929C1 |

| Устройство для регулирования подачи волокна к группе чесальных машин | 1989 |

|

SU1730235A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ МЕТАНА И ДРУГИХ ГОРЮЧИХ ГАЗОВ | 1991 |

|

RU2013565C1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1987 |

|

SU1453378A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ТЕЛЕФОННЫЙ АППАРАТ | 1996 |

|

RU2128887C1 |

Использование: изобретение относится к измерению времени и может быть использовано для создания аудио-часов, а также различных приборов, в которых может присутствовать как одна из функций - аудио-индикация времени, например радиоприемники, электронные игры, электронные термометры и т.д. Сущность изобретения: в устройство, содержащее коммутационную группу 1, две диодные сборки 2, 6, часовую схему 7, схему 4 начальной установки, преобразователя 11, 12 уровня, однокристальный микропроцессор 15, буферный регистр 17, регистры адреса 22, 24, схему ИЛИ 21, инвертор 23, ППЗУ 27, ЦАП 27, ЦАП 20, формирователь 26 звукового сигнала, динамик 29, введены регистр 9 сдвига, счетчик 10, триггеры 3, 18, 25, двухвходовая схема ИЛИ - НЕ 16, трехвходовые схемы И - НЕ 8, 14, инвертор 13, узел 5 формирования интервала времени, ключи 19, 28 с соответствующей совокупностью связей. 9 ил.

ЭЛЕКТРОННЫЕ ЧАСЫ С РЕЧЕВЫМ ОПОВЕЩЕНИЕМ, состоящие из коммутационной группы, двух диодных сборок, часовой схемы, схемы начальной установки, двух преобразователей уровня, однокристального микропроцессора, буферного регистра, двух регистров адреса, схемы ИЛИ, инвертора, полупостоянного запоминающего устройства, цифроаналогового преобразователя, формирователя звукового сигнала, динамика, выходы коммутационной группы соединены с входами первой диодной сборки, первый и второй выходы часовой схемы подключены к входам второй диодной сборки, третий выход часовой схемы соединен с входом второго преобразователя уровня, с первого по К-й выходы однокристального микропроцессора соединены соответственно с первого по К-й входами буферного регистра, второй выход которого подключен к входу первого преобразователя уровня, выход которого соединен с первым входом часовой схемы, выход схемы начальной установки подключен к третьему входу микропроцессора, К + 5-й выход которого соединен с первым входом схемы ИЛИ, второй вход которой соединен с К + 4-м выходом микропроцессора и входом инвертора, а выход подключен к первому входу полупостоянного запоминающего устройства, S выходов которого соединены с S входами микропроцессора и с S входами первого регистра адреса, К + 3-й выход микропроцессора подключен к S + 1-му входу первого регистра адреса, выходы которого соединены с L входами полупостоянного запоминающего устройства, М входы которого подключены к М-выходам микропроцессора, выход инвертора соединен с первым входом второго регистра адреса, последующие входы которого подключены к Н - выходам микропроцессора, а выходы - к Н - входам ППЗУ, выход цифроаналогового преобразователя соединен с вторым входом формирователя звукового сигнала, первый вход которого соединен с третьим входом цифроаналогового преобразователя, а выход подключен к входу динамика и выходу второго преобразователя уровня, отличающиеся тем, что в них дополнительно введены регистр сдвига, счетчик, три триггера, двухвходовая схема ИЛИ - НЕ, две трехвходовые схемы И - НЕ, второй инвертор, узел формирования интервала времени, два ключа, причем N - входов коммутационной группы подключены к N - выходам регистра сдвига, N-й выход которого соединен с первым входом цифроаналогового преобразователя и входом второго триггера, выход которого подключен к второму входу цифроаналогового преобразователя, выход первой диодной сборки соединен с С-входом первого триггера, R-вход которого подключен к первому выходу буферного регистра, прямой выход триггера соединен с вторым входом микропроцессора, а инверсный выход - с первым входом первой трехвходовой схемы И - НЕ, второй вход которой соединен с выходом схемы начальной установки, а третий - с первым выходом узла формирования интервала времени, второй выход которого подключен к четвертому входу микропроцессора, а первый вход - к выходу второй диодной сборки, пятый выход часовой схемы соединен с входом счетчика, первый выход которого подключен к К + 2-му входу регистра сдвига, второй, третий и четвертый выходы счетчика соединены с первым, вторым и третьим входами второй трехвходовой схемы И - НЕ, выход которой подключен к входу первого инвертора, выход которого соединен с первым входом микропроцессора, с К + 1-м входом регистра сдвига и с С-входом второго триггера, выход первой трехвходовой схемы И - НЕ подключен к S-входу третьего триггера, С-вход которого соединен с К + 2-м выходом микропроцессора, а выход - с пятым входом микропроцессора и первым входом второго ключа, выход которого соединен с входом питания полупостоянного запоминающего устройства, К-й выход микропроцессора подключен к первому входу схемы ИЛИ - НЕ, второй вход которой соединен с К + 1-м выходом микропроцессора, а выход подключен к второму входу узла формирования интервала времени, первый вход первого ключа соединен с третьим выходом буферного регистра, а первый выход подключен к третьему входу цифроаналогового преобразователя.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Заявка Японии N 6223836, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-02-20—Публикация

1992-01-24—Подача