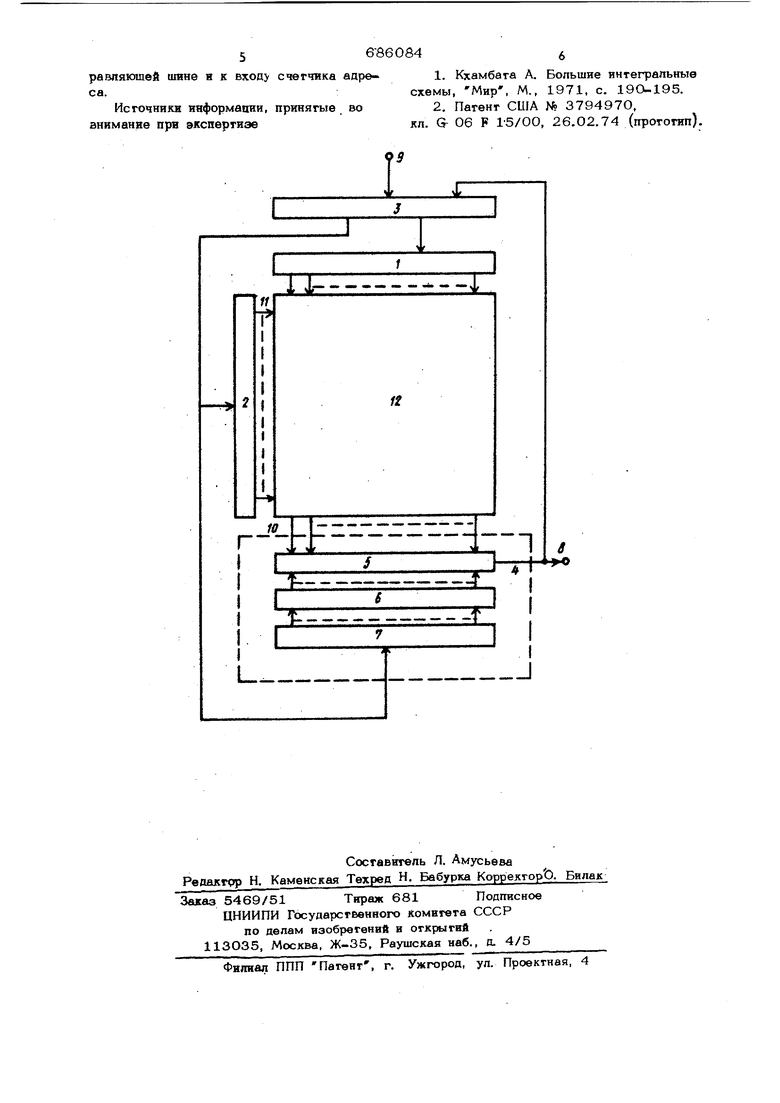

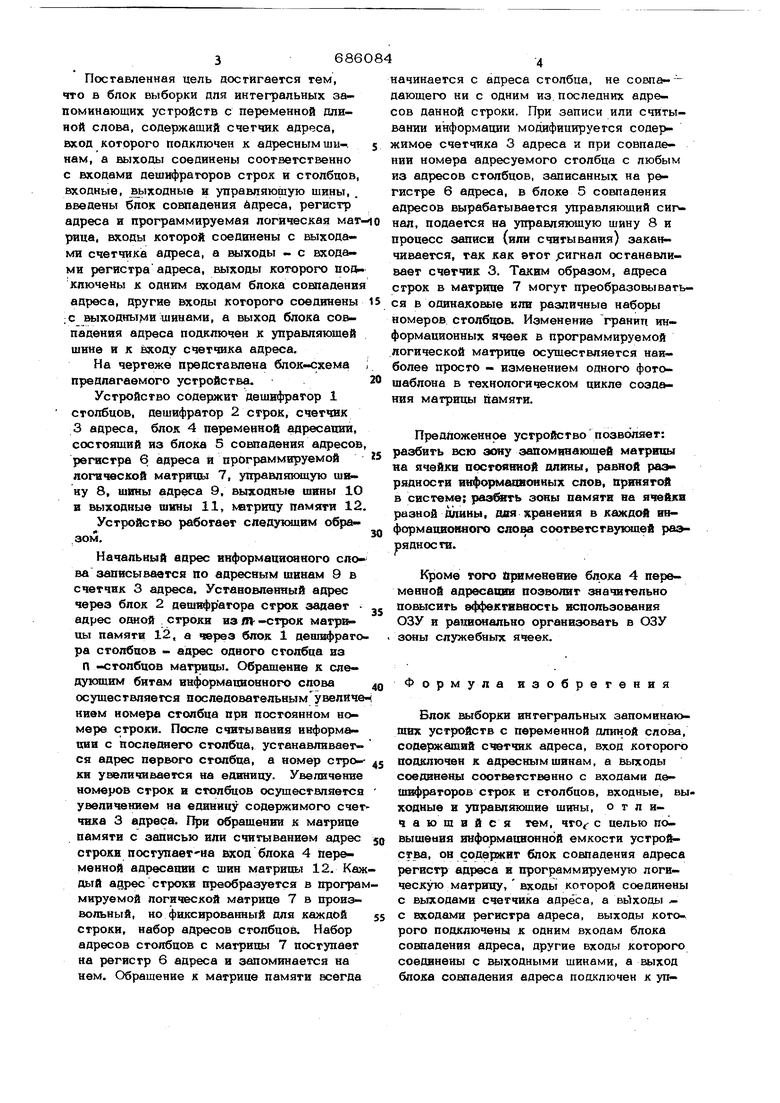

Изобретение относигся к области автоматики и вычислительной техники и npea назначено для применения в оперативных ЗУ в интегральном исполнении. Известно. оперативное запоминающее устройство (ОЗУ) в интегральном испол: нении, содержашее матрицу из однобитны ячеек памяти.. Наличие такой матрниы по воляет производить запись (или считывание) одного бита информации в ячейку (или из ) с произвольно-заданным адресом 1}. Для увеличения разрядности запоминае мых информационных слов используют параллельное включение однобитных ОЗУ, адресные и управляющие шины которых параллельно объединвпот. В этом случае, ргюрядность слова равняется числу запоминающих устройств, и следовательно, постоянна. Использование такого блока запоминающих устройств для хранения информашш с переменной разрядностью, или с разрядностью не равной числу ЗУ, приводит к неращюнальному использованию памяти. Например, если информационное слово больше ячейки ОЗУ, то его нужно разбить на части и записывать по разным адресным ОЗУ, если меньше - то запись в ОЗУ Производится с помошью логических операций. Это усложн5ют работу программиста при написании программ. Наиболее близким техническим решение ем к данному изобретению является устройство, содержашее запоминающую мат рицу, дешифратор столбцов, дешифратор строк, регистр адреса и счетчик адреса, в котором несколько младших разрядов (в данном случае - три) регистра адреса выполнены в виде счетчика адреса 2. Такая схема адресации позволяет разбить всю зону памяти на ячейки одинаковой разрядности. Однако это устройство не позволяет разбивать память ОЗУ на ячейки произвольной длины, что является недостатком такой схемы адресации. Цель1р изобретения является повышение информационной емкости устройства. 3686 Посгавленная цель досгигаегся тем, что в бпок выборки для интегральных запоминающих устройств с переменной длиной слова, содержащий счетчик адреса, вход которого подключен к адресным ши-. нам, а выходы соединены соответственно с входами дешифраторов строк и столбцов, входные, вь1ходные и управляющую шины, . введены бпок совпадения йдреса, регистр адреса и программируемая логическая мат- рица, входы которой соединены с выходами счетчика адреса, а выходы - с входа ми регистра адреса, выходы которого пог ключены к одним входам блока совпадения адреса, другие входы которого соединены :С выходны ли шинами, а илход блока совпадения адреса подключен к управляющей шине и к входу счетчика адреса. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит дешифратор 1 столбцов, дешифратор 2 строк, счетчик 3 адреса, блок 4 переменной адресапии, состоящий из блока 5 совпадения адресов регистра 6 адреса и программируемой логи юской матршсы 7, управлякацую шину 8, шины адреса 9. выходные шяны 10 и выходные шкны 11, кетрниу памяти 12 Устройство работает спедукшим образом. Начальный адрес информационного ело ва записывается по адресным шинам 9 в с«ютчик 3 адреса. Установленный адрес через блок 2 дешифратора строк адрес о{шой .строки из т--строк матрицы памяти 12, а через блок 1 дешифрато ра столбпов - адрес одного столбца из П -столбцов матрицы. Обращение к следующим битам информационного слова осуществляется последовательнымувеличе нием номера столбца при постоянном номере строки. После считывания информации с последнего столбца, устанавливается адрес первого столбца, а номер строки увеличивается на единицу. Увеличение номеров строк и столбцов осуществляется увеличением на единицу содержимого счет чика 3 адреса. При обращении к матрице памяти с записью или считыванием адрес строки поступавТИа вход блока 4 переменной адресации с шин матрипьт 12. Каж дый адрес строка преобразуется в програм мируемой логической матрице 7 в произвольный, но фиксированный для каждой строки, набор адресов столбцов. Набор адресов столбцов с матрицы 7 поступает на регистр 6 адреса и запоминается на нем. Обращение к матрице памяти всегда начинается с адреса столбца, не совпа- дающего ни с одним из. последних адресов данной строки. При записи или считывании информации модифицируется содернжимое счетчика 3 адреса и при совпадении номера адресуемого столбца с любым из адресов столбцов, записанных на регистре 6 адреса, в блоке 5 совпадения адресов вырабатывается управляющий сиг нал, подается на утфавляющую шину 8 и процесс записи (или считывания) заканчивается, так как этот ригнал останавливает счетчик 3. Таким образом, адреса строк в матрице 7 могут преобразовываться в одинаковые или различные наборы номеров столбцов. Изменение границ информационных ячеек в программируемой логической матрице осуществляется наиболее просто - изменением одного фотошаблона в технологическом цикле создания матрицы памяти. Предложенное устройство позволяет: разбить всю зону запоминающей матрицы на ячейки постоягаюй длины, равной разрядности информашюнных слов, принятий в системе; разбаггь зоны памяти на ячейки разной длины, дня хранения в информацвоиного слова соответствукшхей разрядности. Кроме ГОТО артменение блока 4 переменной адресашш позволит значительно повысить 9ффвКТ8В80СТЬ ЕСПОЛЬЗОВаНИЯ ОЗУ и рационально организовать в ОЗУ зоны служебных ячеек. Форм у л а изобретения Блок выборки интегральных запоминак пгах устройств с переменной длиной слова, содержащий счетчик адреса, вход которого подключен к адресным шинам, а выходы соединены соответственно с взсопами дешифраторов строк и столбцов, входные, выходные и управлякяцие шины, отличающийся тем, что,- с целью повышения информационной емкости устройства, он содержит блок совпадения адреса регистр адреса и программируемую логическую матрицу, входы которой соединены с выходами счетчика адреса, а abixoobi - с входами регистра адреса, выходы которого подключены к одним входам блока сога1адения адреса, другие входы которого соединены с выходными шинами, а выход блока совпадения адреса пооключен к уп- 5 равляющей шине и к входу счетчика са. Исгочникн информации, принятые внимание прв экспертизе 6-86084 1.Кхамбага А. Большие интегральные адресхемы, Мир, М., 1971, с. 190-195. 2,Патент США № 379497О, во кл. О- 06 F Г5/00, 26.02.74 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| Устройство адресации к динамической памяти | 1987 |

|

SU1444785A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU269215A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1983 |

|

SU1108507A1 |

| Запоминающее устройство | 1980 |

|

SU920832A1 |

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

I I,,х

If

V j

ij. д t

т ,

е -,-

Г

1

J-Tt

9

I

Авторы

Даты

1979-09-15—Публикация

1977-06-09—Подача