iff

r-i 18

00 СО О5

4

СП

гч

2.т

29.т

Изобретение относится к вычисли тельной технике и может быть использовано для контроля обмена информацией между управляющим и операцион- ным автоматами или между источником информации и устройствами обработки.

Целью изобретения является повышение достоверности контроля.

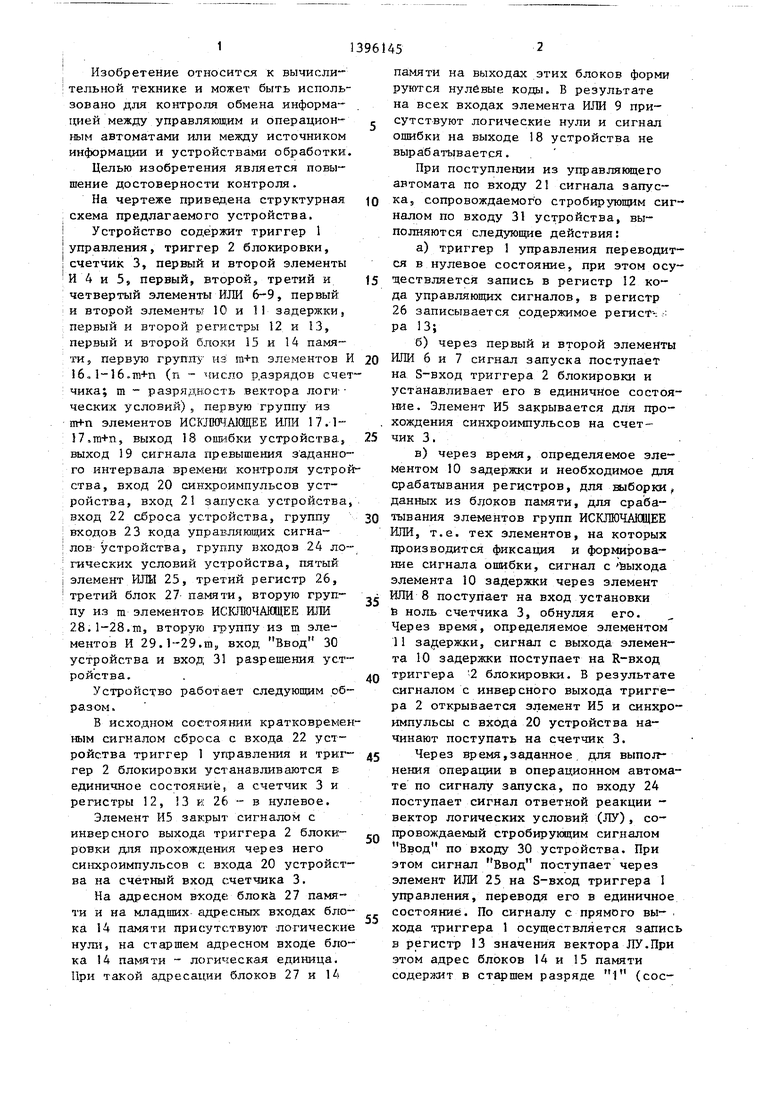

На чертеже привер,ена структурная схема предлагаемого устройства.

Устройство содержит триггер 1 управления, триггер 2 блокировки, счетчик 3, первый и второй элементы И 4 и 5, первый, второй, третий и

четвертый элементы ИЛИ 6-9, первый и второй элементы 10 и 11 задержки, первый и второй регистры 12 и 13, первый и второй блоки 15 и 14 памяти, первую группу из элементов И 16,1-16,га+п (п - число р.азрядов счет чика; m разрядность вектора логи- ческих УСЛОВИЙ), первую труппу из ПГ+-П элементов ИСКЛЮЧ:А1Ш1;ЕЕ И.ПИ 17.1- }7,in+n, выход 18 овмбки устройства, выход 19 сигнала пре.вышения з аданно- го интервала времени: контроля устройства, вход 20 синхроимпульсов устройства, вход 21 запуска устройства вход 22 сброса устройства, группу входов 23 кода управляюидах сигналов- устройства, группу входов 24 логических условий устройства, пятый элемент РШН 25, третий регистр 26, третий блок 27 памяти, вторую груп- пу из m элементов ИСКЛЮЧАЮЩЕЕ Р1ЛИ 28.1-28.т, вторую группу из m элементов И 29.1-29.га, вход Ввод 30 устройства и вход 31 разрешения устройства..

Устройство работает следующим образом.

В исходном состоянии кратковременным сигналом сброса с входа 22 устройства триггер 1 управления и триг- гер 2 блокировки устанавливаются EI еди шчное состояние, а счетчик 3 и регистры 12, 3 к 26 - в нулевое.

Элемент ИЗ зав:рыт сигналом с инверсного выхода триггера 2 блоки- ровки дня прохождения через него синхроимпульсов с входа 20 устройства на счетный вход счетчика 3.

На адресном в-ходе блока 27 памя;- ти и на младших адресных входах бло- ка 14 памяти присутствуют логические нули, на старшем адресном входе блока 14 памяти - логическая единица. При такой адресации блоков 27 и 14

памяти на выходах этих блоков форми руются нулевые коды. В результате на всех входах элемента ИЛИ 9 присутствуют логические нули и сигнал ошибки на выходе 18 устройства не вырабать1вается.

При поступлении из управляющего автомата по входу 21 сигнала запуска, сопровождаемого стробирующим сигналом по входу 31 устройства, выполняются следующие действия:

а)триггер 1 управления переводится в нулевое состояние, при этом осуществляется запись в регистр 12 кода управляющих сигналов, в регистр

26 записывается содержимое регисТч : ра 13;

б)через первый и второй элементы ИЛИ 6 и 7 сигнал запуска поступает на S-вход триггера 2 блокировки и устанавливает его в единичное состояние. Элемент И5 закрывается для прохождения синхроимпульсов на счетчик 3.

в)через время, определяемое элементом 10 задержки и необходимое для срабатывания регистров, для выборки, данных из блоков памяти, для срабатывания элементов групп ИСКЛЮЧАЮЩЕЕ ИЛИ, т.е. тех элементов, на которых производится фиксация и формирова- 1-ше сигнала ошибки, сигнал с выхода элемента 10 задержки через элемент ИЛИ 8 поступает на вход установки

6 ноль счетчика 3, обнуляя его. Через время, определяемое элементом И задержки, сигнал с выхода элемента 10 задержки поступает на R-вход триггера 2 блокировки. В результате сигналом с инверсного выхода триггера 2 открывается элемент ИЗ и синхроимпульсы с входа 20 устройства начинают поступать на счетчик 3.

Через время,заданное, для выполнения операции в операционном автомате по сигналу запуска, по входу 24 поступает сигнал ответной реакции - вектор логических условий (ЛУ), сопровождаемый стробирующим сигналом Ввод по входу 30 устройства. При этом сигнал Ввод поступает через элемент ИЛИ 25 на S-вход триггера 1 управления, переводя его в единичное состояние. По сигналу с прямого вы- . хода триггера 1 осуществляется запис в регистр 13 значения вектора ЛУ.При этом адрес блоков 14 и 15 памяти содержит в старшем разряде 1 (соетояиие прямого выхода триггера 1 управления) , а в младших - значение кода управляющих сигналов (КУС), зафиксированного в регистре 12. Значение КУС является также адресом , блока 27 памяти. По этому адресу в блоке 15 памяти хранится информация о векторе ЛУ, имеющих известные значения для данного КУС, а также код контрольного времени выполнения операции для этого КУС; в блоке 14 памяти - информация о маскировании тех компонент вектора ЛУ и тех разрядов кодов времени, для которых нет априорных знаний их значений; в блоке 27 памяти - информации о маскировании не инвариантных к данному КУС компонентах вектора ЛУ. Далее выполняются действия, отмеченные в пп. б) и а) при поступлении сигнала запуска.

Ч ерез время, заданное для выработки управляющим автоматом нового КУС, соответствующего поступившему на него вектору ЛУ, управляющий автомат выдает по входу 23 КУС, сопровождав- стробирующим сигналом по входу 31 устройства.

При этом сигналом по входу 31 триггер 1 управления переводится в нулевое состояние. Сигналом с его инверсного выхода осуществляется запись КУС в регистр 12 и запись в регистр 26 информации о векторе ЛУ, хранимой в регистре 13. Далее выполняются действия, отмеченные в пп. б), в) при поступлении сигнала запуска. При этом адрес блоков 14 и 15 памяти содержит в старшем разряде О (состояние единичного выхода триггера 1 управления), а в младших - значение КУС. Адрес блока 27 памяти равен КУС. По этим адресам в блоке 15 памяти хранятся постоян-п ные значения компонент векторов ЛУ, под действием которых может вырабатываться управляющим автоматом данный КУС, а также контрольное время его формирования. В блоке 14 памяти хранятся информация о маскировании тек компонент векторов 14 и тех разрядов кодов времени, которые контролю не подлежат, а в блоке 27 памяти - информация о маскировании не инвариантных к данному КУС компонентах вектора ЛУ.

Через время, заданное для выполнения операций в операционном автома0

5

0

те под действием выработанного КУС, из операционного автомата по входу 24 поступает новый вектор ЛУ, сопровождаемый сигналом Ввод, и осуществляются операции, аналогичные рассмотренным.

Сигнал сброса по входу 22 переводит устройство в исходное состояние.

При исправной работе контролируемых автоматов на первых и (или) вторых входах элементов И 16.1- 16.m+n и 29.1-29.т первой и второй групп присутствуют логические нули вследствие поразрядного совпадения ожидаемой и реальной информации или из-за маскирования данных разрядов, поэтому на выходах указанных элементов И, а следовательно, и на выходах элементов ИЛИ 9 и элемента И4 1фи- сутствует нулевой сигнал. В результате на выходе 18 ошибки устройства сигнал ошибки не появляется.

Если сбой в работе управляющего или операционного автомата привел к преждевременному формированию или задержке в выработке КУС или вектора ЛУ, то код, снимаемый с выхода счетчика 3, не совпадает с кодом, поступающим из блока 15 памяти, хотя бы в одном разряде, не замаскированном информацией с блока 14 памяти. На выходе соответствующего элемента И первой группы элементов И с (т+1)- с го по (т+п)-й появляется единичный сигнал, который при поступлении единичного сигнала на первый вход элемента И4 поступает на выход 18 ошибки устройства.

Если в результате сбоев или отказов КУС или векторы ЛУ не вырабатываются, то подача синхроимпульсов на счетчик 3 не-прекращается. В результате на выходе переполнения счетчика появляется сигнал, поступаю5

0

0

5

0

5

щий на выход 19 превышения заданного интервала времени контроля устройства.

Если сбой привел к ложному формиро- рованию для данного КУС вектора ЛУ, то

появится единичный сигнал на выходе хотя бы одного элемента первой группы элементов И с первого по тп-й из-за несоответствия незамаскированных компонент вектора ЛУ априорно известным значениям (из-за несоответствия между замаскированной бло513

ком 14 памяти информацией регистра 13 и информацией с блока 15 памяти);

появится единичный сигнал на выходе хотя бы одного элемента второй группы элементов И из-за изменений среди инвариантных относительно данных КУС компонент вектора ЛУ (из-за несоответствия информации регистра 13 информации регистра 26 с учетом :маскирования соответствующих разрядов информацией с блока 2 7 памяти. , В обоих случаях эти сигналы вызовут появление единичного сигнала нс1 выходе элемента HJDi 9. При разблоки- ровлнии элемента И 4 сигналом с выхода элемента 10 задержки единичный сигнал поступит на выход 18 устройства, свидетельствуя об оямбке.

Если сбой привел к ложному форми- 1рованию КУС, то появится единичный сигнал на выходе хотя бы одного из элементов первой группьз элементов И :С первого по т-й. На выходах элементов второй группы элементов И 29.1- 29.га присутствуют нули, так как в регистрах 12 и 26 находится идентичная информация. При появлении-единич:ного сигнала на выходе элемента 10 :задержки на выходе 18 устройства

сформируется сигнеШ ошибки.

Формула изобретен и я

Устройство для контроля по авт. :св. № 1315983, отличающее- с я тем, что, с цел1: ю повышения

5

0 5 0

5

456

достоверности контроля, устройство содержит пятый элемент ИЖ, третий блок памяти, третий регистр, вторую группу из m элементов И, вторую группу из m элементов 1СКЛЮЧАЩЕЕ ИШ, причем вход ввода устройства соединен с первым входом пятого элемента ИПИ, второй вход которого соединен с входом сброса устройства, выход пятого элемента ИПИ соединен с S-входом триггера управления, которого соединен с входом разрешения устройства, инверсный выход триггера управления соединен с входом синхронизации третьего регистра, информационные входы которого соединены с соответствующими выходами второго регистра, R-вход третьего регистра соединен с входом сброса устройства, разрядные выходы третьего регистра соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы которых соединены с группой выходов второго perHCTpaj группа адресных входов третьего блока памяти соединена с группой разрядных выходов первого регистра, информационные выходы третьего блока памяти соединены с первыми- входами элементов И второй груп- пя J вторые входы которых соединены с соответствующими выходами элементов ИСКПЮЧАКЩЕЕ ИЛИ второй группы, выходы элементов И второй группы соединены с соответствующими входами четвертого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля | 1985 |

|

SU1315983A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1991 |

|

RU2029986C1 |

| Устройство для контроля обмена информацией | 1989 |

|

SU1683018A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2013803C1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для контроля хода микропрограмм | 1987 |

|

SU1430959A1 |

| Устройство для ввода информации | 1986 |

|

SU1314326A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

Изобретение относится к вычислительной технике и предназначено для контроля Обмена информацией между управляющим и операционным автоматами. Целью Изобретения является повышение достоверности контроля. Устройство содержит триггер управления 1, триггер блокировки 2, счетчик 3,пять элементов ИЛИ 6, 7, 8, 9, 25/ два элемента задержки 10, 11, два элемента И 4,5, три регистра 12, 13, 26, три блока памяти 14, 15, 27, две . группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 17, 28, две группы элементов И 16, 29. Сущность изобретения заключается в создании устройства для контроля с высокой достоверностью путем контроля инвариантной относительно управляющего воздействия информации, формируемой операционным автоматом в ответ на данное воздействие. 2 ил. г (Л

| Устройство для контроля | 1985 |

|

SU1315983A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-15—Публикация

1986-11-20—Подача