Изобретение относится к радиотехнике и может быть использовано в системах радиосвязи и измерения дальности.

Современное состояние техники в указанной области и тенденции ее развития, а также вопросы теории рассмотрены в [1].

Однако в научно-технической литературе отсутствуют сведения, касающиеся способов и устройств, реализующих децимацию М-последовательностей с тактовой частотой, не зависящей от индекса децимации. Данное предложение направлено на решение этой задачи.

Наиболее близким по технической сущности к решаемой задаче является устройство для формирования М-последовательностей [2], содержащее генератор тактовых импульсов, делитель с переменным коэффициентом деления, счетный выход которого подключен к выходу генератора тактовых импульсов, а вход установки коэффициента деления является входом устройства, генератор псевдослучайных последовательностей (ПСП), тактовый вход которого подключен к выходу генератора тактовых импульсов, регистр хранения, тактовый вход которого подключен к выходу делителя с переменным коэффициентом деления, а информационные входы - к соответствующим выходам генератора ПСП, параллельный выход регистра хранения является выходом устройства.

Известное устройство позволяет получать различные М-последовательности путем децимации циклических сдвигов исходной М-последовательности, формируемой с помощью регистра сдвига с обратной связью, осуществлять децимацию исходной М-последовательности и получать на выходе циклические сдвиги децимированной ПСП.

Однако известное устройство не позволяет получать постоянную тактовую частоту децимированной ПСП, не зависящую от индекса децимации.

Цель изобретения - расширение области применения за счет устранения зависимости между индексом децимации q и тактовой частотой формируемой ПСП.

Поставленная цель достигается тем, что устройство для преобразования М-последовательностей содержит генератор тактовых импульсов, делитель с переменным коэффициентом деления и генератор М-последовательностей, причем вход генератора тактовых импульсов подключен к шине "Пуск", а выход соединен с тактовым входом делителя с переменным коэффициентом деления, задатчик коэффициента деления, задатчик номера циклического сдвига, три элемента задержки, пять элементов И, два элемента ИЛИ, три RS-триггера, управляемый ключ, задатчик модуля счета, счетчик адресов, группу из n элементов И, формирователь импульсов выборки, группу из n формирователей импульсов, группу из n оперативных запоминающих устройств, группу из n D-триггеров, причем шина "Пуск" подключена к установочным входам задатчика коэффициента деления, задатчика циклического сдвига, задатчика модуля счета и R-входам первого и третьего RS-триггеров, первая и вторая входные шины подключены к соответствующим входам задатчика коэффициента деления, выходы которого соединены с выходом установки делителя с переменным коэффициентом деления, третья входная шина соединена с входом задатчика номера циклического сдвига, выходы которого подключены к входам установки начального состояния генератора М-последовательностей, вход задатчика модуля счета подключен к четвертой входной шине, пятая входная шина соединена с входом генератора М-последовательностей, выходы которого с первого и по n-й соединены с третьими входами элементов И группы из n элементов И, выходы которых через соответствующие формирователи импульсов группы из n формирователей импульсов соединены с информационными входами соответствующих оперативных запоминающих устройств групп из n оперативных запоминающих устройств, выход генератора тактовых импульсов соединен с входами первого и тpетьего элементов задержки, первым входом управляемого ключа и R-входом второго RS-триггера, прямой выход которого подключен к третьему входу пятого элемента И и вторым входам элемента И группы из n элементов И, выход делителя с переменным коэффициентом деления соединен с входом задатчика коэффициента деления, вторым входом управляемого ключа, S-входом первого RS-триггера и через второй элемент задержки с S-входом второго RS-триггера, выход первого элемента задержки соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к первому и второму входам первого элемента ИЛИ, выход которого соединен с тактирующим входом генератора М-последовательностей, прямой выход первого RS-триггера соединен со вторыми входами второго и третьего элементов И, а инверсный выход соединен со вторым входом первого элемента И, выход третьего элемента задержки соединен с вторыми входами четвертого и пятого элементов И, выходы которых подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого через формирователь импульсов выборки соединен с выходами выборки оперативных запоминающих устройств группы из n оперативных запоминающих устройств с входами синхронизации D-триггеров группы из n D-триггеров, входы которых соединены с выходами соответствующих оперативных запоминающих устройств группы из n оперативных запоминающих устройств, выходы задатчика модуля счета подключены к входам установки модуля счета счетчика адресов, счетный вход которого соединен с выходом третьего элемента И, а выход соединен с входом задатчика модуля счета и S-входом третьего RS-триггера, прямой выход которого соединен с первым входом четвертого элемента И, инверсный выход подключен к первым входам пятого элемента И и элементов И группы из n элементов И, входам управления записью оперативных запоминающих устройств группы из n оперативных запоминающих устройств и управляющему входу управляемого ключа, выход которого соединен с первым входом третьего элемента И, адресные входы оперативных запоминающих устройств группы из n оперативных запоминающих устройств подключены к соответствующим выходам счетчика адресов.

Сравнение предложенного устройства с прототипом показывает, что оно имеет отличия, составляющие его новизну.

В прототипе тактовая частота децимированной М-последовательности зависит от коэффициента деления делителя с переменным коэффициентом деления (ДПКД). В предлагаемом устройстве тактовая частота децимированной М-последовательности постоянна и не зависит от индекса децимации.

Таким образом, положительный эффект заключается в стабилизации тактовой частоты децимированной ПСП путем независимости ее от индекса децимации.

Входящие в предложенное устройство RS-триггер, элементы И, ИЛИ, управляемые ключи, ОЗУ, формирователи импульсов, D-триггеры, элементы задержки известны из технической литературы, однако они не направлены на стабилизацию тактовой частоты децимированной ПСП.

Что же касается новых связей, то они либо отсутствуют в литературе, либо известны, но при этом обеспечивают создание другого положительного эффекта. Следовательно, все перечисленные отличия являются существенными.

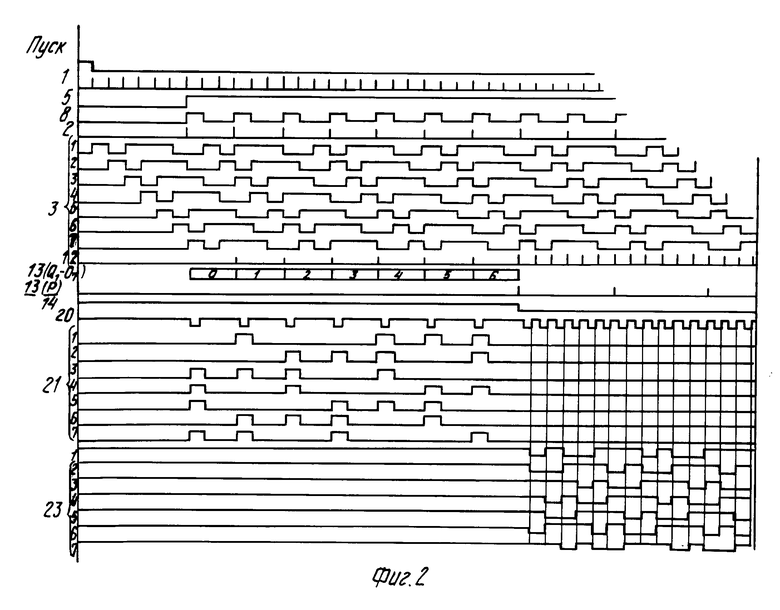

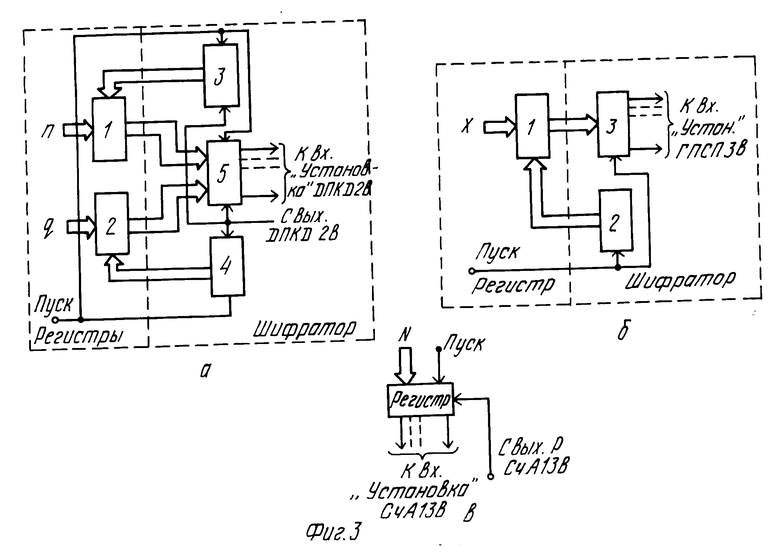

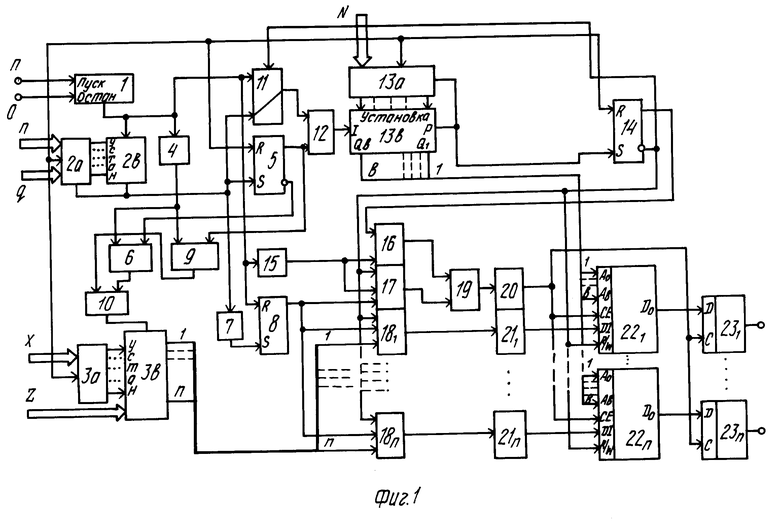

На фиг. 1 представлена структурная электрическая схема заявляемого устройства; на фиг. 2 - временные диаграммы работы устройства в режиме децимации; на фиг. 3 - функциональные схемы соответственно задатчиков коэффициента деления, номера циклического сдвига и модуля счета.

Адреса на выходе счетчика адресов представлены в десятичной форме записи. Задержки, обеспечивающие работоспособность устройства, на временных диаграммах не показаны.

На временных диаграммах показана работа устройства для случая, когда период исходной М-последовательности равен n = 7, а индекс децимации q = 3.

Устройство преобразования М-последовательностей содержит: генератор 1 тактовых импульсов (ГТИ), делитель 2 с переменным коэффициентом деления (ДПКД), содержащий задатчик 2а коэффициента деления (ЗКД) и собственно делитель (Дел) 2b, генератор 3 М-последовательностей (ГПСП), содержащий задатчик 3а номера циклического сдвига (ЗЦС) и собственно генератор 3b М-последовательностей (ГМ), первый элемент задержки (ЭЗ) 4, первый RS-триггер (Тг)5, первый элемент И 6, второй элемент задержки (ЭЗ) 7, второй RS-триггер (Тг) 8, второй элемент И 9, первый элемент ИЛИ 10, первый управляемый ключ (Кл) 11, третий элемент И 12, счетчик адресов (Сч А) 13, содержащий задатчик 13а модуля счета (ЗМС) и собственно счетчик (Сч) 13b, третий RS-триггер (Тг) 14, третий элемент задержки (ЭЗ) 15, пятый и шестой элементы И 16, 17, n седьмых элементов И 181-18n, второй элемент ИЛИ 19, формирователь 20 импульсов выборки ячеек ОЗУ (ФИВ), n формирователей импульсов (ФИ) 211-21n, n оперативных запоминающих устройств (ОЗУ) 221-22n, n D-триггеров (Тг) 231-23n.

Задатчик 2а коэффициента деления (ЗКД) содержит два параллельных регистра для записи в них чисел n и q и шифратор, преобразующий записанные в регистрах числа в код управления коэффициентом деления делителя 2b, причем по сигналу "Пуск" в делитель вводится код, соответствующий числу n и устанавливающий коэффициент деления 2b, равным n, а по импульсу с выхода делителя 2b в него вводится код, соответствующий числу q и устанавливающий коэффициент деления делителя 2b равным q.

Задатчик 3а номера циклического сдвига (ЗМС) содержит параллельный регистр хранения номера сдвига κ и шифратор, преобразующий этот номер в код, загружаемый в генератор М-последовательностей 3b по сигналу "Пуск" и определяющий начальное состояние генератора 3b, соответствующее номеру циклического сдвига.

Генератор М-последовательностей содержит сдвиговый регистр, сумматоры по модулю 2 и управляемые ключи. Изменение образующего полинома осуществляется путем изменения характера обратных связей в генераторе путем управления ключами на шине Z.

Задатчик 13а модуля счета содержит параллельный регистр для записи числа N, которое загружается в счетчик 13а либо по сигналу "Пуск", либо по сигналу "Перенос" с выхода счетчика 13b.

Задатчик 2а коэффициента деления (ЗКД) (фиг. 3) содержит регистр 1 хранения числа n, регистр 2 хранения числа q и шифратор, содержащий преобразователи 3, 4 сигналов управления ЗКД в коды управления регистрами 1, 2 и преобразователи 5 чисел n и q в коды управления ДПКД.

Задатчик работает следующим образом. По сигналу "Пуск" преобразователи 3 и 4 разрешают загрузку чисел n и q в регистры 1 и 2. Соответственно число n с параллельного выхода регистра 1 преобразуется преобразователем 5 в код управления ДПКД 2b, который с выхода преобразователя 5 устанавливает коэффициент деления ДПКД 2b равным n. Импульс с выхода ДПКД 2b разрешает выдачу числа q из регистра 2 и пpеобразование его преобразователем 5 в код управления ДПКД 2b, а также через преобразователь 3 запрещает выдачу числа n из регистра 1, при этом коэффициент деления ДПКД 2b становится равным q.

Задатчик номера циклического сдвига (фиг. 3, б) содержит регистр 1 хранения числа κ - номера циклического сдвига и шифратор, содержащий преобразователь 2 сигналов управления задатчиком в коды управления регистром 1 и преобразователь 3 числа κ в код начальной установки ГПСП 3b.

Задатчик работает следующим образом. По сигналу "Пуск" преобразователь 2 разрешает загрузку числа κ в регистр 1 и преобразование его преобразователем 3 в код начальной установки ГПСП 3b. С выхода преобразователя 3 код начальной установки загружается в ГПСП 3b.

Задатчик 13а модуля счета (фиг. 3, в) содержит регистр хранения числа N.

Задатчик работает следующим образом. По сигналу "Пуск" разрешается запись числа N в регистр и загрузка его в Сч А 13b по входам "Установка". По сигналу переноса "Р" от Сч А 13b разрешается загрузка числа N из регистра в Сч А 13b.

Устройство для преобразования М-последовательностей работает следующим образом.

Сначала осуществляется инициализация устройства путем асинхронной записи чисел N, n, q, κ и Z соответствующие задатчики.

По переднему фронту сигнала "Пуск" происходит установка в "0" RS-триггеров 5 и 14, запись в ДПКД 2 модуля коэффициента деления, равного n, запись в счетчик адресов Сч А 13 числа N равного

N = c - n, где n - период исходной М-последовательности; с - модуль счета счетчика адресов, зависящий от числа его разрядов и определяемый выражением:

c = 2k - 1, где k - число разрядов в счетчике адресов, запись в ГПСП 3 начальной комбинации, определяющей начальный циклический сдвиг М-последовательностей.

По заднему фронту "Пуск" происходит запуск ГТИ 1. Импульсы с выхода ГТИ 1 через ЭЗ 3 и элемент И 6, прохождение через который разрешено уровнем лог "1" с инверсного выхода RS-триггера 5, а также через элемент ИЛИ 10 тактируют ГПСП 3.

Время задержки ЭЗ 4 выбирается равным

τЭЗ4 = τСРДПКД2 + τСРRS5.

На выходах 1, ..., n ГПСП 3 постоянно (фиг. 2, 31-3n) начинают появляться последовательные циклические сдвиги исходной М-последовательности. После n тактовых импульсов от ГТИ 1 на выходе ДПКД 2 появляется импульс, который устанавливает RS-триггер 5 в "1", а через время задержки, равное длительности тактового импульса и задаваемое ЭЗ 7, устанавливает RS-триггер 8 в "1", начиная формирование на его прямом выходе интервала выборки из такта исходной М-последовательности. Этот же импульс с выхода ДПКД 2 через задатчик коэффициента деления 2а устанавливает коэффициент деления ДПКД 2, равный выбранному индексу децимации q.

Уровень лог. "1" с прямого выхода RS-триггера 5 разрешает прохождение импульсов с выхода ГТИ 1 через элемент задержки ЭЗ 4 и элемент И 9 и далее через элемент ИЛИ 10 на вход ГПСП 3, а также разрешает прохождение импульсов с выхода ДПКД 2 через Кл. 11, элемент И 12 на счетный вход "1" счетчика адресов Сч А 13.

Следующий тактовый импульс с выхода ГТИ 1 устанавливает RS-триггер 8 в "0", заканчивая формирование на его прямом выходе интервала выборки.

Предшествующий тактовый импульс, задержанный ЭЗ 15 на время, равное

τЭЗ15 = τЭЗ7 + τСРRS8 , где τЭЗ7 - время задержки ЭЗ 7; τСРRS8 - время срабатывания RS-триггера 8, проходит через элемент И 17, на первом входе которого действует разрешающий потенциал (ур. лог. "1") с выхода RS-триггера 14, а на третьем входе разрешающий потенциал в виде интервала выборки с выхода RS-триггера 8. С выхода элемента И 17 импульс через элемент ИЛИ 19 поступает на ФИВ 20, который формирует импульс выборки ячейки ОЗУ.

На выходах элементов И 181-18n импульс интервала выборки с выхода RS-триггера 8 формирует значения выборки из такта циклических сдвигов исходной М-последовательности, которые через ФИ 211-21n записывается в ОЗУ 221-22n по адресу, сформированному к этому моменту времени счетчиком адресов Сч А 13.

Далее устройство работает аналогичным образом до момента появления импульса переноса на выходе Р счетчика адресов Сч А 13 после n импульсов с выхода ДПКД 2, прошедших через Кл 11, элемент И 13 на вход "1" Сч А 13 и подсчитанных этим счетчиком. Импульс переноса с выхода Р Сч А 13 устанавливает RS-триггер 14 в "1", а также через задатчик числа N 13а записывает число N в Сч А 13, осуществляя, таким образом, его предустановку.

Уровень лог. "0" с инверсного выхода RS-триггера 14 запрещает прохождение сигналов через элементы И 17, 181-18n и переключает ОЗУ 221-22n в режим считывания, а также подключает выход Кл 11 к выходу ГТИ 1, т.е. в режиме считывания адреса ОЗУ будет переключаться с частотой ГТИ 1.

Уровень лог. "1" с прямого выхода RS-триггера 14 разрешает прохождение тактовых импульсов ГТИ 1 с выхода ЭЗ 15 через элемент И 16 и далее через элемент ИЛИ 19 на ФИВ 20 для формирования импульсов выборки ячеек ОЗУ с частотой ГТИ 1.

Последовательным перебором адресов ОЗУ 221-22n счетчиком Сч А 13 с частотой ГТИ 1 осуществляется считывание из ОЗУ 221-22n записанной ранее информации, которая появляется на выходах D в виде импульсов с длительностью, равной длительности импульсов выборки ячеек ОЗУ. Для того чтобы длительность импульсов выходной последовательности устройства равнялась длительности такта ГТИ 1, импульсы с выхода Do ОЗУ 221-22n записываются в соответствующие D-триггеры 231-23n задним фронтом импульсов выборки ячеек ОЗУ с выхода ФИВ 20.

Таким образом, предложенное устройство позволяет осуществлять децимацию М-последовательностей и получать на выходе одновременно все циклические сдвиги децимированных М-последовательностей, причем тактовая частота выходных последовательностей не зависит от индексов децимации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ М-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2112313C1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| ЦИФРОВАЯ РЕГУЛИРУЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2108659C1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2008 |

|

RU2386208C1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2004 |

|

RU2269866C2 |

| Устройство ранжирования чисел | 1987 |

|

SU1425653A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2308163C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2284668C1 |

Применение: устройство относится к радиотехнике и может быть использовано в системах радиосвязи и измерения дальности. Сущность изобретения: устройство содержит генератор 1 тактовых импульсов, задатчик 2а коэффициента деления, делитель 2b с переменным коэффициентом деления, задатчик 3а номера циклического сдвига, генератор 3b М-последовательностей, три элемента задержки 4, 7 и 15, три RS-триггера 5, 8 и 14, пять элементов И 6, 9, 12, 16 и 17, два элемента ИЛИ 10 и 19, управляемый ключ 11, задатчик 13а модуля счета, счетчик 13b адресов, группу из n элементов И 181 ,..., 18n формирователь 20 импульсов выборки, группу из n формирователей импульсов 211 ,..., 21n группу из n оперативных запоминающих устройств 221 ,..., 22n группу из n D-триггеров 231 ,..., 23n с соответствующими связями. 3 ил.

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащее генератор тактовых импульсов, делитель с переменным коэффициентом деления и генератор M-последовательностей, причем вход генератора тактовых импульсов подключен к шине "Пуск", а выход соединен с тактовым входом делителя с переменным коэффициентом деления, отличающееся тем, что, с целью расширения области применения за счет устранения зависимости между индексом децимации q и тактовой частотой формируемой псевдослучайной последовательности, в него введены задатчик коэффициента деления, задатчик номера циклического сдвига, три элемента задержки, пять элементов И, два элемента ИЛИ, три RS-триггера, управляемый ключ, задатчик модуля счета, счетчик адресов, группа из n элементов И, формирователь импульсов выборки, группа из n формирователей импульсов, группа из n оперативных запоминающих устройств, группа из n D-триггеров, причем шина "Пуск" подключена к установочным входам задатчика коэффициента деления, задатчика номера циклического сдвига, задатчика модуля счета и R-входам первого и третьего RS-триггеров, первая и вторая входные шины подключены к соответствующим входам задатчика коэффициента деления, выходы которого соединены с входом установки делителя с переменным коэффициентом деления, третья входная шина соединена с входом задатчика номера циклического сдвига, выходы которого подключены к входам установки начального состояния генератора M-последовательностей, вход задатчика модуля счета подключен к четвертой входной шине, пятая входная шина соединена с входом генератора M-последовательностей, выходы которого с первого по n-й соединены с третьими входами элементов И группы из n элементов И, выходы которых через соответствующие формирователи импульсов группы из n формирователей импульсов соединены с информационными входами соответствующих оперативных запоминающих устройств группы из n оперативных запоминающих устройств, выход генератора тактовых импульсов соединен с входами первого и третьего элементов задержки, первым входом управляемого ключа и R-входом второго RS-триггера, прямой выход которого подключен к третьему входу пятого элемента И и вторым входам элементов И группы из n элементов И, выход делителя с переменным коэффициентом деления соединен с входом задатчика коэффициента деления, вторым входом управляемого ключа, S-входом первого RS-триггера и через второй элемент задержки с S-входом второго RS-триггера, выход первого элемента задержки соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к первому и второму входам первого элемента ИЛИ, выход которого соединен с тактирующим входом генератора M-последовательностей, прямой выход первого RS-триггера соединен с вторыми входами второго и третьего элементов И, а инверсный выход - с вторым входом первого элемента И, выход третьего элемента задержки соединен с вторыми входами четвертого и пятого элементов И, выходы которых подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого через формирователь импульсов выборки соединен с входами выборки оперативных запоминающих устройств группы из n оперативных запоминающих устройств и входами синхронизации D-триггеров группы из n D-триггеров, входы которых соединены с выходами соответствующих оперативных запоминающих устройств группы из n оперативных запоминающих устройств, выходы задатчика модуля счета подключены к входам установки модуля счета счетчика адресов, счетный вход которого соединен с выходом третьего элемента И, а выход соединен с входом задатчика модуля счета и S-входом третьего RS-триггера, прямой выход которого соединен с первым входом четвертого элемента И и инверсный выход подключен к первым входам пятого элемента И и элементов И группы из n элементов И, входам управления записью оперативных запоминающих устройств группы из n оперативных запоминающих устройств и управляющему входу управляемого ключа, выход которого соединен с первым входом третьего элемента И, адресные входы оперативных запоминающих устройств группы из n оперативных запоминающих устройств подключены к соответствующим выходам счетчика адресов.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Бессарабова А.А | |||

| Использование свойств М-последовательностей для повышения эффективности устройств их формирования | |||

| - Техника средств связи, сер | |||

| "Техника радиосвязи", 1985, N 7, с.107, рис.1а. | |||

Авторы

Даты

1995-02-27—Публикация

1989-02-06—Подача