Изобретение относится к импульсной технике и может быть использовано в радиолокации, радионавигации, телеметрии и импульсной радиосвязи, в измерительной и вычислительной технике.

Известна цифровая регулируемая линия задержки, выбранная в качестве прототипа, содержащая генератор тактовых импульсов (ГТИ), два элемента И, два счетчика, элемент И-НЕ, регистр, шины: кодовую, начальную установки, входную и выходную (авт. св. N 1661966, A1 H 03 H 9/30, H 03 K 5/153, 07.07.91).

Кодовая шина соединена с информационными входами регистра и одного из счетчиков непосредственно, а через регистр - с информационными входами второго счетчика. В обоих случаях счетчики используются как делители частоты с переменными коэффициентами деления (ДПКД).

Наряду с достоинствами (многофункциональность) регулируемая линия задержки имеет и недостатки:

период входного сигнала не может быть меньше времени задержки. После установки кода задержки в счетчиках и регистре (установка исходного состояния) и подачи входного импульса пока счетчики и регистр не завершат цикл работы и не будут установлены вновь в исходное состояние второй импульс подавать нельзя. Устройство на входной сигнал не реагирует, а это значит, что устройство имеет ограниченную разрешающую способность;

входной импульс подается логическим нулем и работа задержки зависит от длительности входного импульса. Если длительность импульса больше времени задержки, то на выходе этот импульс будет короче входного, т.е. происходит искажение информации;

относительная сложность схемы.

Задача изобретения - повышение разрешающей способности с одновременным упрощением устройства

Поставленная задача решается тем, что в цифровую регулируемую линию задержки, содержащую ГТИ, делитель частоты с переменным коэффициентом деления ДПКД, введено оперативное запоминающее устройство (ОЗУ), вход выбора кристалла которого соединен с первым выходом ГТИ, вход записи соединен со вторым выходом ГТИ и с тактовым входом ДПКД, информационные входы которого подключены к шине управления, а выход каждого триггера ДПКД соединен поразрядно с адресными входами ОЗУ, информационный вход и выход которого являются входом и выходом линии задержки соответственно.

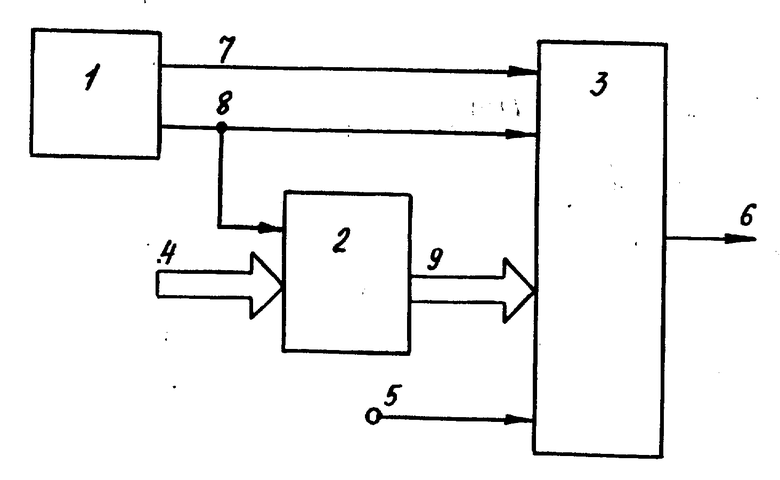

Функциональная схема устройства приведена на чертеже.

Устройство состоит из генератора тактовых импульсов ГТИ 1, ДПКД 2, ОЗУ 3, шины управления 4, информационного входа 5 и выхода 6, причем первый вход 7 ГТИ 1 соединен с входом "Выбор кристалла" ОЗУ 3, второй выход - с входом "Запись" ОЗУ 3 и тактовым входом ДПКД 2, информационные входы которого подключены к шине управления 4, а выход каждого триггера ДПКД 2 соединен с входом адресов строк и столбцов ОЗУ 3 поразрядно, информационный вход 5 и выход 6 ОЗУ 3 являются входом и выходом управляемой линии задержки соответственно

Сопоставительный анализ показывает, что заявленное техническое решение отличается от прототипа тем, что вместо двух управляющих счетчиков (делителей частоты с переменным коэффициентом деления - ДПКД) применен один, регистр заменен на ОЗУ, исключены два элемента И, элемент И - НЕ и шина начальной установки, изменены связи.

Поэтому данное техническое решение отвечает критерию "новизна".

При сравнении заявленного решения не только с прототипом, но и с другими техническими решениями в науке и технике, не обнаружены решения, обладающие сходными признаками.

Схема работает следующим образом.

Сигналы на входы "Выбор кристалла" и "Запись" должны быть сформированы и поданы в соответствии с ТУ на конкретный тип ОЗУ. Если используется ОЗУ с тремя состояниями на выходе, необходимо на выходе линии задержки использовать элемент хранения информации (например, триггер, конденсатор и др.).

Рассмотрим рабочий цикл линии задержки, который определяется коэффициентом деления (N) ДПКД 2.

После установки коэффициента деления в ДПКД 2 уровнем логической единицы по входу 8 считывается информация, записанная первым импульсом в предыдущем цикле работы, а уровнем логического нуля записывается информация, поступающая по входу 5 для считывания первым импульсом во втором цикле. Уровнем логической единицы второго импульса, поступающим по входу 8, считывается информация, записанная вторым импульсом в предыдущем цикле работы, а уровнем логического нуля записывается информация, поступающая по входу 5, для считывания во втором цикле и т.д. Уровнем логической единицы последнего N-го импульса считывания информации, записанная последним импульсом в предыдущем цикле, а уровнем логического нуля записывается информация для считывания последним импульсом в следующем цикле работы. Одновременно в ДПКД 2 устанавливается прежний (если не было изменений кода по шине 4 управления)) коэффициент деления.

Параллельно с поступлением каждого импульса записи в ОЗУ 3 с ДПКД 2 по шине 9 поступает код нового адреса, а по входу 7 - сигнал для выбора кристалла в ОЗУ 3. Таким образом задержка сигнала в ОЗУ 3 будет пропорциональна периоду импульса записи Tз и коэффициенту деления ДПКД 2

t = Tз•N.

Меняя коэффициент деления, можно получить задержку сигнала на выходе 6 относительно входа 5 от одного периода частоты записи до N, верхнее значение которого определяется емкостью ОЗУ.

На вход задержки можно подавать непрерывную последовательность импульсов с любой скважностью, а на выходе каждый импульс будет задержан относительно своего входного на Tз•N.

Для исключения появления на выходе искаженной информации частота импульсов записи должна быть не менее чем в 2 раза выше частоты входных импульсов.

При реализации линии задержки на микросхемах серии 533, 564 и 537 входную последовательность импульсов с частотой до 1 МГц можно задерживать т единиц микросекунд до сотен миллисекунд.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2004 |

|

RU2269866C2 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2008 |

|

RU2386208C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2002 |

|

RU2222101C2 |

| СПОСОБ КОДИРОВАНИЯ РЕЧЕВЫХ СИГНАЛОВ | 1993 |

|

RU2120700C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2030103C1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Цифровой умножитель частоты следования периодических импульсов | 1988 |

|

SU1596445A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2001 |

|

RU2214043C2 |

Изобретение относится к импульсной технике и может быть использовано в радиолокации, радионавигации, телеметрии и импульсной радиосвязи, в измерительной и вычислительной технике. Техническим результатом предложения является повышение разрешающей способности и упрощение линии задержки. Технический результат достигается тем, что в цифровую регулируемую линию задержки, содержащую генератор тактовых импульсов, делитель частоты с переменным коэффициентом деления, входную, выходную и кодовые шины, введено оперативное запоминающее устройство и генератор тактовых импульсов снабжен вторым выходом, который соединен с входом разрешения оперативного запоминающего устройства, вход записи/считывания которого соединен с первым выходом генератора тактовых импульсов и с тактовым входом делителя частоты с переменным коэффициентом деления, информационные входы которого подключены поразрядно к кодовым шинам, а выход каждого разряда делителя частоты с переменным коэффициентом деления соединен с соответствующим адресным входом оперативного запоминающего устройства, информационный вход которого подключен к входной шине, а выход подключен к выходной шине. 1 ил.

Цифровая регулируемая линия задержки, содержащая генератор тактовых импульсов, делитель частоты с переменным коэффициентом деления, входную, выходную и кодовые шины, отличающаяся тем, что в нее введено оперативное запоминающее устройство и генератор тактовых импульсов снабжен вторым выходом, который соединен с входом разрешения оперативного запоминающего устройства, вход записи/считывания которого соединен с первым выходом генератора тактовых импульсов и с тактовым входом делителя частоты с переменным коэффициентом деления, информационные входы которого подключены поразрядно к кодовым шинам, а выход каждого разряда делителя частоты с переменным коэффициентом деления соединен с соответствующим адресным входом оперативного запоминающего устройства, информационный вход которого подключен к входной шине, а выход подключен к выходной шине.

| SU, авторске свидетельство, 1661996, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-04-10—Публикация

1993-06-08—Подача