Iti ю

ел d5

СП

СлЭ

записывается ла место вызванного в первый буферный регистр, затем следующее по порядку число из блока 6 вызывается во второй буферный регистр, а на его место записывается число из первого буферного регистра, затем по следующему адресу число вызывается из блока 6 в первый буферный регистр.

а на его место записывается число из второго буферного регистра и т.д. Таким образом, осуществляется сдвиг всей информации в блоке 6 на одну единицу адреса. Последнее число (самое меньшее) не записывается в блок 6 и отбрасывается. 1 з,п,ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для ввода информации | 1982 |

|

SU1056175A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки сигналов радио- и гидролокаторов, системах связи и др. Цель изобретения - повышение быстродействия при выводе информации без нарушения собственного режима работы устройства. Устройство содержит блок управления 2, блок сравнения 3, буферные регистры 5, 10, оперативный запоминаюпи{й блок б, счетчик 7, генератор тактовых импульсов 8, коммутаторы 4, 9. Анализируемое число последовательно сравнивается с числами, записанными в оперативном запоминаюшем блоке 6, причем число из блока 6 вызьшается на первый буферный регистр 5. Блок 6 опрашивается по порядку следования адреса, начиная с самых больших чисел. Как только анализируемое число оказалось больше очередного числа из блока 6, порядок работы устройст ва меняется: анализируемое число о. & (Л

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки сигна лов радио- и гидролокаторов, системах связи и др.

Цель изобретения - повышение быстродействия -при выводе информации без нарушения собственного режима работы устройства.

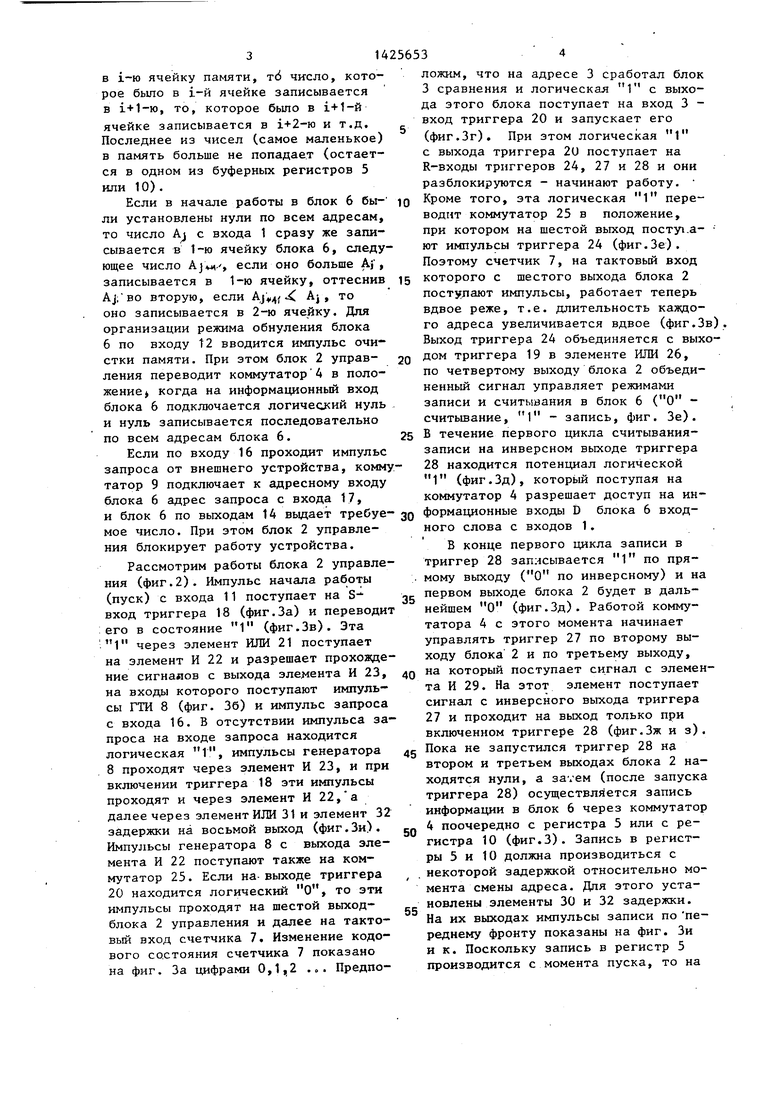

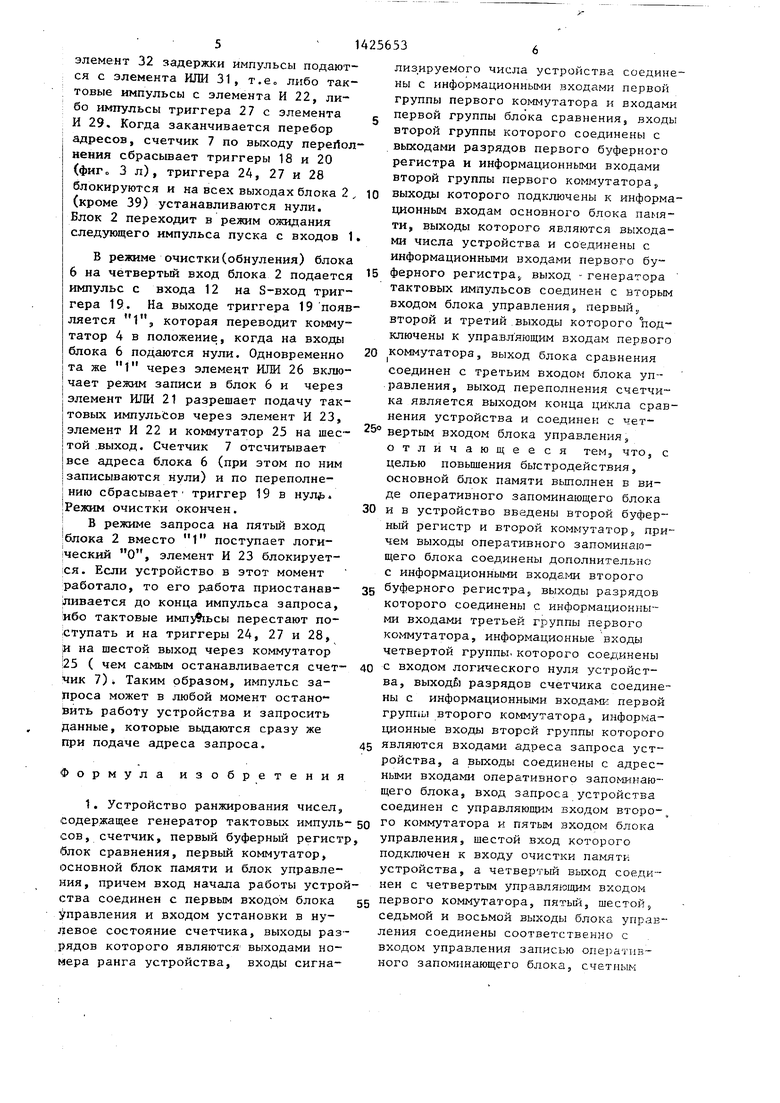

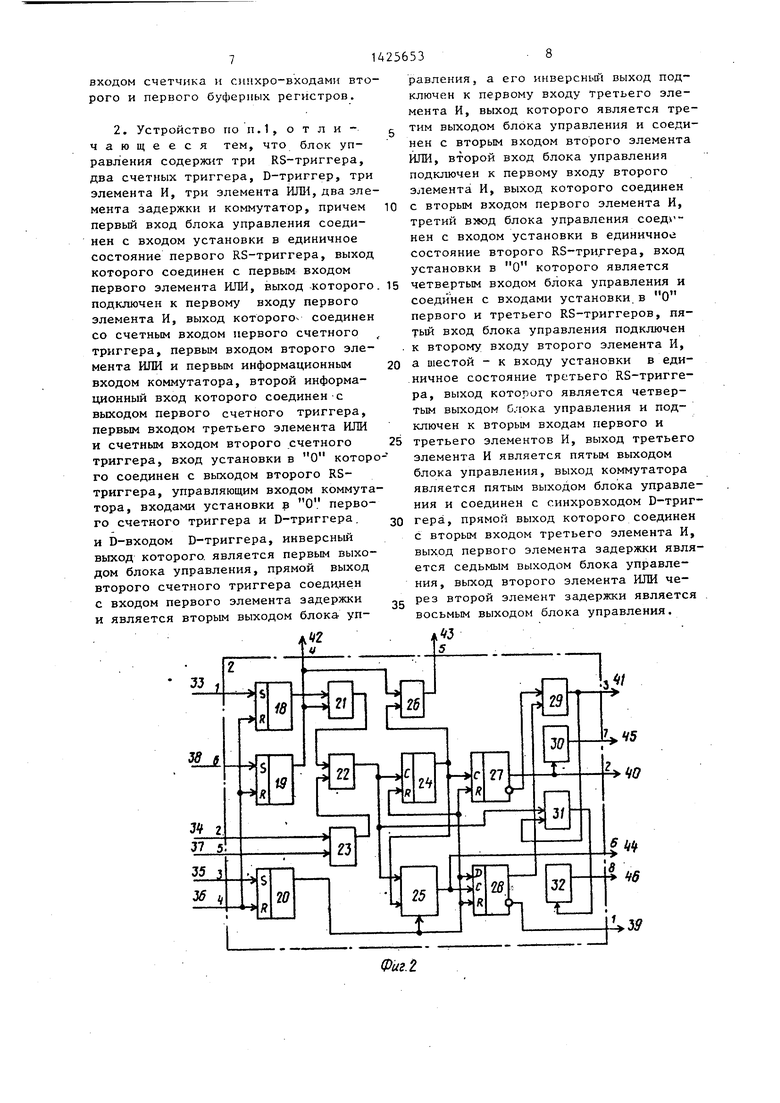

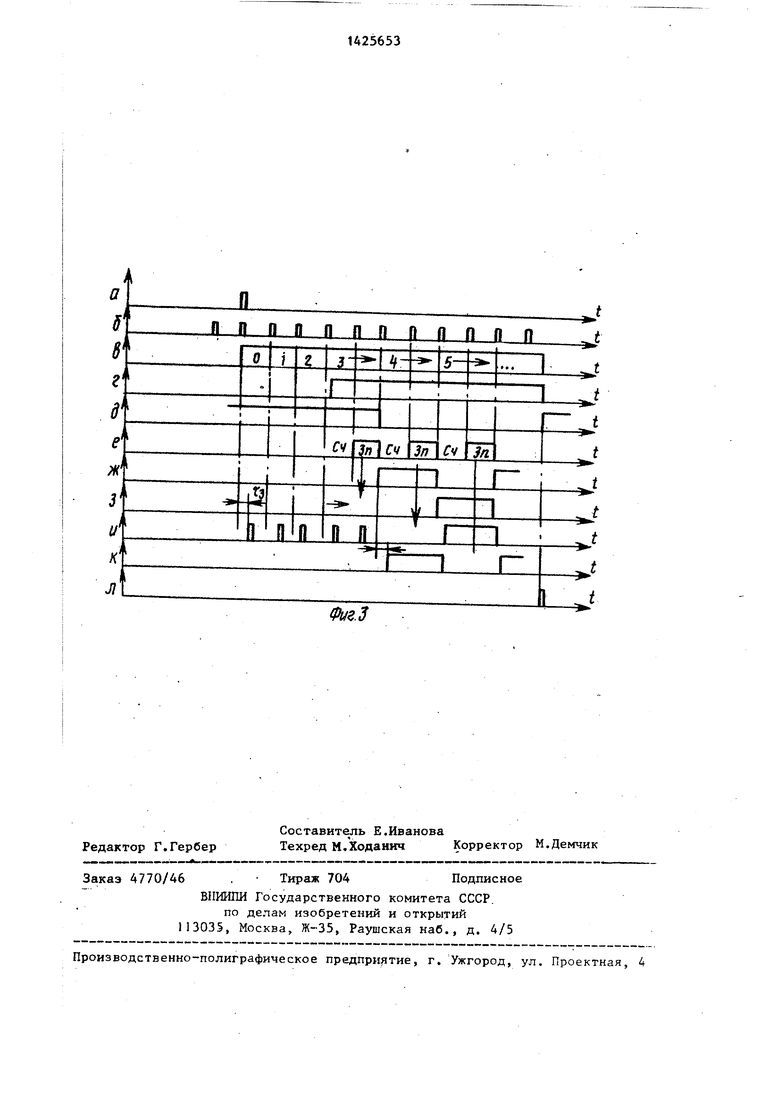

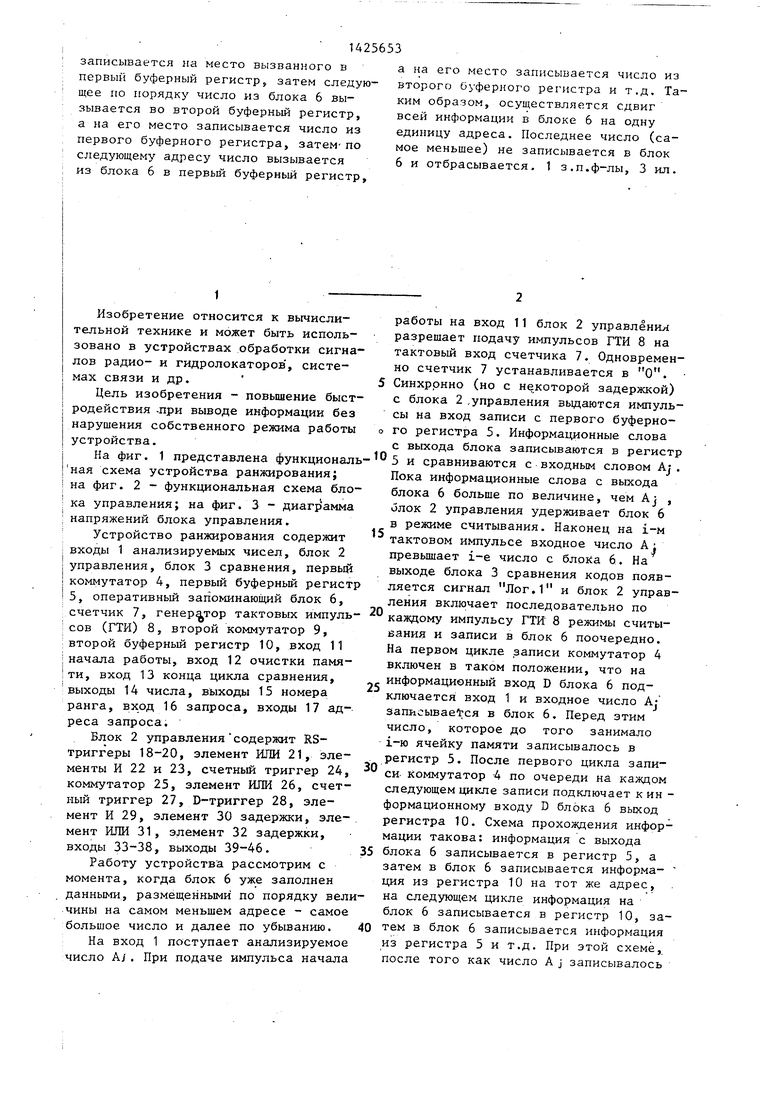

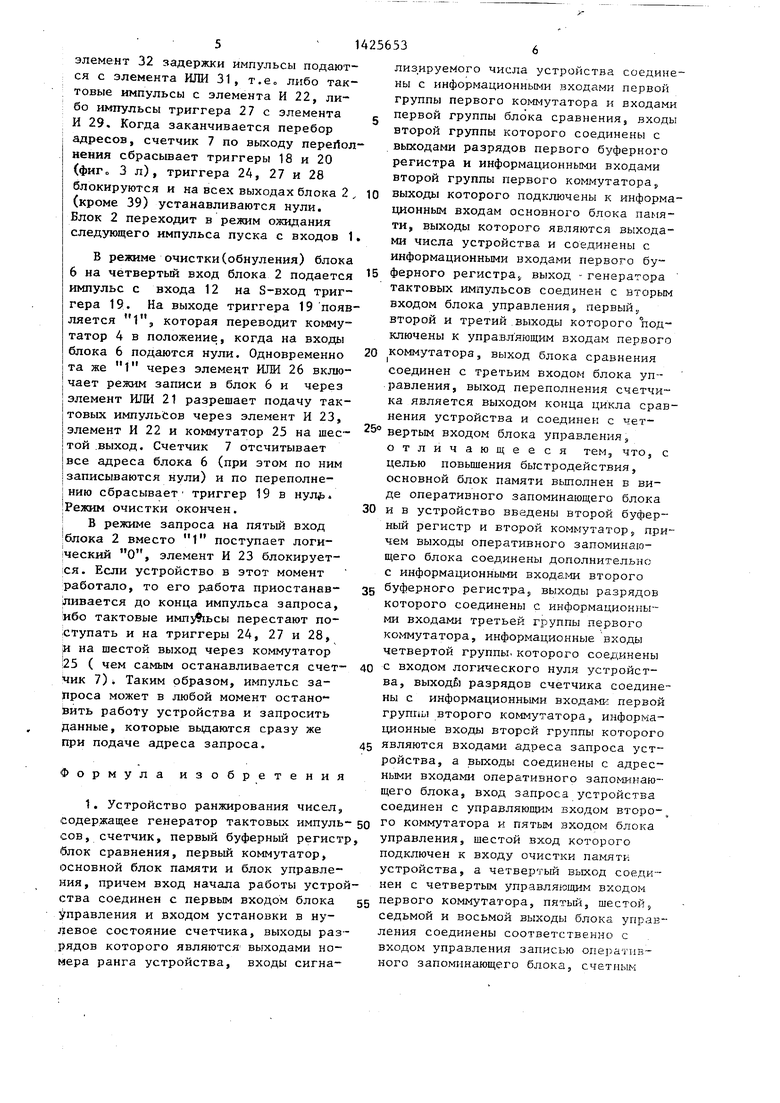

На фиг. 1 представлена функциональ ная схема устройства ранжирования; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - диагр амма напряжений блока управления.

Устройство ранжирования содержит : входы 1 анализируемых чисел, блок 2 I управления, блок 3 сравнения, первый I коммутатор 4, первый буферньй регистр I 5, оперативный запоминающий блок 6,

счетчик 7, генератор тактовых импуль сов (ГТИ) 8, второй коммутатор 9, iвторой буферный регистр 10, вход 11 I начала работы, вход 12 очистки памя- 1ти, вход 13 конца цикла сравнения, выходы 14 числа, выходы 15 номера ранга, вход 16 запроса, входы 17 адреса запроса.

Блок 2 управления содержит RS- тригг еры 18-20, элемент ИЛИ 21, элементы И 22 и 23, счетный триггер 24, коммутатор 25, элемент ИЛИ 26, счетный триггер 27, D-триггер 28, элемент И 29, элемент 30 задержки, элемент ИЛИ 31, элемент 32 задержки, входы 33-38, выходы 39-46.

Работу устройства рассмотрим с момента, когда блок 6 уже заполнен данными, размещенными по порядку вел чины на самом меньшем адресе - самое большое число и далее по убыванию.

На вход 1 поступает анализируемое число А/. При подаче импульса начала

10

15

20

25

30

35

40

работы на вход 11 блок 2 управления разрешает подачу импульсов ГТИ 8 на тактовый вход счетчика 7. Одновременно счетчик 7 устанавливается в О. Синхронно (но с некоторой задержкой) с блока 2 .управления выдаются импульсы на вход записи с первого буферного регистра 5. Информационные слова с выхода блока записываются в регистр 5 и сравниваются с входным словом AJ. Пока информационные слова с выхода блока 6 больше по величине, чем AJ , олок 2 управления удерживает блок 6 в режиме считывания. Наконец на i-м тактовом импульсе входное число А; превьшает i-e число с блока 6. На выходе блока 3 сравнения кодов появляется сигнал Лог.1 и блок 2 управления включает последовательно по каждому импульсу ГТИ 8 режимы считывания и записи в блок 6 поочередно. На первом цикле записи коммутатор 4 включен в таком положении, что на информационный вход D блока 6 подключается вход 1 и входное число А; Записывае1;ся в блок 6. Перед этим число, которое до того занимало i-ю ячейку памяти записывалось в регистр 5. После первого цикла записи коммутатор -4 по очереди на каждом следующем цикле записи подключает к ин - формационному входу D блока 6 выход регистра 10. Схема прохождения информации такова: информация с выхода блока 6 записывается в регистр 5, а затем в блок 6 записывается информация из регистра 10 на тот же адрес, на следующем цикле информация на блок 6 записывается в регистр 10, затем в блок 6 записывается информация из регистра 5 и т.д. При этой схеме, после того как число А j записывалось

314

в i-ю ячейку памяти, т6 число, которое было в i-й ячейке записывается в i+1-ю, то, которое было в i+1-й ячейке записывается в i+2-ю и т.д. Последнее из чисел (самое маленькое) в память больше не попадает (остается в одном из буферных регистров 5 или 10).

Если в начале работы в блок 6 бы- ли установлены нули по всем адресам, то число А с входа 1 сразу же записывается в 1-ю ячейку блока 6, следующее число Ajvn , если оно больше А} , записывается в 1-ю ячейку, оттеснив Aj; BO вторую, если Aj,,f Aj , то оно записывается в 2-ю ячейку. Для организации режима обнуления блока 6 по входу 12 вводится импульс очистки памяти. При этом блок 2 управления переводит коммутатор 4 в положение j когда на информационный вход блока 6 подключается логичео ий нуль и нуль записывается последовательно по всем адресам блока 6.

Если по входу 16 проходит импульс запроса от внешнего устройства, коммутатор 9 подключает к адресному входу

с выхода триггера 20 поступает на R-входы триггеров 24, 27 и 28 и они разблокируются - начинают работу. Кроме того, эта логическая 1 пере водит коммутатор 25 в положение, при котором на шестой выход nocTyi.a ют импульсы триггера 24 (фиг.Зе). Поэтому счетчик 7, на тактовый вход которого с шестого выхода блока 2 постилают импульсы, работает теперь вдвое реже, т.е. длительность каждо го адреса увеличивается вдвое (фиг. Выход триггера 24 объединяется с вы дом триггера 19 в элементе ИЛИ 26, по четвертому выходу блока 2 объеди ненный сигнал управляет режимами записи и считывания в блок 6 (О - считьшание, 1 - запись, фиг. Зе). 25 В течение первого цикла считывания- записи на инверсном вьпсоде триггера 28 находится потенциал логической 1 (фиг.Зд), который поступая на коммутатор 4 разрешает доступ на ин

блока 6 адрес запроса с входа 17, и блок 6 по выходам 14 выдает требуе- зо Формационные входы D блока 6 входное число. При этом блок 2 управле- ного слова с входов 1, ния блокирует работу устройства. в конце первого цикла записи в

Рассмотрим работы блока 2 управле- триггер 28 записывается 1 ния (фиг.2). Импульс начала работы

по прямому выходу (О по инверсному) и на

40

(пуск) с входа 11 поступает на S- gg вход триггера 18 (фиг.За) и переводит его в состояние 1 (фиг.Зв). Эта 1 через элемент ИЛИ 21 поступает на элемент VI 22 я разрешает прохождение сигналов с выхода эле 1ента И 23, на входы которого поступают импульсы ГТИ 8 (фиг. Зб) и импульс запроса с входа 16. В отсутствии импульса запроса на входе запроса находится логическая 1, импульсы генератора 8 проходят через элемент И 23, и при включении триггера 18 эти импульсы проходят и через элемент И 22, а далее через элемент ИЛИ 31 и элемент 32 задержки на восьмой выход (фиг.Зи). Импульсы генератора 8 с выхода элемента И 22 поступают также на коммутатор 25. Если на- выходе триггера 20 находится логический О, то эти импульсы проходят на шестой выход- блока 2 управления и далее на тактовый вход счетчика 7. Изменение кодового состояния счетчика 7 показано на фиг. За цифрами 0,1,2 .о. Предпопервом выходе блока 2 будет в дальнейшем О (фиг.Зд). Работой коммутатора 4 с этого момента начинает управлять триггер 27 по второму выходу блока 2 и по третьему выходу, на который поступает сигнал с элемен та И 29. На этот элемент поступает сигнал с инверсного выхода триггера 27 и проходит на выход только при включенном триггере 28 (фиг.Зж и з) с Пока не запустился триггер 28 на

втором и третьем выходах блока 2 находятся нули, а загем (после запуска триггера 28) осуществляется запись информации в блок 6 через коммутатор 4 поочередно с регистра 5 или с регистра 10 (фиг.З). Запись в регистры 5 и 10 должна производиться с некоторой задержкой относительно момента смены адреса. Для этого установлены элементы 30 и 32 задержки. На их выходах импульсы записи по переднему фронту показаны на фиг. Зи и к. Поскольку запись в регистр 5 производится с момента пуска, то на

50

55

ложим, что на адресе 3 сработал блок 3 сравнения и логическая 1 с выхода этого блока поступает на вход 3 - вход триггера 20 и запускает его (фиг.Зг), При этом логическая 1

10

15

с выхода триггера 20 поступает на R-входы триггеров 24, 27 и 28 и они разблокируются - начинают работу. Кроме того, эта логическая 1 переводит коммутатор 25 в положение, при котором на шестой выход nocTyi.a- ют импульсы триггера 24 (фиг.Зе). Поэтому счетчик 7, на тактовый вход которого с шестого выхода блока 2 постилают импульсы, работает теперь вдвое реже, т.е. длительность каждого адреса увеличивается вдвое (фиг.Зв). Выход триггера 24 объединяется с выходом триггера 19 в элементе ИЛИ 26, по четвертому выходу блока 2 объединенный сигнал управляет режимами записи и считывания в блок 6 (О - считьшание, 1 - запись, фиг. Зе). 25 В течение первого цикла считывания- записи на инверсном вьпсоде триггера 28 находится потенциал логической 1 (фиг.Зд), который поступая на коммутатор 4 разрешает доступ на ин0

зо Формационные входы D блока 6 входного слова с входов 1, в конце первого цикла записи в

триггер 28 записывается 1

по прямому выходу (О по инверсному) и на

первом выходе блока 2 будет в дальнейшем О (фиг.Зд). Работой коммутатора 4 с этого момента начинает управлять триггер 27 по второму выходу блока 2 и по третьему выходу, на который поступает сигнал с элемента И 29. На этот элемент поступает сигнал с инверсного выхода триггера 27 и проходит на выход только при включенном триггере 28 (фиг.Зж и з). Пока не запустился триггер 28 на

втором и третьем выходах блока 2 находятся нули, а загем (после запуска триггера 28) осуществляется запись информации в блок 6 через коммутатор 4 поочередно с регистра 5 или с регистра 10 (фиг.З). Запись в регистры 5 и 10 должна производиться с некоторой задержкой относительно момента смены адреса. Для этого установлены элементы 30 и 32 задержки. На их выходах импульсы записи по переднему фронту показаны на фиг. Зи и к. Поскольку запись в регистр 5 производится с момента пуска, то на

5

элемент 32 задержки импульсы подаюся с элемента ИЛИ 31, т.е либо татовые импульсы с элемента И 22, либо импульсы триггера 27 с элемента И 29. Когда заканчивается перебор адресов, счетчик 7 по выходу перей нения сбрасьшает триггеры 18 и 20 (фиго 3 л), триггера 24, 27 и 28 блокируются и на всех выходах блока (кроме 39) устанавливаются нули. Блок 2 переходит в режим ожидания следующего импульса пуска с входов

В режиме очистки(обнуления) блока 6 на четвертый вход блока 2 подается импульс с входа 12 на S-вход триггера 19. На выходе триггера 19 появляется 1, которая переводит коммутатор 4 в положение, когда на входы блока 6 подаются нули. Одновременно та же 1 через элемент ИЛИ 26 включает режим записи в блок 6 и через элемент ИЛИ 21 разрешает подачу так- Iтовых импульйов через элемент И 23, элемент И 22 и коммутатор 25 на шес I той.выход. Счетчик 7 отсчитывает 1все адреса блока 6 (при этом по ним I записываются нули) и по переполне- нию сбрасывает триггер 19 в нул#з. 1Режим очистки окончен. : в режиме запроса на пятый вход |блока 2 вместо 1 поступает логи- ческий О, элемент И 23 блокирует- :ся. Если устройство в этот момент работало, то его работа приостанавливается до конца импульса запроса, ибо тактовые имп 91ьсы перестают по- :ступать и на триггеры 24, 27 и 28, на шестой выход через коммутатор |25 ( чем самым останавливается счет чик 7)i Таким образом, импульс запроса может в любой момент остано вить работу устройства и запросить данные, которые выдаю1тся сразу же при подаче адреса запроса.

ормула изобретения

лизируемого числа устройства соединены с информационными входами первой группы первого коммутатора и входами первой группы блока сравнения, входы второй группы которого соединены с выходами разрядов первого буферного регистра и информационными входами второй группы первого коммутаторар выходы которого подключены к информационным входам основного блока памяти, выходы которого являются выходами числа устройства и соединены с информационными входами первого буферного регистра;, выход - генератора тактовых импульсов соединен с вторым входом блока управления, первыйj, второй и третий.выходы которого подключены к управляющим входам первого коммутатора, выход блока сравнения соединен с третьим входом блока управления, выход переполнения счетчика является выходом конца цикла сравнения устройства и соединен с четвертым входом блока управленияj

отличающееся тем, что, с целью повышения быстродействия, основной блок памяти вьшолнен в виде оперативного запоминающего блока

и в устройство введены второй буферный регистр и второй коммутатор, причем выходы оперативного запоминающего блока соединены дополнительно с информационными входами второго

буферного регистра; выходы разрядов которого соединены с информационными входами третьей группы первого коммутатора, информационные входы четвертой группы.которого соединены с входом логического нуля устройст

ва, ВЫХОДЕ) разрядов счетчика соединены с информационными входами первой группы второго коммутатора, информационные входы второй группы которого являются входами адреса запроса устройства, а выходы соединены с адресными входами оперативного запоминающего блока, вход запроса устройства соединен с управляющим входом второ-„ го коммутатора и пятым входом блока управления, шестой вход которого подключен к входу очистки памяти устройства, а четвертый выход соединен с четвертым управляющим входом первого коммутатора, пятый, шестой седьмой и восьмой выходы блока управления соединены соответственно с входом управления записью оперативного запоминающего блока, счетным

входом счетчика и сямхро-входами второго и первого буферных регистров.

равления, а его инверсный выход подключен к первому входу третьего элемента И, выход которого является тре тим выходом блока управления и соеди нен с вторым входом второго элемента ИЛИ, второй вход блока управления подключен к первому входу второго элемента И, выход которого соединен с вторым входом первого элемента И, третий блока управления нен с входом установки в единичное состояние второго RS-триггера, вход О

установки в и которого является первого элемента ИЛИ, выход которого. 15 четвертым входом блока управления и

О

подключен к первому входу первого элемента И, выход которого- соединен со счетным входом первого счетного триггера, первым входом второго элемента ИЛИ и первым информационным входом коммутатора, второй информационный вход которого соединен-с выходом первого счетного триггера, первым входом третьего элемента ИЛИ и счетным входом второго счетного триггера, вход установки в О которого соединен с выходом второго RS- триггера, управляющим входом коммутатора, входами установки в О первого счетного триггера и D-триггера. и D-входом D-триггера, инверсный выход которого, является первым выходом блока управления, прямой выход второго счетного триггера соединен с входом первого элемента задержки и является вторым выходом блока уп20

соединен с входами установки.в первого и третьего RS-триггеров, пятый вход блока управления подключен к второму входу второго элемента И, а шестой - к входу установки в единичное состояние третьего RS-триггера, выход которого является четвертым выходом блока управления и подключен к вторым входам первого и 25 третьего элементов И, выход третьего элемента И является пятым выходом блока управления, выход коммутатора является пятым выходом блока управле ния и соединен с синхровходом D-триг гера, прямой выход которого соединен с вторым входом третьего элемента И выход первого элемента эадержки явля ется седьмым выходом блока управления, выход второго элемента ИЛИ через второй элемент задержки является восьмым выходом блока управления.

30

35

равления, а его инверсный выход подключен к первому входу третьего элемента И, выход которого является тре- тим выходом блока управления и соединен с вторым входом второго элемента ИЛИ, второй вход блока управления подключен к первому входу второго элемента И, выход которого соединен с вторым входом первого элемента И, третий блока управления нен с входом установки в единичное состояние второго RS-триггера, вход О

установки в и которого является четвертым входом блока управления и

О

0

соединен с входами установки.в первого и третьего RS-триггеров, пятый вход блока управления подключен к второму входу второго элемента И, а шестой - к входу установки в единичное состояние третьего RS-триггера, выход которого является четвертым выходом блока управления и подключен к вторым входам первого и 5 третьего элементов И, выход третьего элемента И является пятым выходом блока управления, выход коммутатора является пятым выходом блока управления и соединен с синхровходом D-триггера, прямой выход которого соединен с вторым входом третьего элемента И, выход первого элемента эадержки является седьмым выходом блока управления, выход второго элемента ИЛИ через второй элемент задержки является восьмым выходом блока управления.

0

5

| Патент США № 3829664, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство ранжирования экстремальных значений | 1982 |

|

SU1049899A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-01-12—Подача