Изобретение относится к автоматике и вычислительной технике и может использоваться для построения многооперандных быстродействующих арифметических устройств и синтеза на их основе встроенных средств технического контроля и диагностики.

Известно устройство для суммирования четырех одноразрядных двоичных чисел, содержащее четыре элемента сложения по модулю два и четыре элемента И. На выходах устройства реализуются логические функции S = (X1⊕ X4) ⊕ (X2⊕ X3); соответствующая сигналу суммы;P1 = X1X2X3X4, соответствующая сигналу старшего переноса; P2= (X1⊕ X4) (X2⊕ X3)⊕ X1X4⊕ X2X3, соответствующая сигналу младшего переноса [1].

Известен параллельный счетчик, состоящий из m-уровней (где m=[log2n]+1= 4; n= 8 - количество входных шин полусумматоров. Количество полусумматоров на каждом уровне определяется по формуле

Ki=n-i, где i =  =

=  . .

. .

Общее количество полусумматоров в счетчике определяется по формуле

N = (n-i)

(n-i)

На оба входа первого полусумматора и первые входы всех полусумматоров первого уровня поступает входной вектор Х=(Х1,Х2,Х3,...,Х8), который необходимо преобразовать в код количества единиц.

Вторые входы полусумматоров, кроме первого, первого уровня соединены с первыми выходами (сигналами сумм) предыдущих полусумматоров этого же уровня. Вторые выходы первых двух полусумматоров первого уровня соединены с обоими входами первого полусумматора группы полусумматоров второго уровня, а первые входы остальных полусумматоров второго уровня соединены с вторыми выходами (сигналы переноса) полусумматоров первого уровня. Первые входы полусумматоров второго уровня соединены с вторыми входами последующих полусумматоров этого же уровня. Соединение полусумматоров последующих уровней идентична соединениям предыдущих уровней. Первые выходы (сигналы суммы) последних полусумматоров всех уровней образуют выход устройства, на котором формируется код количества единиц от входных двоичных переменных Х=(Х1,Х2, Х3,Х4,Х5,Х6,Х7,Х8) [2].

Известно устройство, осуществляющее определение количества сигналов на входах устройства, количество которых, в частности, может быть равно восьми, и выдачу его на выходы устройства в двоичном коде, т.е. устройство для определения количества единиц в двоичном восьмиразрядном числе. Это устройство содержит, в частности, два шифратора (два четырехвходовых модуля преобразователя входных переменных в двоичный код количества единиц) и сумматор, входы которого соединены с выходами указанных шифраторов, а выход является выходом устройства [3].

Цель изобретения - сокращение аппаратных затрат.

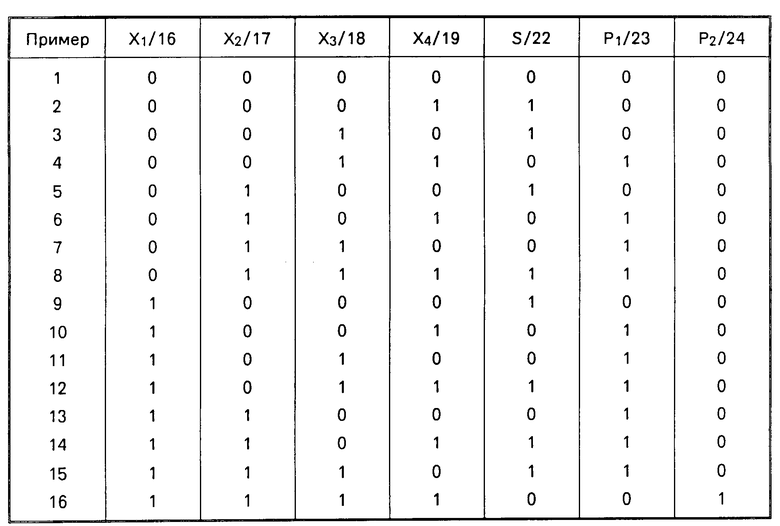

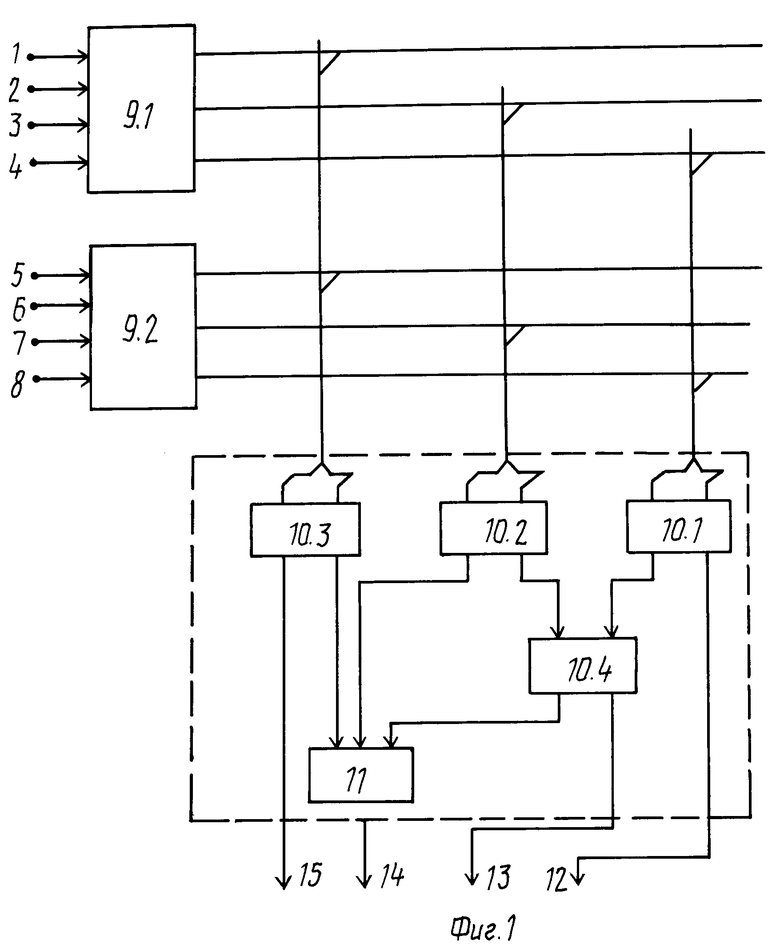

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема преобразователя входных переменных в код количества единиц.

Устройство содержит входы 1-8, два преобразователя 9.1 и 9.2 входных переменных в код количества единиц, полусумматоры 10.1, 10.2, 10.3, 10.4, элемент ИЛИ 11, образующие сумматор, и выходы 12-15. Преобразователь 9.1 (9.2) содержит входы 16-19, полусумматоры 20.1, 20.2, 20.3, 20.4, элемент ИЛИ 21, выходы 22-24 (фиг. 2).

Устройство работает следующим образом.

На входы 1-4 и 5-8 устройства подаются переменные Х1, Х2, Х3, Х4, Х5, Х6, Х7, Х8 соответственно. На выходах каждого преобразователя 9.1 и 9.2 реализуются логические функции : на первом выходе S = (X1⊕ X2) ⊕ (X3⊕ X4), соответствующая сигналу суммы; на втором выходе P1= (X1⊕ X2)(X3⊕ X4)∨(X1X2⊕ X3X4) соответствующая сигналу младшего переноса; на третьем выходе Р2= Х1,Х2,Х3,Х4, соответствующая сигналу старшего переноса. Равновесные выходы преобразователей 9.1 и 9.2 попарно соединены, начиная с выходов сумм с первым, вторым и третьим полусумматорами 10.1, 10.2 и 10.3. Выход переноса первого полусумматора 10.1 и выход суммы второго полусумматора 10.2 соединены с входом четвертого полусумматора 10.4. Выходы переносов второго, четвертого и выход суммы третьего полусумматоров 10.2, 10.4, 10.3 соединены с соответствующими входами элемента ИЛИ 11. Выходы сумм первого и четвертого полусумматоров 10.1 и 10.4, выход элемента ИЛИ 11 и выход переноса третьего полусумматора 10.3 образуют соответственно разрядные выходы 12, 13, 14 и 15, при этом выход 12 устройства является младшим.

П р и м е р. Допустим, что на входы 1-8 поступает вектор переменных Х= Х1, Х2, Х3, Х4,Х5,Х6,Х7,Х8=0111 1001. При этом на вход преобразователя 9.1 поступает вектор Х/2=Х1,Х2,Х3,Х4=0111, а на преобразователе 9.2-1001. На их выходах вырабатываются сигналы 011 и 010 соответственно.

На входы первого полусумматора 10.1 поступает код 10 второго полусумматора 10.2 - код 11; третьего полусумматора 10.3- код 00. По выходу переноса первого полусумматора 10.1 и выходу суммы второго переноса полусумматора 10.2 на вход четвертого полусумматора 10.4 поступает код 00. По выходу суммы третьего полусумматора 10.3, выходу переноса второго и выходу четвертого полусумматоров 10.2 и 10.4, на вход элемента ИЛИ 11 поступает код 010. На выходах переноса третьего полусумматора 10.3, элемента ИЛИ 11, суммы четвертого полусумматора 10.4 и суммы первого полусумматора 10.1 вырабатывается результат вычисления 0101, который поступает на выходы 15, 14, 13 и 12 устройства соответственно.

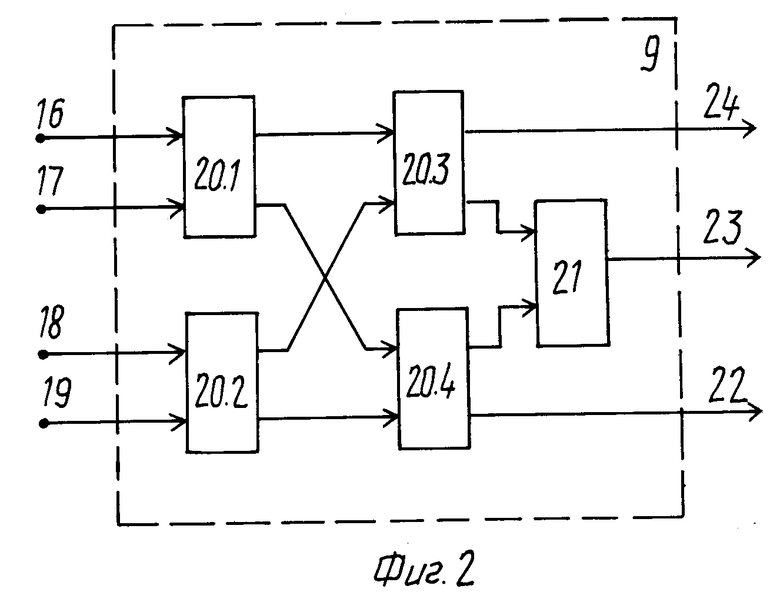

Преобразователь 9.1 (9.2) функционирует в соответствии с нижеприведенной таблицей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовой сумматор по модулю два | 2015 |

|

RU2614370C1 |

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1688405A1 |

| СУММАТОР КОДОВ "1 ИЗ N" | 1997 |

|

RU2129730C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ | 2007 |

|

RU2356165C1 |

| УСТРОЙСТВО ДЛЯ ГЕНЕРИРОВАНИЯ МАСКИ КВАЗИОРТОГОНАЛЬНОГО КОДА В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 1999 |

|

RU2200366C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Многоканальный цифровой фильтр | 1990 |

|

SU1751781A1 |

| Устройство для определения координаты локомотива | 1990 |

|

SU1832093A1 |

| Цифровой фильтр | 1986 |

|

SU1348981A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться для построения многооперандных быстродействующих арифметических устройств и синтеза на их основе встроенных средств технологического контроля и диагностики. Устройство содержит два преобразователя входных переменных в код количества единиц, четыре полусумматора и элемент ИЛИ. При этом каждый преобразователь содержит четыре полусумматора и элемент ИЛИ. 1 з.п. ф-лы, 2 ил., 1 табл.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для определения количества единиц в двоичном числе | 1984 |

|

SU1275778A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1995-03-10—Публикация

1991-07-03—Подача