четвертого элементов И, вход элемента задержки соединен с первым управляющим входом одноразрядного сумматора и первыми входами пятого и девятого элементов И, выход элемента задержки подключен к входу четвертого элемента НЕ, выход которого соединен с четвертыми входами элементов И с первого по четвертьи и с третьими входами элементов И с шестого по восьмой, вторые входы пятого и девятого элементов И соединены с вторым управляющим входом одноразрядного сумматора, третьи входы пятого и девятого элементов И соединены с выходами соответственно первого и второго элементов ИЛИ, первые управляющие входы

6064

одноразрядных сумматоров р-й и 2р-й строк матрицы соединены соответственно с первым и вторым тактовыми входами устройства, вторые управляющие входы одноразрядных сумматоров р-й и 2р-й строк матрицы соединены соответственно с первым и вторым входами сброса устройства, выходы переноса одноразрядных сумматоров 2р-й строки матрицы соединены с вторыми информационными входами соответствующих одноразрядных сумматоров первой строки матрицы, выходы одноразрядных сумматоров с второго по п-и и 2р-й строки матрицы соединеныс третьими входами одноразрядных сумматоров соответственно с первого по(п-1) -ипервой строки матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1501047A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Устройство для умножения | 1987 |

|

SU1501045A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| СУММАТОР КОДОВ "1 ИЗ N" | 1997 |

|

RU2129730C1 |

| Многоканальный цифровой фильтр | 1990 |

|

SU1751781A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

| Устройство для умножения 12N-разрядных двоичных чисел | 1988 |

|

SU1589271A1 |

УСТРОЙСТВО Гщя , содержащее матрицу элементов И и матрицу одноразрядных сумматоров, причем первые входы элементов и; -го столбца матридь

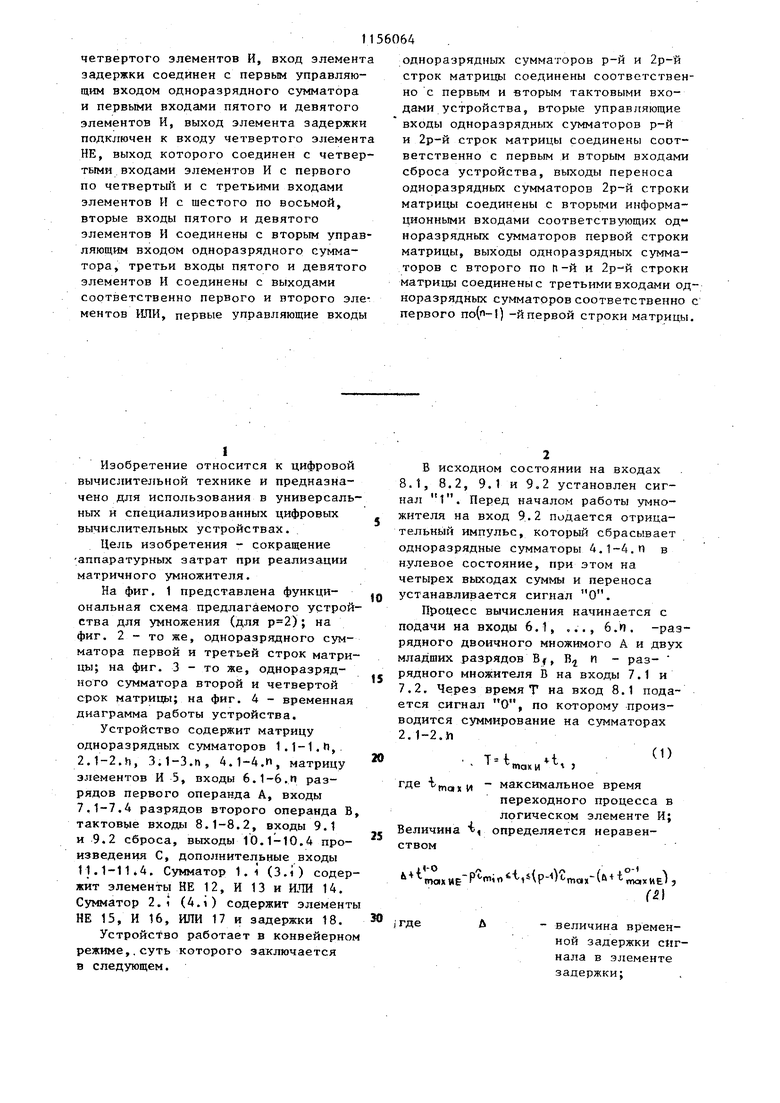

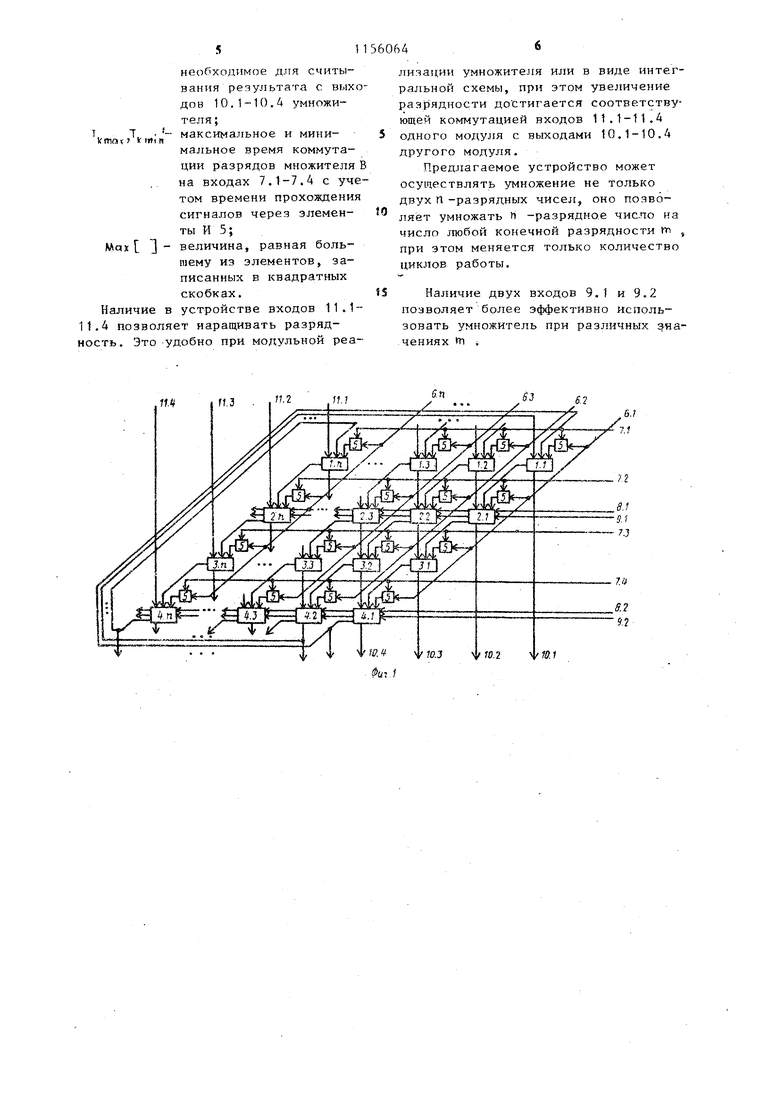

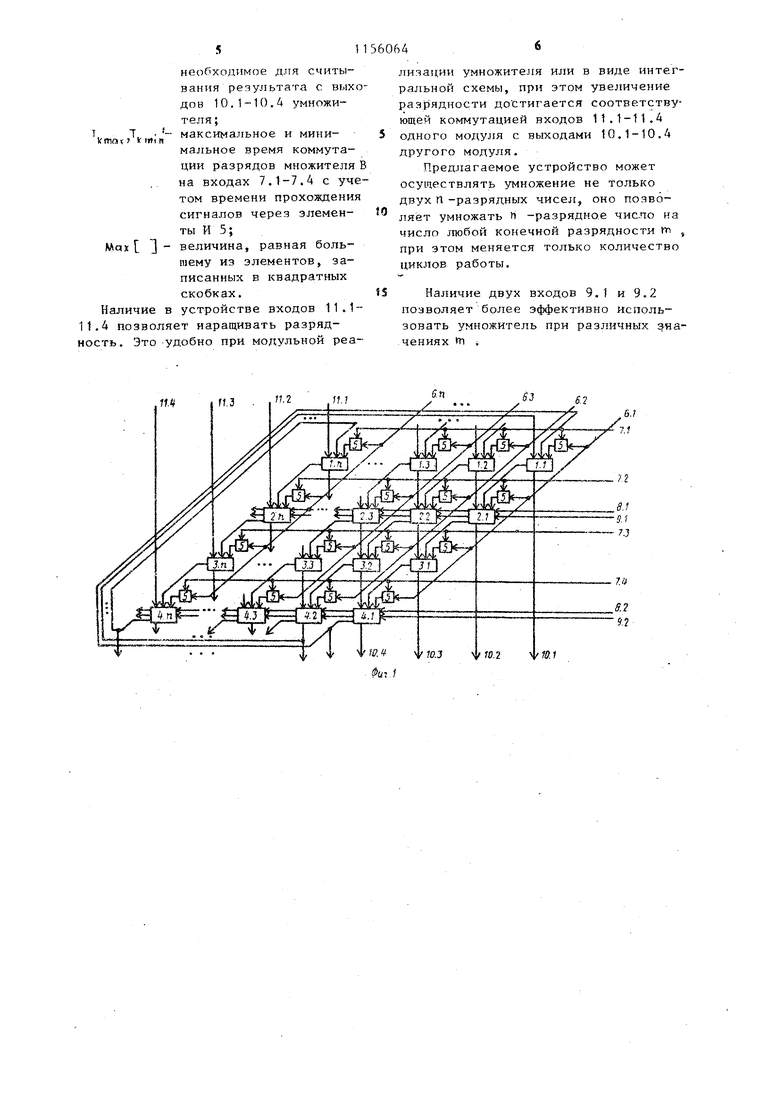

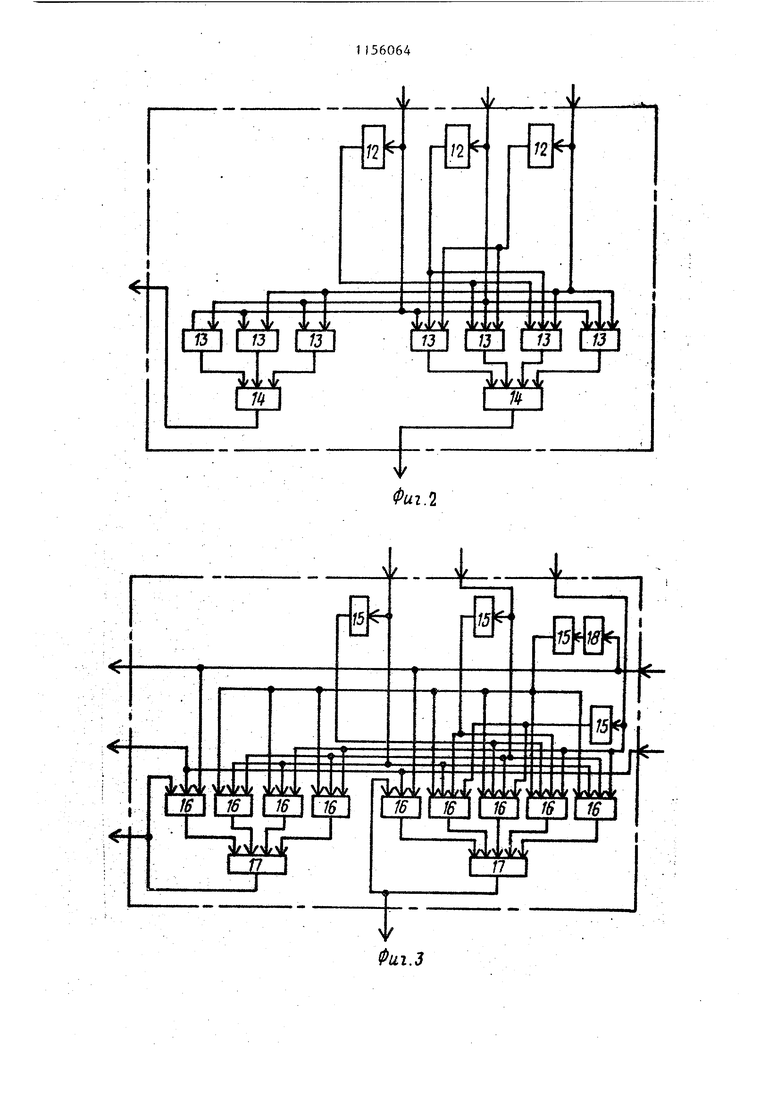

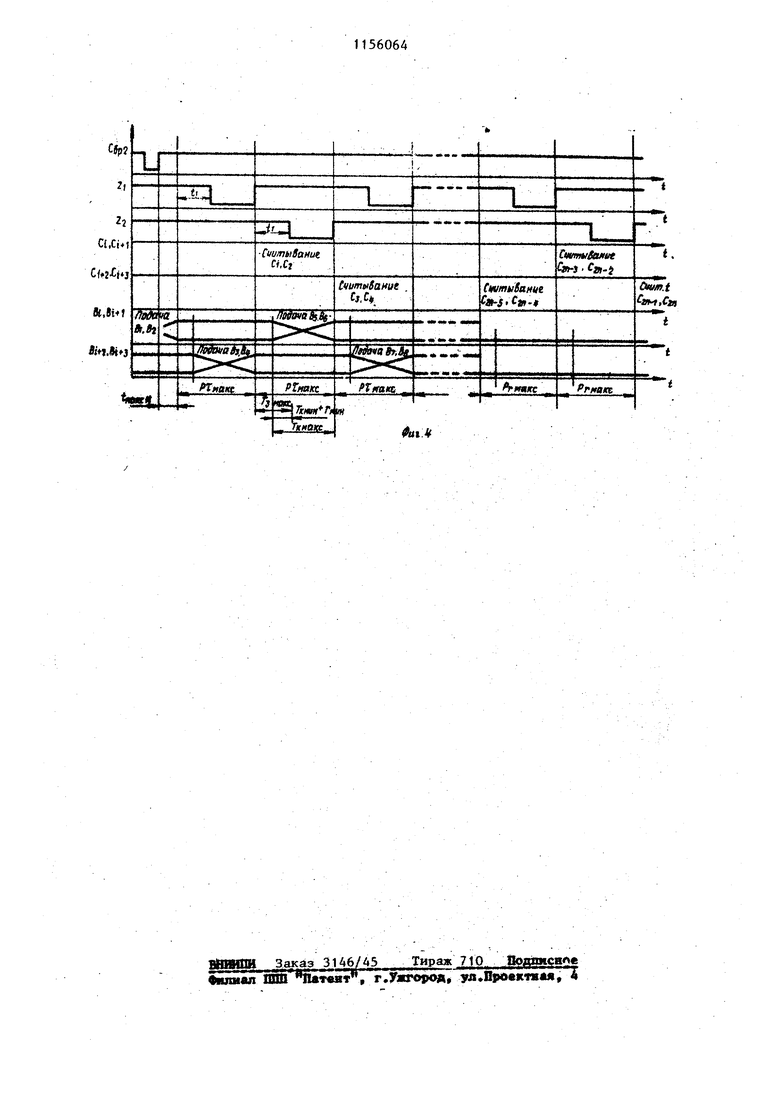

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсаль ных и специализированных цифровых вычислительных устройствах. Цель изобретения - сокращение аппаратурных затрат при реализации матричного умножителя. На фиг, 1 представлена функциональная схема предлагаемого устрой ства для умножения (для ); на фиг. 2 - то же, одноразрядного сумматора первой и третьей строк матри цы; на фиг. 3 - то же, одноразрядного сумматора второй и четвертой срок матрицы; на фиг. 4 - временная диаграмма работы устройства. Устройство содержит матрицу одноразрядных сумматоров 1.1-1,И,. 2.1-2.И, 3.1-З.п, 4.1-4.П, матрицу элементов И 5, входы 6.1-6,п разрядов первого операнда А, входы 7.1-7.4 разрядов второго операнда В тактовые входы 8.1-8.2, входы 9.1 и 9.2 сброса, выходы 10.1-10.4 произведения С, дополнительные входы 11.. Сумматор 1.1 (3.i) содер жит элементы НЕ 12, И 13 и ИЛИ 14. Сумматор 2.1 (4.i) содержит элемент НЕ 15, И 16, ИЛИ 17 и задержки 18. Устройство работает в конвейерно режиме,.суть которого заключается в следующем. В исходном состоянии на входах 8.1,8.2, 9.1 и 9.2 установлен сигнал 1. Перед началом работы умножителя на вход 9,2 подается отрицательный импульс, который сбрасывает одноразрядные сумматоры 4,1-4,п в нулевое состояние, при этом на четырех выходах суммы и переноса устанавливается сигнал О. Процесс вычисления начинается с подачи на входы 6.1, ,.,, 6.И, -разрядного двоичного множимого А и двух младших разрядов Bf, В и - разрядного множителя IB на входы 7.1 и 7.2.Через время Т на вход 8.1 подается сигнал О, по которому производится суммирование на сумматорах 2,1-2.И тахи 5 где , J/, - максимальное время переходного процесса в логическом элементе И; Величина определяется неравенством nSixMEP « P- mo.,-(), (Тде Д - величина временной задержки сигнала в элементе задержки; ,.С 0-. максимальное таяие время переходного процесса в логическом элементе .НЕ при переходе соответственно из 1 О и из О , в U и из и , в г О минимальное и тл я та максимальное вре мя задержки сигн ла в одноразрядпом полном сумматоре при прохождении сигкалов от входов до выходов (во всех полных одно разрядных суммат pax оно одинаково) . Через время (mot поскольку вычисления в первых двух линей ках закончилось, на вход 8.1 подается сигнал 1, который осуществляет запо минание информации, установившейся на выходах сумматоров 2.1-2.h, и запрещает отработку сумматорами 2.1-2.h сигналов, которые появляться на их информационных входах. В течение времени, пока проходит вычисление ia сумматорах 1.1-l.n и 2,1-2.М , на сумматорах 3.1-З.п и 4.1-4.П идет подготовка и вычислению на входы 7.3-7.4 подаются разряды В и В множителя В, К моменту времени (таки ) заканчивается подача В и В, вычисление продолжается на сумматорах 3.1-З.п, а затем после подачи через время ( та w + ак на вход 8.2 сигнала О и на сумматорах 4.1-4..VI. В то же время на сумматорах 1. 1 -1. Ч и Г2,1-2. И осуществляется считывание двух младших разрядов С и С произведения

где

- минимальное время

mm W

переходного процесса F 1

т;п

не меньших, чел (Т,,- f „,„

,

4nVl, ПриТцп,о,х

Аиьо , меньые{Тк +С,-„)

/ ,0-1ч

,- Ji -такие /,

логическом элементе И}

- максимальное время; 64 .4 С с выходов 10.1 и 10.2, а также подача разрядов В и В множителя В па входы 7.1,7.2. После подачи в момент времени ( + 2P moix ° сигнала 1, который осуществляет за т-оминание промежуточного результата -на выходах сумматоров 4,1-4.f, а также запрет отработки сумматорами 4.1-4,1 поступающей информации, вычисление продолжается в сумматорах 1.1-1. fl и 2.1-2.П. В течение времени, пока будут 1адти вычисления, осуществляется считывание разрядов С, С произведения , С с выходов умножителя 10.3 и 10.4 и подача разрядов By и Eg множителя В на входы 7.3 и 7.4. Процесс продолжается циклически. Когда все п разрядов множителя В будут поданы, на входах .1-7.4 устанавливается сигнал О, а процесс вычисления не прекращается до получения всех 2 п разрядов произведения С с выходов 10.1-10.4. При необходнмости ускорения получения результата можно закончить вычисление разу же после ввода разрядов В,,, и В множителя В и суммирования их частичных произведений. Тогда на выходах суммы и переноса сумматоров 4.14.11 получится двухразрядный код старших разрядов произведения С, который после суммирования на сумматоре с ускоренным переносом даст значение старших разрядов произведения С. Для обеспечения гфавильной работы умножителя, максимального быстродействия, а также для обеспечения возможности считывания промежуточной информации и коммутации разрядов множителя В величина Р должна определяться, исходя из следующей сксте1 п 1 неравенства

необходимое для считывания результата с выходов 10.1-10,4 умножителя;

т Т . - максимальное и миниkmoK If mi N

мальное время коммутации разрядов множителя В на входах 7,1-7.4 с учетом времени прохождения сигналов через элементы И 5;

цддх 1 - величина, равная большему из элементов, записанных в квадратных скобках.

Наличие в устройстве входов 1 Kil. 4 позволяет наращивать разрядость. Это удобно при модульной реалияа);ии умножителя или в виде интегральной схемы, при этом увеличение разрядности достигается соответствующей коммутацией входов 11,1-11,4 одного модуля с выходами 10.1-10,4 другого модуля.

Предлагаемое устройство может осуществлять умножение не только двухП-разрядных чисел, оно позволяет умножать п -разрядное число на число любой конечной разрядности m , при этом меняется только количество циклов работы.

tS Наличие двух входов 9.1 и 9,2 позволяет более эффективно использовать умножитель при различных .чениях Ti i

Ш Ю Ш

АфХ

7-

Ч

Ш Ш Ш

1/ффф

ФФ4Г

т

(йг.2

Фиг.З

| Авторское свидетельство СССР ,№ 8)7705, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логические основы ЦВТ, М., Советское радио, 1972, с | |||

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1985-05-15—Публикация

1982-12-24—Подача