1

(21)4720613/21 (22) 14.07.89 (46)30.10.91. Бюл. №40 (72)А.Н.Пархоменко, В.В.Голубцов. В.А.Жилин и В.С.Харламов (53)621.374(088.8)

(56)Авторское свидетельство СССР N;953734, кл. Н 03 К 21/36. 1982.

Авторское свидетельство СССР Ns 1102043, кл. Н 03 К 21 /36, 1984.

(54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

(57)Изобретение относится к импульсной технике и может быть использовано в цифровой измерительной аппаратуре, в устройствах вычислительной техники и

промышленной автоматики и телемеханики. Цель изобретения - повышение эксплуатационной отказоустойчивости путем введения резервного триггера со средствами реконфигурации структуры - достигается введением трех элементов И, двух элементов И-И-НЕ, пяти элементов И-ИЛИ/И- ИЛИ-НЕ, трех элементов НЕ, элемента 2 И-ИЛИ-НЕ, четырех элементов 2 И- ИЛИ/2И-ИЛИ-НЕ, шины управления работой триггеров и резервного триггера. Устройство также содержит счетчик импульсов, два триггера, элемент ИЛИ, пять элементов 2 И-ИЛИ, четыре элемента 2 И-НЕ, элемент РАВНОЗНАЧНОСТЬ ИЛИ-НЕ, входную шину, шину управления коэффициентом деления и выходную шину. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Двоичный счетчик | 1985 |

|

SU1272503A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Счетчик - делитель | 1989 |

|

SU1674362A1 |

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Счетчик-делитель | 1988 |

|

SU1529446A1 |

| Счетчик-делитель | 1989 |

|

SU1598169A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

Изобретение относится к импульсной технике и может быть использовано в цифровой измерительной аппаратуре, в устройствах вычислительной техники и промышленной автоматики и телемеханики.

Цель изобретения - повышение эксплуатационной отказоустойчивости путем введения резервного триггера со средствами реконфигурации структуры.

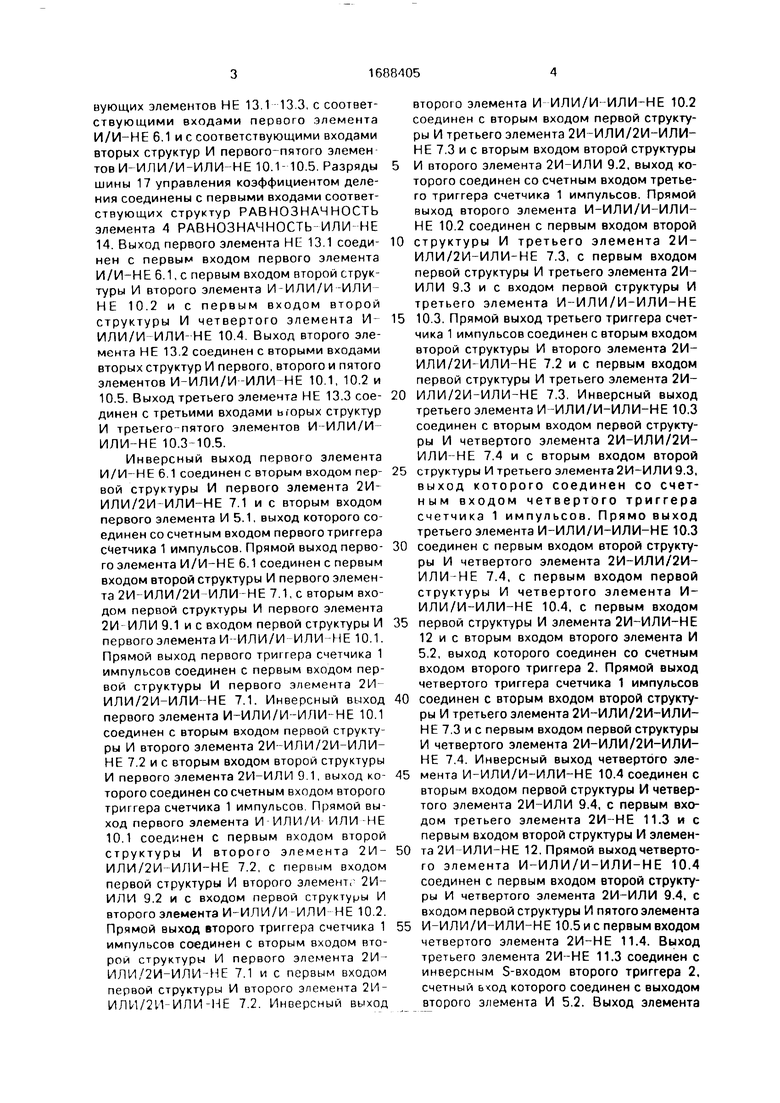

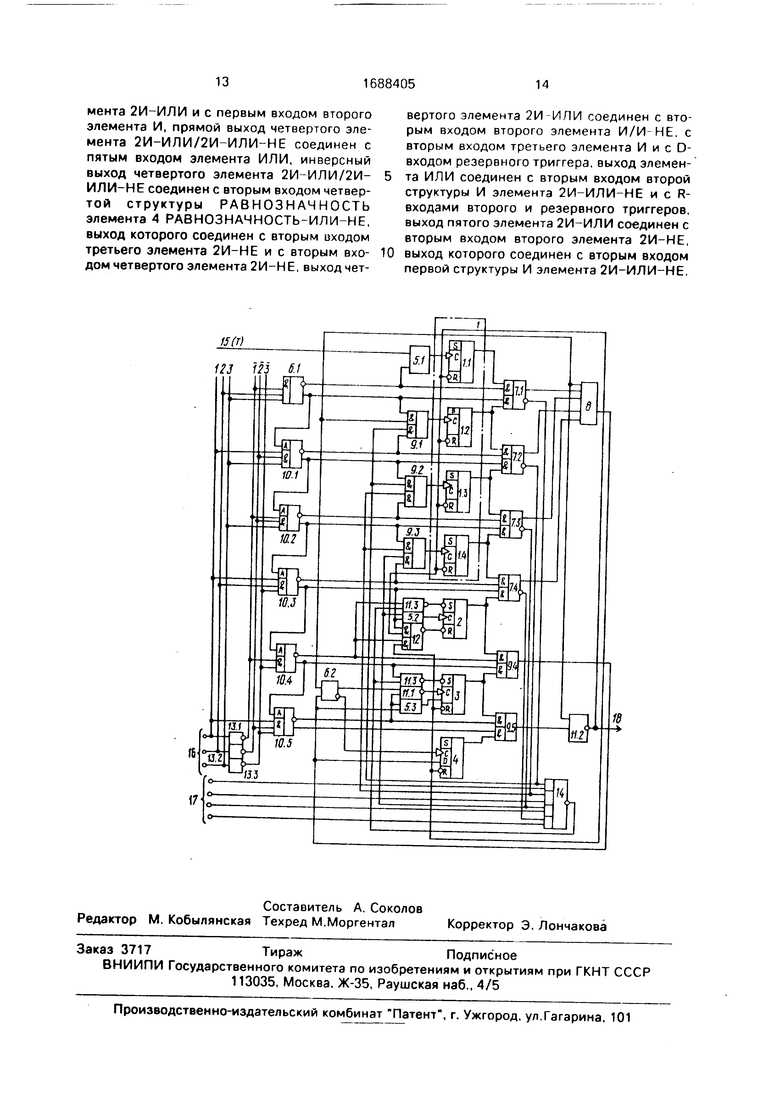

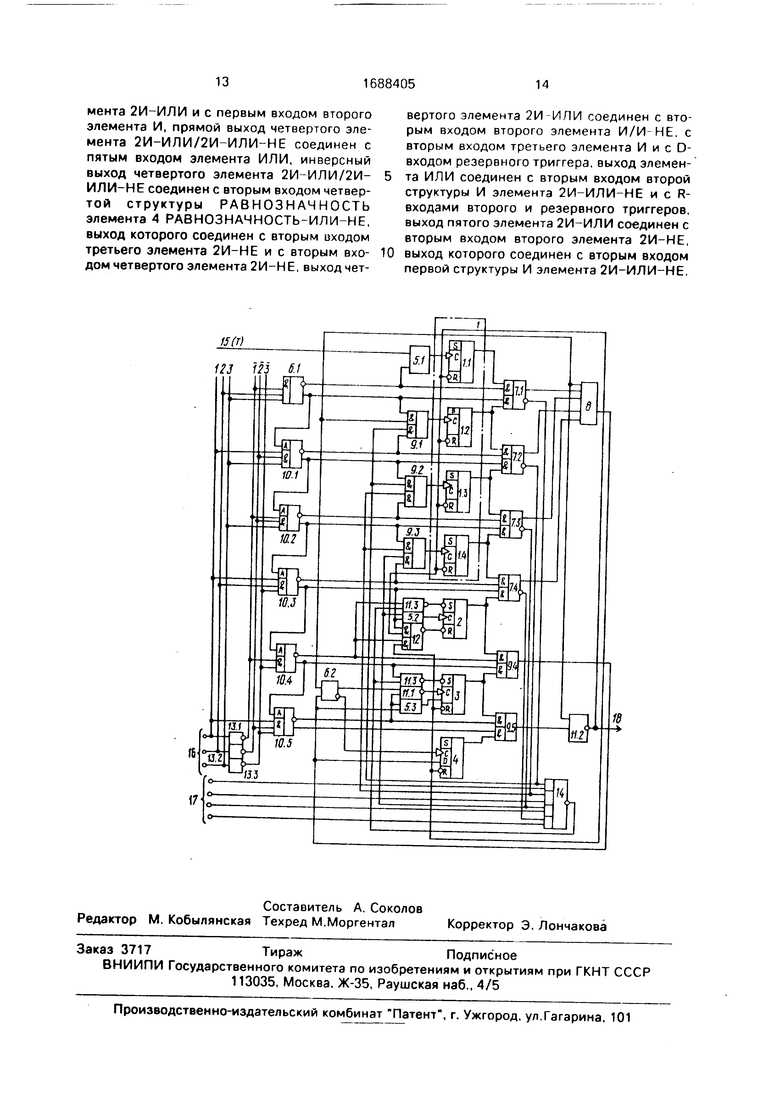

На чертеже изображена электрическая функциональная схема управляемого делителя частоты следования импульсов.

Устройство содержит четырехразрядный счетчик 1 импульсов, выполненный на триггерах, входы сброса которых соединены с входом сброса счетчика 1 импульсов, первый 2 и второй 3 триггеры, резервный триггер 4, первый-третий элементы И 5.1-5.3, первый и второй элементы И/И-НЕ 6.1 и

fe

Шина 15 соединена с первым входом элемента ИЛИ 8, с первым входом второго элемента 2И-НЕ 11.2, с первым входом второго элемента И/И-НЕ G 2, с первым входом первой группы входов элемента 2И-ИЛИ 9.1 и с первым входом элемента И 5.1.

Разряды шины 16 разрешения работы триггеров соединены с входами соответстОiOO 00

о ел

вующих элементов НЕ 13.1 13.3, с соответствующими входами первого элемента И/И-НЕ 6.1 и с соответствующими входами вторых структур И первого-пятого элемен тов И-ИЛИ/И-ИЛИ-НЕ 10.1- 10.5. Разряды шины 17 управления коэффициентом деления соединены с первыми входами соответствующих структур РАВНОЗНАЧНОСТЬ элемента 4 РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 14. Выход первого элемента НЕ 13.1 соединен с первым входом первого элемента И/И-НЕ 6.1, с первым входом второй структуры И второго элемента И-ИЛИ/И -ИЛИ- НЕ 10.2 и с первым входом второй структуры И четвертого элемента И- ИЛИ/И-ИЛИ- НЕ 10.4. Выход второго элемента НЕ 13.2 соединен с вторыми входами вторых структур И первого, второго и пятого элементов И-ИЛИ/И-ИЛИ-НЕ 10.1, 10.2 и 10.5. Выход третьего элемента НЕ 13.3 соединен с третьими входами ыорых структур И третьего-пятого элементов И-ИЛИ/И- ИЛИ-НЕ 10.3-10.5.

Инверсный выход первого элемента И/И-НЕ 6.1 соединен с вторым входом первой структуры И первого элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.1 и с вторым входом первого элемента И 5.1, выход которого соединен со счетным входом первого триггера счетчика 1 импульсов. Прямой выход первого элемента И/И-НЕ 6.1 соединен с первым входом второй структуры И первого элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.1, с вторым входом первой структуры И первого элемента 2И-ИЛИ 9.1 и с входом первой структуры И первого элемента И-ИЛИ/И-ИЛИ-НЕ 10.1. Прямой выход первого триггера счетчика 1 импульсов соединен с первым входом первой структуры И первого элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.1. Инверсный выход первого элемента И-ИЛИ/И-ИЛИ-НЕ 10.1 соединен с вторым входом первой структуры И второго элемента 2И-ИЛИ/2И-ИЛИ- НЕ 7.2 и с вторым входом второй структуры И первого элемента 2И-ИЛИ 9.1, выход которого соединен со счетным входом второго триггера счетчика 1 импульсов. Прямой выход первого элемента И - ИЛИ/И- ИЛИ -НЕ 10.1 соединен с первым входом второй структуры И второго элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.2, с первым входом первой структуры И второго элемент, 2И- ИЛИ 9.2 и с входом первой структуры И второго элемента И-ИЛИ/И-ИЛИ-НЕ 10.2. Прямой выход второго триггера счетчика 1 импульсов соединен с вторым входом второй структуры И первого элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.1 и с первым входом первой структуры И второго элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.2. Инверсный выход

второго элемента И-ИЛИ/И-ИЛИ-НЕ 10.2 соединен с вторым входом первой структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ- НЕ 7.3 и с вторым входом второй структуры

И второго элемента 2И-ИЛИ 9.2. выход которого соединен со счетным входом третьего триггера счетчика 1 импульсов. Прямой выход второго элемента И-ИЛИ/И-ИЛИ- НЕ 10.2 соединен с первым входом второй

0 структуры И третьего элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.3, с первым входом первой структуры И третьего элемента 2И- ИЛИ 9.3 и с входом первой структуры И третьего элемента И-ИЛИ/И-ИЛИ-НЕ

5 10.3. Прямой выход третьего триггера счетчика 1 импульсов соединен с вторым входом второй структуры И второго элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.2 и с первым входом первой структуры И третьего элемента 2И0 ИЛИ/2И-ИЛИ-НЕ 7.3. Инверсный выход третьего элемента И-ИЛИ/И-ИЛИ-НЕ 10.3 соединен с вторым входом первой структуры И четвертого элемента 2И-ИЛИ/2И- ИЛИ-НЕ 7.4 и с вторым входом второй

5 структуры И третьего элемента 2И-ИЛИ 9.3, выход которого соединен со счетным входом четвертого триггера счетчика 1 импульсов. Прямо выход третьего элемента И-ИЛИ/И-ИЛИ-НЕ 10.3

0 соединен с первым входом второй структуры И четвертого элемента 2И-ИЛИ/2И- ИЛИ-НЕ 7.4, с первым входом первой структуры И четвертого элемента И-ИЛИ/И-ИЛИ-НЕ 10.4, с первым входом

5 первой структуры И элемента 2И-ИЛИ-НЕ 12 и с вторым входом второго элемента И 5,2, выход которого соединен со счетным входом второго триггера 2. Прямой выход четвертого триггера счетчика 1 импульсов

0 соединен с вторым входом второй структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ- НЕ 7.3 и с первым входом первой структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ- НЕ 7.4. Инверсный выход четвертого эле5 мента И-ИЛИ/И-ИЛИ-НЕ 10.4 соединен с вторым входом первой структуры И четвертого элемента 2И-ИЛИ 9.4, с первым входом третьего элемента 2И-НЕ 11.3 и с первым входом второй структуры И элемен0 та 2И-ИЛИ-НЕ 12. Прямой выход четвертого элемента И-ИЛИ/И-ИЛИ-НЕ 10.4 соединен с первым входом второй структуры И четвертого элемента 2И-ИЛИ 9.4, с входом первой структуры И пятого элемента

5 И-ИЛИ/И-ИЛИ-НЕ 10.5 и с первым входом четвертого элемента 2И-НЕ 11.4. Выход третьего элемента 2И-НЕ 11.3 соединен с инверсным S-входом второго триггера 2, счетный ьчод которого соединен с выходом второго элемента И 5.2. Выход элемента

2И-ИЛИ-НЕ 12 соединен с инверсным R- входом второго триггера 2, прямой выход которого соединен с вторым входом второй структуры И четвертого элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7,4 и с первым входом первой структуры И четвертого элемента 2И-ИЛИ 9.4. Инверсный выход пятого элемента И-ИЛИ/И-ИЛИ-НЕ 10.5 соединен с вторым входом первой структуры И пятого элемента 2И-ИЛИ 9.5, с вторым входом первого элемента 2И-НЕ 11.1 и с первым входом третьего элемента И 5.3. Прямой выход пятого элемента И-ИЛИ/И-ИЛИ-НЕ 10.5 соединен с первым входом второй структуры И пятого элемента 2И-ИЛИ 9.5. Инверсный и прямой выходы второго элемента И/И-НЕ 6.2 соединены соответственно с первым входом первого элемента 2И-НЕ 11.1 и со счетным входом резервного триггера 4. Выход четвертого элемента 2И-НЕ 11.4 соединен с инверсным S-вхо- дом третьего триггера 3, счетный вход которого соединен с выходом первого элемента 2И-НЕ 11.1. Выход третьего элемента И 5.3 соединен с D-входом третьего триггера 3, прямой выход которого соединен с вторым входом второй структуры И четвертого элемента 2И-ИЛИ 9.4 и с первым входом первой структуры И пятого элемента 2И-ИЛИ 9.5. Прямые выходы первого-четвертого элементов 2И-ИЛИ/2И-ИЛИ-НЕ 7.1-7.4 соединены соответственно с вторым-пятым входами элемента ИЛИ 8, выход которого соединен с вторым входом второй структуры И элемента 2И-ИЛИ-НЕ 12 и с инверсными R-входами второго и резервного триггеров 3 и 4.

Инверсный выход первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ 7.1 соединен с вторым входом первой структуры РАВНОЗНАЧНОСТЬэлемента4РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 14, с первым входом второй структуры И первого элемента 2И-ИЛИ 9.1 и с вторым входом первой структуры И второго элемента 2И- ИЛИ 9.2. Инверсный выход второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ 7.2 соединен с вторым входом второй структуры РАВНОЗНАЧНОСТЬ элемента 4 РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ 14, с первым входом второй структуры И второго элемента 2И- ИЛИ 9.2 и с вторым входом первой структуры И третьего элемента 2И-ИЛИ 9.3. Инверсный выход третьего элемента 2И- ИЛИ/2И-ИЛИ-НЕ 7.3 соединен с вторым входом третьей структуры РАВНОЗНАЧНОСТЬ элемента 4 РАВНОЗНАЧНОСТЬ- ИЛИ-НЕ 14, с первым входом второй структуры И третьего элемента 2И-ИЛИ 9.3 и с первым входом второго элемента И 5.2.

Инверсный выход четвертого элемента 2И ИЛИ/2И-ИЛИ-НЕ 7.4 соединен с вторым входом четвертой структуры РАВНОЗНАЧНОСТЬ элемента 4 РАВНОЗНАЧНОСТЬ- 5 ИЛИ-НЕ 14, выход которого соединен с вторым входом третьего элемента 2И-НЕ 11.3 и с вторым входом четвертого элемента 2И-НЕ 11.4.

Выход четвертого элемента 2И-ИЛ И 9.4 10 соединен с вторым входом второго элемента И/И-НЕ 6.2, с вторым входом третьего элемента И 5.3 и с D-входом резервного триггера 4, прямой выход которого соединен с вторым входом второй структуры И 15 пятого элемента 2И-ИЛИ 9.5, выход которого соединен с вторым входом второго элемента 2И-НЕ 11.2, выход которого соединен с входом сброса счетчика 1 импульсов, с вторым входом первой структуры 0 И элемента 2И-ИЛИ-НЕ 12 и с выходной шиной 18.

В исходном состоянии все триггеры счетчика 1 и триггеры 2-4 установлены в исходное нулевое состояние. На шинах 17 5 установлен код, соответствующий выбранному коэффициенту деления, на выходе элемента 14 присутствует уровень Лог.О, как и на выходе элемента 8.

Коэффициент деления устройства опре- 0 деляется из выражения

Кд К + 1,

где К - двоичный код коэффициента деления, поступающий с шины 17.

В случае исправного состояния тригге- 5 ров счетчика 1 и триггеров 2 и 3 триггер 4 находится в горячем резерве и сигнал с его прямого выхода заблокирован нулевым логическим сигналом.с прямого выхода элемента 10.5, поступающего на первый вход 0 второй структуры И элемента 9.5.

В этом случае деление входных импульсов устройство производит следующим образом.

Так как в случае исправного состояния 5 всех триггеров устройства на шине 16 устанавливается код 111, то вторые структуры И элементов 10.1-10.5 и элемент 6.1 закрыты, что приводит к формированию сигнала Лог. 1 на их инверсных выходах и к форми- 0 рованию сигнала Лог.О на их прямых выходах. В результате этого подсчет входных импульсов производится по следующей логической ветви устройства: с шины 15 через элемент 5.1 - на счетный вход первого триг- 5 гера счетчика 1; состояние прямого выхода первого триггера (и его изменения) через первую структуру И элемента 7.1 поступает с его прямого выхода на второй вход элемента 7 и с инверсного выхода - на первый вход первой стр: ггуры РАВНОЗНАЧНОСТЬ

элемента 14, на первый вход второй структуры И элемента 9.1 и на второй вход первой структуры И элемента 9.2. Так как открыта вторая структура И элемента 9.1, то положительный фронт изменения сигнала на инверсном выходе элемента 7.1 воздействует на счетный вход второго триггера счетчика 1.

Изменение сигнала на прямом выходе второго триггера счетчика 1 через первую структуру И элемента 7.2, вторую структуру И элемента 9.2 воздействует на счетный вход третьего триггера счетчика 1. Изменение сигнала на прямом выходе третьего триггера через первую структуру И элемента 7.3 и вторую структуру И элемента 9.3 воздействует на счетный вход четвертого триггера счетчика 1.

С ттчик 1 считает входные импульсы до тех ги р, пока в нем не установится код, совпадающий с двоичным кодом коэффициента деления. До этого момента на выходе хотя бы одной из структур РАВНОЗНАЧНОСТЬ элемента 14 присутствует уровень Лог.1. При установлении в счетчике 1 кода, совпадающего с двоичным кодом коэффициента деления, на выходах всех структур РАВНОЗНАЧНОСТЬ элемента 14 формируются сигналы Лог.О, что приводит к формированию единичного сигнала на выходе элемента 14, который через элемент 11.3 устанавливает в состояние Лог.1 триггер 2. Единичный уровень сигнала с прямого выхода триггера 2 через первую структуру И элемента 9.4 и элемент 5.3 воздействует на D-вход триггера Зина второй вход элемента 6.2, в результате чего в момент окончания входного импульса на шине 15 триггер 3 устанавливается в единичное состояние, которое через первую структуру И элемента 9.5 воздействует на второй вход элемента 11.2. С приходом очередного входного импульса на выходе элемента 11.2 формируется сигнал нулевого логического уровня, который начинает установку триггеров счетчика 1 в нулевое состояние.

Значение сигнала на выходе элемента 8 определяется состоянием сигналов на выходах триггеров счетчика 1 и значением входного сигнала устройства. Когда на шине 18 заканчивается импульс, на выходе элемента 8 появляется уровень Лог.О, который устанавливает триггеры 2-4 в нулевое состояние.

В дальнейшем устройство работает аналогично. В результате на шине 18 появляются импульсы с частотой, пропорциональной частоте входных импульсов и обратно пропорциональной двоичному числу плюс единица, код которого установлен на шине 17.

Рассмотрим пример восстановления работоспособности устройства при отказе второго триггера счетчика 1 и пример отказа триггера 2 устройства.

В случае отказа второго триггера счетчика 1 на шине 16 устанавливается код 101, что приводит к смене состояний сигналов на прямых и инверсных выходах элементов 10.1-10.5, так как вторая структура

0 И элемента 10.1 пропускает на свой выход сигнал единичного логического уровня. В результате этого на прямых выходах элементов 10.1-10.5 сформирован сигнал Лог, 1, а на их инверсных выходах - сигнал

5 Лог.О, При этом открываются вторые структуры И элементов 7.2-7.4 и элементов 9.4 и 9.5. Кроме того, открываются первые структуры И элементов 9.2 и 9.3, элемент 5.2, первая структура И элемента 12 и элемент

0 11.4. Одновременно с этим закрываются следующие логические элементы устройства: вторая структура И элемента 9.1 (заметим, что остается закрытой и его первая структура И нулевым сигналом с прямого

5 выхода элемента 6.1), первые структуры И элементов 7,2-7.4, первые структуры И элементов 9.4 и 9.5, вторые структуры И элементов 9.2 и 9.3, элемент 11.3, вторая структура И элемента 12, элемент 11.1 и

0 элемент 5.3.

При поступлении на шину 15 импульсов устройство в этом случае работает следующим образом.

С шины 15 импульсы счета через эле5 мент 5.1 поступают на счетный вход первого триггера счетчика 1. Состояние (и его изменения) сигнала на выходе первого триггера через первую структуру И элемента 7.1 поступает с его прямого выхода на вход эле0 мента Вис его инверсного выхода - на первый вход первой структуры РАВНОЗНАЧНОСТЬ элемента 14, на второй вход первой структуры И элемента 9.2 и через этот элемент - на счетный вход третьего

5 триггера счетчика 1. На счетный вход второго триггера счетчика 1 этот сигнал не воздействует, так как вторая структура И элемента 9.1 закрыта.

Изменение сигнала на выходе третьего

0 триггера счетчика 1 через вторую структуру И элемента 7.2 поступает с его прямого выхода на вход элемента 8 и с его инверсного выхода поступает на вход второй структуры РАВНОЗНАЧНОСТЬ элемента 14 и через

5 первую структуру И элемента 9.3 - на счетный вход четвертого триггера счетчика 1.

Изменение сигнала на выходе четвертого триггера через вторую структуру И элемента 7.о поступает с его прямого выхода на соответствующий вход элемента 8 и с его

инверсного выхода поступает на вход третьей структуры РАВНОЗНАЧНОСТЬ элемента 14 и через первый вход элемента 5.2 - на счетный вход триггера 2.

Изменение сигнала на выходе триггера

2через вторую структуру И элемента 7.4 поступает с его прямого выхода на вход элемента 8 и с его инверсного выхода поступает на вход четвертой структуры РАВНОЗНАЧНОСТЬ элемента 14. Таким образом, второй триггер счетчика 1 оказывается замененным третьим триггером, третий триггер - четвертым триггером, а четвертый триггер - триггером 2, Так как элемент 6.2 открыт, то открывается доступ к счетному входу триггера 4, а так как элементы 11.1 и 5.3 закрыты, то триггер 3 начинает работать как обыкновенный RS-триггер, т.е. триггер 3 замещает триггер 2, а триггер 4 - триггер 3.

Далее работа управляемого делителя частоты следования импульсов происходит аналогично описанному.

При отказе триггера 2 на шине 16 устанавливается код 010, что приводит к смен состояний сигналов на прямых и инверсных выходах элементов 10.4 и 10.5. В этом случае на инверсных выходах элементов 10.110.3остаются сигналы Лог.1, а на инверсных выходах элементов 10.4 и 10.5 - сигналы Лог.О. На прямых выходах элементов 10.1-10.3 сформированы сигналы Лог.О, а на прямых выходах элементов

Единичным разрешающим сигналом с прямого выхода элемента 10.4 открываются следующие элементы устройства: элемент 11.4, вторая структура И элемента 9.4 и первая структура И элемента 10.5. Нулевым потенциалом с инверсного выхода элемента

Замена отказавших первого, третьего и четвертого триггеров счетчика 1 и триггера

3производится аналогично. Для отключе- ния первого триггера счетчика 1 на шину 16 необходимо подать код 011, для отключения второго триггера - код 101, для отключения третьего триггера - код 001, для отключения четвертого триггера - код 110,

для отключения триггера 2 - код 010 и для отключения триггера 3 - код 100.

Формула изобретения Управляемый делитель частоты следования импульсов, содержащий счетчик импульсов на триггерах, первый триггер, первый элемент 2И-НЕ, выход которого соединен со счетным входом второго триггера, второй элемент 2И-НЕ, выход которого соединен с входом сброса счетчика импульсов и с выходной шиной, входную шину, элемент ИЛИ и элемент 4 РАВНОЗНАЧ- НОСТЬ-ИЛИ-НЕ, первые входы структур РАВНОЗНАЧНОСТЬ которых соединены с соответствующими разрядами шины управления коэффициентом деления, отличающийся тем, что, с целью повышения эксплуатационной отказоустойчивости путем введения резервного триггера со средствами реконфигурации структуры, в него введены три элемента И, два элемента И/И- НЕ, пять элементов И-ИЛИ/И-ИЛИ-НЕ, три элемента НЕ, третий и четвертый элементы 2И-НЕ, пять элементов 2И-ИЛИ, элемент2И-ИЛИ-НЕ, четыре элемента 2И- ИЛИ/2И-ИЛИ-НЕ, шина управления работой триггеров и резервный триггер, причем входная шина соединена с первым входом первого элемента И, с первым входом элемента ИЛИ, с первым входом второго элемента 2И-НЕ, с первым входом первой структуры И первого элемента 2И-ИЛИ и с первым входом второго элемента И/И-НЕ, разряды шины управления работой триггеров устройства подключены к входам соответствующих элементов НЕ, к соответствующим входам первого элемента И/И-НЕ и к соответствующим входам второй структуры И всех элементов И-ИЛИ/И- ИЛИ-НЕ, выходы элементов НЕ подключены к соответствующим входам вторых структур И элементов И-ИЛИ/И- ИЛИ-НЕ, инверсный выход первого элемента И/И-НЕ соединен с вторым входом первого элемента И и с вторым входом первой структуры И первого элемента 2И- ИЛИ/2И-ИЛИ-НЕ, выход первого элемента И соединен со счетным входом первого триггера счетчика импульсов, прямой выход которого соединен с первым входом первой структуры И первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, прямой выход первого элемента И/И-НЕ соединен с первым входом второй структуры И первого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, с вторым входом первой структуры И первого элемента 2И- ИЛИ и с входом первой структуры И первого элемента И-ИЛИ/И-ИЛИ-НЕ, инверсный выход которого соединен с вторым входом

первой структуры И второго элемента 2И- ИЛИ/2И -ИЛИ-НЕ и с вторым входом второй структуры И первого элемента 2И-ИЛИ, выход которого соединен со счетным входом второго триггера счетчика импульсов, выход которого соединен с вторым входом второй структуры И первого и с первым входом первой структуры И второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ. прямой выход первого элемента И-ИЛИ/И-ИЛИ-НЕ соединен с первым входом второй структуры И второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ, с первым входом первой структуры И второго элемента 2И-ИЛИ и с входом первой структуры И второго элемента И-ИЛИ/И-ИЛИ- НЕ, инверсный выход которого соединен с вторым входом первой структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй структуры И второго элемента 2И-ИЛИ, выход которого соединен со счетным входом третьего триггера счетчика импульсов, прямой выход которого соединен с вторым входом второй структуры И второго и с первым входом первой структуры И третьего элементов 2И- ИЛИ/2И-ИЛИ-НЕ, прямой выход второго элемента И-ИЛИ/И-ИЛИ-НЕ соединен с первым входом второй структуры И третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ, с первым входом первой структуры И третьего элемента 2И-ИЛИ и с входом первой структуры И третьего элемента И-ИЛИ-И-ИЛИ- НЕ, выход третьего элемента 2И-ИЛИ соединен со счетным входом четвертого триггера счетчика импульсов, выход которого соединен с вторым входом второй структуры И третьего и с первым входом первой структуры И четвертого элемента 2И- ИЛИ/2И-ИЛ И-НЕ, инверсный выход третьего элемента И-ИЛИ/И-ИЛИ-НЕ соединен с вторым входом первой структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с вторым входом второй структуры И третьего элемента 2И-ИЛИ, прямой выход третьего элемента И-ИЛИ/И-ИЛИ-НЕ соединен с первым входом первой структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ, с вторым входом второго элемента И, с первым входом первой структуры И элемента 2И- ИЛИ-НЕ и с входом первой структуры И четвертого элемента И-ИЛИ/И-ИЛИ-НЕ, инверсный выход которого соединен с вторым входом первой структуры И четвертого элемента 2И-ИЛИ, с первым входом третьего .элемента 2И-НЕ и с первым входом второй структуры И элемента 2И-ИЛИ-НЕ, прямой выход четвертого элемента И-ИЛИ/И-ИЛИ-НЕ соединен с первым входом второй структуры И четвертого элемента 2И -ИЛИ, с первым входом четвертого элемента 2И-НЕ и с входом первой структуры И пятого элемента И-ИЛИ/И- ИЛИ-НЕ, инверсный выход которого соединен с вторым входом первой структуры И

пятого элемента 2И-ИЛИ, с вторым входом первого элемента 2И-НЕ и с первым входом третьего элемента И, прямой выход пятого элемента И-ИЛИ/И-ИЛИ-НЕ соединен с первым входом второй структуры И пятого

0 элемента 2И-ИЛИ, выход третьего элемента 2И-НЕ соединен с инверсным 5-входом первого триггера, счетный вход которого соединен с выходом второго элемента И, выход элемента 2И-ИЛИ-НЕ соединен с

5 инверсным R-входом первого триггера, прямой выход которого соединен с вторым входом второй структуры И четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ и с первым входом первой структуры И четвертого эле0 мента 2И-ИЛИ, прямой и инверсный выходы второго элемента И/И-НЕ соединены соответственно с первым входом первого элемента 2И-НЕ и со счетным входом резервного триггера, выход четвертого эле5 мента 2И-НЕ соединен с инверсным S-входом второго триггера, выход третьего элемента И соединен с D-входом второго триггера, прямой выход которого соединен с вторым входом второй структуры И четвер0 того элемента 2И-ИЛИ и с первым входом первой структуры И пятого элемента 2И- ИЛИ, выход резервного триггера соединен с вторым входом второй структуры И пятого элемента 2И-ИЛИ, прямой выход первого

5 элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с вторым входом элемента ИЛИ, инверсный выход первого элемента 2И-ИЛИ/2И- ИЛИ-НЕ соединен с вторым входом первой структуры РАВНОЗНАЧНОСТЬ элемента 4

0 РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ, с первым входом второй структуры И первого элемента 2И-ИЛ И и с вторым входом первой структуры И второго элемента 2И-ИЛИ, прямой выход второго элемента 2И-ИЛИ/2И5 ИЛИ-НЕ соединен с четвертым входом элемента ИЛИ, инверсный выход второго элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с вторым входом второй структуры РАВНОЗНАЧНОСТЬ элемента 4 РАВНОЗНАЧ0 НОСТЬ-ИЛИ-НЕ, с первым входом второй структуры И второго элемента 2И-ИЛИ и с вторым входом первой структуры И третьего элемента 2И-ИЛИ, прямой выход третьего элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с

5 третьим входом элемента ИЛИ, инверсный выход третьего элемента 2И-ИЛИ/2И- ИЛИ-НЕ соединен с вторым входом третьей структуры РАВНОЗНАЧНОСТЬ элемента 4 РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ, с первым входом второй структуры И третьего элемента 2И-ИЛИ и с первым входом второго элемента И, прямой выход четвертого элемента 2И-ИЛИ/2И-ИЛИ-НЕ соединен с пятым входом элемента ИЛИ, инверсный выход четвертого элемента 2И-ИЛИ/2И- ИЛИ-НЕ соединен с вторым входом четвертой структуры РАВНОЗНАЧНОСТЬ элемента 4 РАВНОЗНАЧНОСТЬ-ИЛИ-НЕ, выход которого соединен с вторым входом третьего элемента 2И-НЕ и с вторым входом четвертого элемента 2И-НЕ, выход чета (т)

17

0

вертого элемента 2И-ИЛИ соединен с вторым входом второго элемента И/И-НЕ. с вторым входом третьего элемента И и с D- входом резервного триггера, выход элемента ИЛИ соединен с вторым входом второй структуры И элемента 2И-ИЛИ-НЕ и с R- входами второго и резервного триггеров, выход пятого элемента 2И-ИЛИ соединен с вторым входом второго элемента 2И-НЕ, выход которого соединен с вторым входом первой структуры И элемента 2И-ИЛИ-НЕ.

Авторы

Даты

1991-10-30—Публикация

1989-07-14—Подача