Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен счетчик импульсов в коде Грея, который может использоваться в качестве делителя частоты с постоянным коэффициентом деления 2N, где N число разрядов [1] имеющий N разрядов и содержащий N входовой сумматор по модулю 2, входы которого соединены с прямыми выходами триггеров всех разрядов, и в каждом разряде с номером n, где n=1,2.(N-1), первую двухвходовую схему совпадения, выход которой соединен со счетным входом триггера, а первый вход с прямым выходом триггера (n-1)-го разряда, первый и второй дополнительные триггеры и в каждом разряде с номером n вторую двухвходовую схему совпадения, первый вход которой соединен с инверсным выходом триггера (n-1)-го разряда, второй вход с вторым входом первой схемы совпадения и с выходом второй схемы совпадения (n-1)-го разряда, а выход с вторыми входами схем совпадения (n+1)-го разряда. Счетные входы первого и второго дополнительных триггеров соединены с шиной счетных импульсов и через инвертор с вторыми входами схем совпадения первого разряда, входы сброса соответственно с инверсным и прямым выходами сумматора, а прямые выходы с первыми входами соответственно первой и второй схем совпадения первого разряда, причем выход второй схемы совпадения (N-1)-го разряда соединен со счетным входом триггера N-го разряда.

Недостатком указанного делителя частоты являются ограниченные функциональные возможности в связи с отсутствием возможности реализации других коэффициентов деления, кроме 2N.

Известна группа разрядов счетного устройства, которая может использоваться в качестве делителя частоты с постоянным коэффициентом деления, равным 10 [2] содержащая четыре триггера, выполненные в виде одноступенчатых D-триггеров, и двенадцать логических элементов, из которых первый, восьмой, девятый и десятый выполнены в виде элементов ИЛИ, второй, третий, одиннадцатый и двенадцатый в виде элементов ИЛИ-НЕ, четвертый, пятый, шестой, седьмой в виде элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Прямой выход первого триггера соединен с первым входом первого логического элемента, выход которого соединен с первым входом второго логического элемента. Выход четвертого логического элемента соединен с первым входом пятого, выход шестого логического элемента с первым входом седьмого, выход восьмого логического элемента с вторым входом первого, выход второго логического элемента с С-входом четвертого триггера, первый вход девятого логического элемента с прямым выходом третьего триггера, выход седьмого логического элемента с первым входом четвертого логического элемента, первый вход третьего логического элемента с R-входами первого и второго триггеров, первый вход восьмого логического элемента с первым входом устройства, второй вход которого соединен с R-входами третьего и четвертого триггеров, выход девятого логического элемента соединен с выходной шиной, первый вход шестого логического элемента с управляющей шиной, первый вход десятого логического элемента с первым входом восьмого, а выход с вторыми входами третьего и девятого. С-входы первого, второго, третьего триггеров соединены с выходами соответственно третьего, одиннадцатого и двенадцатого логических элементов. Прямые выходы второго и четвертого триггеров соединены соответственно с вторыми входами четвертого и шестого логических элементов. D-входы первого, второго, третьего и четвертого триггеров соединены соответственно с первыми входами пятого, четвертого, седьмого и шестого логических элементов. Второй вход второго логического элемента соединен с инверсным выходом второго триггера, а первый вход с первым входом двенадцатого логического элемента, второй вход которого соединен с прямым выходом второго триггера. Второй выход первого логического элемента соединен с первым входом одиннадцатого, второй вход которого соединен с инверсным выходом первого триггера. Инверсный выход третьего триггера соединен с вторым входом седьмого и первым входом третьего логических элементов. D-вход дополнительного триггера соединен с выходом пятого логического элемента, прямой выход с первым входом десятого логического элемента, инверсный выход с вторым входом восьмого логического элемента, С-вход с первым входом счетного устройства, а R-вход с вторым входом счетного устройства.

Недостатком указанного делителя частоты являются ограниченные функциональные возможности в связи с отсутствием возможности реализации других коэффициентов деления, кроме 10.

Наиболее близким к заявляемому объекту по технической сущности является делитель частоты [3] содержащий два элемента совпадения, первые входы которых подключены к входной шине, управляющую и выходную шины и в каждом разряде, с первого по N-й. триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента совпадения, выход второго из которых соединен со счетным входом триггера, прямой выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. В каждом разряде, с первого по (N-1)-й, где N-число разрядов делителя частоты, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда. Первые входы первого и второго элементов совпадения каждого разряда, с второго по N-й, соединены с выходом первого элемента совпадения предыдущего разряда, вторые входы соответственно с инверсным и прямым выходами триггера предыдущего разряда. Первые входы первого и второго элементов совпадения первого разряда соединены с выходом первого элемента совпадения, вторые входы соответственно с прямым и инверсным выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда. В последнем разряде второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющей шиной, при этом элементы совпадения выполнены в виде элементов И. Делитель частоты содержит также триггер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с прямым выходом триггера. Выход первого элемента совпадения N-го разряда соединен с выходной шиной, вторые входы первого и второго элементов совпадения соединены соответственно с инверсным и прямым выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом триггера второго разряда, выход второго элемента совпадения соединен со счетным входом триггера.

Указанный делитель частоты позволяет реализовать любые недвоичные коэффициенты деления в диапазоне от 2N-1 до 2N путем изменения способа соединения элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с триггерами.

Недостатком указанного делителя частоты являются ограниченные функциональные возможности в связи с невозможностью реализовать любые целочисленные коэффициенты деления менее 2N-1, а также в связи с невозможностью изменения коэффициента деления в диапазоне от 2N-1 до 2N без изменения схемы делителя частоты.

Цель изобретения расширение функциональных возможностей достигается за счет обеспечения возможности изменения коэффициента деления и расширения его диапазона.

Расширение функциональных возможностей делителя частоты за счет обеспечения возможности изменения коэффициента деления достигается без изменения схемы делителя частоты за счет расширения диапазона коэффициента деления путем уменьшения нижней границы с 2N-1 до 1. Задание коэффициента деления осуществляется по соответствующей шине в позиционном двоичном коде.

Указанные преимущества рассматриваемого делителя частоты, построенного на основе счетчика в коде Грея, обеспечиваются схемными мерами путем организации работы счетчика в режиме ограничения счета на заданном уровне. При этом информация на входах разрядов числа А цифрового компаратора за время цикла работы последовательно изменяется в соответствии с позиционным двоичным кодом от нуля до состояния Кзад-1, соответствующего выбранному коэффициенту деления Кзад, затем переходит в состояние, соответствующее числу 2N-Кзад, и далее последовательно изменяется в соответствии с позиционным двоичным кодом до состояния 2N-1, после этого переходит в исходное состояние. За время цикла на выходную шину выдается два импульса.

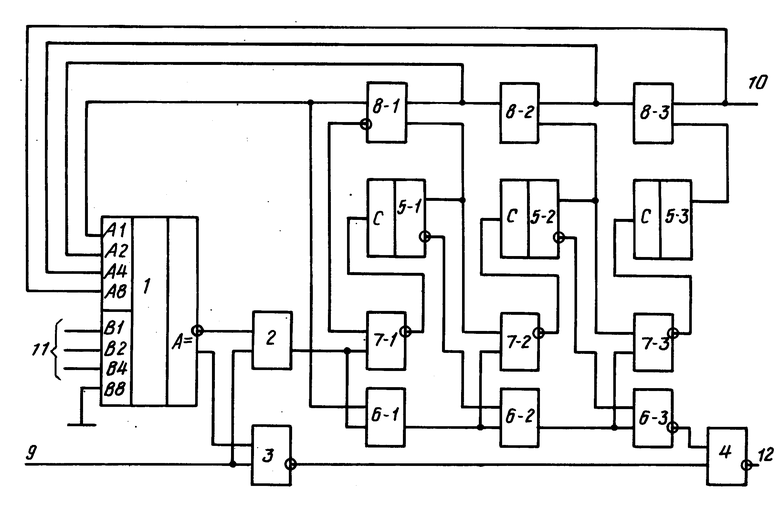

На чертеже приведена электрическая функциональная схема трехразрядного делителя частоты.

Делитель частоты содержит цифровой компаратор 1, первый, второй и третий элементы 2 4 совпадения и в каждом разряде с номером n, где n=1,2,3, триггер 5-n, первый и второй элементы 6-n и 7-n совпадения и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 8-n, а также входную шину 9, управляющую шину 10, шину 11 кода коэффициента деления и выходную шину 12.

В каждом разряде выход элемента 7-n совпадения соединен со счетным входом триггера 5-n, прямой выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8-n. Второй вход элемента 8-1 соединен с выходом элемента 8-2, второй вход которого соединен с выходом элемента 8-3, второй вход которого соединен с управляющей шиной 10. Первые входы элементов 6-3 и 7-3 совпадения соединены с выходом элемента 6-2 совпадения, а вторые входы соответственно с инверсным и прямым выходами триггера 5-2. Первые входы элементов 6-2 и 7-2 совпадения соединены с выходом элемента 6-1 совпадения, а вторые входы соответственно с инверсным и прямым выходами триггера 5-1. Первые входы элементов 6-1 и 7-1 совпадения соединены с выходом элемента 2 совпадения, а вторые входы соответственно с прямым и инверсным выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1. Первые входы элементов 2 и 3 совпадения соединены с входной шиной 9, а вторые входы соответственно с инверсным и прямым выходами А= В цифрового компаратора 1. Первый и второй входы элемента 4 совпадения соединены с выходами соответственно элементов 6-3 и 3 совпадения, а выход с выходной шиной 12. Входы разрядов числа А цифрового компаратора 1, начиная с младшего, соединены соответственно с прямым выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1, с выходами элементов 8-2 и 8-3 и с управляющей шиной 10. Вход старшего разряда числа В цифрового компаратора 1 соединен с общей шиной, а входы остальных разрядов с шиной 11 кода коэффициента деления.

Цифровой компаратор 1 выполнен на микросхеме 564ИП2, элементы 2, 3, 4, 6 -1,6- 2,6-3,7-1,7-2,7-3 совпадения на микросхемах 564ЛА7, триггеры 5-1, 5-2, 5-3 на микросхемах 564ТВ1, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1, 8-2, 8-3 на микросхемах 564ЛП2, инверсные выходы элемента 8-1 и компаратора 1, а также прямые выходы элементов 2, 6-1 и 6-2 совпадения организованы путем дополнительного подключения инверторов на микросхемах 564ЛА7.

Цифровой компаратор 1, элементы 2, 3, 4, 6-1, 6-2, 6-3, 7-1, 7-2, 7-3 совпадения, триггеры 5-1, 5-2, 5-3 и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 8-1,8-2, 8-3 могут быть выполнены на КМОП-микросхемах других серий, а также на ТТЛ микросхемах и других.

Делитель частоты работает следующим образом.

В исходном состоянии триггеры 5-1, 5-2, 5-3 находятся в состоянии логического "0", на шинах 9, 10 и 12 уровень логического "0", на прямом выходе элемента 8-1 и на выходах элементов 8-2, 8-3 уровень логического "0". Допустим, что на шине 11 задан код числа 5-101. На прямом выходе компаратора 1 уровень логического "0", а на инверсном выходе уровень логической "1".

Первый счетный импульс положительной полярности поступает на шину 9 и проходит через элементы 2 и 7-1. Счетный импульс отрицательной полярности с выхода элемента 7-1 поступает на счетный вход триггера 5-1 и в момент окончания задним фронтом переключает триггер 5-1 в состояние логической "1", изменяя состояние элемента 8-1.

Поэтому второй счетный импульс с шины 9 проходит через элементы 2, 6-1 и 7-2 на счетный вход триггера 5-2, переключает триггер 5-2 в состояние логической "1", изменяя состояние элементов 8-2 и 8-1. Третий счетный импульс переключает триггер 5-1 в состояние логического "0". Четвертый счетный импульс проходит через элементы 2, 6-1, 6-2, 7-3 на счетный вход триггера 5-3, переключает его в состояние логической "1" и изменяет состояние элементов 8-3, 8-2, 8-1. Пятый счетный импульс переключает триггер 5-1 в состояние логической "1".

После пятого счетного импульса на выходах элементов 8-1, 8-2 и 8-3 устанавливается код "101". Цифровой компаратор 1 изменяет свое состояние: на его прямом выходе устанавливается уровень логической "1", а на инверсном выходе уровень логического "0". Поэтому шестой счетный импульс проходит через элементы 3 и 4 на выходную шину 12 и изменяется состояние последующего устройства. При этом на шине 10 устанавливается уровень логической "1", компаратор 1 возвращается в исходное состояниекогда на его прямом выходе присутствует уровень логического "0", а на инверсном выходе уровень логической "1".

Далее работа происходит аналогичным образом в следующей последовательности: седьмой счетный импульс переключает триггер 5-1 в состояние логического "0", восьмой счетный импульс переключает триггер 5-3 в состояние логического "0", девятый счетный импульс переключает триггер 5-1 в состояние логической "1", десятый счетный импульс переключает триггер 5-2 в состояние логического "0", одиннадцатый счетный импульс переключает триггер 5-1 в состояние логического "0". Двенадцатый счетный импульс проходит через элементы 2, 6-1, 6-2, 6-3, 4 на выходную шину 12, изменяя состояние последующего устройства. На шине 10 устанавливается состояние логического "0". Делитель частоты вернулся в исходное состояние.

Далее работа происходит аналогичным образом.

Если в процессе работы делитель частоты под действием внешних помех установится в одно из запрещенных состояний на выходах элементов 8-1, 8-2, 8-3, например, в состояние "011", то дальнейшие процессы развиваются в зависимости от уровня сигнала на шине 10. При указанном состоянии элементов 8-1, 8-2, 8-3 триггеры 5-1, 5-2, 5-3 находятся в состоянии "101".

Если на шине 10 присутствует уровень логического "0", то очередной счетный импульс переключит триггер 5-1 в состояние логического "0", а следующий счетный импульс пройдет через элементы 2, 6-1, 6-2, 6-3, 4 в последующее устройство и установит на шине 10 уровень логической "1". После этого триггеры 5-1, 5-2, 5-3 в соответствии с кодом Грея переключатся счетными импульсами в состояние логического "0". Делитель частоты устанавливается в исходное состояние.

Если же на шине 10 присутствует уровень логической "1", то счетные импульсы переключают триггеры 5-1, 5-2, 5-3 в состояние логического "0" в соответствии с кодом Грея, начиная с состояния "101".

Таким образом, описание работы подтверждает нормальное функционирование делителя частоты и вывод его счетными импульсами из запрещенных состояний.

При этом обеспечивается расширение функциональных возможностей делителя частоты за счет обеспечения возможности изменения коэффициента деления без изменения схемы делителя частоты путем установки кода коэффициента деления на соответствующей шине, а также за счет расширения диапазона коэффициента деления путем уменьшения нижней границы с величины 2N-1, где N число разрядов, до 1.

Указанные преимущества заявляемого делителя частоты, построенного на основе счетчика в коде Грея, обеспечиваются схемными мерами путем организации работы счетчика в режиме ограничения счета на заданном уровне. При этом информация на выходах элементов 8-1, 8-2, 8-3 за время цикла работы последовательно изменяется в соответствии с позиционным двоичным кодом от нуля до состояния Кзад-1, соответствующего заданной величине коэффициента деления Кзад, затем переходит в состояние, соответствующее числу 2N-2Kзад, и далее последовательно изменяется в соответствии с позиционным двоичным кодом до состояния 2N-1, а после этого переходит в исходное состояние. При этом появляется дополнительная возможность в каждом цикле формировать импульсы, расположение которых во времени привязано и к началу цикла и к его концу. За время цикла на выходную шину выдается два импульса. Фактический коэффициент деления Кзад превышает на 1 величину, заданную на шине 11 кода коэффициента деления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036554C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2036550C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| ДВОИЧНЫЙ СЧЕТЧИК | 1990 |

|

RU2040855C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1993 |

|

RU2111609C1 |

| СЧЕТНОЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ | 1993 |

|

RU2074513C1 |

Применение: устройство относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления. Сущность изобретения: делитель частоты содержит цифровой компаратор, первый, второй и третий элементы совпадения в каждом разряде с номером n, где n = 1, 2, 3, триггер, первый и второй элементы совпадения и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, а также входную шину, управляющую шину, шину кода коэффициента деления и выходную шину с соответствующими связями. 1 ил.

ДЕЛИТЕЛЬ ЧАСТОТЫ, содержащий два элемента совпадения, первые входы которых подключены к входной шине, управляющую и выходную шины и в каждом разряде триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента совпадения, выход второго из которых соединен со счетным входом триггера, прямой выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, в каждом разряде с первого по (N-1)-ый второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда, первые входы первого и второго элементов совпадения каждого разряда с второго по N-й соединены с выходом первого элемента совпадения предыщущего разряда, вторые входы соответственно с инверсным и прямым выходами триггера предыдущего разряда, первые входы первого и второго элементов совпадения первого разряда соединены с выходом первого элемента совпадения, вторые входы соответственно с прямым и инверсным выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда, в последнем разряде второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющей шиной, при этом первый элемент совпадения и первые элементы совпадения каждого разряда с первого по (N-1)-й выполнены в виде элементов И, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены третий элемент совпадения, шина кода коэффициента деления и цифровой компаратор, первая группа информационных входов которого поразрядно соединена с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ каждого разряда и с управляющей шиной, вход старшего разряда второй группы информационных входов с общей шиной, входы остальных разрядов второй группы информационных входов с шиной кода коэффициента деления, прямой и инверсный выходы "равно" с вторыми входами соответственно второго и первого элементов совпадения, первый и второй входы третьего элемента совпадения соединены с выходами соответственно первого элемента совпадения последнего разряда и второго элемента совпадения, выход с выходной шиной, причем второй и третий элементы совпадения, вторые элементы совпадения каждого разряда и первый элемент совпадения последнего разряда выполнены в виде элементов И НЕ.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1983 |

|

SU1162368A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1995-06-19—Публикация

1991-06-28—Подача