Изобретение относится к вычислительной технике, а именно к классу кодирую- ще-декодирующих :систем, устройств, находящих широкое применение в системах с ИКМ для чтения и записи цифровой ин- .формации: оптических запоминающих устройствах реверсивного типа, системах. класса CD ROM. CD INTERACTIVE и т.д. в

качестве постпроцессоров, подготавливающих требуемую информационную среду в режиме кодирования и.обеспечивающих прием, обработку и дальнейшую передачу информационного потока с требуемыми, статистическими характеристиками в альтернативном режиме.

Целью изобретения является повышение быстродействия кодека.

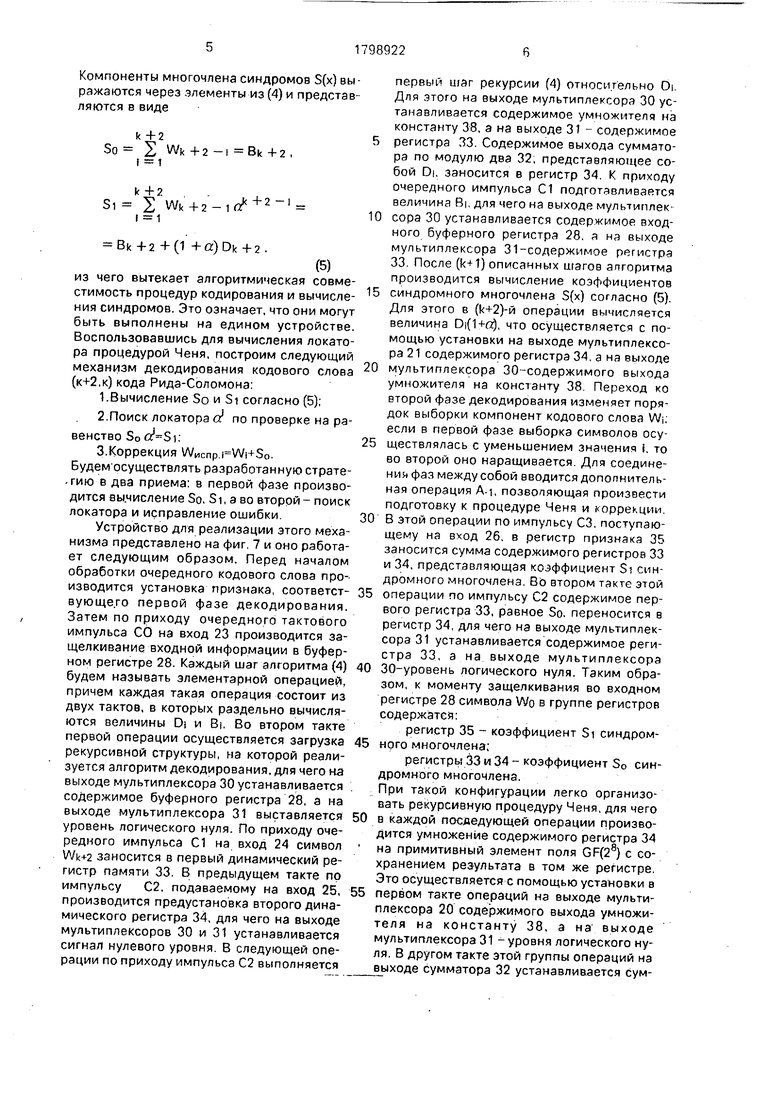

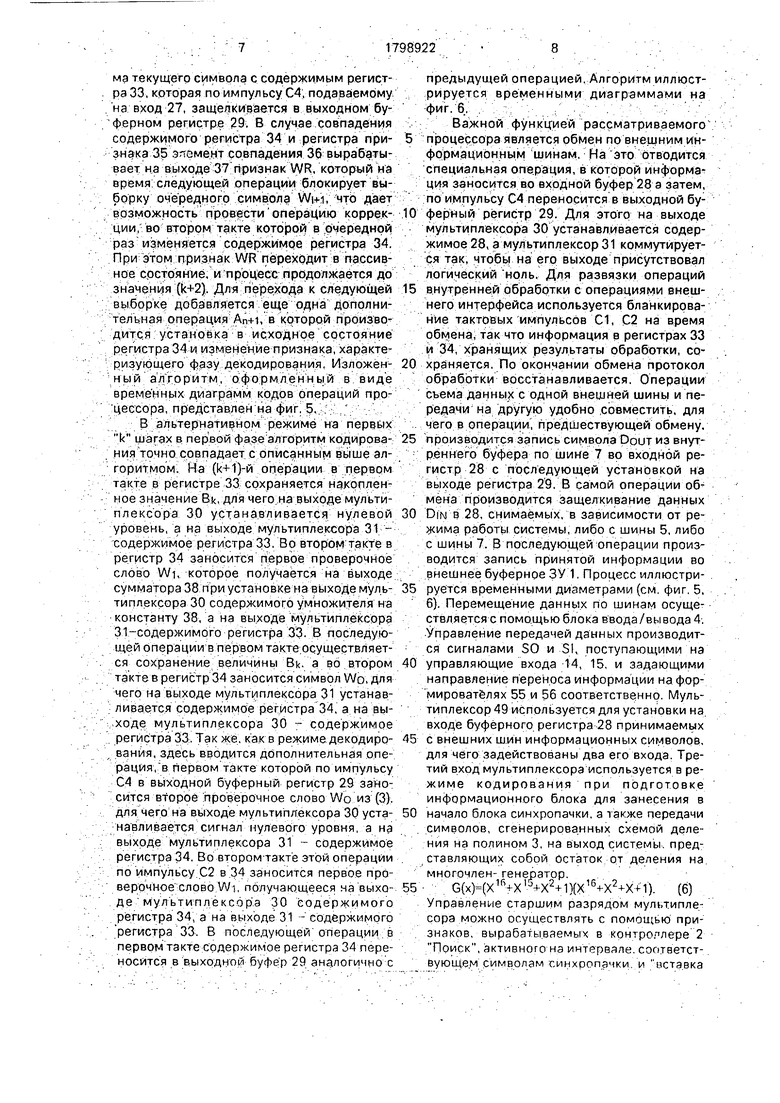

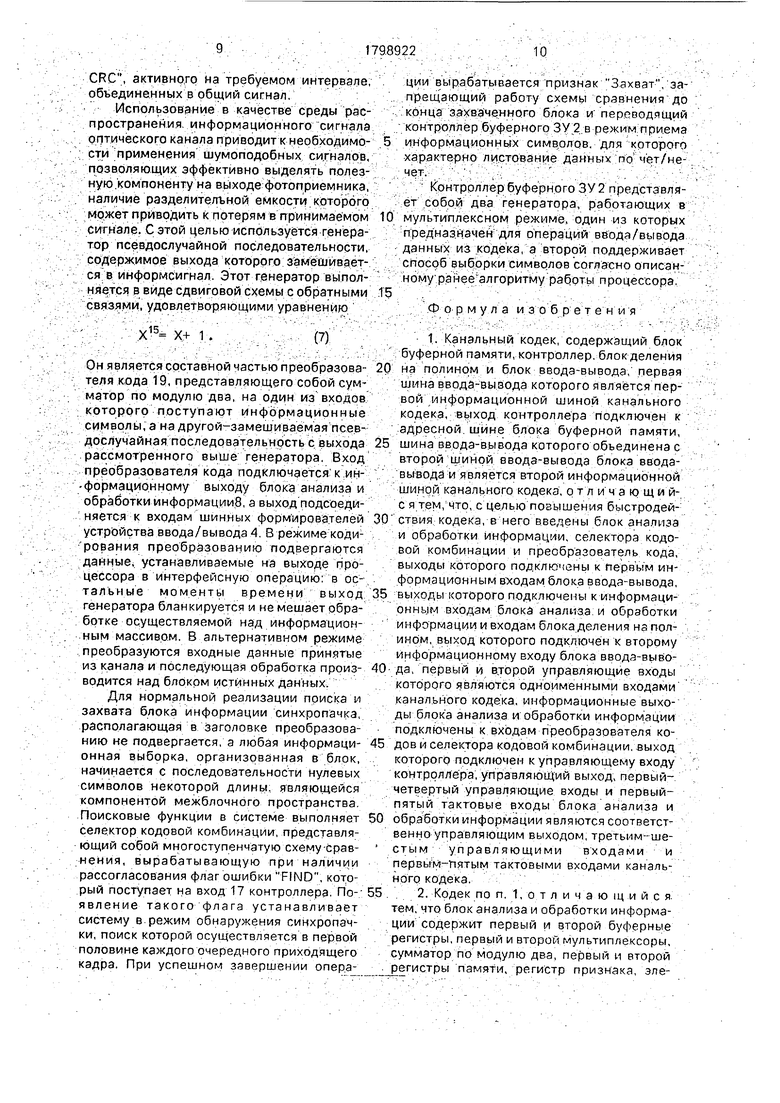

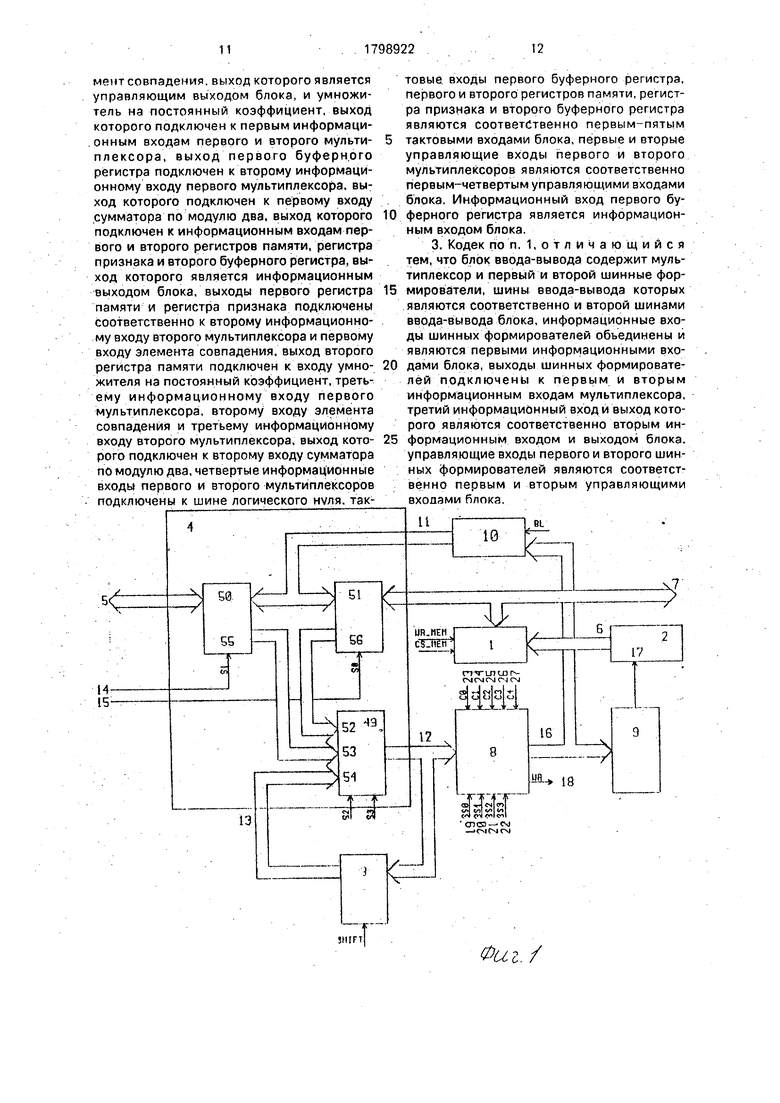

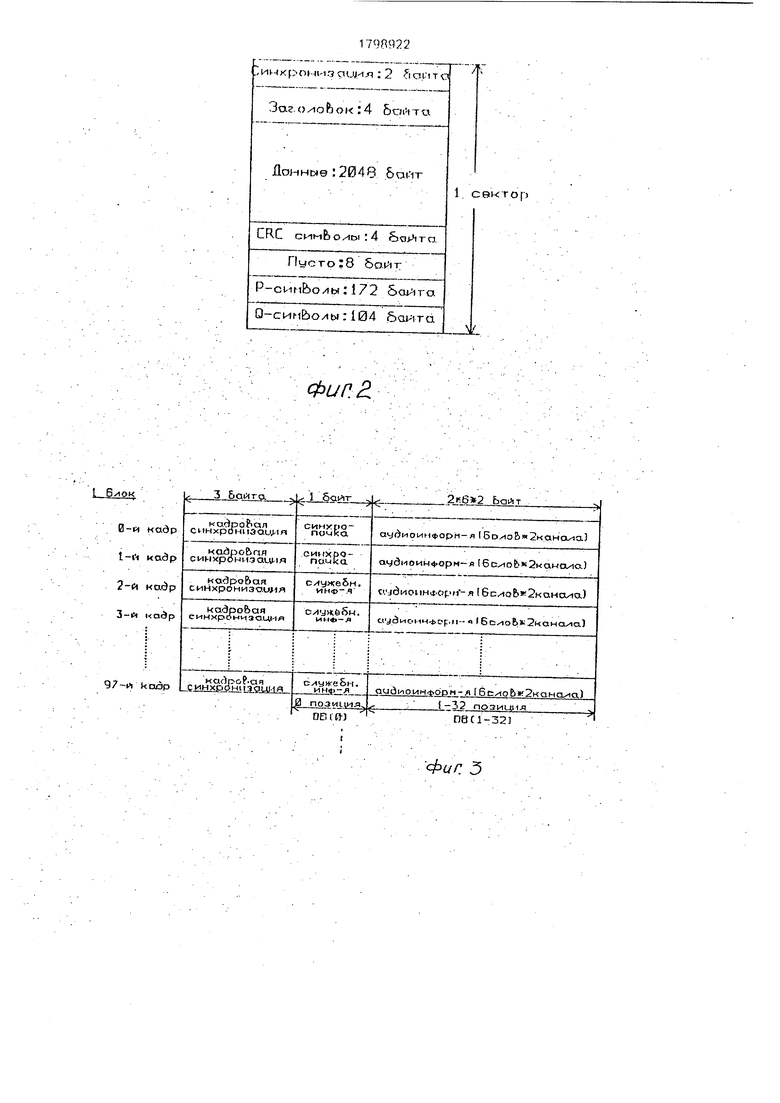

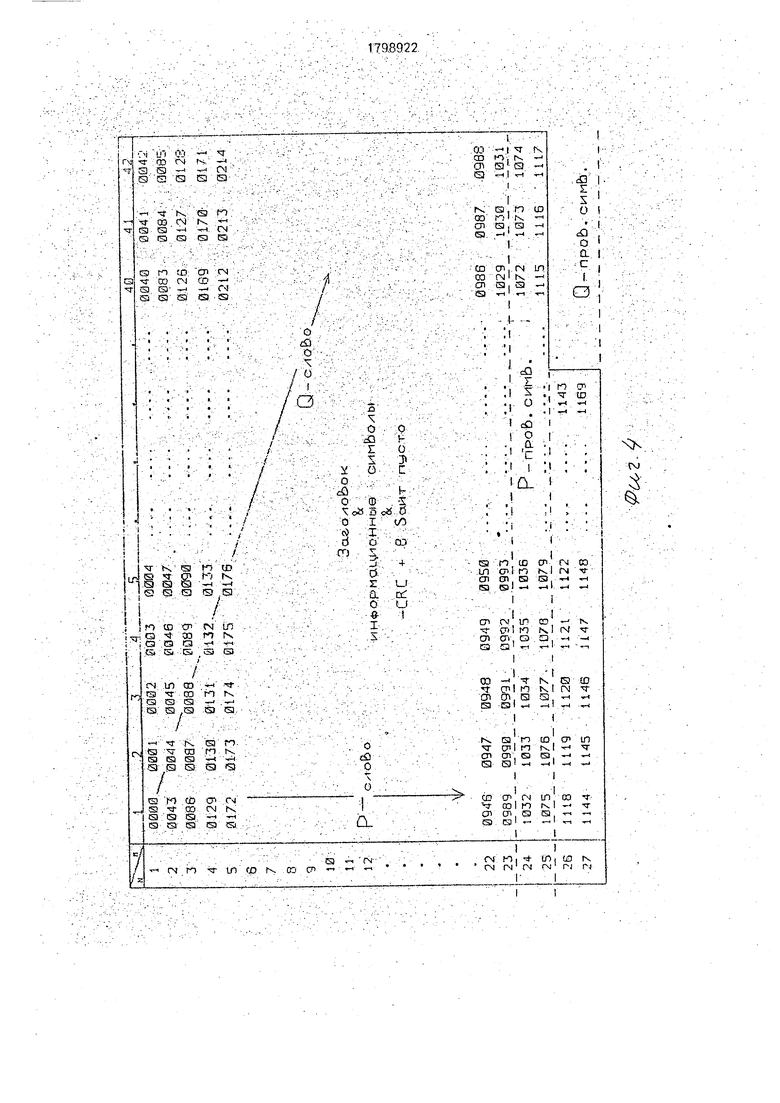

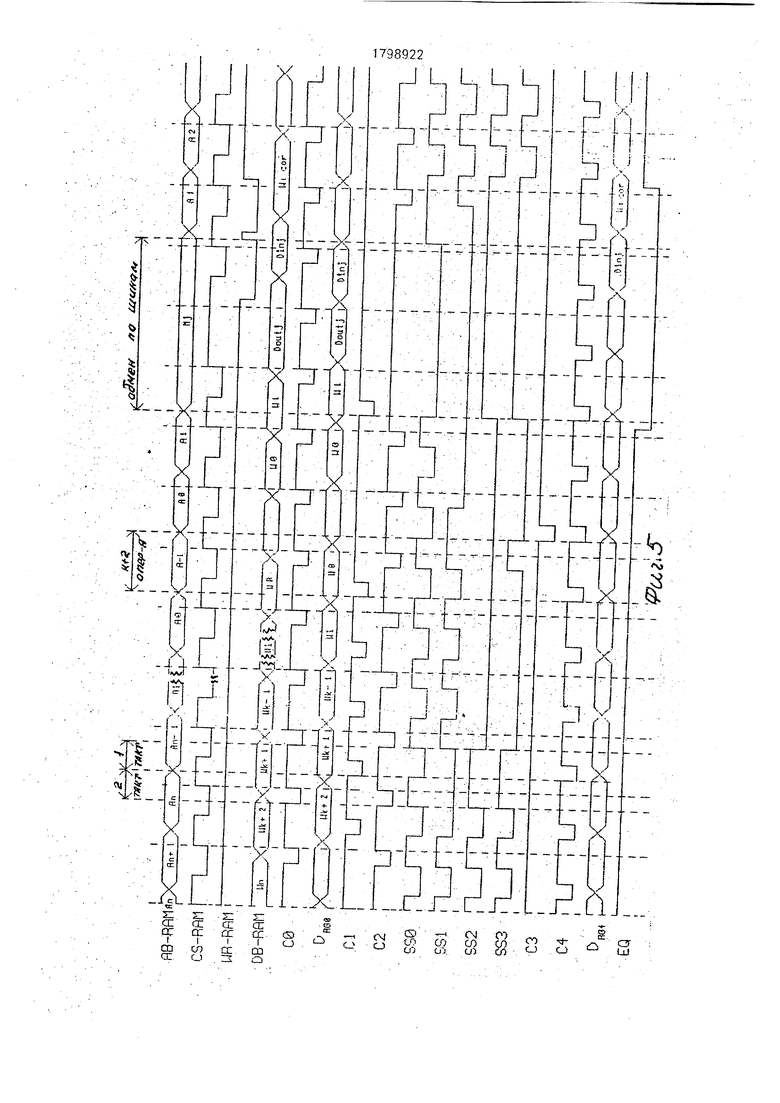

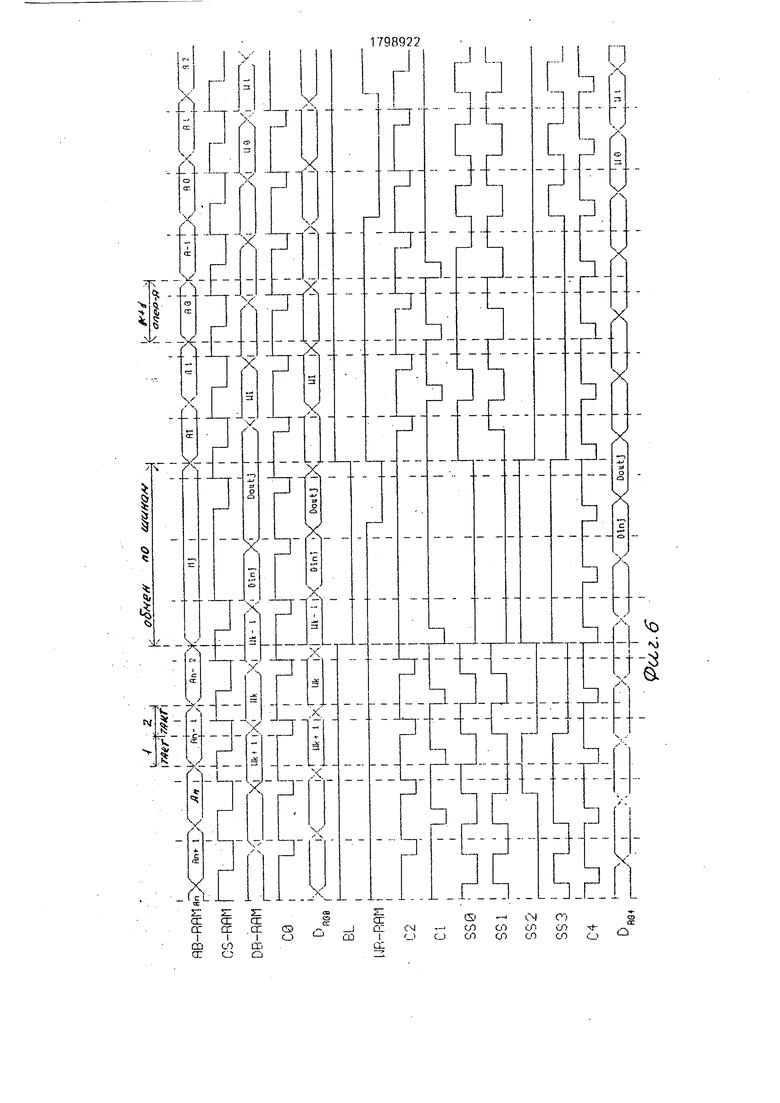

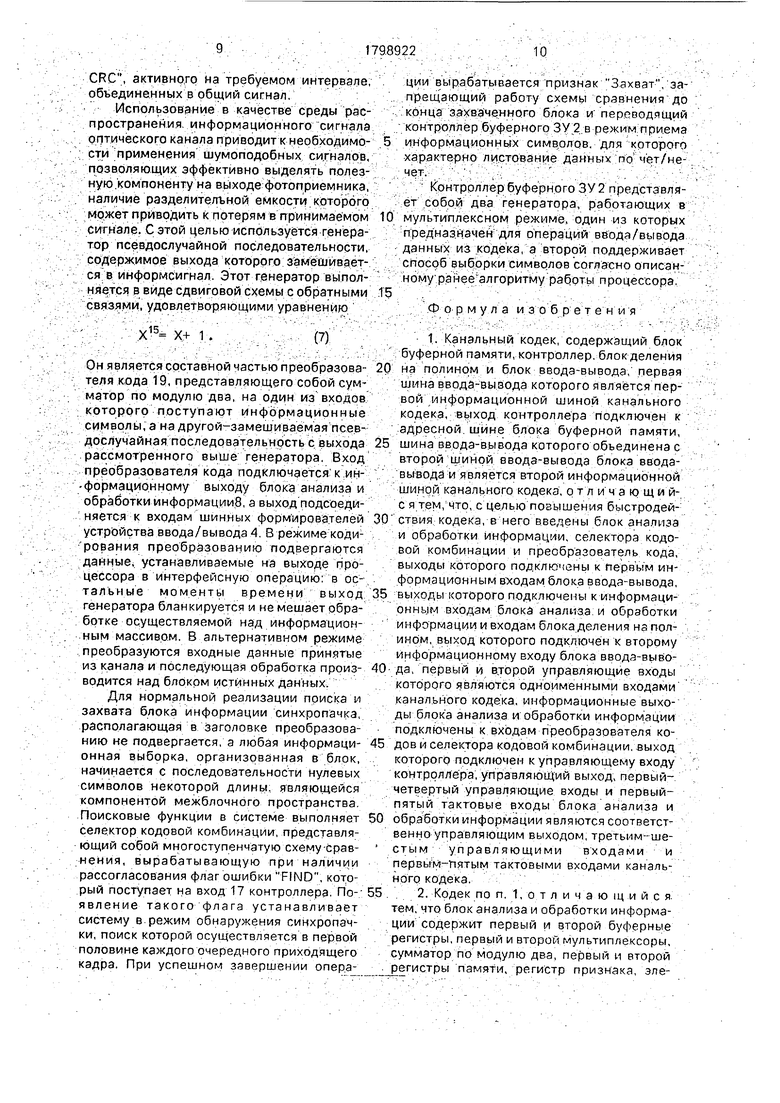

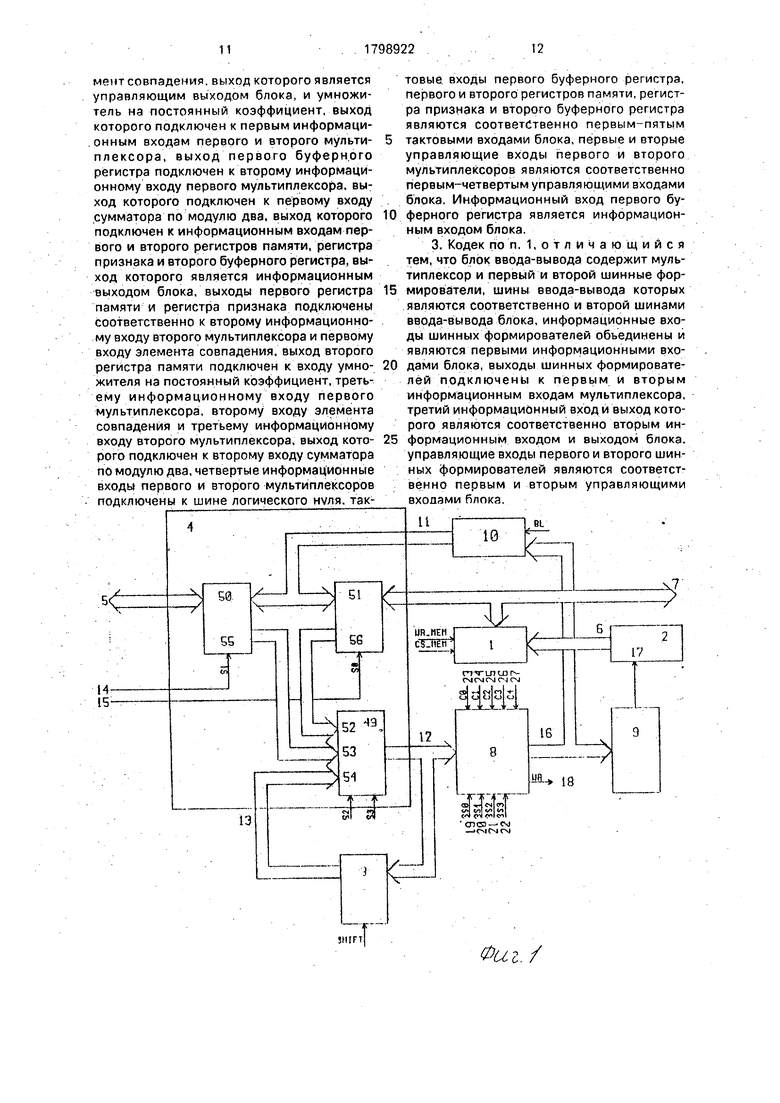

На фиг, 1 показана структурная схема кодекса; на фиг. 2 - структура сектора CD- ROM; на фиг. 3 - формат блока аудиаинфор- м.адии; на фиг, 4 - конфигурация кода выбо рки P.Q; на. фиг. 5-.Y алгоритм декодирован йя, временны е ди а грамм ы; н а ф иг. 6 - алгоритм кодирования, временные диаграммы; на фиг. 7 - функциональная, схема схемь|:ана/1иза и обработки информации.

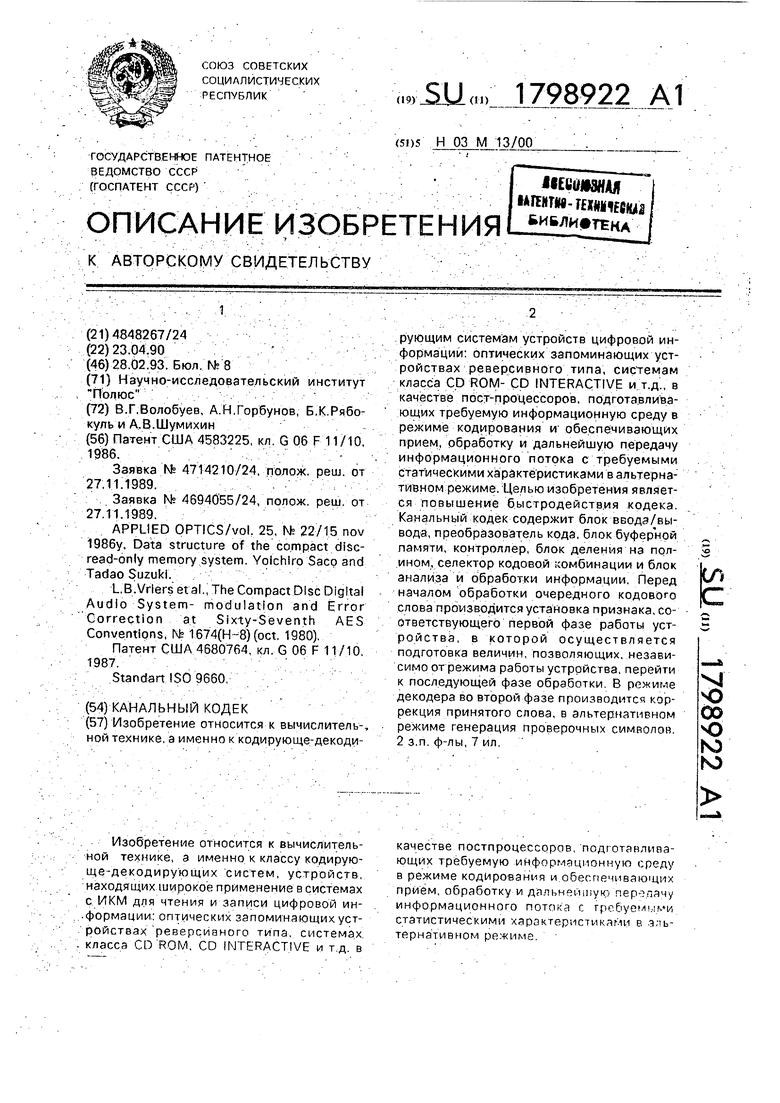

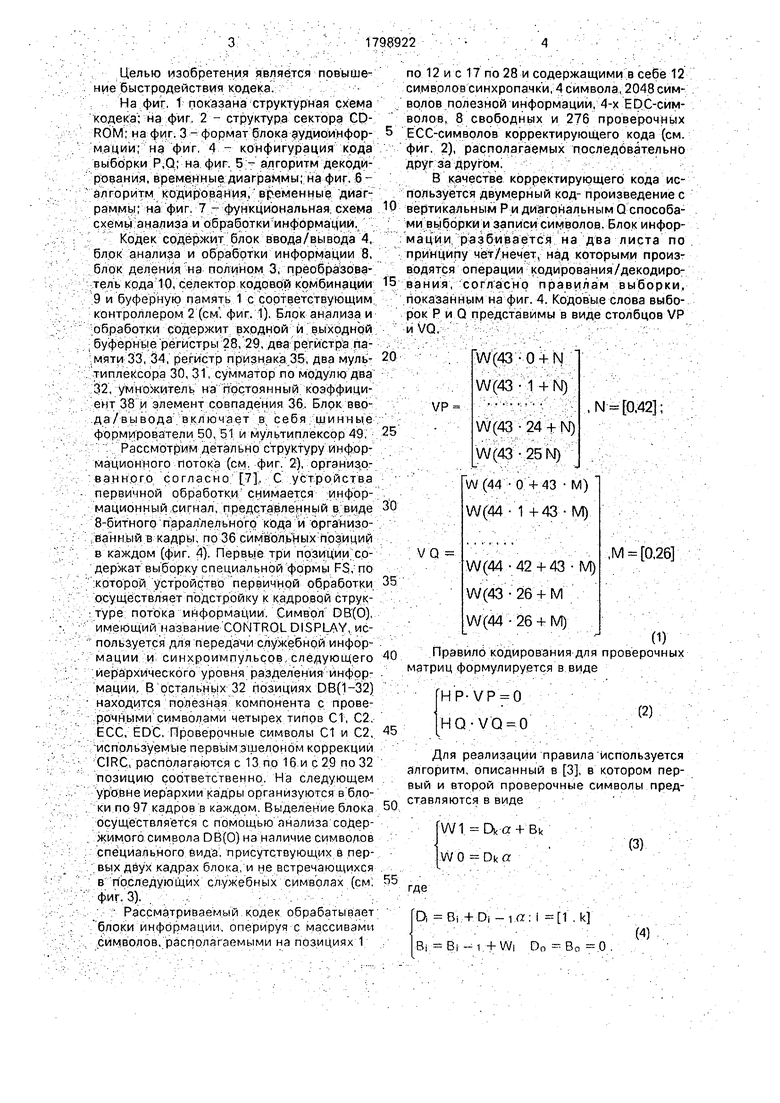

Кодексрдёржит блок ввода/вывода 4, блрк анализа и обработки информации 8, блок деления на полином 3, прёобраЗовател ь кода 10, селектор кодоврй комбинации ;9 и буферную память 1 с соответствующим : контроллером 2 (ем , фиг. 1). Блрк анализа и ;0бработк1 сРдержит входной и. вь1х6днрй ; буферные регйстрьг28, 29, два рег.йстр :па;мяти 33, 34, регистр признака 35, два муль т типлексора 30, 31 .сумматор по модул ю два 32, ум н ожител ь на гтоЪтря н н ы и. коэффици- ент 38 .и элемент совпадения 36, Блок ввр- .да/вы вода включает в себя .щи иныел формирователи 50, 51 и мультиплексор 49. . Рассмотрим детально структуру информационного потока (см, фиг. 2), оргэнизо- ваннрго согласно; 7, С устройства первичной обработки/ снимается инфор- мационн ыйi си гнал, представленн ы й в виде 8-битногр параллельного кРда и :ррга низо- , ванный в кадры, по 36 символ;ьных:прзиций в каждом (фиг. 4). Первые три позиции содержат выборку специальной формы FS,:no жоторой устройствопервичной обработки осуществляет подстройку к кадровой струк- : туре; потока информации. Символ DB (O), имеющий название COKITRQL , ис- ; пользуется для передачи служебной информации : ;и , сип хроим пул ьсрв, с л еду ю Щего . иера рхического у ров ня раздел е н ия информации, В остальных 32 позициях DB(1-32) находится полезная компонента с прове- .рочными символами четырех типов СТ, С2, ЁСС, EDC. Проверочные символы С1 и С2,

используемые первУм.зшелоном коррекций CIRC, располагаются с 13 по 16 и с 29 по 32 позицинэ соответственно. На следующем уро.вне иерархии кадры организуются в блоки по 97 кадров в каждом. Выделение блока

осуществляется с помощью анализа содержимого символа DB(0) на наличие символов специального вида, присутствующих в пер; вых двух кадрах блока., и не встречающихся

в последующих служебных символах (см; фиг.З). - .; ./ :: .. ;. - :: .. ;.: : - Рзссматриваемый к.одек обрабатывает

. блоки информации, оперируя с массивами Символов, располагаемыми на позициях 1

по 12 и с 17 по 28 и содержащими в себе 12 символов синхропачк и, 4 символа, 2048 символов полезной информации, 4-х Ер.С-сим- врлов, 8 свободных и 276 проверочных ЕСС-симврлов корректирующего кода (см. фиг. 2), располагаемых послёдРваЧельнр другзадругрм; - ; :-.-/.

В качестве корректирующего кода используется двумерный код- произведение с вертикальным Р и диагональным Q-способа- . ми выборки и записи символов, Блок инфор- мацйи/ р:азби1ваетсяСна два листа по принципу чёт/нечет, над которыми производятся операции кодирования/декодиро- ва н и я, со г л д с н о п р а вил а м выборки, показанным на фиг. 4. Кодовые слова выборок Р и Q представймы в виде столбцов VP и VQ. .- :: :: -:--v.;/, : . :. - ..-.-. :

VP

W(43-;i-f N)

,N 0,

W(43-244-N) W(43v25N)

W(44 0 +43 M) W(44- 1 +43-M)

V Q

W(44-42+43-M) W(43-26 + M W(44-26 + M)

,M 0,26

(1)

Правило кодирования для проверочных матриц формулируется в виде

45

HP-VP 0 HQ-VQ 0

(2)

Для реализации правила используется алгоритм, описанный в 3, в котором первый и второй проверочные символы пред- CQ ставляются в виде

fW 1 Dk a + Bk WO Dka

(3)

B5

где

О Bi..-H -D i -i.a: i 1. .+ Wi .0.

(4)

Компоненты многочлена синдромов S(x) выражаются через .элементы из (4) и представляются в виде

k+2

So 2 Wk +2 -i Bk +2 , i 1

s1 kJ2Wk+2 -,«k+2-|

i 1

Bk +2 +(1 + a)Dk +2.

(5)

из чего вытекает алгоритмическая совместимость процедур кодирования и вычисления синдромов. Это означает, что они могут быть выполнены на едином устройстве. Воспользовавшись для вычисления локатора процедурой Ченя, построим следующий механизм декодирования кодового слова (к+2,к) кода Рида-Соломона:

1.Вычисление So и Si согласно (5);

2.Поиск локатора о по проверке на равенство

3.Коррекция Wncnp.i Wi+S0. Будем осуществлять разработанную страте- -гию в два приема: в первой фазе производится вычисление So, S1, а во второй - поиск локатора и исправление ошибки.

Устройство для реализации этого механизма представлено на фиг. 7 и оно работает следующим образом. Перед началом обработки очередного кодового слова производится установка признака, соответствующего первой фазе декодирования. Затем по приходу очередного тактового импульса СО на вход 23 производится защелкивание входной информации в буферном регистре 28. Каждый шаг алгоритма (4) будем называть элементарной операцией, причем каждая такая операция состоит из двух тактов, в которых раздельно вычисляются величины DI и В|. Во втором такте первой операции осуществляется загрузка рекурсивной структуры, на которой реализуется алгоритм декодирования, для чего на выходе мультиплексора 30 устанавливается содержимое буферного регистра 28, а на выходе мультиплексора 31 выставляется уровень логического нуля. По приходу очередного импульса С1 на вход 24 символ Wk+2 заносится в первый динамический регистр памяти 33. В предыдущем такте по импульсу С2. подаваемому на вход 25, производится предустановка второго динамического регистра 34, для чего на выходе мультиплексоров 30 и 31 устанавливается сигнал нулевого уровня. В следующей операции по приходу импульса С2 выполняется

первый шаг рекурсии (4) относительно Oi. Для этого на выходе мультиплексора 30 устанавливается содержимое умножителя на константу 38, а на выходе 31 - содержимое 5 регистра 33. Содержимое выхода сумматора по модулю два 32; представляющее собой DI, заносится в регистр 34. К приходу очередного импульса С1 подготавливается величина В|, для чего на выходе мультиплек0 сора 30 устанавливается содержимое входного буферного регистра 28, а на выходе мультиплексора 31-содержимое регистра 33. После (k-И) описанных шагов алгоритма производится вычисление коэффициентов

5 синдромного многочлена S(x) согласно (5). Для этого в (k+2)-n операции вычисляется величина Di(1+o), что осуществляется с помощью установки на выходе мультиплексора 21 содержимого регистра 34. а на выходе

0 мультиплексора 30-содержимого выхода умножителя на константу 38. Переход ко второй фазе декодирования изменяет порядок выборки компонент кодового слова если в первой фазе выборка символов осу5 ществлялась с уменьшением значения i. то во второй оно наращивается. Для соединения фаз между собой вводится дополнительная операция A-i, позволяющая произвести подготовку к процедуре Ченя и коррекции.

0 В этой операции по импульсу СЗ, поступающему на вход 26, в регистр признака 35 заносится сумма содержимого регистров 33 и 34, представляющая коэффициент Si синдромного многочлена. Во втором такте этой

5 операции по импульсу С2 содержимое первого регистра 33, равное So. переносится в регистр 34, для чего на выходе мультиплексора 31 устанавливается содержимое регистра 33, а на выходе мультиплексора

0 30-уровень логического нуля. Таким образом, к моменту защелкивания во входном регистре 28 символа Wo в группе регистров содержатся:

регистр 35 - коэффициент Si синдром5 ного многочлена;

регистры 33 м 34 - коэффициент So синдромного многочлена. При такой конфигурации легко организовать рекурсивную процедуру Ченя, для чего

0 в каждой последующей операции производится умножение содержимого регистра 34

на примитивный элемент поля GF(28} с сохранением результата в том же регистре. Это осуществляется с помощью установки в

5 первом такте операций на выходе мультиплексора 20 содержимого выхода умножителя на константу 38, а на выходе мультиплексора 31 - уровня логического нуля. В другом такте этой группы операций на выходе сумматора 32 устанавливается сумма текущего символа с содержимым регистра 33, которая по импульсу С4;, подаваемому на вход 27, защелкивается в выходном буферном регистре 29. В случае совпадения содержимого регистра 34 и регистра признака 35 элемент совпадения 36 вырабатывает на выходе 37 признак WR, который на время/следующей операции блокирует выборку очередного символа WH-I, что дает возможность провести операцию коррекции, во втором такте которой в очередной разг изменяется содержимое регистра 34. При: этом признак WR переходит в пассивное состояниё, и пррцесс продолжается до значения (k+2). Для перехода к следующей в ыбр рке до бэ в л я етс я е ще од на дополни;тель ная рперация Ап-и, в которой произво дится установка в исходное состояние регистра 34 и изменение признака, характеризующего «фазу декодирования, Изложен: ный алгоритм, о:формлен ны.й в виде временных диаграмм крдрв операций про- цеесора, представлен на фиг, 5,.; ;

В альтернативном режиме на первых k шагах в первой фазе алгоритм кодирования точно совпадает, с описанным выше алгоритмом. На (к+1)-й операции в лервом такте в регистре 33 сохраняется накопленное значение Bk, для чего;на выходе мультиплексора 30 устанавливается нулевой уровень, а на выходе мультиплексора 31 - содержимое регистра 33. Во втором такте в регистр 34 заносится первое проверочное слово Wi, которое получается на выходе сумматора 38 при установке на выходе мультиплексора 30 содержимого умножителя на константу 38, а на выходе мультиплексора 31-содержимого регистра 33. В последующей операции в первом такте.осуществляет- ся сохранение величины Bk, а во втором такте в регистр 34 заносится символ Wo, для чего на выходе мультиплексора 31 уставав. ливается содержимое регистра 34, а на ЁЫходе мультиплексора 30 - содержимое . регистра 33. Так же. как в режиме, декодиро- , ванйя, здесь вводится дополнительная опе- рацйя. в первом такте которой по импульсу С4 в выходной буферный регистр 29 заносится второе проверочное слово Wo из (3). для чего на выходе мультиплексора 30 устанавливается сигнал нулевого уровня, а на выходе мультиплексора 31 - содержимое регистра 34. Во втором-такте этой операции по импульсу.С2 в 34 заносится первое про- верочное слово Wi, получающееся на выходе мул ьтиплексбр а 30 содержимого регистра 34, а на выходе 31 - содержимого регистра 33. В последующей операции; в первом тахте содержимое регистра 34 переносится в выходкой буфер 29 аналогично с

предыдущей операцией, Алгоритм иллюстрируется временными диаграммами на

фИГ. 6. ,. .-. ; , ... .. - -, ..: . ..

Важной функцией рассматриваемого1

процессора является обмен по внешним информационным шинам. На это отводится специальная операция, в которой информа-г : ция заносится во входной буфер 28 а затем, по импульсу С4 переносится в выходной буферный регистр 29. Для этого на выходе мультиплексора 30 устанавливается содержимое 28, а мультиплексор 31 коммутируется так, чтобы на его выходе присутствовал логический нрль. Для развязки операций

внутренней обработки с операциями внешнего интерфейса используется бланкирование тактовых импульсов С1, С2 на время обмена, так что информация в регистрах 33 и 34, хранящих результаты обработки, сохраняется, По окончании обмена протокол обработки восстанавливается. Операции съема данных с одной внешней шины и передачи на другую удобно .совместить, для . чего в операции, предшествующей обмену.

производится запись символа DOUT из внут- ;.; р.ённего буфера по шине 7 во входной регистр 28 с последующей установкой на выходе регистра 29, В самой операции обмена производится защелкивание данных

DIN в 28, снимаемых, в зависимости от режима работы системы, либо с шины 5, либо с шины 7. В последующей операции производится запись принятой информации во внешнее буферное ЗУ 1, Процесс иллюстрируется временными диаметрами (см. фиг. 5, б). Перемещение данных по шинам осуществляется с помощью блока ввода /вы вода 4. Управление передачей данных производится сигналами SO и SK поступающими на

управляющие входа 14, 15, и задающими направление переноса информации на фор- мироватёлях 55 и 56 соответственно. Мультиплексор 49 используется для установки на. входе буферного регистра 28 принимаемых

с внешних шин информационных символов, для чего задействованы два его входа. Третий вход мультиплексора используется в режиме кодирования при подготовке информационного блока для занесения в

начало блока синхропачки. а также передачи . символов, сгенерированных схемой деления на полином 3, на выход системы, представляющих собой остаток от деления на. многочлен- генератор.

; G(x)(X16+Xlj+X2+1)(X16+X2+X+l). (6)

5

Управление старшим разрядом мультипле- сора можно осуществлять с помощью признаков, вырабатываемых в контроллере 2 Поиск, активного на интервале, соответст- вующ.е.м символам синхропачки. и вставка

CRC, активного на требуемом интервале, объединенных в общий сигнал.:

Использование в качестве среды распространения, информационного сигнала отичёского канала приводит к необходимости применения шумоподобных сигналов, позволяющих эффективно выделять полезную . компоненту на выходе фотоприемника, наличие разделительной емкости которого может приводить к потерям в принимаемом Сигнале. С этой целью используется генератор псевдослучайной последовательности, содержимое выхода которого замешивается; в информсигнал. Этот генератор выполняется в виде сдвиговой схемы с обратными связями, удовлетворяющими уравнению

ции вырабатывается признак Захват /эа- .. прещающий работу схемы сравнения до V. конца захв:аче.нного блока и переводящий ; контроллер буферного ЗУ 2.в режим,приема 5 информационных символов, для которого характерно листоеание данных :по ч ет/не- .. .-: .нету-: .. /: ,-:-; -::.:.. / ..: ;... .,: .-. :... .; Контроллер буферного ЗУ 2 предстзвля- ёт собой два генератора, работающих в 10 мультиплексном режиме, один из которых предназначен для операций вбода/вывода данных из кодека, а второй поддерживает : способ выборки символов согласно описанному ранее алгоритму работы процессора.

. .. -.-..-.- ,. : , :. ..-:,

.Формула и зо б ре т е н и я

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для кодирования | 1987 |

|

SU1462494A1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Устройство для кодирования | 1985 |

|

SU1275782A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

Изобретение относится к вычислитель-, ной технике, а именно к кодирующе-декоди. рующим системам устройств цифровой информации: оптических запоминающих устройствах реверсивного типа, системам класса CD ROM- CD INTERACTIVE и. т.д., в качестве пост-процессоров, подготавливающих требуемую информационную среду в режиме кодирования и- обеспечивающих прием, обработку и дальнейшую передачу информационного потока с требуемыми статическими характеристиками в альтерна: тивном режиме. Целью изобретения является повышение б.ыстродейств.ия кодека. Канальный кодек содержит блок ввода/вывода, преобразователь кода, блок буферной памяти, контроллер, блок деления на пол- .ином, селектор кодовой комбинации и блок анализа и обработки информации. Перед началом обработки очередного кодового слова промзводится установка признака, соответствующего первой фазе работы устройства, в которой осуществляется подготовка величин, позволяющих, независимо от режима работы устройства, перейти к последующей фазе обработки. В режиме декодера во второй фазе производится коррекция принятого слова, в альтернативном режиме генерация проверочных символов. 2 з.п. ф-лы, 7 ил. М о 00 Ю ю ю

,Х-5 Х+ 1 .

(П

Он является составной частью преобразователя кода 19, представляющего собой сумматор по модулю два, на один из входов которого поступают информационные символы, а на другой-замещиваёмая псе.в- д ос луча и на я по следо ватель н ост ь с в ыхода .рассмотренного выше генератора. Вход преобразователя кода подключается; к:ин- -формационному выходу блока анализа и обработки информации, а выход подсоединяется к входам шинных формирователей устройства ввода/вывода 4. 8 режиме коди- рования преобразованию подвергаются данные; устанавливаемые на выходе процессора в интерфейсную операцию: в ос- тальные моменты времени выход: генератора бланкируется и не мешает обработке осуществляемой над информационным массивом. В альтернативном режиме .преобразуются входные данные принятые из канала и последующая обработка производится над блоком истинных данных.

Для нормальной реализации поиска и захвата блока информации синхропачка, располагающая в заголовке преобразованию не подвергается, а любая информационная выборка, организованная в блок, начинается с последовательности нулевых символов некоторой длины, являющейся компонентой межблочного пространства. Поисковые функции в системе выполняет селе.ктор кодовой комбинации, представляющий собой многоступенчатую схему-сравнения, вырабатывающую при наличии рассогласования флаг ошибки FIND, который поступает на вход 17 контроллера. По-; явление такого флага устанавливает систему в режим обнаружения синхропэч- ки, поиск которой осуществляется в первой половине каждого очередного приходящего кадра. При успешном завершении опера- 1. Канальный кодек, содержащий блок ; буферной памяти, контроллер, блок деления на полином и блок ввода-вывода, первая шина ввода-вызода которого является первой информационной шиной канального кодека, выход контроллера подключен к Адресной, шине блока буферной памяти, шина ввода-вывода которого объединена с второй шиной ввода-вывода блока ввода- . вывода и является второй информационной шиной, канального кодека, от л и ч а ю щи й- с я тем/что, с целью повышения быстродей-: ствия кодека, в него введены блок анализа и обработки информации, селектора кодовой комбинации и преобразователь кода, выходы которого подключены к перв ым информационным входам блока ввода-вывода, выходы которого подключены к информационным входам блока анализа, и обработки

информации и входам блока.деления на полином, выход которого подключён к второму информационному входу блока ввода-выво- да, первый и второй управляющие входы которого являются одноименными входами канального кодека, информационные выходы блока анализа и: обработки информации

подключены к входам преобразователя ко- дов и селектора кодовой комбинации/выход которого подключен к управляющему входу контроллера, управляющий выход- первый-. четвертый управляющие входы и первый- пятый тактовые входы блока анализа и обработки информации являются соответственно управляющим выходом, третьим-ше- стым управляющими входами и первьгм-пятым тактовыми входами канального кодека,

тактовыми входами блока, первые и вторые управляющие входы первого и второго мультиплексоров являются соответственно первым-четвертым управляющими входами блока, Информационный вход первого буферного регистра является информационным входом блока.

имхроммзомия : 2 Sai-что Заг. o/iofcoK :4 Байта

Донные 2048 байт

CRC симЬоиы:4 .

Пусто Г8 байт

Р-симЬоиы: 172

0-симЬоиы:104 &аита

Фи г. а

Фиг. 3

I

fxi

Чх

ггб8Ш

К . i

I

| Патент США 4583225, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Заявка № 4714210/24, полож | |||

| реш | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Заявка № 4694055/24, полож | |||

| реш, от 27.11.1989 | |||

| APPLIED OPTICS/vol | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Yqlchiro Saco and Tadao Suzuki | |||

| L.B.Vrlers etal.; The Compact Disc Digital Audio System- modulation and Error Correction at Sixty-Seventh AES Conventions, № 1674(H-8) (oct | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| ПатентСША 4680764, кл.С 06 F 11/10 | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| АВТОМАТИЧЕСКАЯ МАСЛЕНКА ДЛЯ КРЕЙЦКОПФОВ | 1928 |

|

SU9660A1 |

Авторы

Даты

1993-02-28—Публикация

1990-04-23—Подача