Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных средств, требующих высокопроизводительной обработки информации, например, для цифровой обработки изображений.

Известно устройство для обработки цифрового сигнала, содержащее последовательно соединенные арифметические блоки, объединенные в две группы вычислителей (патент, РФ N 2033637, кл. G 06 F 17/14, 09.07.91).

Устройство обеспечивает возможность параллельной обработки информационных потоков, однако его использование ограничено возможностью однонаправленного обмена информацией.

Наиболее близким аналогом-прототипом является вычислительная система, содержащая управляющий (базовый) компьютер, блоки памяти, контроллер ввода-вывода, вычислительные блоки и коммутаторы, группы управляющих и информационных выходов которых соединены с входами соответствующих блоков памяти (патент РФ, N 2042193, кл. G 06 F 15/16, 08.10.91).

Эта вычислительная система обладает широкими функциональными возможностями за счет увеличения числа одновременно работающих на базе общей шины групп вычислительных блоков и организации их взаимодействия, однако в ней необходимо проведение промежуточных операций, связанных с переадресовкой и перезапуском команд, что снижает быстродействие системы.

Сущность изобретения состоит в том, что в вычислительную систему, содержащую базовый компьютер, блоки памяти, контроллер ввода-вывода, вычислительный блок и коммутатор, первые и вторые группы управляющих выходов которого соединены с первыми группами управляющих входов соответственно первого и второго блоков памяти, а первые и вторые группы информационных входов-выходов коммутатора подключены к группам информационных входов-выходов соответственно первого и второго блоков памяти, введены блок управления, блок задания и контроля тактовой частоты и буферный блок, причем группа управляющих входов-выходов базового компьютера соединена с первыми группами управляющих входов-выходов соответственно блока управления и третьего блока памяти, группа информационных входов-выходов базового компьютера подключена к группе информационных входов-выходов третьего блока памяти и третьей группе информационных входов-выходов коммутатора, а группа адресных выходов базового компьютера соединена с первыми группами адресных входов соответственно третьего блока памяти и контроллера ввода-вывода, первые, вторые и третьи группы адресных выходов которого подключены к группам адресных входов соответственно буферного блока и первого и второго блоков памяти, первая группа управляющих выходов и группа адресных выходов блока управления подключены к вторым группам соответственно адресных и управляющих входов третьего блока памяти, группа информационных выходов которого соединена с группами информационных входов блока управления и контроллера ввода-вывода, группа управляющих выходов которого подключена к первой группе управляющих входов коммутатора, вторая группа управляющих входов которого соединена с второй группой управляющих выходов блока управления, причем группа управляющих входов-выходов блока управления подключена к группе управляющих входов-выходов контроллера ввода-вывода, а третья группа управляющих выходов блока управления соединена с группой управляющих входов буферного блока, группа информационных входов-выходов которого соединена с четвертой группой информационных входов-выходов коммутатора, при этом группы информационных, адресных и управляющих выходов буферного блока подключены соответственно к группам информационных, адресных и управляющих входов вычислительного блока, первая группа информационных выходов которого соединена с группой информационных входов буферного блока, первая группа выходов блока задания и контроля тактовой частоты соединена с группами тактовых входов контроллера ввода-вывода, блока управления и вычислительного блока, вторая группа информационных выходов которого подключена к группе входов блока задания и контроля тактовой частоты, второй группой выходов соединенного с группой управляющих входов блока управления, информационным входом подключенного к соответствующему выходу вычислительного блока, причем базовый компьютер выходом соединен с управляющим входом блока задания и контроля тактовой частоты, а вычислительный блок выполнен в виде матрицы процессорных элементов.

Такая вычислительная система (далее система НБМПЭ) обеспечивает возможность параллельной обработки однородной и разнородной информации. При этом арифметико-логическую обработку и процессы обмена и передачи информации производят и по ортогональным направлениям с обменом между потоками информации ортогональных направлений без проведения промежуточных операций, что существенно повышает быстродействие.

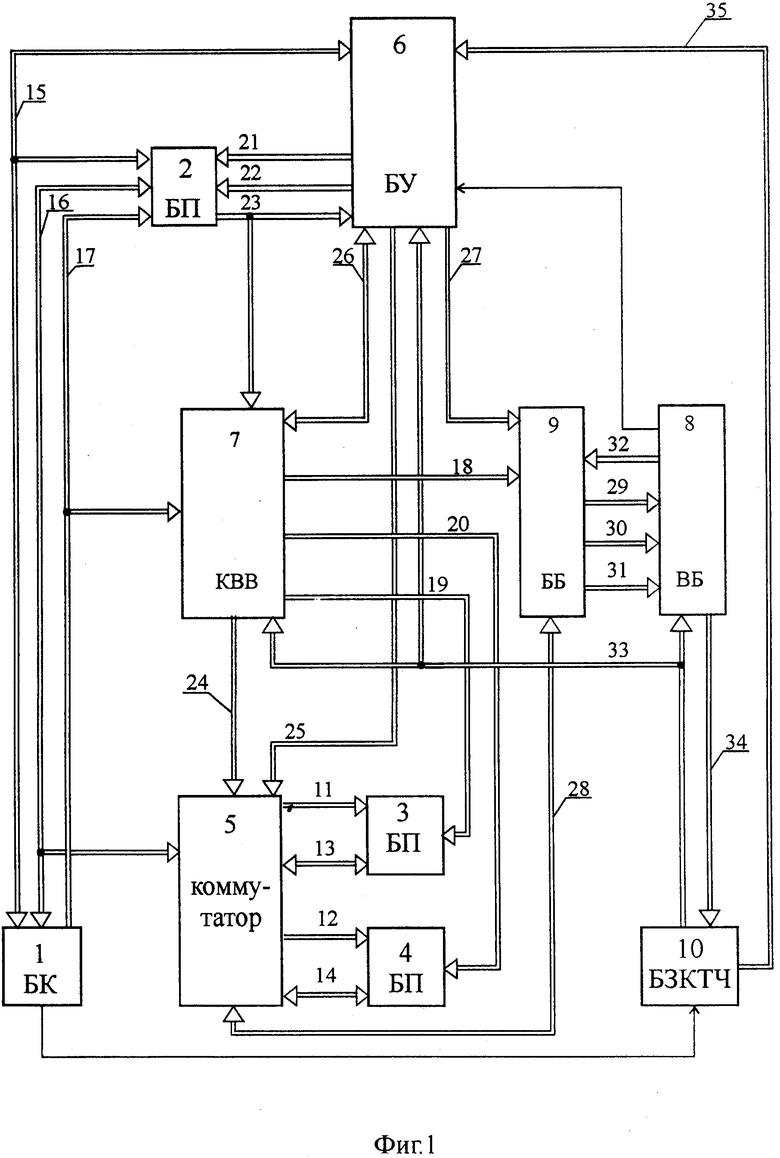

На фиг. 1 представлена блок-схема системы НБМПЭ; на фиг. 2-12 приведены функциональные схемы выполнения отдельных блоков и устройств, входящих в эти блоки.

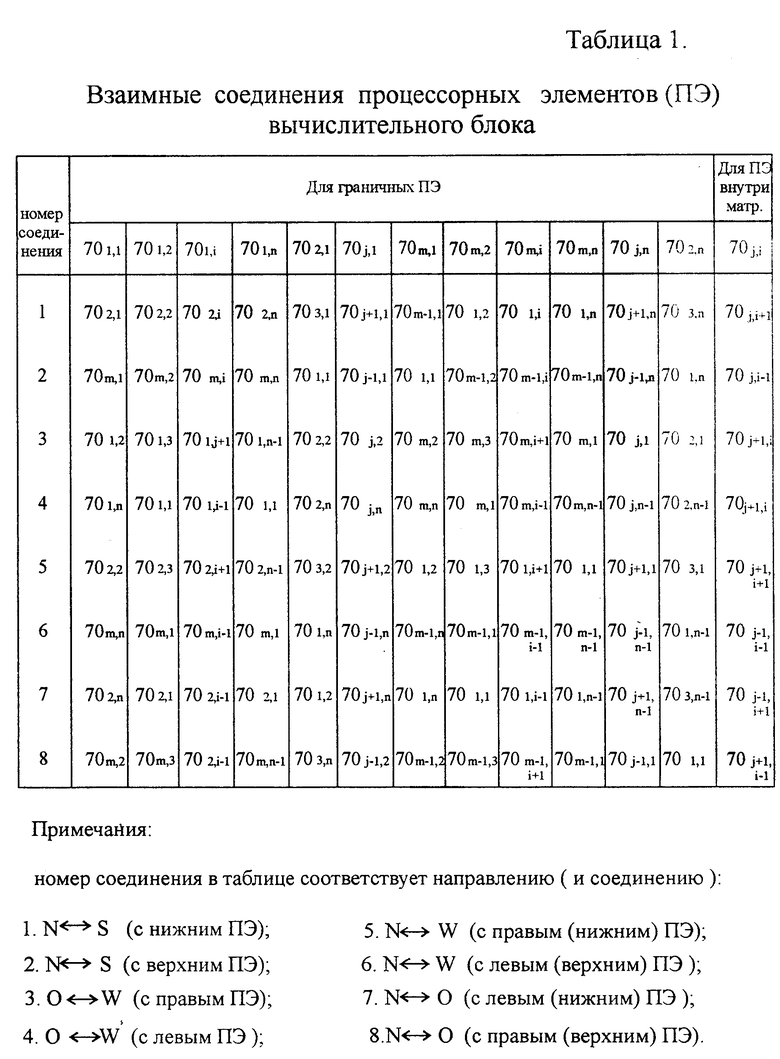

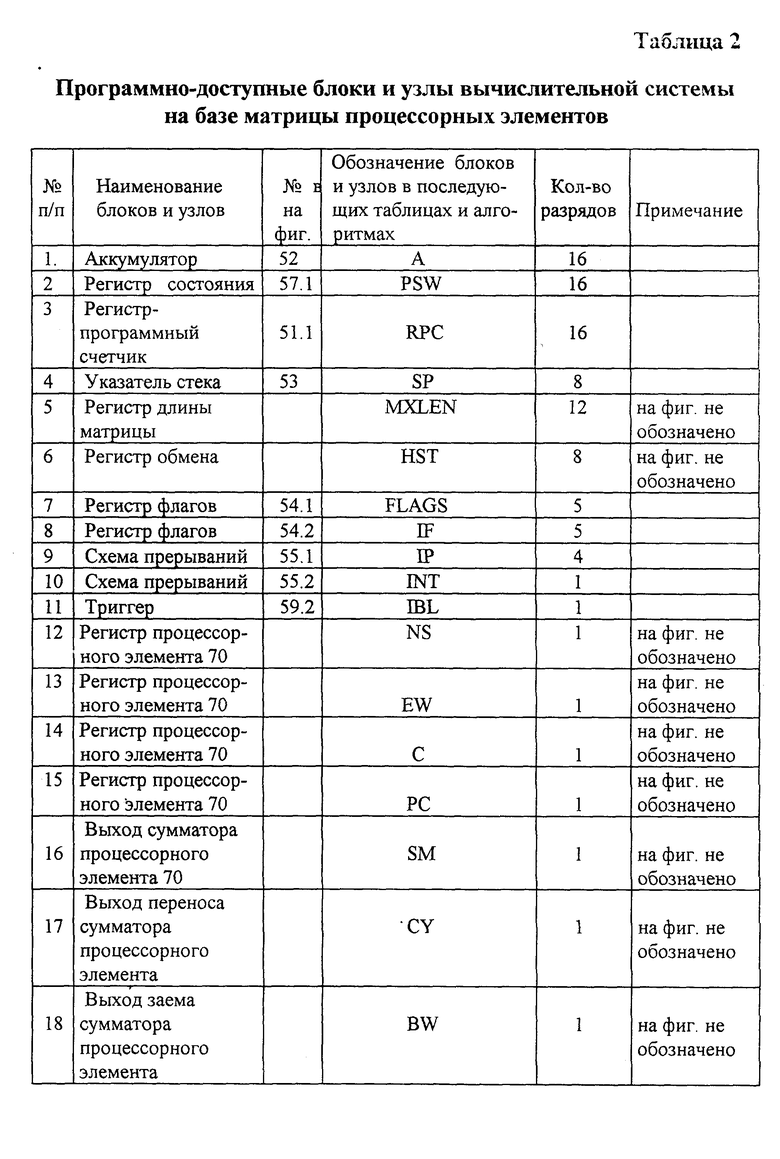

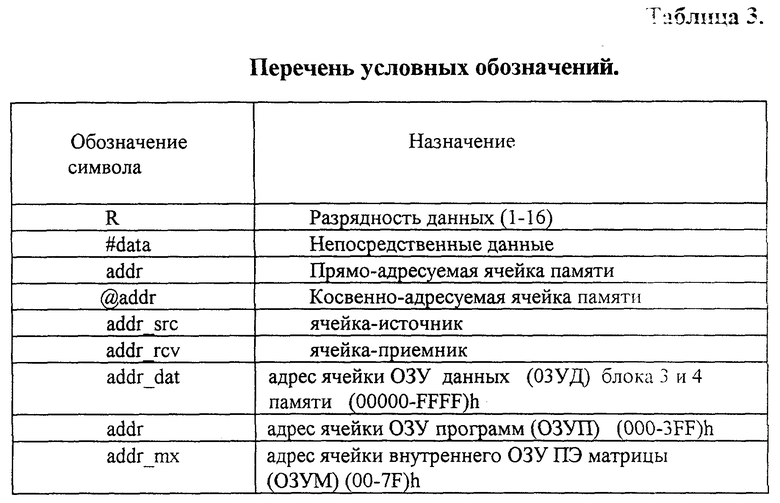

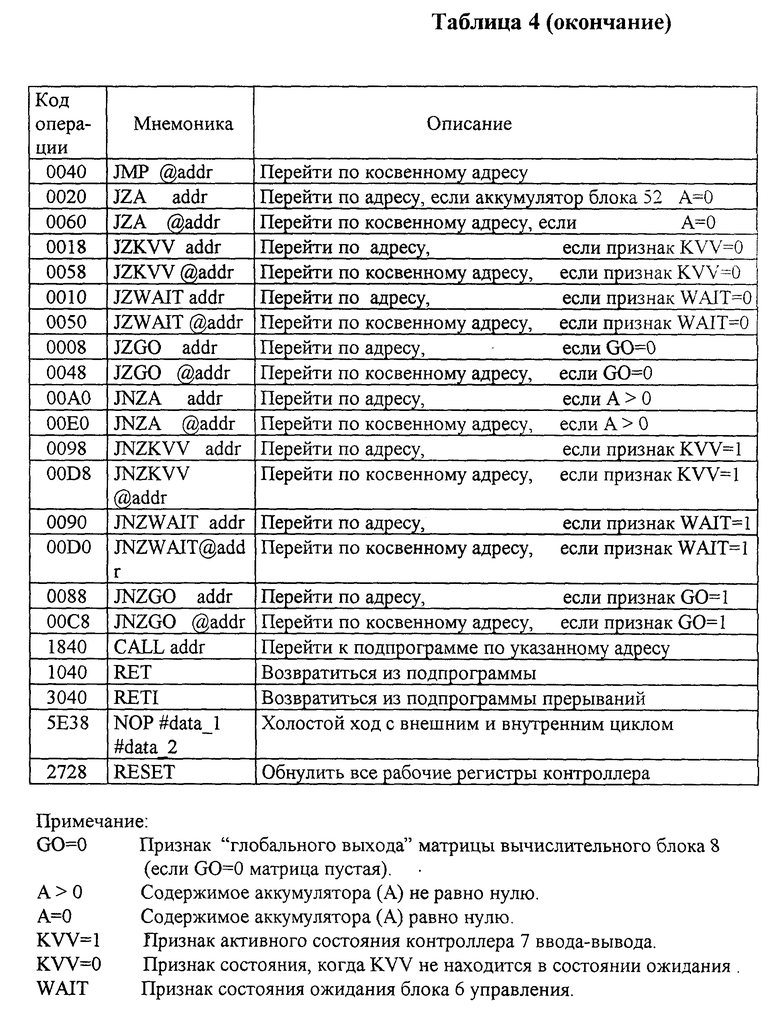

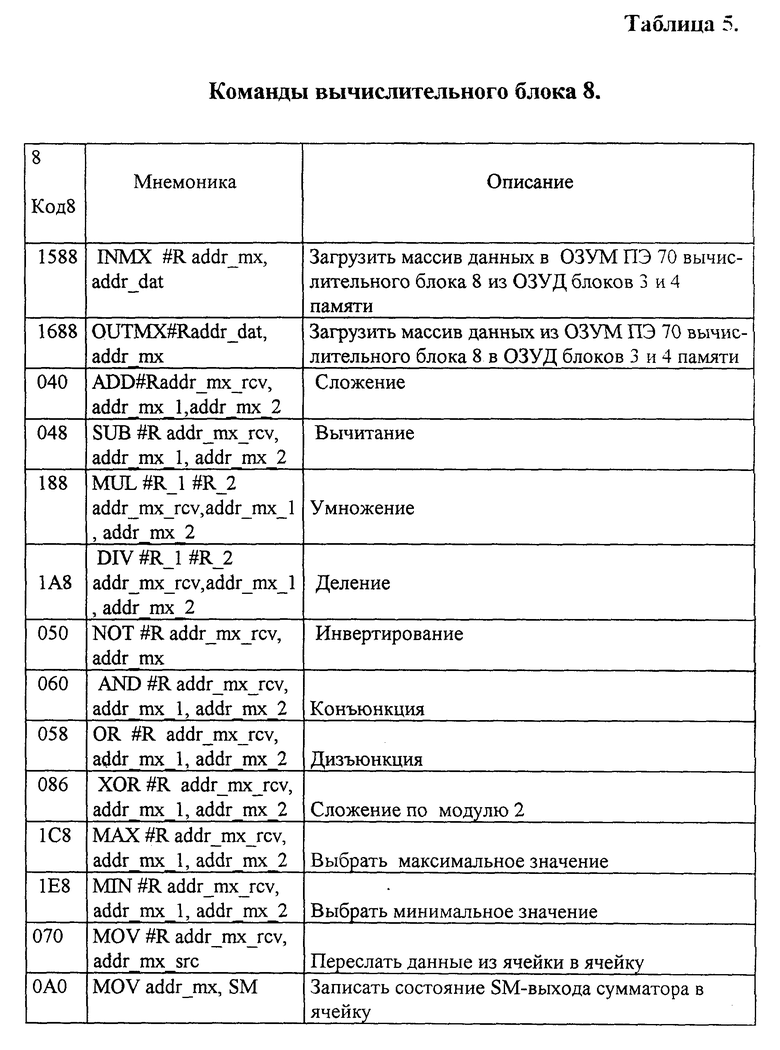

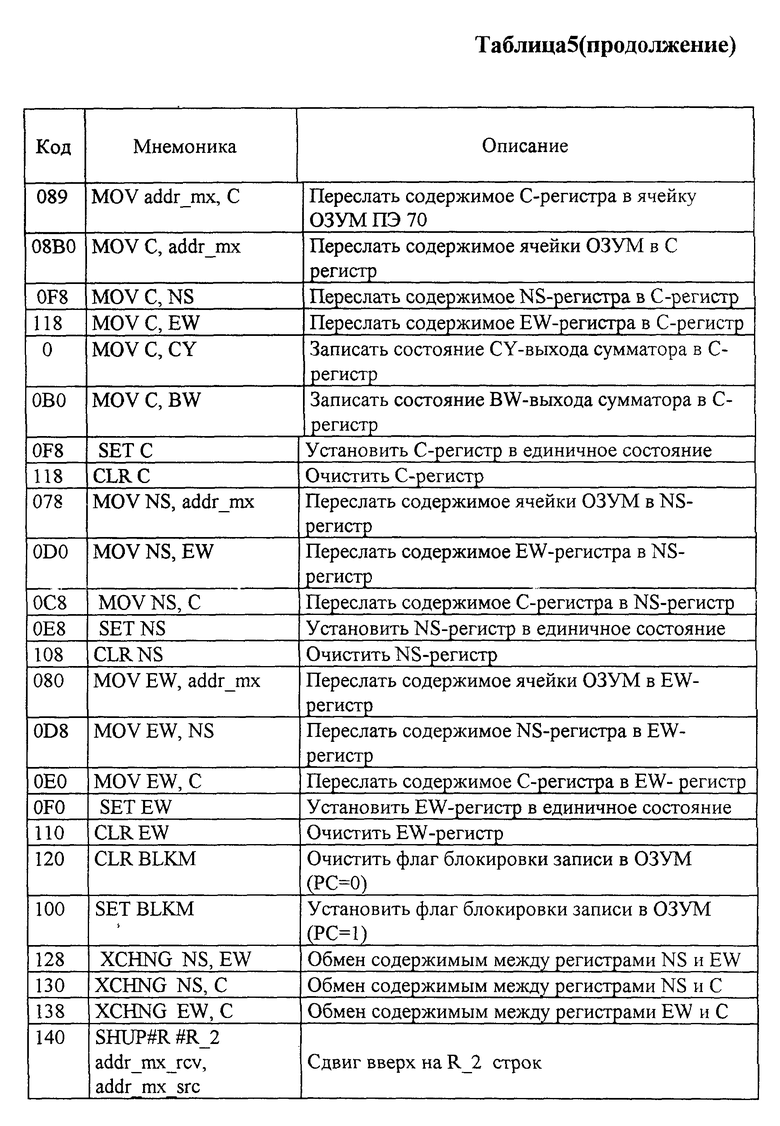

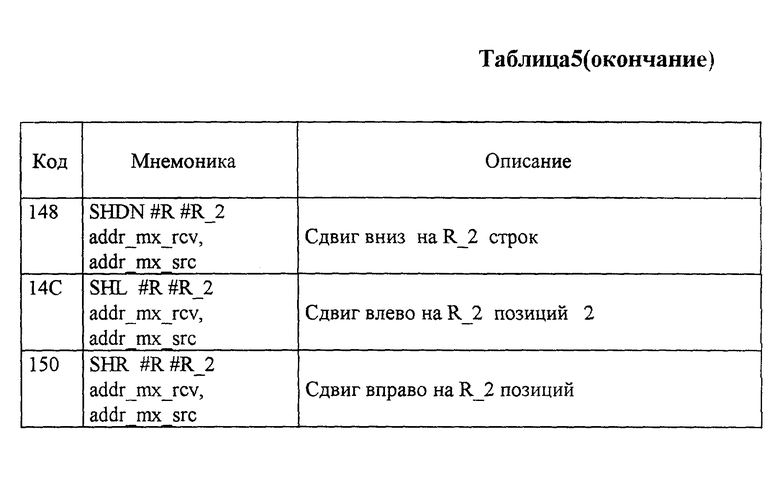

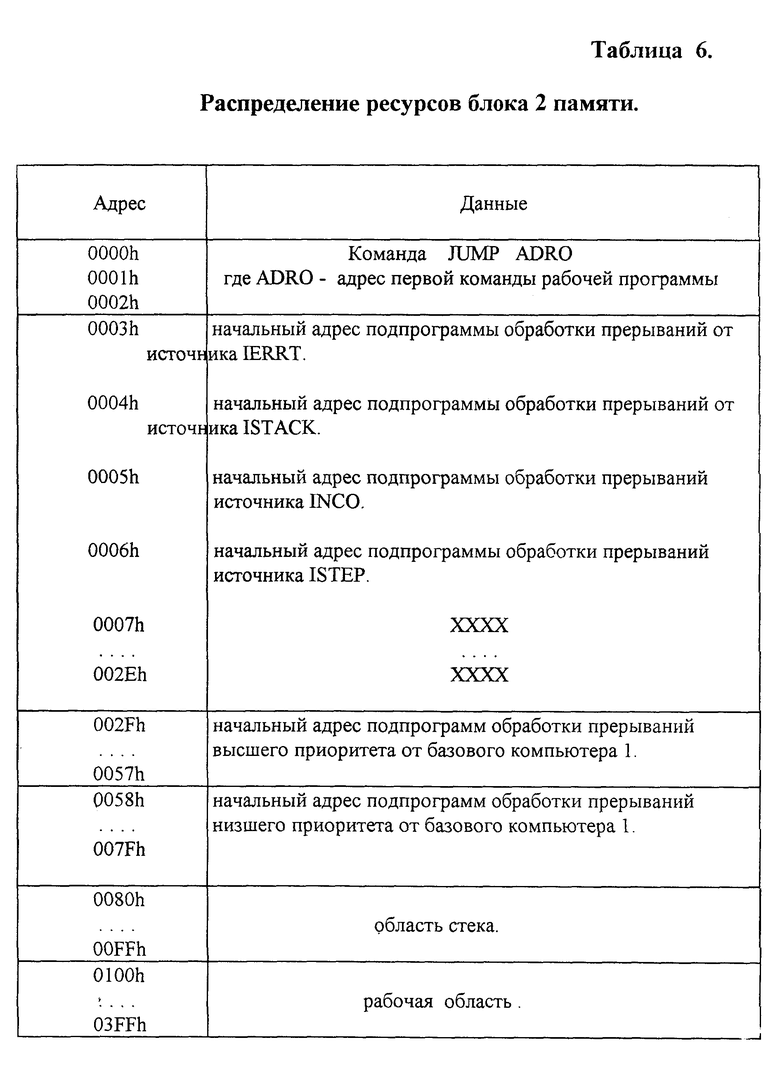

В табл. 1 приведена информация о взаимных соединениях процессорных элементов вычислительного блока, в табл. 2 указаны программно-доступные блоки и узлы системы НБМПЭ, в табл. 3 приведен перечень условных обозначений, применяемых в описании команд, в табл. 4 и 5 расписан состав команд, входящих в группы команд блока управления и вычислительного блока соответственно, в табл. 6 приведена расшифровка адресации.

Система НБМПЭ (фиг. 1) включает базовый компьютер 1, выполненный в виде, например, компьютера IBM PC (386 серии) и предназначенный для введения информационных потоков, их диспетчеризации и вывода обработанной информации, и блоки 2-4 памяти, выполненные в виде оперативных запоминающих устройств (ОЗУ) и предназначенные соответственно: блок 2 - для хранения программ, блоки 3 и 4 - для хранения данных.

При этом блок 2 выполнен на микросхеме IDT7026S двухпортовой памяти, а блоки 3 и 4 выполнены на микросхеме MT5LC512K8D4.

Система НБМПЭ содержит также коммутатор 5, предназначенный для одновременного и независимого подключения соответственно информационных и адресных входов блоков, блок 6 управления, предназначенный для формирования команд управления и обеспечения обмена управляющими кодами прерывания с базовым компьютером 1, контроллер 7 ввода-вывода, предназначенный для формирования сигналов управления, вычислительный блок 8, выполненный в виде двухмерного массива процессорных элементов (ПЭ), реализующего SIMD - архитектуру, и предназначенный для арифметико-логической обработки, обмена и передачи информации, буферный блок 9, предназначенный для реализации процедуры обмена данными между вычислительным блоком 8 и блоками системы, а также блок 10 задания и контроля тактовой частоты, предназначенный для выработки единой рабочей тактовой частоты и контроля выходных частот элементов вычислительного блока 8.

Первые и вторые группы управляющих выходов коммутатора 5 соединены шинами 11 и 12 с первыми группами управляющих входов соответственно блоков 3 и 4 памяти, а первые и вторые группы информационных входов-выходов коммутатора 5 подключены шинами 13 и 14 к группам информационных входов-выходов соответственно блоков 3 и 4 памяти.

Группа управляющих входов-выходов базового компьютера 1 шиной 15 соединена с первыми группами управляющих входов соответственно блока 7 управления и блока 2 памяти, группа информационных входов-выходов базового компьютера 1 подключена шиной 16 к группе информационных входов-выходов блока 2 памяти и третьей группе информационных входов- выходов коммутатора 5, а группа адресных выходов базового компьютера 1 шиной 17 соединена с первыми группами адресных входов соответственно блока 2 памяти и контроллера 7 ввода-вывода.

Первые, вторые и третьи группы адресных выходов контроллера 7 ввода-вывода шинами 18-20 подключены к группам адресных входов соответственно буферного блока 9 и блоков 3 и 4 памяти.

Первая группа управляющих выходов блока 6 управления шинами 21 и шинами адреса 22 подключена к вторым группам соответственно адресных и управляющих входов блока 2 памяти, группа информационных входов-выходов которого шиной 23 соединена с группами информационных входов соответственно блока 6 управления и контроллера 7 ввода-вывода.

Группа управляющих выходов контроллера 7 ввода-вывода шиной 24 подключена к первой группе управляющих входов коммутатора 5, вторая группа управляющих входов которого шиной 25 соединена с второй группой управляющих выходов блока 6 управления.

Группа управляющих входов-выходов блока 6 управления шиной 26 подключена к группе управляющих входов-выходов контроллера 7 ввода- вывода, а группа управляющих выходов блока 6 управления шиной 27 соединена с группой управляющих входов буферного блока 9, группа информационных входов-выходов которого шиной 28 соединена с четвертой группой информационных входов-выходов коммутатора 5.

Группы информационных, адресных и управляющих выходов буферного блока 9 через шины 29 и 30, 31 подключены соответственно к группам информационных, адресных и управляющих входов вычислительного блока 8, группа информационных выходов которого шиной 32 соединена с второй группой информационных входов буферного блока 9.

Группа выходов блока 10 задания и контроля тактовой частоты шиной 33 соединена с группами тактовых входов контроллера 7 ввода-вывода, блока 6 управления и вычислительного блока 8. группа выходов которого шиной 34 соединена с группой входов блока 10 задания и контроля тактовой частоты, группой выходов соединенного шиной 35 с группой управляющих входов блока 6 управления, информационным входом подключенного к соответствующему выходу вычислительного блока 8. при этом базовый компьютер 1 выходом подключен к управляющему входу блока 10 задания и контроля тактовой частоты.

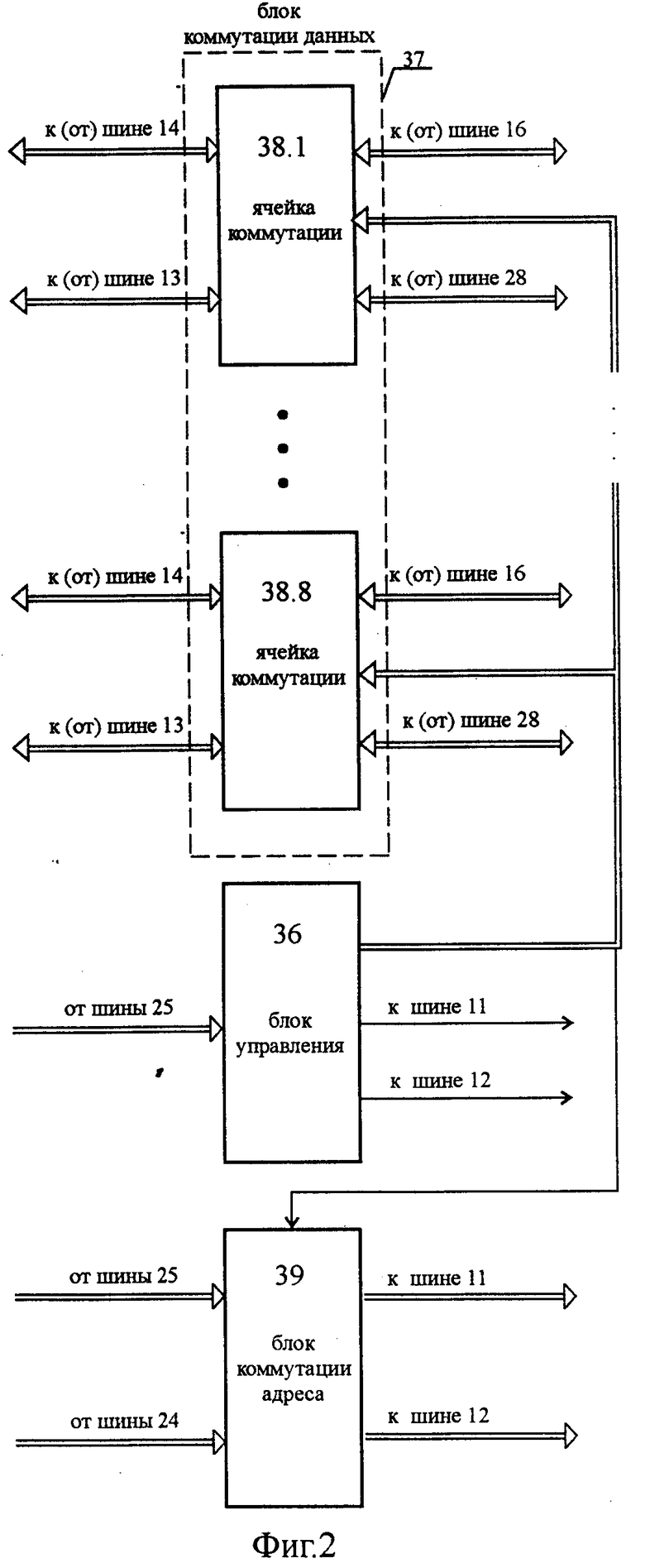

Коммутатор 5 (фиг. 2) содержит блок 36 управления, блок 37 коммутации данных, включающий восемь параллельно соединенных ячеек коммутации 38 и блок 39 коммутации адреса.

Блок 36 управления группой входов подключен к группе управляющих выходов коммутатора 5, подключенных к шине 25, группой входов соединен с группой входов блока 37 коммутатора данных и одновременно подключен к управляющему входу блока 39 коммутации адреса. Первая, вторая, третья и четвертая группы входов-выходов блока 37 коммутации соединены с группами входов-выходов коммутатора 5, подключенных соответственно к шинам 13, 14, 16 и 28, первая и вторая группы входов блока 39 коммутации адреса соединены соответственно с группами входов коммутатора 5, подключенных к шинам 24 и 25, а первая и вторая группы выходов блока 39 коммутации адреса соединены с группами выходов коммутатора 5, подключенных соответственно к шинам 11 и 12. Ячейки 38 коммутации блока 37 коммутации данных своим первым входом-выходом подключены к первой группе входов-выходов блока 37 коммутации данных, своим вторым входом-выходом соединены с второй группой входов-выходов блока 37 коммутации данных, своим третьим входом-выходом подключены к третьей группе входов-выходов блока 37 коммутации данных, своим четвертым входом-выходом соединены с четвертой группой входов-выходов подключенных к группе входов блока 37 коммутации данных, а группой входов соединены с группой управляющих входов блока 37 коммутации данных.

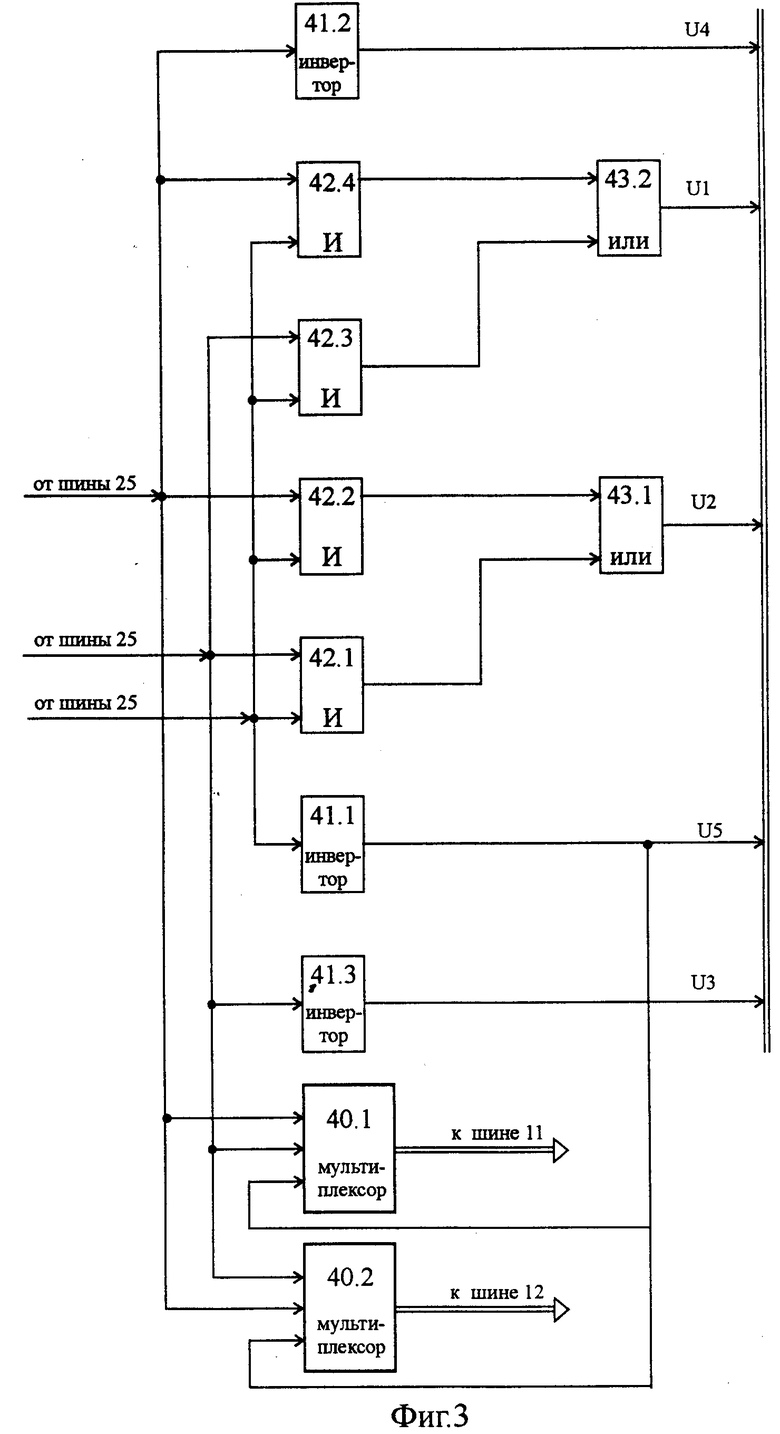

Блок 36 управления содержит (фиг. 3) два мультиплексора 40 (40.1-40.2), три инвертора 41 (41.1-41.3), четыре элемента И 42 (42.1-42.4) и два элемента ИЛИ 43 (43.1-43.2). Мультиплексоры 40 первым и вторым входами соединены с соответствующими входами группы входов блока 36 управления, подключенными к входам коммутатора 5, соединенным с шиной 25. Третьи входы мультиплексоров 40 подключены к выходу первого инвертора 41.1, входом соединенного с третьим входом группы входов блока 36 управления. Этот вход подключен также к первым входам входящих в блок 36 управления параллельно включенных элементов И 42. Вторые входы элементов И 42.1 и 42.3 соединены с вторым входом группы входов блока 36 управления, а вторые входы элементов И 42.2 и 42.4 подключены к первому входу группы входов блока 36 управления. Выходы первого и второго элементов И 42 (42.1 и 42.2) соединены соответственно с первым и вторым входами элемента ИЛИ 43.1, а выходы третьего и четвертого элементов И 42 (42.3 и 42.4) подключены соответственно к первому и второму входам элемента ИЛИ 43.2.

Выходы первого и второго элементов ИЛИ 43, а также первого, второго и третьего инверторов 41 соединены соответственно с первым, вторым, третьим, четвертым и пятым выходами блока 36 управления, причем входы второго и третьего инверторов 41 (41.2 и 41.3) подключены соответственно к первому и второму входам группы входов блока 36 управления, а выходы первого и второго мультиплексоров 40 соединены соответственно с выходами блока 36 управления, подключенными к группам выходов коммутатора 5. соединенных с шинами 11 и 12.

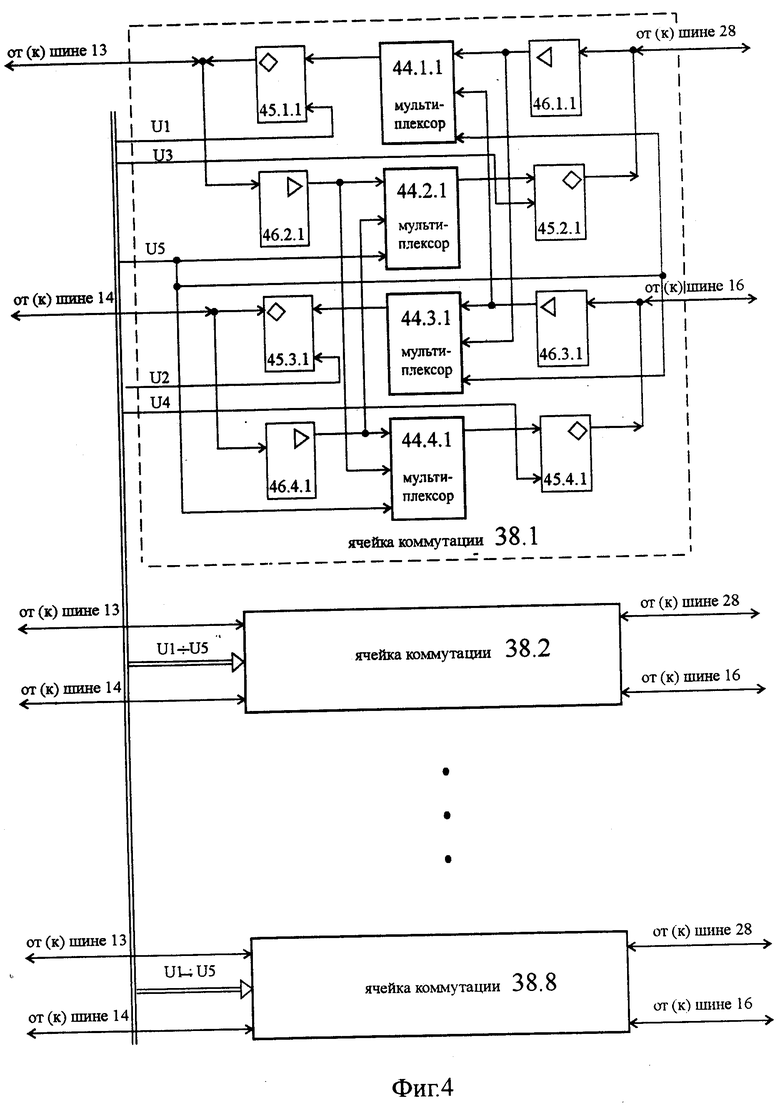

Каждая i (в приведенной схеме i=1,...,8) ячейка 38 коммутации (фиг. 4) содержит четыре мультиплексора 44 (44.1.i-44.4.i), четыре трехстатических буферных элемента 45 (45.1.i-45.4.i) и четыре буферных элемента 46 (46.1. i-46.4. i). Здесь (фиг. 4) схема ячейки 38.i коммутации показана для ячейки 38.1 коммутации (для i=1). Первый и третий мультиплексоры 44.1 и 44.3 своими первым и вторым адресными входами соединены с выходами первого и третьего буферных элементов (46.1 и 46.3), а второй и четвертый мультиплексоры (42.2 и 44.4) - с выходами второго и четвертого буферных элементов (46.2 и 46.4) соответственно. Третий управляющий вход мультиплексоров 44 подключен к входу управления ячейки 38 коммутации (на схеме U5).

Выходы первого, второго, третьего и четвертого мультиплексоров 44 соединены с первым входом соответствующего трехстатического буферного элемента (ТБЭ) 45, вторым входом подключенных соответственно первого ТБЭ (45.1) к первому входу группы входов, второго ТБЭ (45.2) к третьему входу группы входов, третьего ТБЭ (45.3) к второму входу группы входов, а четвертого ТБЭ (45.4) к четвертому входу группы входов ячейки 38 коммутации. Выходы ТБЭ 45 соединены с входами-выходами соответственно первого - первой группы, второго - четвертой группы, третьего - второй группы, четвертого - третьей группы входов-выходов ячейки 38 коммутации. Входы буферных элементов 46 подключены к входам-выходам соответственно первого (46.1) - четвертой группы, второго (46.2) - первой группы, третьего (46.3) - третьей группы и четвертого (46.4) - второй группы входов-выходов ячейки 38 коммутации. При этом элементы первой ячейки (38.1) коммутации соединены с первыми входами-выходами соответствующих групп входов-выходов, второй ячейки (38.2) коммутации подключены к вторым входам-выходам групп входов-выходов и т.д.

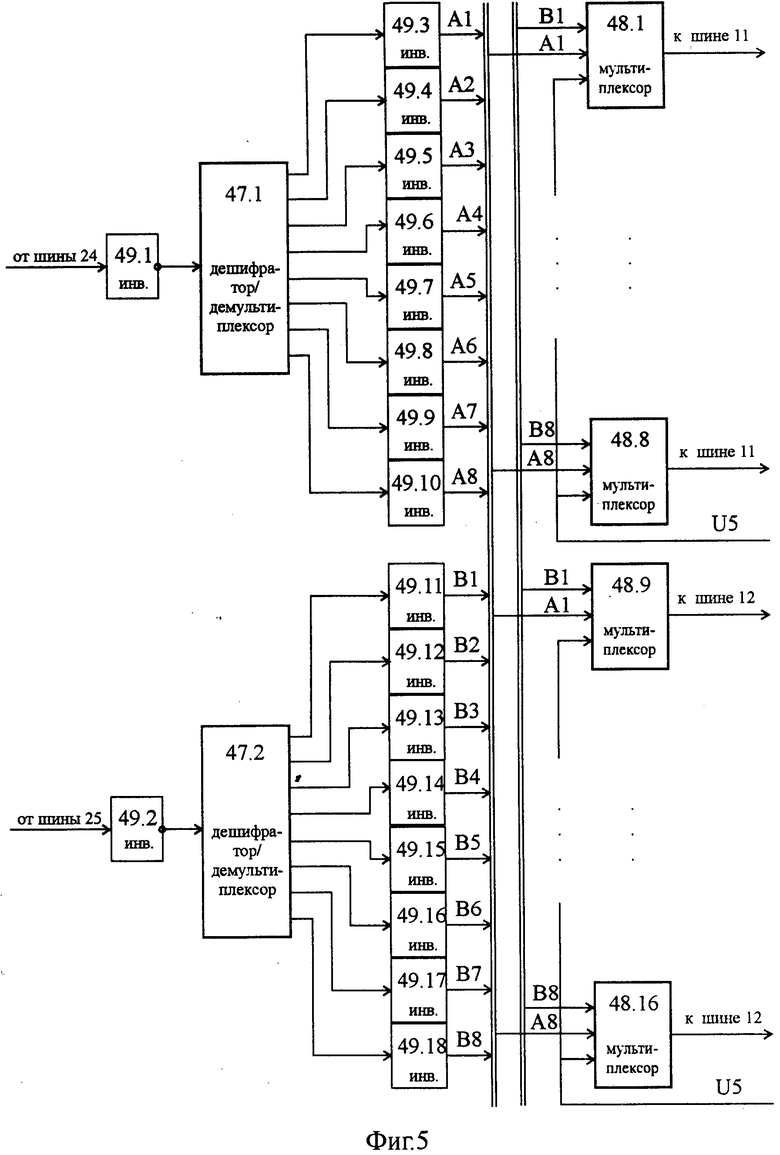

Блок 39 коммутации адреса (фиг. 5) содержит два дешифратора/демультиплексора 47 (47.1 и 47.2), шестнадцать мультиплексоров 48 (48.1-48.16) и восемнадцать инверторов 49 (49.1-49.18), при этом входы первого и второго инверторов (49.1 и 49.2) соединены с первой группой входов блока 39 коммутации адреса (шина 24), выходы первых восьми мультиплексоров (48.1-48.8) соединены с первой группой выходов (шина 11), а вторых восьми мультиплексоров (48.9-48.16) - со второй группой выходов блока 39 коммутации адреса (шина 12). Управляющие входы дешифраторов/демультиплексоров 47.1 и 47.2 подключены к выходам соответственно инверторов 49.1 и 49.2.

Выходы первого дешифратора/демультиплексора 47.1 соединены с входами соответственно с третьего по десятый инверторов (49.3-49.10), а выходы второго дешифратора/демультиплексора 47.2 подключены к входам соответственно с одиннадцатого по восемнадцатый инверторов (49.11-49.18).

Выходы третьего и одиннадцатого, четвертого и двенадцатого, пятого и тринадцатого, шестого и четырнадцатого, седьмого и пятнадцатого, восьмого и шестнадцатого, девятого и семнадцатого, десятого и восемнадцатого инверторов (49.3-49.18) соединены соответственно с первым и вторым входами соответственно с первого по шестнадцатый мультиплексоры (48.1-48.16), третьи управляющие входы которых подключены к управляющему входу блока 39 коммутации адреса.

Мультиплексоры 40 и 44, инверторы 41 и 49 элементы И 42, элементы ИЛИ 43, трехстатические элементы 45, буферные элементы 46 и дешифраторы/демультиплексоры 47 соответствуют своему функциональному назначению (Титце У. и др. Полупроводниковая схемотехника. - М.: Мир, 1982, с. 33, 326, 328, 366) и выполнены на программируемых БИС, изготовленных по технологии КМОП, серии XC 4010-6PQ160C (Каталог фирмы XILINX, The Programmble Logic Data Book, 1994, USA).

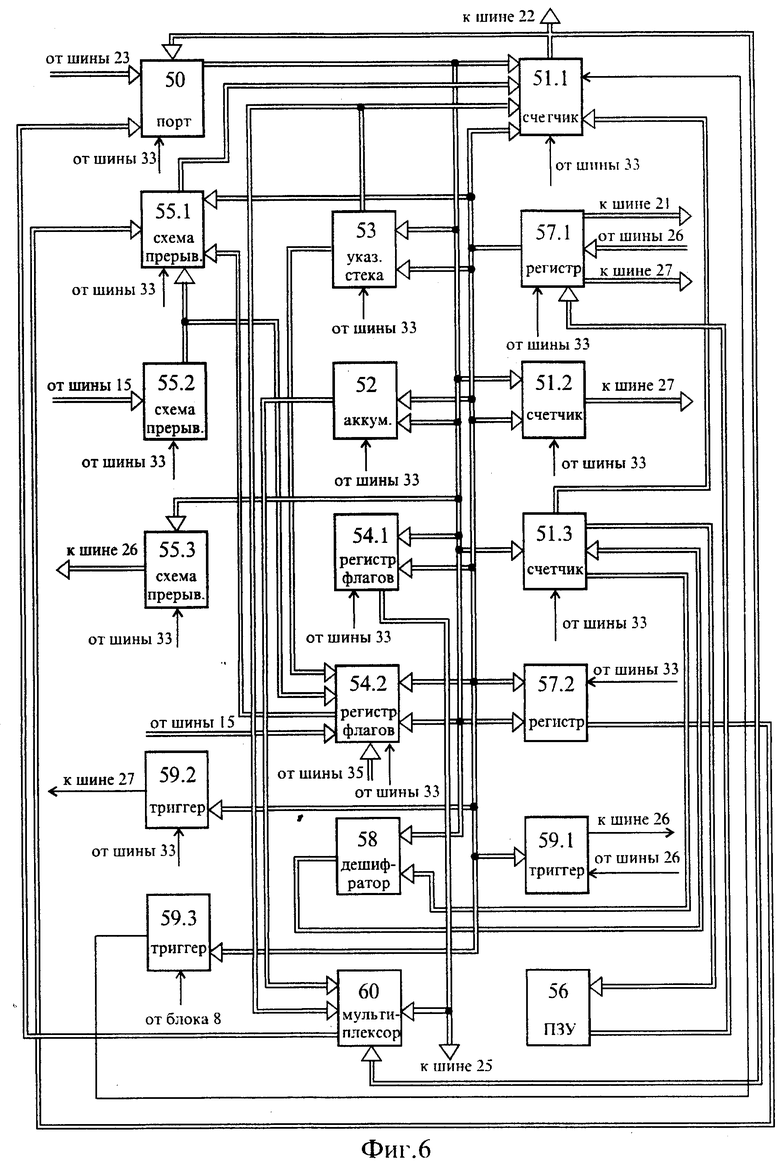

Блок 6 управления (фиг. 6) содержит порт 50 ввода-вывода, три счетчика 51 (51.1-51.3), аккумулятор 52, указатель 53 стека, два регистра 54 флагов (54.1-54.2), три схемы 55 прерывания (55.1-55.3), постоянное запоминающее устройство 56 (ПЗУ), два регистра 57 (57.1-57.2), дешифратор 58, три триггера 59 (59.1-59.3) и мультиплексор 60.

Порт 50 ввода-вывода первой группой входов подключен к группе входов блока 6 управления, соединенной с шиной 23, второй группой входов подключен к группе выходов мультиплексора 60, третьей группой входов соединен с группой выходов счетчика 51.1. подключенной также к первой группе входов мультиплексора 60 и к группе выходов блока 6 управления, соединенной с шиной 33, а группой выходов подключен к первым группам входов счетчиков 51, аккумулятора 52, указателя 53 стека, регистров 54 флагов, регистра 57.2, дешифратора 58 и к группе входов схемы 55.3 прерывания.

Счетчик 51.1 второй группой входов соединен с группой выходов схемы 55.1 прерывания, третьей группой входов подключен к первой группе выходов указателя 53 стека, соединенной также с второй группой входов мультиплексора 60, четвертой группой входов подключен к первой группе выходов счетчика 51.3, а пятой группой входов соединен с первой группой выходов регистра 57.1, подключенной также к вторым группам входов счетчика 51.2, аккумулятора 52, указателя 53 стека, регистров 54 флагов и регистра 57.2 и к первым группам входов схемы 55.1 прерывания и триггеров 59.

Первым входом счетчик 51.1 соединен с выходом триггера 59.3, а вторым входом подключен к второму входу группы входов блока 6 управления, соединенной с шиной 33.

Счетчик 51.3 второй группой входов подключен к группе выходов дешифратора 58, второй группой входов соединенного с первой группой выходов счетчика 51.3, второй группой выходов подключенного к группе входов ПЗУ 56, а входом соединенного с четвертым входом группы входов блока 6 управления, подключенной к шине 33.

Аккумулятор 52 группой выходов соединен с третьей группой входов мультиплексора 60, а входом подключен к Пятому входу группы входов блока 6 управления, соединенной с шиной 33.

Указатель 53 стека второй группой выходов подключен к третьей группе входов регистра 54.2 флагов, а входом соединен с шестым входом группы входов блока 6 управления, подключенной к шине 33.

Группа выходов регистра 54.1 флагов соединена с четвертой группой входов мультиплексора 60, а также с группой выходов блока 6 управления, подключенной к шине 25, а вход этого регистра соединен с седьмым входом группы входов блока 6 управления, подключенной к шине 33.

Регистр 54.2 группой выходов соединен с второй группой входов схемы 55.1 прерывания, четвертой и пятой группами входов подключен к группам входов блока 6 управления, соединенных соответственно с шинами 15 и 35, шестой группой входов подключен к группе выходов схемы 55.2 прерывания, а входом подключен к восьмому входу группы входов блока 6 управления, соединен с шиной 33.

Схема 55.1 прерывания четвертой группой входов подключена к группе выходов регистра 57,2, группа входов схемы 55.2 прерывания и группа выходов схемы 55.3 прерывания соединены соответственно с группой входов и группой входов-выходов блока управления, подключенных к шинам 15 и 26 соответственно.

Входы схем 55.1-55.3 прерывания соединены соответственно с 9, 10 и 11 входами группы входов блока 6 управления, подключенной к шине 33.

Группа выходов ПЗУ 56 соединена с первой группой входов регистра 57.1, второй группой входов и второй и третьей группами выходов подключенного соответственно к группе входов и группам выходов блока 6 управления, соединенных с шинами 26, 21 и 27 соответственно.

Входы регистров 57.1 и 57.2 подключены соответственно к 12 и 13 входам группы входов блока управления, соединенной с шиной 33.

Входы и выходы триггеров 59.1 и 59.2 подключены к входам и выходам соответственно групп входа и групп выхода блока 6 управления, соединенных с шинами 26 и 27 соответственно, а вход триггера 59.3 подключен к входу блока управления, соединенному с выходом вычислительного блока 8.

Порт 50 ввода-вывода, счетчики 51, аккумулятор 52, указатель 53 стека, регистры 54 флагов, схемы 55 прерывания, ПЗУ 56, регистры 57, дешифратор 58, триггеры 59 и мультиплексор 60 соответствуют своему функциональному назначению (Титце У. и др. Полупроводниковая схемотехника, с. 121, 326, 353, а также Справочник Микропроцессорные структуры. - М.: Радио и связь, 1990, с. 44, 184, 187, 433-435) и выполнены на программируемых БИС, изготовленных по технологии КМОП, серии XC 4010 - GPQ 160C (Каталог фирмы XILINX).

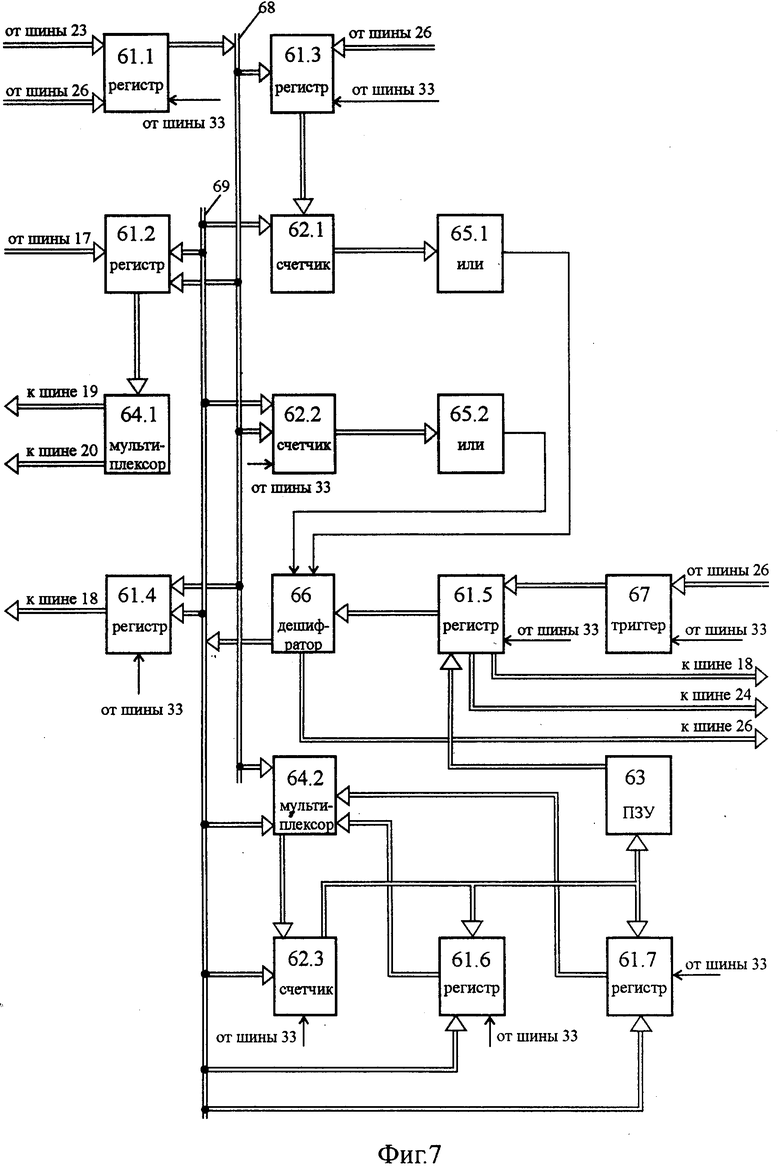

Контроллер 7 ввода-вывода (фиг. 7) содержит семь регистров 61 (61.1-61.7), три счетчика 62 (62.1-62.3), постоянное запоминающее устройство (ПЗУ) 63, два мультиплексора 64 (64.1-64.2), два элемента ИЛИ 65 (65.1-65.2), дешифратор 66 и триггер 67.

Регистр 61 первой группой управляющих входов подключен к группе входов контроллера 7 ввода-вывода, соединенной с шиной 23, второй группой управляющих входов подключен к группе входов-выходов контроллера 7 ввода-вывода, соединенной с шиной 26, а группой выходов подключен к шине 68, с которой первыми группами входов соединены регистры 61.2, 61.3 и 61.4, счетчик 62.2 и мультиплексор 64.2.

Регистр 61.2 второй группой входов подключен к группе входов контроллера 7 ввода-вывода, соединенной с шиной 17, а группой выходов подключен к группе входов мультиплексора 64.1, первой и второй группами выходов соединенного с группами выходов контроллера 7 ввода- вывода, подключенными к шинам 19 и 20 соответственно.

Регистр 61.3 второй группой входов соединен с группой входов контроллера 7 ввода-вывода, подключенного к шине 26, а группой выходов соединен с первой группой входов счетчика 62.1, выходами подключенного к соответствующим входам элемента ИЛИ 65.1, а второй группой входов соединенного с шиной 69, к которой первой группой выходов подключен дешифратор 66, а вторыми группами входов - регистры 61.2, 61.4, 61.6 и 61.7, счетчики 62.1, 62.2 и 62.3 и мультиплексор 64.2. Входы регистров 61.1, 61.3, 61.4, 61.5, 61.6, 61.7 и счетчиков 62.2, 62.3 соединены соответственно с 1 по 8 входами группы входов контроллера 7 ввода-вывода, подключенной к шине 33.

Регистры 61.4 и 61.5 группами выходов соединены с группой выходов контроллера 7 ввода-вывода, подключенной к шине 18, при этом регистр 61.5 второй группой выходов соединен с группой выходов контроллера 7 ввода-вывода, подключенной к шине 24.

Регистры 61.6 и 61.7 вторыми группами входов соединены с группой выходов счетчика 62.3, подключенной также к группе входов ПЗУ 63, группой выходов соединенного с первой группой входов регистра 61.5, второй группой входов подключенного к выходам триггера 67, группой входов соединенного с группой входов контроллера 7 ввода-вывода, подключенной к шине 26.

Группа выходов регистра 61.5 соединена с первой группой входов дешифратора 66, второй группой выходов подключенного к группе выходов контроллера ввода-вывода, соединенной с шиной 26.

Группы выходов регистров 61.6 и 61.7 подключены соответственно к третьей и четвертой группам входов мультиплексора 64.2, группой выходов соединенного с второй группой входов счетчика 62.3.

Счетчик 62.2 выходами подключен к соответствующим входам элемента ИЛИ 65.2, а счетчик 62.3 второй группой входов соединен с группой выходов мультиплексора 64.2.

Выходы элементов ИЛИ 65.1 и 65.2 соединены с соответствующими входами дешифратора 66.

Регистры 61, счетчики 62, ПЗУ 63, мультиплексоры 64, блоки ИЛИ 65, дешифратор 66 и триггер 67 соответствуют своему функциональному назначению (Титце У. и др. Полупроводниковая схемотехника, с. 121, 353, 370, 377, 403) и выполнены на программируемых БИС, 160С (Каталог фирмы XILINX).

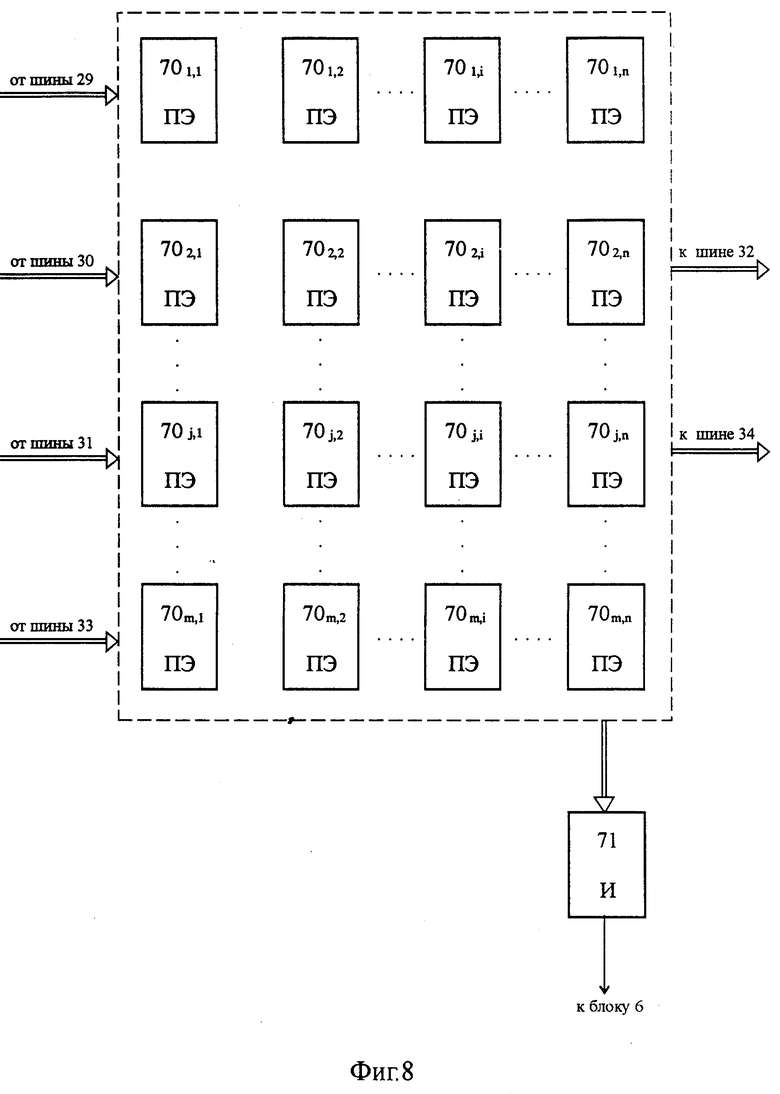

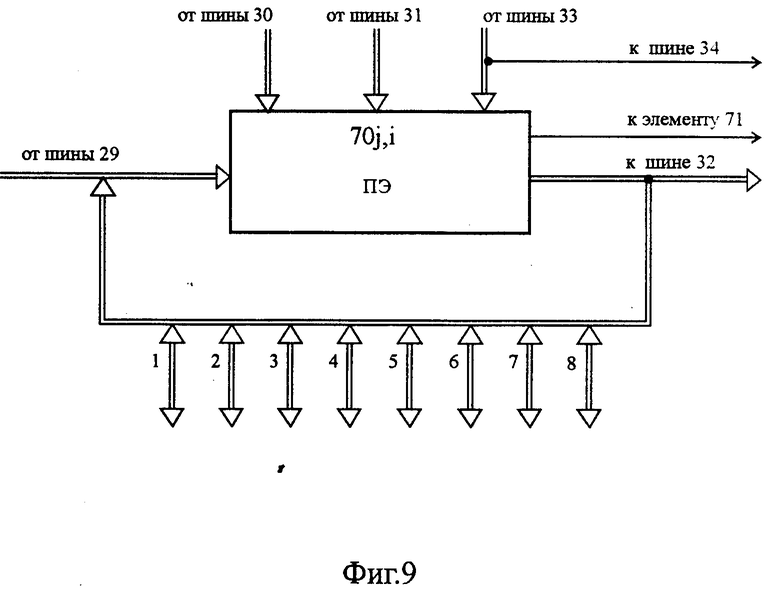

Вычислительный блок 8 (фиг. 8) содержит матрицу (n x m) процессорных элементов (ПЭ) 70, в которой группы информационных выходов каждого процессорного элемента 70j,i (i=1,..., n; j=1,..., m) соединены с соответствующими группами информационных входов каждого соседнего процессорного элемента 70j+1, i+1. Перечень этих соединений процессорных элементов 70 вычислительного блока 8 приведен в табл. 1.

При этом группы информационных, управляющих, адресных и тактовых входов каждого процессорного элемента 70 соответственно подключены к группам информационных, управляющих, адресных и тактовых входов вычислительного блока 8, соединенных соответственно с шинами 29, 30, 31 и 33, группы информационных выходов каждого процессорного элемента 70 подключены к группе информационных выходов вычислительного блока 8, соединенных с шиной 32, причем первый выход группы информационных выходов каждого процессорного элемента 70 подключен также к соответствующему входу элемента И 71, выход которого соединен с выходом вычислительного блока 8.

Когда количество процессорных элементов 70 (и соответственно их выходов) таково, что подсоединение всех этих выходов к одному элементу И невозможно, составляют комбинацию (пирамиду) элементов И (не показано), в которой количество элементов И первого уровня выбирают с учетом возможности подключения каждого выхода процессорного элемента 70 к входу элементами, а затем выходы элементов И этого уровня соединяют соответственно с входами элементов И следующего уровня и т. д. вплоть до сведения всех видов к одному элементу И. Каждая первая линия шины (не показана), подключенная к группе тактовых входов каждого процессорного элемента 70, соединена одновременно с соответствующим выходом группы выходов вычислительного блока 8, подключенных к шине 34.

Процессорный элемент 70 содержит пять мультиплексоров, четыре регистра, оперативное запоминающее и арифметико-логическое устройства. Схема выполнения такого процессорного элемента приведена, например, в патенте N 2089936 с приоритетом от 18.06.96 г. на изобретение "Процессорный элемент".

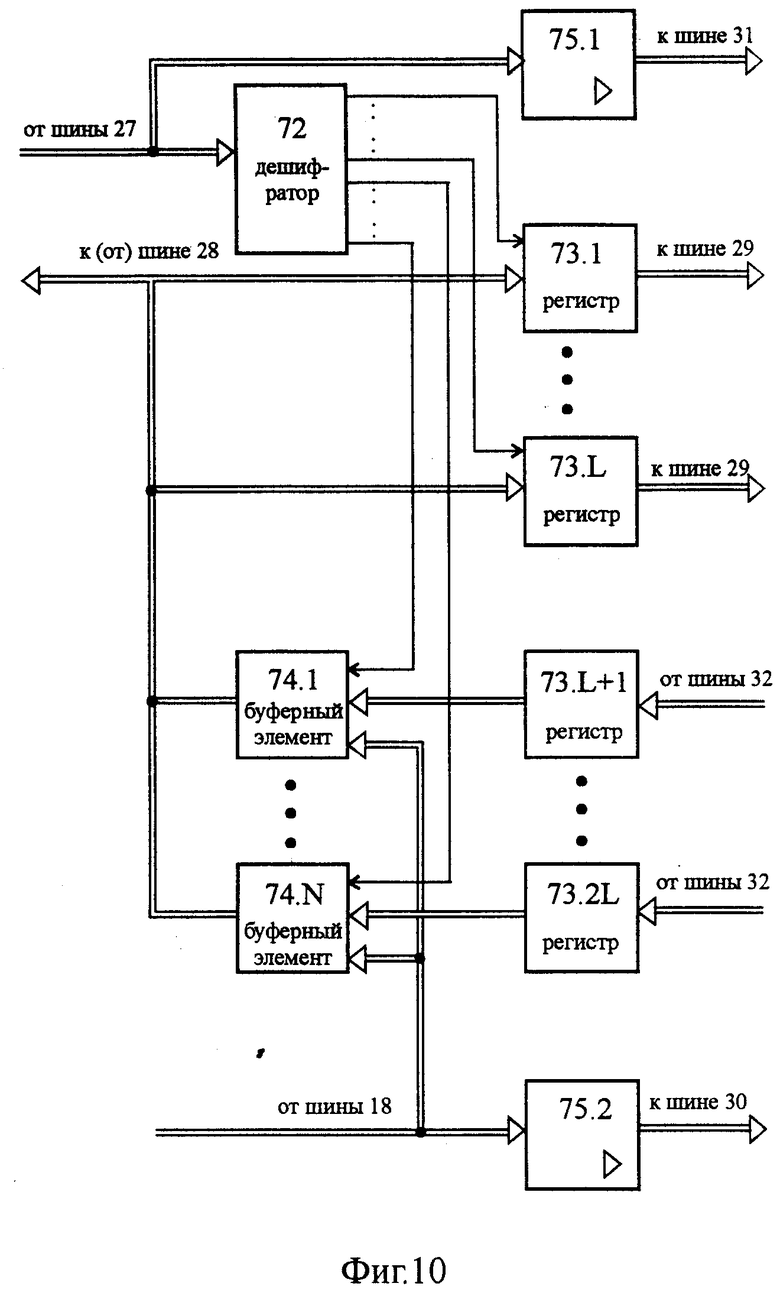

Буферный блок 9 (фиг. 10) содержит дешифратор 72, 2L регистров 73, где L равна отношению n/w, где n - число столбцов в матрице процессорных элементов (фиг. 8), а w - разрядность слов, передаваемых по шине 28. Внутренняя разрядность каждого из регистров 73.1-L группы также не более w - разрядов.

Группы входов дешифратора 72 и буферного элемента 75.1 подключены к группе входов буферного блока 9, соединенной с шиной 27.

Первые L выходов (1-L) дешифратора 72 подключены соответственно к входам регистров 73.1-73. L, выходы которых соединены с группой выходов буферного блока 9, подключенной к шине 29, а вторые L выходов (L+1-2L) дешифратора 72 соединены соответственно с первыми входами трехстатических буферных элементов 74.1-74. L (выполненных на микросхемах КР1533АП14), первые группы входов которых подключены соответственно к группам выходов регистров 73.L+1 - 73.2L, группами входов соединенных с группой входов буферного блока 9, подключенной к шине 32. Вторые группы входов трехстатических буферных элементов 74.1-74.L и группа входов буферного элемента 75.2 соединены с группой входов буферного блока 9, подключенной к шине 18, при этом группа входов буферного элемента 75.2 соединена с группой входов буферного блока 9, подключенной к шине 30.

Группы выходов трехстатических буферных элементов соединены с группой выходов буферного блока 9, подключенный к шине 28, при этом группа входов буферного блока 9, соединенная с шиной 28, подключена к группам входов регистров 73.1-73. L, группы выходов которых соединены с группой выходов буферного блока 9, подключенной к шине 29.

Группа входов дешифратора 72 и группа входов буферного элемента 75.1 соединены с группой входов буферного блока 9, подключенной к шине 27, причем группа выходов буферного элемента 75.1 соединена с группой входов буферного блока 9. подключенного к шине 31.

Дешифратор 72, регистры 73, трехстатические буферные элементы 74 и буферные элементы 75 соответствуют своему функциональному назначению (Титце У. и др. Полупроводниковая схемотехника, с. 319, 370, 403) и выполнены на программируемых БИС, изготовленных по технологии КМОП, серии XC4010-GPQ160C (Каталог фирмы XILINX).

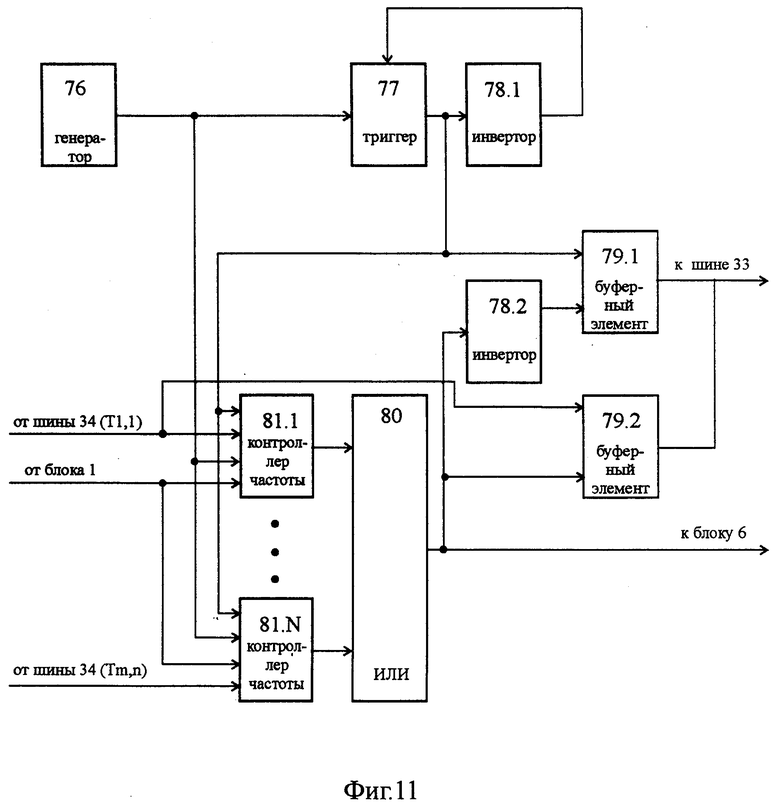

Блок 10 задания и контроля тактовой частоты (фиг. 11) содержит задающий генератор (осциллятор) 76, триггер 77, два инвертора 78, два трехстабильных буферных блока 79, элемент ИЛИ 80 и N-контроллеров 81 частоты (N=n x m и соответствует числу процессорных элементов 70 вычислительного блока 8).

Группа выходов блока 10 задания и контроля тактовой частоты, соединенная с шиной 33, подключена к выходам трехстабильных буферных блоков 79, группа входов блока 10 задания и контроля тактовой частоты, соединенная с шиной 34, подключена к первому входу буферного блока 79.2 и к первым входам контроллера 81 частоты, выход блока 10 задания и контроля тактовой частоты соединен с выходом элемента ИЛИ 80, подключенного также к входу инвертора 78.2 и к второму входу трехстабильного буферного блока 79.2, а вход блока 10 соединен с вторыми входами контроллера 81 частоты.

При этом выход задающего генератора 76 соединен с первым входом триггера 77 и третьими входами контроллеров 81 частоты, выход триггера 77 подключен к первому входу трехстабильного буферного блока 79.1, к четвертым входам контроллеров 8! частоты и через инвертор 78.1 на свой второй вход.

Выходы контроллеров 81 частоты соединены с входами элемента ИЛИ 80, выход инвертора 78.2 подключен к второму входу трехстабильного буферного блока 79.1.

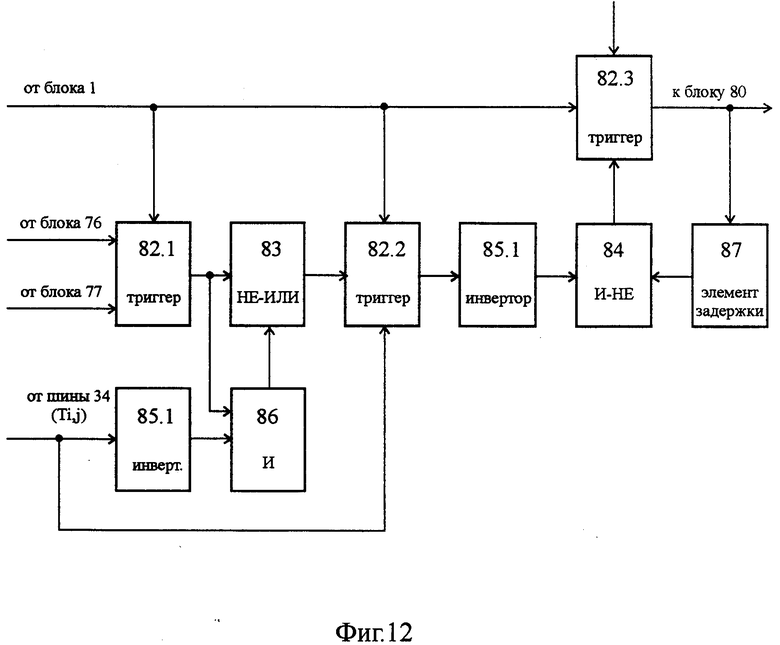

Контроллер 81 частоты (фиг. 12) содержит три триггера 82, элемент НЕ-ИЛИ 83, элемент И-НЕ 84, два инвертора 85. элемент И 86 и элемент 87 задержки.

Первый вход контроллера 81 частоты подключен к входу инвертора 85.1 и второму входу триггера 82.2, второй вход контроллера 81 частоты соединен с первыми входами триггеров 82 (82.1-82.3), третий и четвертый входы контроллера 81 частоты подключены соответственно к второму и третьему входам триггера 82.1, а выход контроллера 81 соединен с выходом триггера 82.3 и входом элемента 87 задержки.

Выход триггера 82.1 соединен с первыми входами элемента НЕ-ИЛИ 83 и элемента И 86, выход которого подключен к второму входу элемента НЕ-ИЛИ 83, выходом соединенного с третьим входом триггера 82.2. Выход триггера 82.2 подключен к первому входу инвертора 85.2, выходом соединенного с первым входом элемента И-НЕ 84, второй вход которого подключен к выходу элемента 87 задержки, а выход соединен с вторым входом триггера 82.3.

При этом третий вход триггера 82.3 подключен к источнику питания +5В (не показан), а выход инвертора 85.2 соединен с вторым входом элемента И 86.

Генератор (осциллятор) 76, триггеры 77 и 82, инверторы 78 и 85, трехстабильные буферные блоки 79, элемент ИЛИ 80, элемент НЕ-ИЛИ 83, элемент И-НЕ 84 и элемент 87 задержки соответствуют своему функциональному назначению (Титце У. и др. Полупроводниковая схемотехника, с. 28, 112, 113, 121, 298) и выполнены на программных БИС, изготовленных по технологии КМОП, серии XC4010-GPQ160C (Каталог фирмы XILINX).

Работу системы НБМПЭ осуществляют на базе команд, разделенных на группу команд блока 6 управления, включающую сорок шесть команд, и группу команд вычислительного блока 8, содержащую сорок одну команду. При этом группа команд блока 6 управления обеспечивает установку параметров вычислительного блока 8, пересылку данных внутри системы НБМПЭ и передачу управления, например, контроллеру 7 ввода-вывода, а группа команд вычислительного блока 8 реализует ввод-вывод данных, их пересылку, обмен и сдвиг внутри вычислительного блока 8, а также арифметические и логические операции.

Следует указать также, что в системе НБМПЭ используют 48-разрядные команды, при этом для проведения арифметических и логических операций выбрано трехадресное обращение к памяти.

В приведенной версии системы команд реализована только беззнаковая целочисленная арифметика.

Обобщенный формат команд имеет вид: КМОП, модификаторы,  .

.

Код операции (КОП) содержится в 47-35 разрядах команды. Модификаторы команды (M1, M2) содержатся в 37-35. 34-31 разрядах. M1 (разряды 37-35): коды (0-6)h представляют команды блока 6 управления, код 7h - команды матрицы вычислительного блока 8. M2 (разряды 34-31): Код Eh - используется только для команд матрицы в тех случаях, когда команда не содержит разрядности (R).

Перед началом работы системы НБМПЭ в блок 2 памяти загружают подпрограммы обработки прерываний, рабочие программы, а также управляющие переменные (эти данные не приведены, поскольку их описание связано с решением конкретных задач, рассмотрение которых здесь не целесообразно).

При этом рабочую область блока 2 памяти обычно делят на четыре поля:

поле подпрограмм прерываний, на котором записывают управляющие подпрограммы прерываний от базового компьютера 1 и программно-доступных блоков системы НБМПЭ;

поле управляющих переменных, где хранят значения управляющих переменных (например, номер текущей итерации программного цикла);

поле выводимых данных, куда в процессе работы записывают необходимые для просмотра и анализа данные (например, при отладке рабочих программ - состояние внутренних регистров блока 6 управления);

поле рабочих программ.

В общем случае проведение вычислительного процесса состоит в последовательном выполнении следующих основных этапов:

загрузка исполняемой программы через базовый компьютер 1 в блок 2 памяти;

ввод исходных данных через базовый компьютер 1 и коммутатор 5 в блоки 3 и 4 памяти;

загрузка программно-доступных подблоков блока 6 управления соответствующими программами;

запуск с последующим обменом данными между базовым компьютером 1 и блоками 3 и 4 памяти и вычислительным блоком 8;

получение результатов счета.

Ввод исходных данных в блоки 3 и 4 памяти производят с помощью блока 6 управления, который вырабатывает соответствующие сигналы для коммутатора 5, и контроллера 7 ввода-вывода. При этом коммутатор 5 подключают к шине 16 данных базового компьютера 1 одной из шин (13 или 14) и соответственно одного из блоков (3 или 4) памяти, после чего производят обмен данными между базовым компьютером 1 и соответствующим блоком памяти. Наличие двух блоков 3 и 4 памяти данных позволяет организовать непрерывный поток данных между базовым компьютером 1 и матрицей процессорных элементов. Так, например, после загрузки данными со стороны базового компьютера 1 блока памяти 3 последний поступает в распоряжение блока матриц процессорных элементов и из него получают данные под управлением команд контроллера 7 ввода-вывода. В то же время базовый компьютер 1 может продолжить закачку данных в блок 4 памяти данных. Аналогичным образом может быть организована обратная передача данных из НБМПЭ в базовый компьютер 1.

После загрузки в блок 2 памяти рабочей программы и введения в блоки 3 и 4 памяти исходных данных производят запуск блока 6 управления путем установки стартового адреса начала программы в регистре (не показан) счетчика 51.1 блока 6 управления и последующего обращения через шину 22 к блоку 2 памяти по фиксированному адресу к первой команде исполняемой программы. Эту команду принимают (через шину 23) в блоке 6 управления и с его помощью реализуют.

В общем случае через блок 6 управления производят загрузку вычислительного блока 8 исходными данными и реализацию в нем программы обработки, выдачу результатов и запись их в блоках 3 и 4 памяти, а также завершение работы программы или оценку необходимости получения дополнительных данных из базового компьютера 1 и принимают решение о необходимости передачи полученных результатов в базовый компьютер 1.

При этом получение ("подкачка") дополнительных данных из базового компьютера 1 или прием результатов вычислений блока 8 может быть осуществлено непосредственно на фоне работы вычислительного блока 8. В этом случае блок 6 управления через флаги триггера 59 программно-доступных регистров 54 производит "оповещение" базового компьютера 1 о необходимости реализации соответствующего обмена информацией.

Информационный обмен между блоками системы НБМПЭ и базовым компьютером 1 производят асинхронно посредством обоюдных прерываний с помощью восьмиразрядного регистра (не показан) схемы 55.2 прерываний. Этот регистр непосредственно доступен (может взаимодействовать) базовому компьютеру 1 как для записи, так и для считывания данных (протокол обмена реализуют через шины 15-17).

В этом случае в схему 55.2 прерываний заносят код прерывания от базового компьютера 1 к блокам системы НБМПЭ и в блоке 6 управления устанавливают флаг внешнего прерывания. Этот флаг снимают с помощью команды RSTINT. После выполнения текущей команды блок 6 управления исполняет аппаратную команду JUMPINT перехода к прерыванию.

Во время выполнения данной команды в блоке 6 управления по подпрограмме производят следующие действия:

1. В регистре (не показан) указателя 53 стека увеличивают уровень на 1.

2. По указанному в указателе 53 стека адресу в ячейку памяти блока 2 памяти записывают информацию из регистра 57.1, в который в конце действия каждой команды автоматически сбрасывают адрес следующей.

3. Устанавливают флаги (триггеры 59.1-59.2) запрета прерываний.

4. Исполняют команду, записанную в ячейку памяти блока 2 памяти с адресом APR, где APR - содержимое ячейки памяти блока 2 памяти с адресом, младший байт которого хранят в вышеупомянутом регистре схемы 55.2 прерываний, а старший байт равен 00h.

Выход из программы прерывания осуществляют посредством команды RETINT, во время исполнения которой выполняют следующие действия:

1. Снимают флаги (через триггеры 59.1-59.2) запрета прерывания.

2. Из ячейки памяти блока 2 памяти по адресу из вышеуказанного регистра указателя 53 стека извлекают значение адреса возврата; после чего в этом регистре уменьшают уровень на 1.

3. Используют команду, записанную в ячейке памяти блока 2 памяти с адресом AST, где AST - содержимое ячейки памяти блока 2 памяти с адресом, младший байт которого хранят в указанном выше регистре указателя 53 стека, старший байт равен 00h.

Прерывания со стороны блоков системы НБМПЭ могут быть вызваны в следующих случаях:

1. Прерывание по флагу через триггер 59.3 ошибки синхронизации в одном из процессорных элементов 70 вычислительного блока 8 (код источника прерывания - 03h, имя IERRT).

2. Прерывание по флагу регистра 54.2 флагов переполнения стека указателя 53 стека (код источника прерывания - 04h, имя ISTACK).

3. Прерывание по флагу (через триггер 59.2) ошибки кода операции (код источника прерывания - 05h, имя INCO).

4. Прерывание по флагу (через триггер 59.1) шагового режима (код источника прерывания - 06h, имя ISTEP).

При обратном прерывании (блоков системы НБМПЭ со стороны базового компьютера 1) имя источника прерывания - INT. а коды этого источника прерывания обозначают - (2F,...,7F)h.

Приоритеты прерываний устанавливают командой MOV Xh PRP, при этом принята следующая очередность: первым отрабатываю: прерывание INT, затем прерывание IERRT, затем ISTACK, а последним ISTER.

Просмотр состояния регистров блока 6 управления осуществляют путем записи их содержимого в блоке 2 памяти.

После записи (загрузки) в блоки 2-4 памяти исходной информации начинают выполнение задачи посредством проведения последовательной выборки блоком 6 управления операторов из блока 2 памяти и обмен данными между вычислительным блоком 8 и блоками 3 и 4 памяти.

При этом с помощью блока 6 управления формируют адреса для ОЗУ процессорных элементов 70 вычислительного блока 8, за исключением микрокоманд загрузки, формируют адреса следующей команды, производят селекцию команд обмена и формируют сигналы разрешения на прием контроллером 7 ввода-вывода.

Из блока 2 памяти через шину 23 передают команды на блок 6 управления, при этом 48-разрядную команду передают в три приема 16-разрядными словами, которые последовательно через порт 50 загружают в регистры (не показаны) счетчиков 51 (51.1-51.3). В блоке 6 управления эти команды разворачивают в последовательность 12-разряднмх микроинструкций и 7-разрядных адресов для вычислительного блока 8. При приеме команды обмена данными с вычислительным блоком 8 в блоке 6 управления производят опознание этой команды и формируют сигнал разрешения контроллеру 7 ввода-вывода принять и исполнить текущую команду. При этом в блоке 6 управления выставляют флаг F0, закрывают триггер 59.1 как признак занятости контроллера 7 ввода-вывода. После окончания выполнения контроллером 7 ввода-вывода выполнения команды обмена снимают флаг F0 (открывают триггер 59.1) и таким образом сообщают блоку 6 управления о готовности контроллера 7 ввода-вывода выполнить следующую команду обмена. Если в контроллере 7 ввода-вывода не выполнена предыдущая команда, то до снятия флага F0 блок 6 управления выполняет микрокоманду ожидания. Когда контроллер 7 ввода-вывода снимает флаг F0, блок 6 управления возвращают к микрокоманде, на которой было прервано исполнение команды обмена. Такая организация позволяет блоку 6 управления выполнить команды обработки данных, не ожидая конца загрузки матрицы процессорных элементов 70 вычислительного блока 8.

Контроллер 7 ввода-вывода, приняв команду обмена данными между вычислительным блоком 8 и одним из блоков 3 или 4 памяти, вырабатывает управляющие сигналы и через шину 18 подает их на буферный блок 9, а через шины 19, 20 и 24 в блоки 3 и 4 памяти и на коммутатор 5 соответственно. Буферный блок 9 коммутирует двунаправленную шину 28 с шиной 29 (при записи данных в вычислительный блок 8) или с шиной 32 (при чтении данных из вычислительного блока 8), через шины 30 и 31 вычислительного блока 8 передают соответствующие сигналы управления.

В вычислительном блоке 8 реализована возможность независимой работы при загрузке-выгрузке и обработке данных. Это существенно сокращает время обработки "окна" данных, загруженного в вычислительный блок 8, так как команды обмена имеют большую длительность. Оптимальным чередованием команд обмена с другими командами обеспечивают длительность обработки "окна" данных, определяемую только временем ввода-вывода. При одновременном выполнении команды обмена контроллером 7 ввода-вывода и команды обработки блоком 6 управления возможно их одновременное обращение к внутреннему ОЗУ процессорных элементов 70 вычислительного блока 8 в одном такте.

В этом случае приоритет принадлежит контроллеру 7 ввода-вывода, а блок 6 управления задерживает исполнение своей микрокоманды на один такт. Такая приоритетность связана с тем, что в процессе выполнения команд обмена обращаемость контроллера 7 ввода-вывода к вычислительному блоку 8 обычно гораздо реже, чем соответствующая обращаемость блока 6 управления. При этом длительность команд обмена обычно сравнима или больше длительности обработки данных.

При загрузке вычислительного блока 8 информацию через буферный блок 9 записывают в первую строку матрицы процессорных элементов 70 с одновременным сдвигом информации всех строк матрицы в вертикальном направлении (NS или SN). Таким образом по каждой отдельной строке матрицы производят последовательный сдвиг массива данных.

Одновременно с загрузкой-выгрузкой возможно выполнение арифметико-логических операций над данными, уже находящимися в памяти и регистрах процессорных элементов 70.

Число повторения тактов сдвига при загрузке зависит от количества строк матрицы процессорных элементов 70.

Выгрузку массива производят в обратном порядке.

Блок 10 задания и контроля тактовой частоты в процессе работы всего устройства осуществляет контроль правильности функционирования вычислительного блока 8 на уровне тактовой частоты. Данный контроль необходим в связи с тем, что блок 8 представляет из себя однородную распределенную вычислительную среду, где особенно остро стоит вопрос синхронизации заботы всех ее компонентов. Блок 10 по описанной выше схеме (фиг. 11 и 12) осуществляет постоянное сравнение тактовой частоты, выдаваемой в блок 8 по шине 33, с тактовой частотой, поступающей обратно по шине 34, а в случае расхождения данных частот вырабатывает сигнал, который по шине 35 поступает в блок 6 управления. В блоке 6 управления по данному сигналу устанавливают флаг в регистре 54.2, по которому базовый компьютер 1 определяет, что в вычислительном блоке 8 произошел аппаратный сбой, требующий вмешательства специалиста по обслуживанию комплекса, и базовый компьютер 1 подает на блоки системы НБМПЭ сигнал остановки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОРНЫЙ ЭЛЕМЕНТ | 1996 |

|

RU2089936C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для программного управления объектом | 1988 |

|

SU1605211A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Многопроцессорная вычислительная система | 1987 |

|

SU1792540A3 |

Изобретение может быть использовано при построении вычислительных средств, требующих высокопроизводительной обработки информации, например, для цифровой обработки изображений. Технический результат направлен на обеспечение возможности параллельной обработки разнородной и однородной информации, причем арифметико-логическую обработку и процессы обмена и передачи информации проводят по ортогональным направлениям с обменом между потоками информации ортогональных направлений без проведения промежуточных операций. Вычислительная система на базе матрицы процессорных элементов содержит базовый компьютер, три блока памяти, контроллер ввода-вывода, коммутатор, блок управления, блок задания и контроля тактовой частоты, буферный блок и вычислительный блок, выполненный в виде матрицы процессорных элементов. 12 ил., 6 табл.

Вычислительная система на базе матрицы процессорных элементов, содержащая базовый компьютер, блоки памяти, контроллер ввода-вывода, вычислительный блок и коммутатор, первые и вторые группы управляющих входов которого соединены с первыми группами управляющих входов соответственно первого и второго блоков памяти, а первые и вторые группы информационных входов-выходов коммутатора подключены к группам информационных входов-выходов соответственно первого и второго блоков памяти, отличающаяся тем, что в нее введены блок управления, блок задания и контроля тактовой частоты и буферный блок, причем группа управляющих входов-выходов базового компьютера соединена с первыми группами управляющих входов-выходов соответственно блока управления и третьего блока памяти, группа информационных входов-выходов базового компьютера подключена к группе информационных входов-выходов третьего блока памяти и третьей группе информационных входов-выходов коммутатора, а группа адресных выходов базового компьютера соединена с первыми группами адресных входов соответственно третьего блока памяти и контроллера ввода-вывода, первые, вторые и третьи группы адресных выходов которого подключены к группам адресных входов соответственно буферного блока и первого и второго блоков памяти, первая группа управляющих выходов и группа адресных выходов блока управления подключены к вторым группам соответственно адресных и управляющих входов третьего блока памяти, группа информационных выходов которого соединена с группами информационных входов блока управления и контроллера ввода-вывода, группа управляющих выходов которого подключена к первой группе управляющих входов коммутатора, вторая группа управляющих входов которого соединена с второй группой управляющих выходов блока управления, причем группа управляющих входов-выходов блока управления подключена к группе управляющих входов-выходов контроллера ввода-вывода, а третья группа управляющих выходов блока управления соединена с группой управляющих входов буферного блока, группа информационных входов-выходов которого соединена с четвертой группой информационных входов-выходов коммутатора, при этом группы информационных, адресных и управляющих выходов буферного блока подключены соответственно к группам информационных, адресных и управляющих входов вычислительного блока, первая группа информационных выходов которого соединена с группой информационных входов буферного блока, первая группа выходов блока задания и контроля тактовой частоты соединена с группами тактовых входов контроллера ввода-вывода, блока управления и вычислительного блока, вторая группа информационных выходов которого подключена к группе входов блока задания и контроля тактовой частоты, второй группой выходов соединенного с группой управляющих входов блока управления, информационным входом подключенного к соответствующему выходу вычислительного блока, причем базовый компьютер выходом соединен с управляющим входом блока задания и контроля тактовой частоты, а вычислительный блок выполнен в виде матрицы процессорных элементов.

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЦИФРОВОГО СИГНАЛА | 1991 |

|

RU2033637C1 |

| ПРОЦЕССОРНЫЙ ЭЛЕМЕНТ | 1996 |

|

RU2089936C1 |

| RU 94010060 F1, 27.02.96 | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| US 5642499 A1, 24.06.97 | |||

| US 5574939 A1, 12.11.96 | |||

Авторы

Даты

1998-08-10—Публикация

1998-01-29—Подача