Изобретение относится к радиолокации.

Известна импульсно-доплеровская радиолокационная станция (ИД РЛС), содержащая последовательно соединенные приемопередающую антенну, антенный переключатель, первый смеситель, предварительный усилитель промежуточной частоты и блок селекции, состоящий из N каналов селекции, где N количество элементов разрешения РЛС по дальности, каждый из которых состоит из последовательно соединенных селектора дальности, блока частотной селекции и блока цифровой обработки, выход которого является выходом из N выходов блока селекции, соединенных с соответствующими N входами первой группы входов индикатора, а выходы всех N селекторов дальности объединены и соединены с входом блока селекции, а также усилитель мощности, второй смеситель, генератор высокой частоты, кварцевый гетеродин, модулятор и синхронизатор, причем первый выход синхронизатора через модулятор соединен с первым входом усилителя мощности, второй вход которого соединен с выходом генератора высокой частоты, а выход с вторым входом антенного переключателя, выход кварцевого гетеродина соединен с первым входом второго смесителя, второй вход которого соединен с выходом генератора высокой частоты, а выход с вторым входом первого смесителя.

Недостатками данной ИД РЛС являются ее узкие функциональные возможности из-за отсутствия возможности распознавания боевого порядка групповой воздушной цели (БП ГВЦ) и определения ее ракурса относительно РЛС.

Цель изобретения расширение функциональных возможностей за счет распознавания боевого порядка групповой воздушной цели и определения ее ракурса относительно РЛС.

Это достигается тем, что в ИД РЛС, содержащую последовательно соединенные приемопередающую антенну, антенный переключатель, первый смеситель, предварительный усилитель промежуточной частоты и блок селекции, состоящий из N каналов селекции, где N количество элементов разрешения РЛС по дальности, каждый из N каналов селекции состоит из последовательно соединенных селектора дальности, блока частотной селекции и блока цифровой обработки, выход которого является выходом из N выходов блока селекции, соединенных с соответствующими N входами первой группы входов индикатора, первые входы всех N селекторов дальности объединены и являются первым входом блока селекции, а также усилитель мощности, второй смеситель, генератор высокой частоты, кварцевый гетеродин, модулятор и синхронизатор, причем первый выход синхронизатора через модулятор соединен с первым входом усилителя мощности, второй вход которого соединен с выходом генератора высокой частоты, а выход с вторым входом антенного переключателя, второй выход синхронизатора соединен с вторыми входами всех N селекторов дальности и является вторым входом блока селекции, выход кварцевого гетеродина соединен с первым входом второго смесителя, второй вход которого соединен с выходом генератора высокой частоты, а выход с вторым входом первого смесителя, вторые входы всех N селекторов дальности объединены и являются вторым входом блока селекции, дополнительно введены блок привязки координат, блок формирования эталонов, блок вычисления вероятностей и решающий блок, причем первые группы входов блока привязки координат и блока вычисления вероятностей объединены и каждый вход этих групп входов соединен с соответствующим выходом блока селекции, второй вход блока привязки координат соединен с третьим выходом синхронизатора, первая группа выходов с второй группой входов блока вычисления вероятностей, а второй, третий и четвертый выходы соответственно с третьим, четвертым и пятым входами блока формирования эталонов, первый и второй входы которого соединены соответственно с вторым и третьим выходами антенны, а L ˙ M спаренных групп выходов c L ˙ M спаренными группами входов блока вычисления вероятностей, где L количество фиксированных ракурсов цели с общей их суммой 360о, а М количество эталонов возможных боевых порядков воздушной цели, третий вход блока вычисления вероятностей соединен с четвертым выходом синхронизатора, а группа его выходов с первой группой входов решающего блока, второй вход которого соединен с четвертым выходом синхронизатора, группа выходов решающего блока соединена с второй группой входов индикатора.

Кроме того, блок привязки координат содержит первый генератор тактовых импульсов, N первых элементов И и N первых триггеров, первый элемент ИЛИ, первый и второй элементы НЕ, второй, третий, четвертый, пятый и шестой элементы И, первый запоминающий блок, первый и второй дешифраторы, первый счетчик, первый, второй и третий умножители, причем первые входы N первых элементов И соединены и являются первой группой входов блока привязки координат, выходы N первых элементов И соединены с информационными входами соответствующих N первых триггеров, выходы которых соединены с соответствующими входами первого и второго дешифраторов и первого элемента ИЛИ, выход которого через последовательно соединенные первый элемент НЕ, второй элемент И, первый счетчик, третий элемент И и первый умножитель соединен с вторым выходом блока привязки координат, второй вход третьего элемента И соединен с выходом первого элемента ИЛИ, выход первого элемента НЕ соединен с объединенными вторыми входами N первых элементов И, второй вход второго элемента И соединен с выходом первого генератора тактовых импульсов, вход которого является вторым входом блока привязки координат, первые входы четвертого, пятого и шестого элементов И соединены соответственно с первым, вторым и третьим выходами первого запоминающего блока, вторые входы четвертого, пятого и шестого элементов И объединены и через второй элемент НЕ соединены с выходом второго элемента И, а их выходы с вторыми входами соответственно первого, второго и третьего умножителей, первый вход второго умножителя соединен с выходом первого умножителя, а выход является третьим выходом блока привязки координат, первый вход третьего умножителя соединен с выходом второго дешифратора, а выход является четвертым выходом блока привязки координат, группа выходов второго дешифратора является первой группой выходов блока привязки координат, входы обнуления первого счетчика и N первых триггеров объединены и соединены со вторым входом блока привязки координат.

Кроме того, блок формирования эталонов содержит L ˙ M вычислителей эталонов, первые, вторые, третьи, четвертые и пятые входы которых одноименно объединены между собой соответственно и являются первым, вторым, третьим, четвертым и пятым входами блока формирования эталонов, пара групп выходов каждого из L ˙ M вычислителей эталонов является соответствующей спаренной группой из L ˙ M спаренных групп выходов блока формирования эталонов.

Кроме того, блок вычисления вероятностей содержит L ˙ M вычислителей вероятности и первый генератор тактовых импульсов, причем спаренная группа входов каждого вычислителя вероятности соединена с соответствующей спаренной группой входов блока вычисления вероятностей, вторые группы входов всех вычислителей вероятности объединены и являются первой группой входов блока вычисления вероятностей, вторая группа входов которого соединена с третьими группами входов всех вычислителей вероятности, четвертые входы которых объединены и соединены с выходом первого генератора тактовых импульсов, вход которого является третьим входом блока вычисления вероятностей и соединен также с объединенными пятыми входами вычислителей вероятности, выход каждого вычислителя вероятности является соответствующим выходом группы из L ˙ M выходов блока вычисления вероятностей.

Кроме того, каждый вычислитель вероятности содержит блок управления и вычислитель, причем спаренная группа входов блока управления соединена с соответствующей спаренной группой входов вычислителя вероятности, второй и третий входы соответственно с четвертым и пятым входами вычислителя вероятности, а первый, второй и третий выходы соответственно с первым, вторым и третьим входами вычислителя, четвертая группа входов которого соединена с третьей группой входов вычислителя вероятности, пятая группа входов с второй группой входов вычислителя вероятности, а выход является выходом вычислителя вероятности.

Кроме того, вычислитель содержит блок первых линий задержки, блок первых элементов совпадения, блок памяти, второй, третий, четвертый и пятый элементы совпадения, первый и второй запоминающие блоки, первый и второй элементы НЕ, первый и второй вычитающие блоки, первый элемент ИЛИ, первый умножитель и вторую линию задержки, причем группа входов блока первых линий задержки соединена с пятой группой входов вычислителя, а группа выходов с первой группой входов блока первых элементов совпадения, вторая группа входов которого соединена с четвертой группой входов вычислителя, а группа выходов с первой группой входов блока памяти, второй и третий входы которого соединены соответственно с первым и вторым входами вычислителя, а выход с первыми входами второго и пятого элементов совпадения непосредственно, а третьего и четвертого элементов совпадения через второй элемент НЕ, третий вход вычислителя соединен с вторыми входами второго и третьего элементов совпадения непосредственно, а четвертого и пятого элементов совпадения через первый элемент НЕ, выход первого запоминающего блока соединен с третьим входом второго элемента совпадения и через первый вычитающий блок с третьим входом третьего элемента совпадения, выход второго запоминающего блока соединен с третьим входом пятого элемента совпадения и через второй вычитающий блок с третьим входом четвертого элемента совпадения, выходы второго, третьего, четвертого и пятого элементов совпадения соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым входом первого умножителя, второй вход которого соединен с выходом второй линии задержки, а выход с входом второй линии задержки и является выходом вычислителя.

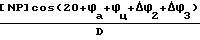

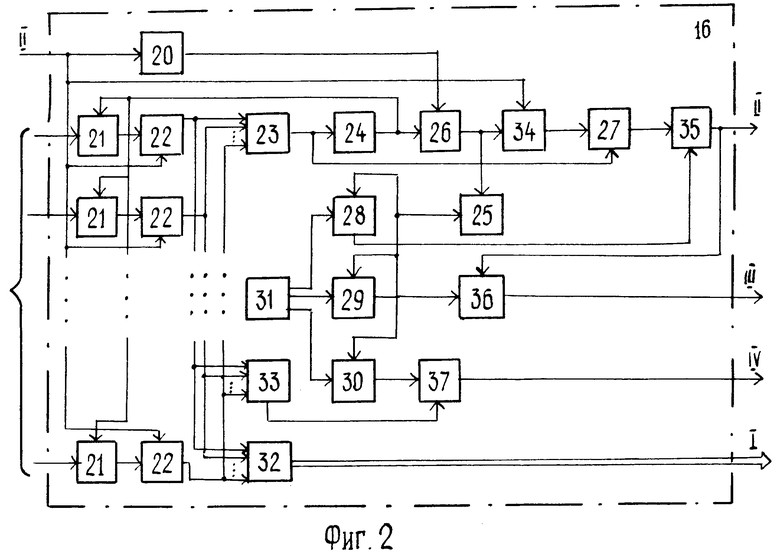

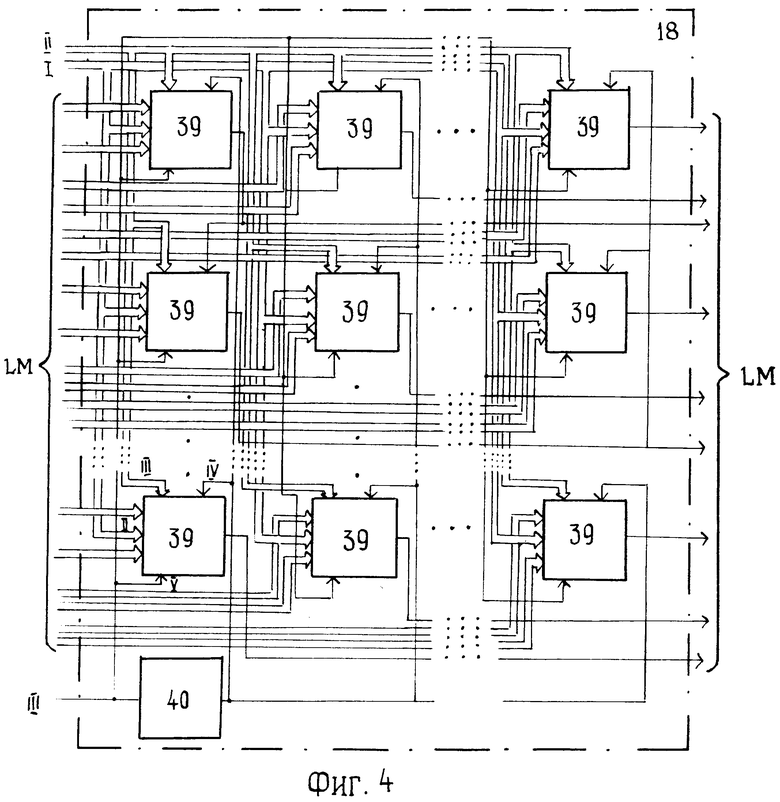

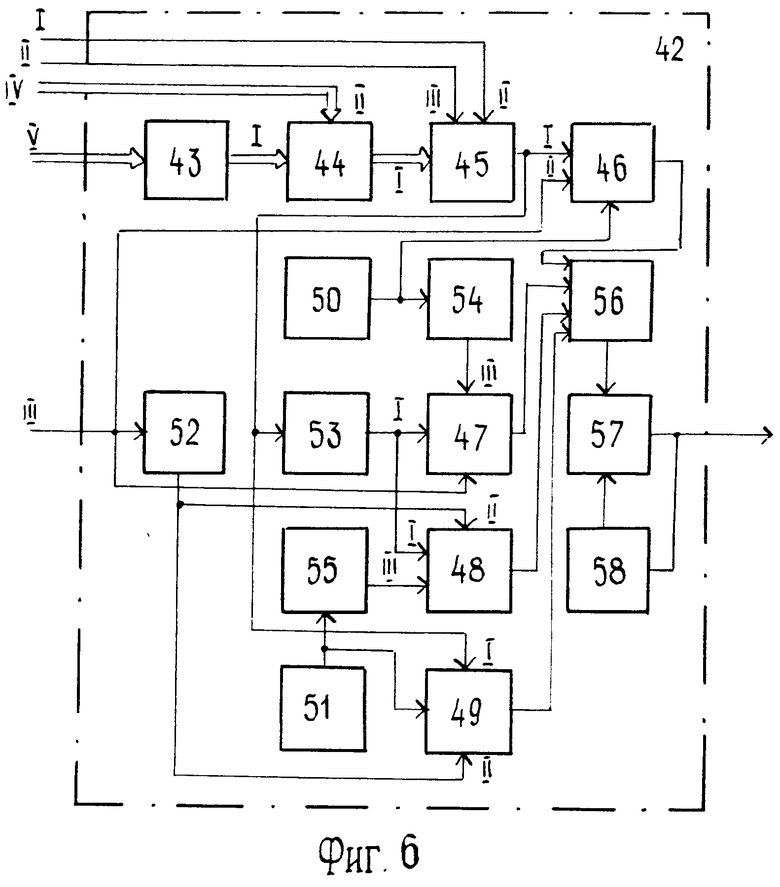

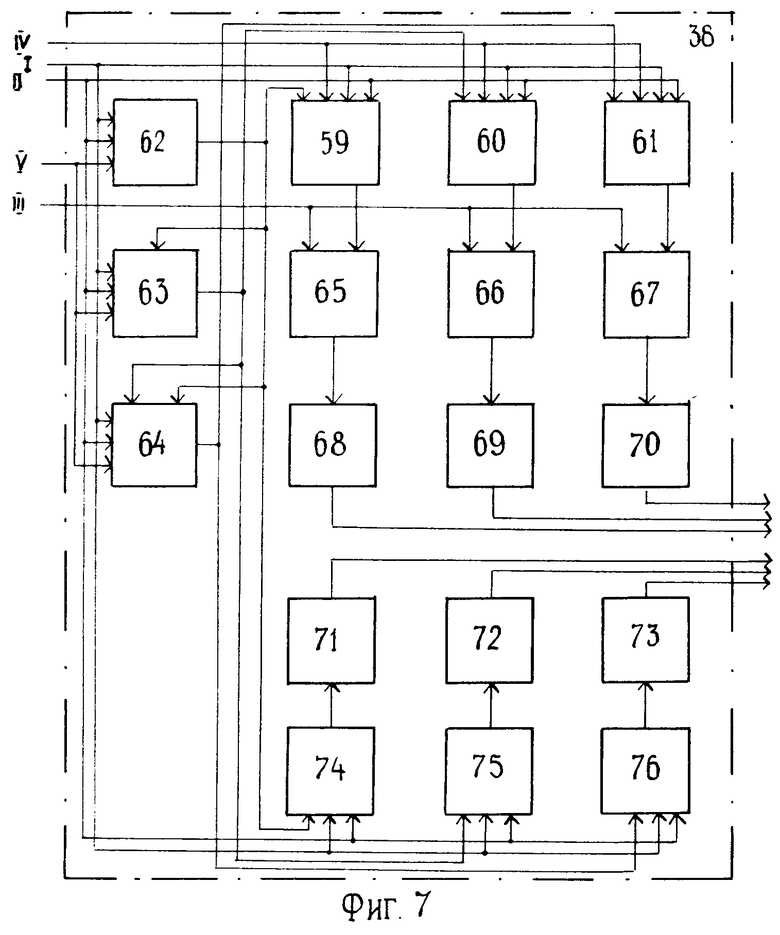

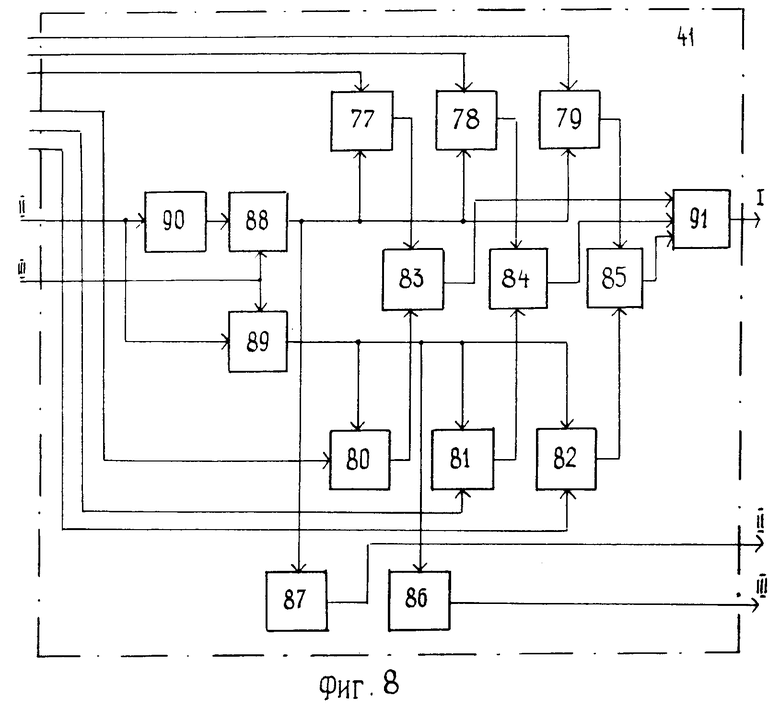

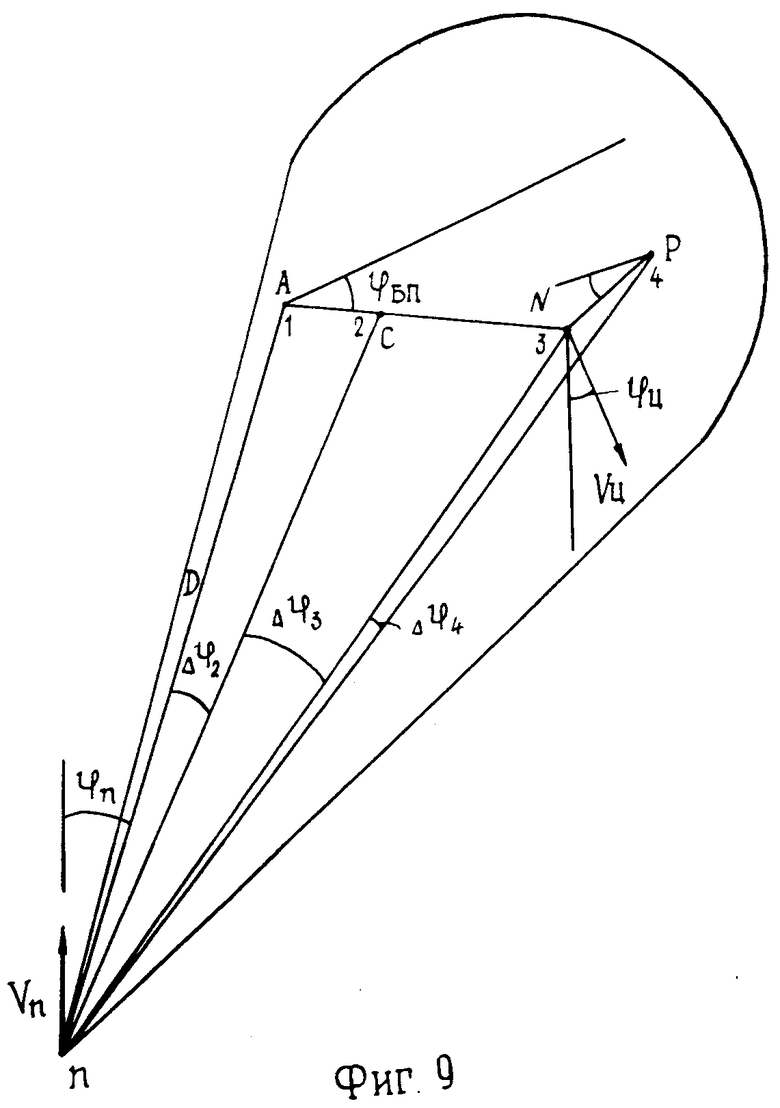

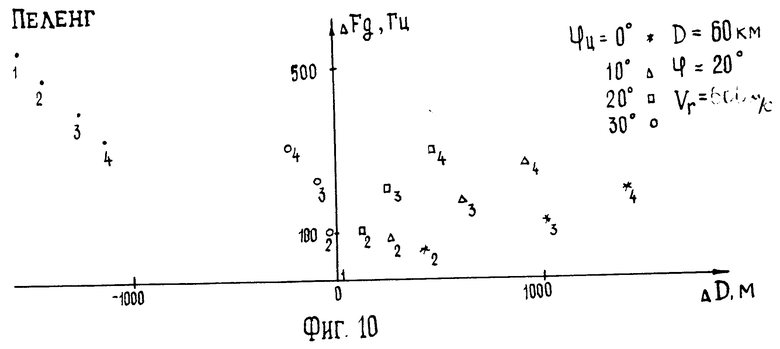

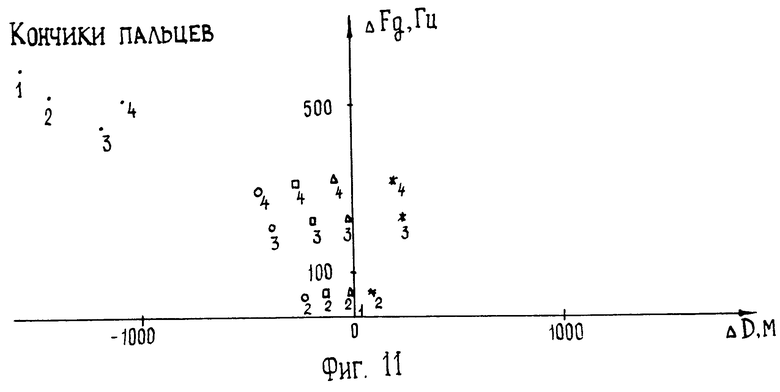

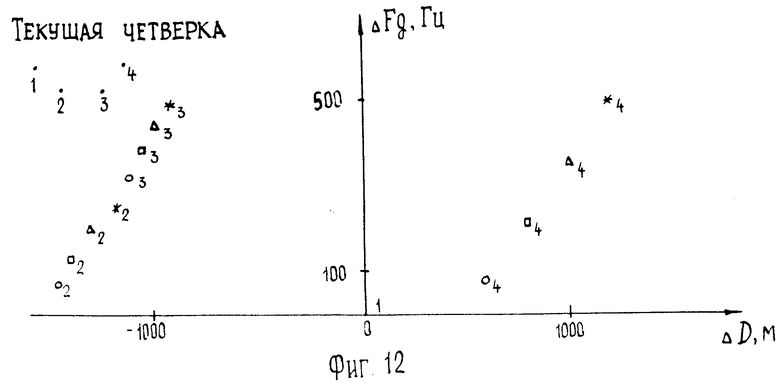

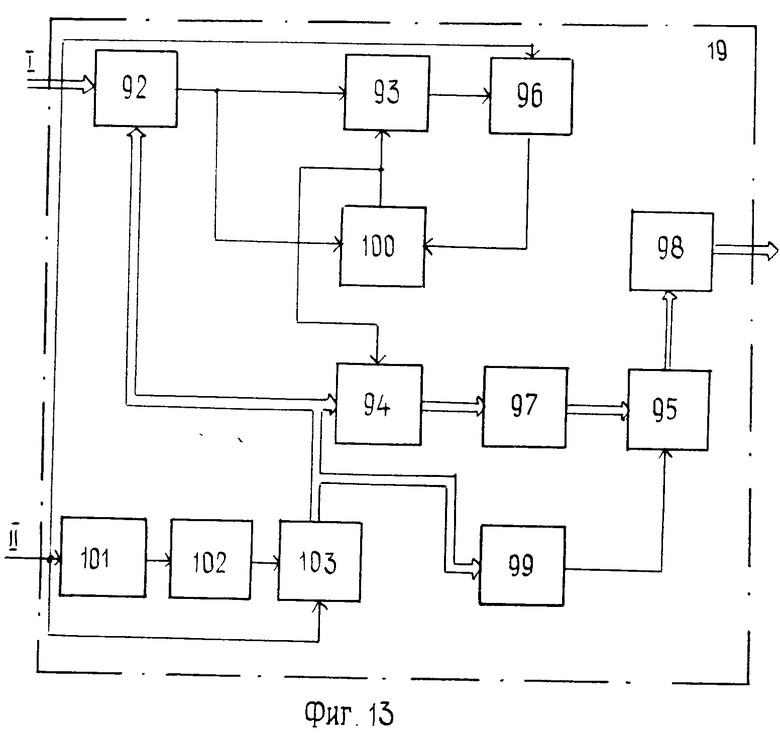

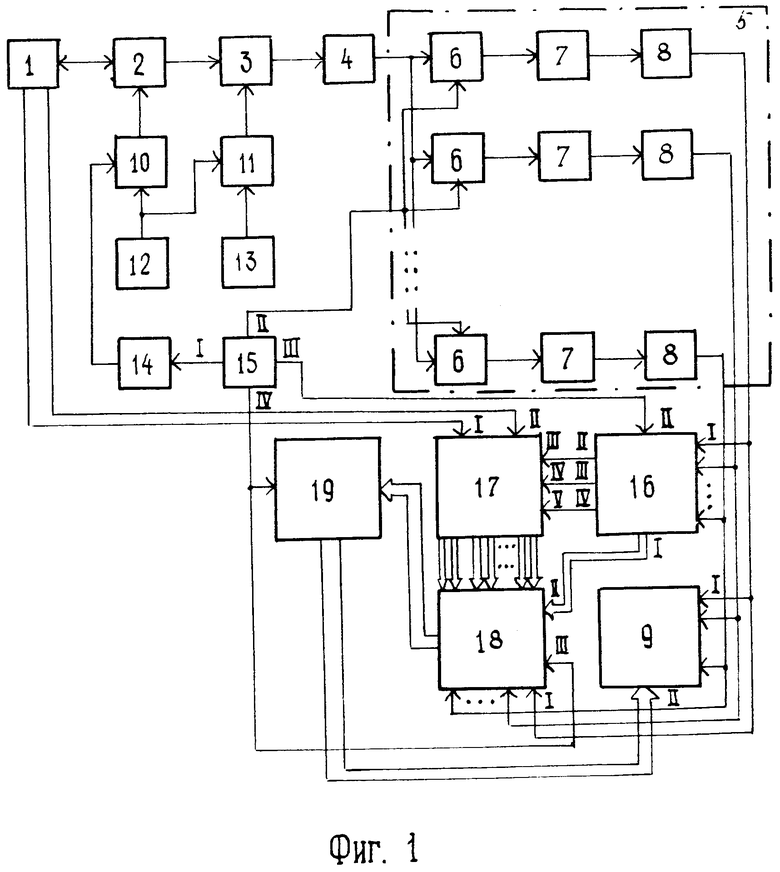

На фиг.1 приведена структурная схема ИД РЛС; на фиг.2 структурная схема блока привязки координат; на фиг.3 структурная схема блока формирования эталонов; на фиг. 4 структурная схема блока вычисления вероятностей; на фиг.5 структурная схема вычислителя вероятности; на фиг.6 структурная схема вычислителя; на фиг.7 структурная схема вычислителя эталона; на фиг.8 структурная схема блока управления; на фиг.9 пример боевого порядка; на фиг.10-12 примеры дальностно-доплеровских портретов; на фиг.13 структурная схема решающего блока.

Импульсно-доплеровская РЛС содержит (см. фиг.1) последовательно соединенные приемопередающую антенну 1, антенный переключатель 2, первый смеситель 3, предварительный усилитель 4 промежуточной частоты и блок 5 селекции, состоящий из N каналов селекции, где N количество элементов разрешения РЛС по дальности, каждый из N каналов селекции состоит из последовательно соединенных селектора 6 дальности, блока 7 частотной селекции и блока 8 цифровой обработки, выход которого является выходом каждого из N выходов блока селекции, соединенных с соответствующими N выходами первой группы входов индикатора 9, а первые входы всех N селекторов 6 дальности объединены и являются первым входом блока 5 селекции, а таже усилитель 10 мощности, второй 11 смеситель, генератор 12 высокой частоты, кварцевый гетеродин 13, модулятор 14, синхронизатор 15, блок 16 привязки координат, блок 17 формирования эталонов, блок 18 вычисления вероятностей и решающий блок 19, причем первый выход синхронизатора 15 через модулятор 14 соединен с первым входом усилителя 10 мощности, второй вход которого соединен с выходом генератора 12 высокой частоты, а выход с вторым входом антенного переключателя 2, второй выход синхронизатора 15 соединен с вторыми входами всех N селекторов дальности и являются вторым входом блока селекции, выход кварцевого гетеродина 13 соединен с первым входом второго смесителя 11, второй вход которого соединен с выходом генератора 12 высокой частоты, а выход с вторым входом первого сместеля 3, вторые входы всех N селекторов 6 дальности объединены и являются вторым входом блока 5 селекции, первые группы входов блока 16 привязки координат и блока 18 вычисления вероятностей объединены и каждый вход этих групп входов соединен с соответствующим выходом блока 5 селекции, второй вход блока 16 привязки координат соединен с третьим выходом синхронизатора 15, первая группа выходов с второй группой входов блока 18 вычисления вероятностей, а второй, третий и четвертый выходы соответственно с третьим, четвертым и пятым входами блока 17 формирования эталонов, первый и второй входы которого соединены соответственно с вторым и третьим выходами антенны 1, а L ˙ M спаренных групп выходов с L ˙ M спаренными группами входов блока 18 вычисления вероятностей, где L количество фиксированных ракурсов цели с общей их суммой 360о, а М количество эталонов возможных боевых порядков воздушной цели, третий вход блока 18 вычисления вероятностей соединен с четвертым выходом синхронизатора 15, а группа его выходов с первой группой входов решающего блока 19, второй вход которого соединен с четвертым выходом синхронизатора 15, группа выходов решающего блока 19 соединена с второй группой входов индикатора 9.

Блок 16 привязки координат (см. фиг.2) содержит первый генератор 20 тактовых импульсов, N первых элементов И 21 и N первых триггеров 22, первый элемент ИЛИ 23, первый 24 и второй 25 элементы НЕ, второй 26, третий 27, четвертый 28, пятый 29 и шестой 30 элементы И, первый запоминающий блок 31, первый 32 и второй 33 дешифраторы, первый счетчик 34, первый 35, второй 36 и третий 37 умножители, причем первые входы N первых элементов И 21 соединены и являются первой группой входов блока 16 привязки координат, а выходы N первых элементов И соединены с информационными входами соответствующих N первых триггеров 22, выходы которых соединены с соответствующими входами первого 32 и второго 33 дешифраторов и первого элемента ИЛИ 23, выход которого через последовательно соединенные первый элемент НЕ 24, второй элемент И 26, первый счетчик 34, третий элемент И 27 и первый умножитель 35 соединен с вторым выходом блока 16 привязки координат, второй вход третьего элемента И 27 соединен с выходом первого элемента ИЛИ 23, выход первого элемента НЕ 24 соединен с объединенными вторыми входами N первых элементов И 21, второй вход второго элемента И 26 соединен с выходом первого генератора 20 тактовых импульсов, вход которого является вторым входом блока 16 привязки координат, первые входы четвертого 28, пятого 29 и шестого 30 элементов И соединены соответственно с первым, вторым и третьим выходами первого запоминающего блока 31, вторые входы четвертого 28, пятого 29 и шестого 30 элементов И объединены и через второй элемент НЕ 25 соединены с выходом второго элемента И 26, а их выходы с вторыми входами соответственно первого 35, второго 36 и третьего 37 умножителей, первый вход второго умножителя 36 соединен с выходом первого умножителя 35, а выход является третьим выходом блока 16 привязки координат, первый вход третьего умножителя 37 соединен с выходом второго дешифратора 33, а выход является четвертым выходом блока 16 привязки координат, группа выходов второго дешифратора 33 является первой группой выходов блока 16 привязки координат, входы обнуления первого счетчика и N первых триггеров 22 объединены и соединены с вторым входом блока 16 привязки координат.

Блок 17 формирования эталонов (см. фиг.3) содержит L ˙ M вычислителей 38 эталонов, первые, вторые, третьи, четвертые и пятые входы которых одноименно объединены между собой соответственно и являются первым, вторым, третьим, четвертым и пятым входами блока 17 формирования эталонов, пара групп выходов каждого из L ˙ M вычислителей 38 эталонов является соответствующей спаренной группой из L ˙ M спаренных групп выходов блока 17 формирования эталонов.

Блок 18 вычисления вероятностей (см. фиг.4) содержит L ˙ M вычислителей 39 верoятности и первый генератор 40 тактовых импульсов, причем спаренная группа входов каждого вычислителя 39 вероятности соединена с соответствующей спаренной группой входов блока 18 вычисления вероятностей, вторые группы входов всех вычислителей 39 вероятности объединены и являются первой группой входов блока 18 вычисления вероятностей, вторая группа входов которого соединена с третьими группами входов всех вычислителей 39 вероятности, четвертые входы которых объединены и соединены с выходом первого генератора 40 тактовых импульсов, вход которого является третьим входом блока 18 вычисления вероятностей и соединен также с объединенными пятыми входами вычислителей 39 вероятности, выход каждого вычислителя 39 вероятности является соответствующим выходом группы из L ˙ M выходов блока 18 вычисления вероятностей.

Каждый вычислитель 39 вероятности (см. фиг.5) содержит блок 41 управления и вычислитель 42, причем спаренная группа входов блока 41 управления соединена с соответствующей спаренной группой входов вычислителя 39 вероятности, второй и третий входы соответственно с четвертым и пятым входами вычислителя 39 вероятности, а первый, второй и третий выходы соответственно с первым, вторым и третьим входами вычислителя 42, четвертая группа входов которого соединена с третьей группой входов вычислителя 39 вероятности, пятая группа входов с второй группой входов вычислителя 39 вероятности, а выход является выходом вычислителя 39 вероятности.

Вычислитель 42 (см. фиг.6) содержит блок 43 первых линий задержки, блок 44 первых элементов совпадения, блок 45 памяти, второй 46, третий 47, четвертый 48 и пятый 49 элементы совпадения, первый 50 и второй 51 запоминающие блоки, первый 52 и второй 53 элементы НЕ, первый 54 и второй 55 вычитающие блоки, первый элемент ИЛИ 56, первый умножитель 57 и вторую линию задержки 58, причем группа входов блока 43 первых линий задержки соединена с пятой группой входов вычислителя 42, а группа выходов с первой группой входов блока 44 первых элементов совпадения, вторая группа входов которого соединена с четвертой группой входов вычислителя 42, а группа выходов с первой группой входов блока 45 памяти, второй и третий входы которого соединены соответственно с первым и вторым входами вычислителя 42, а выход с первыми входами второго 46 и пятого 49 элементов совпадения непосредственно, а третьего 47 и четвертого 48 элементов совпадения через второй элемент НЕ 53, третий вход вычислителя 42 соединен с вторыми входами второго 46 и третьего 47 элементов совпадения непосредственно, а четвертого 48 и пятого 49 элементов совпадения через первый элемент НЕ 52, выход первого запоминающего блока 50 соединен с третьим входом второго элемента 46 совпадения и через первый вычитающий блок 54 с третьим входом третьего элемента 47 совпадения, выход второго запоминающего блока 51 соединен с третьим входом пятого элемента 49 совпадения и через второй вычитающий блок 55 с третьим входом четвертого элемента 48 совпадения, выходы второго 46, третьего 47, четвертого 48 и пятого 49 элементов совпадения соединены с соответствующими входами первого элемента ИЛИ 56, выход которого соединен с первым входом первого умножителя 57, второй вход которого соединен с выходом второй линии 58 задержки, а выход с входом второй линии 58 задержки и является выходом вычислителя 42.

Вычислитель 38 эталона (см. фиг.7) содержит первый 62, второй 63 и третий 64 вычислители разности углов, первый 59, второй 60 и третий 61 вычислители доплеровской частоты, первый 65, второй 66 и третий 67 вычитающие блоки, первый 74, второй 75 и третий 76 вычислители относительной дальности, первый 68, второй 69, третий 70, четвертый 71, пятый 72 и шестой 73 масштабирующие усилители.

Блок 41 управления (см. фиг.8) содержит первую 77, вторую 78, третью 79, четвертую 80, пятую 81 и шестую 82 схемы сравнения, первый 83, второй 84 и третий 85 элементы И, первый 86 и второй 87 дешифраторы, первый 88 и второй 89 счетчики, делитель 90 частоты и первый элемент ИЛИ 91.

Решающий блок 19 содержит (см. фиг.13) мультиплексор 92, первый 93, второй 94 и третий 95 элементы совпадения, первый 96 и второй 97 запоминающие блоки, первый 98 и второй 99 дешифраторы, первую 100 схему сравнения, первую линию 101 задержки, первый генератор 102 тактовых импульсов, первый счетчик 103.

ИД РЛС работает следующим образом (см. фиг.1).

Синхроимпульсы с первого выхода синхронизатора 15 поступают на вход модулятора 14, формирующего прямоугольные импульсы, которые подаются на первый вход усилителя 10 мощности. Одновременно на его второй вход поступает сигнал с выхода генератора 12 высокой частоты. В результате на выходе усилителя 10 мощности формируются высокочастотные зондирующие импульсы, которые через антенный переключатель 2 поступают на антенну 1 и излучаются в пространство. Отраженные от цели сигналы через антенну 1 и антенный переключатель 2 поступают на первый вход первого смесителя 3, на его второй вход подается гетеродинный сигнал с выхода второго смесителя 11. Этот сигнал формируется путем суммирования и фильтрации во втором смесителе 11 сигналов с выходов соответственно генератора 12 высокой частоты и кварцевого гетеродина 13. Сигнал с выхода первого смесителя 3 через предварительный усилитель 4 промежуточной частоты поступает на входы N каналов блока 5 селекции. В селекторах 6 дальности осуществляется стробирование сигнала по дальности импульсами с второго выхода синхронизатора 15. Причем длительность стробирующих импульсов равна длительности излучаемых импульсов, а количество каналов селеции определяется скважностью излучаемого сигнала. В каждом канале селеции с выхода селектора 6 дальности сигнал через блок 7 частотной селекции, в котором осуществляется выделение участка спектра сигнала, свободного от помеховых составляющих, поступает на вход блока 8 цифровой обработки. В блоке 8 цифровой обработки осуществляется спектральный анализ по алгоритму дискретного преобразования Фурье. Полученные отсчеты спектра в блоке 8 цифровой обработки сравниваются с порогом, в результате чего на выходе каждого из N каналов селекции формируется бинарный сигнал. Эти сигналы поступают на первую группу входов индикатора 9 для их индикации.

Однако с помощью данной ИД БРЛС нельзя осуществить распознавание БП ГВЦ и определить ее ракурс относительно БРЛС. В предлагаемом техническом решении распознавание основано на определении меры близости или соответствия полученного изображения эталонному изображению БП ГВЦ в пространстве признаков. Размерность пространства признаков распознавания определяется количеством элементов разрешения по дальности и доплеровской частоте, занимаемых в пространстве ГВЦ, и равно n. В результате решения статистической задачи обнаружения сигнала в каждом из элементов разрешения принимается решение о наличии или отсутствии сигнала цели в этом элементе. В этом случае признаки распознавания бинарны и принимают значение 0 или 1.

Изображение БП ГВЦ в координатах дальность доплеровская частота существенно зависит от ракурса ϕц (см. фиг.9), который неизвестен. В предлагаемом техническом решении количество формируемых эталонов равно L ˙ M, где М количество возможных боевых порядков; L количество фиксированных дискретов ракурса.

Причем L таково, что

L Δ ϕц 360о, где Δ ϕц выбранный дискрет ракурса.

Мерой близости является апостериорная вероятность гипотезы  при условии наблюдения реализации

при условии наблюдения реализации  , где

, где

эталонное изображение

эталонное изображение

j-го БП ГВЦ для k-го дискрета ракурса;

реализация на выходе

реализация на выходе

блока 5 селекции;

Хнi и X

к признаки распознавания.

к признаки распознавания.

Значение принятой меры соответствия вычисляется по формуле

P

P

P Xiн/ X

Xiн/ X где Р(Хiн/X

где Р(Хiн/X

к) вероятность i-го бинарного признака в наблюдаемой реализации при условии, что она соответствует j-му эталону для К-го дискрета ракурса.

к) вероятность i-го бинарного признака в наблюдаемой реализации при условии, что она соответствует j-му эталону для К-го дискрета ракурса.

Исходя из этого, Р(Хiн/X

к) может принимать следующие значения:

к) может принимать следующие значения:

Рпо при X

к 1, Хнi 1;

к 1, Хнi 1;

Рпр при X

к 1, Хнi 0;

к 1, Хнi 0;

Рлт при X

к 0, Хнi 1;

к 0, Хнi 1;

Рпн при X

к 0, Хнi 0; где Рпо, Рпр, Рлт, Рпн вероятности правильного обнаружения, пропуска, ложной тревоги и правильного необнаружения соответственно. Таким образом, распознавание БП ГВЦ и определение ее ракурса сводится к выбору максимальной апостериорной вероятности соответствия наблюдаемой реализации одному из эталонных изображений, сформированных на основании априорных данных о возможных боевых порядках и учета возможности перехвата ГВЦ под разными ракурсами.

к 0, Хнi 0; где Рпо, Рпр, Рлт, Рпн вероятности правильного обнаружения, пропуска, ложной тревоги и правильного необнаружения соответственно. Таким образом, распознавание БП ГВЦ и определение ее ракурса сводится к выбору максимальной апостериорной вероятности соответствия наблюдаемой реализации одному из эталонных изображений, сформированных на основании априорных данных о возможных боевых порядках и учета возможности перехвата ГВЦ под разными ракурсами.

Данный алгоритм реализуется следующим образом.

Сигналы с выходов блока 5 селекции поступают на первую группу входов блока 16 привязки координат, в котором определяется максимальный номер спектрального отсчета, на котором произошло обнаружение цели, и соответствующий ему номер элемента разрешения по дальности. По полученным номерам в блоке 16 привязки координат определяются значения доплеровской частоты (Fд1), скорости сближения (Vr1) и дальности (D1) до цели, имеющей максимальный доплеровский сдвиг частоты. На втором, третьем и четвертом выходах блока 16 привязки координат формируются двоичные коды чисел пропорциональные соответственно значениям Fд1, Vr1, D1, поступающие соответственно на третий, четвертый и пятый входы блока 17 формирования эталонов. На первой группе выходов блока 16 привязки координат формируется N-разрядный параллельный код, поступающий на вторую группу входов блока 18 вычисления вероятностей. С помощью этого кода осуществляется управление записью информации с N выходов блока 5 селекции в блок 18 вычисления вероятностей. На второй вход блока 16 привязки координат поступают тактовые импульсы управления и обнуления цифровых элементов этого блока.

Изображение БП ГВЦ в координатах дальность доплеровская частота зависит от углов ϕА и ϕВ отклонения антенны БРЛС, отслеживающей энергетический центр ГВЦ соответственно в азимутальной и угломестной плоскостях. Значения углов ϕА и ϕВ с второго и третьего выходов антенны 1 поступают соответственно на первый и второй входы блока 17 формирования эталонов. Значения Fд1, Vr1, D1 ϕА, ϕВ используются в блоке 17 формирования эталонов для вычисления эталонов боевых порядков. Всего формируется L ˙ M кодов эталонов, которые с L ˙ M спаренных групп выходов поступают через соответствующие входы в блок 18 вычисления вероятностей. На его третий вход с четвертого выхода синхронизатора 15 поступают тактовые импульсы обнуления и управления работой.

Каждое эталонное изображение БП ГВЦ представляет собой номера элементов разрешения по дальности и доплеровской частоте относительно цели, имеющей максимальный доплеровский сдвиг частоты (наименьший угол пеленга). По сигналам, поступающим с первой группы выходов блока 16 привязки координат на вторую группу входов блока 18 вычисления вероятностей, осуществляется совмещение эталонов с изображением БП ГВЦ в координатах дальность доплеровская частота, которое поступает на первую группу входов блока 18 вычисления вероятностей с N выходов блока 5 селекции. В блоке 18 вычисления вероятностей вычисляется апостериорная поверхность соответствия полученного изображения каждому эталону. Полученные значения апостериорной вероятности через группу выходов блока 18 вычисления вероятностей поступают на решающий блок 19, в котором посредством выбора максимальной апостериорной вероятности определяется боевой порядок ГВЦ и ее ракурс относительно носителя БРЛС. В результате на группе выходов решающего блока 19 формируется цифровой код, соответствующий БП и ракурсу ГВЦ, который поступает через вторую группу входов на индикатор 9. На индикаторе 9 загораются два транспоранта (вид БП ГВЦ и его ракус).

Совмещение изображения БП ГВЦ в координатах дальность доплеровская частота осуществляется в блоке 16 привязки координат следующим образом (см. фиг. 2). Каждый такт работы начинается с поступления на второй вход блока 16 привязки координат тактового импульса, обнуляющего первые триггеры 22 и первый счетчик 34.

Этим же импульсом осуществляется запуск первого генератора 20 тактовых импульсов. Период повторения импульсов равен периоду поступления спектральных отсчетов на входы N первых элементов И 21. После обнуления на выходах N первых триггеров 22 формируется сигнал, соответствующий логическому "0". Такой же уровень сигнала присутствует на выходе первого элемента ИЛИ 23. Тогда на выходе первого элемента НЕ 24 формируется сигнал логической "1", поступающий на вторые входы N первых элементов И 21 и разрешающий прохождение сигналов через эти элементы на входы N первых триггеров 22. Этот же сигнал разрешает прохождение тактовых импульсов через второй элемент И 26 на вход первого счетчика 34. При появлении на каком-либо из входов N первых триггеров 22 спектрального отсчета с амплитудой, соответствующей уровню логической "1", что соответствует обнаружению цели, данный триггер опрокидывается, на его выходе формируется сигнал логической "1", который, проходя через первый элемент ИЛИ 23, приводит к формированию на выходе первого элемента НЕ 24 логического "0". Этот нулевой сигнал запрещает прохождение последующих спектральных отсчетов сигнала через N первых элементов И 21 и прохождение тактовых импульсов через второй элемент И 26 на вход первого счетчика 34. Таким образом фиксируется номер спектрального отсчета, на котором произошло обнаружение сигнала в блоке 5 селекции, а при условии поступления значений спектральных отсчетов с больших номеров фиксируется максимальный номер спектрального отсчета, на котором была обнаружена цель из состава ГВЦ. Код номера отсчета с выхода первого счетчика 34 через третий элемент И 27, на второй вход которого поступает разрешающий сигнал с выхода первого элемента ИЛИ 23, подается на первый вход первого умножителя 35. Сигнал нулевого уровня с выхода второго элемента И 26 инвертируется во втором элементе НЕ 25 и в виде разрешающего сигнала единичного уровня поступает на вторые входы четвертого 28, пятого 29 и шестого 30 элементов И.

Запоминающий блок 31 представляет собой задатчик постоянных величин δFд, λ/2, δD, коды которых формируются соответственно на первом, втором и третьем выходах, где δFд ширина спектрального отсчета; λ/2 половина длины волны зондирующего сигнала, δD величина элемента разрешения по дальности.

Код величины δFд с первого выхода первого запоминающего блока 31 поступает на первый вход четвертого элемента И 28, а с его выхода на второй вход первого умножителя 35. На его выходе формируется код, пропорциональный доплеровской частоте:

Fд1 δFд k, где k номер спектрального отсчета с выхода первого счетчика 34. Полученное значение в виде кода поступает на первый вход второго умножителя 36, на первый вход которого через пятый элемент И 29 поступает код величины λ/2. В результате на выходе второго умножителя 36 формируется код, пропорциональный скорости сближения носителя ИД БРЛС и ГВЦ

V =

=  поступающий на третий выход блока 16 привязки координат. На входы второго дешифратора 33 поступают сигналы с выходов N первых триггеров 22. После опрокидывания одного из них и фиксации спектрального отсчета второй дешифратор 33 формирует на своем выходе код, соответствующий номеру элемента разрешения по дальности, в котором находится обнаруженная цель, имеющая максимальный доплеровский сдвиг частоты. Этот код поступает на первый вход третьего умножителя 37, на второй вход которого с третьего выхода запоминающего блока 31 через шестой элемент И 30 поступает код величины δD.

поступающий на третий выход блока 16 привязки координат. На входы второго дешифратора 33 поступают сигналы с выходов N первых триггеров 22. После опрокидывания одного из них и фиксации спектрального отсчета второй дешифратор 33 формирует на своем выходе код, соответствующий номеру элемента разрешения по дальности, в котором находится обнаруженная цель, имеющая максимальный доплеровский сдвиг частоты. Этот код поступает на первый вход третьего умножителя 37, на второй вход которого с третьего выхода запоминающего блока 31 через шестой элемент И 30 поступает код величины δD.

В результате на выходе умножителя 37 формируется код дальности до цели D1. Этот код поступает на четвертый выход блока 16 привязки координат. Сигналы с выходов N первых триггеров 22 поступают также на входы первого дешифратора 32, который в зависимости от номера опрокинутого триггера, соответствующего элементу разрешения по дальности, выдает на r из N выходах единичный сигнал, где r определяется удвоенным максимальным размером зоны пространства по дальности, занимаемым ГВЦ и выраженным в количестве элементов разрешения по дальности. Выходы первого дешифратора 32 объединены в первую группу выходов блока 16 привязки координат.

Блок 17 формирования эталонов, представляющий собой L ˙ M параллельно, соединенных вычислителей 38 эталонов, работает следующим образом (см. фиг. 3).

На входы блока 17 формирования эталонов и на аналогичные входы каждого вычислителя 38 эталона поступают следующие сигналы: на первый вход код ϕА, пропорциональный отклонению антенны 1 ИД БРЛС в азимутальной плоскости; на второй вход код ϕВ, пропорциональный отклонению антенны 1 ИД БРЛС в угломестной плоскости; на третий вход код доплеровской частоты Fд1; на четвертый вход код скорости сближения; на пятый вход код дальности D1.

На основании алгоритма, определяемого геометрией построения БП ГВЦ в пространстве, в схеме каждого из L ˙ M вычислителей 38 эталонов вычисляется эталон в виде кодов номеров элементов разрешения по дальности и доплеровской частоте, в которых должны находиться цели. Результаты вычислений формируются на спаренной группе входов каждого из L ˙ M вычислителей эталонов.

Блок 18 вычисления вероятностей, состоящий из L ˙ M параллельно соединенных вычислителей 39 вероятности и первого генератора 40 тактовых импульсов, работает следующим образом (см. фиг.4).

На вторую группу входов каждого вычислителя 39 вероятности через первую группу входов блока 18 вычисления вероятностей поступают спектральные отсчеты с N выходов блока 5 селекции. Блок 18 вычисления вероятностей соединен L ˙ M спаренными группами входов с L ˙ M спаренными группами выходов блока 17 формирования эталонов, причем каждый из вычислителей 39 вероятности соединен спаренной группой входов со спаренной группой выходов соответствующего вычислителя 38 эталона (см. фиг.3). На вторую группу входов блока 18 вычисления вероятностей поступают сигналы с первой группы выходов блока 16 привязки координат, которые обеспечивают совмещение реального и эталонного изображений в каждом из L ˙ M вычислителей 39 вероятности. На третий вход блока 18 вычисления вероятностей поступают синхроимпульсы с четвертого выхода синхронизатора 15, обеспечивающие запуск генератора 40 тактовых импульсов и обнуление цифровых элементов блока 18 вычисления вероятностей в начале каждого такта. В каждом из L ˙ M вычислителей 39 вероятности вычисляется апостериорная вероятность соответствия наблюдаемого изображения соответствующему эталону. Значение апостериорной вероятности формируется в виде кода на выходе каждого вычислителя 39 вероятности. Эти выходы объединены в группу из L ˙ M выходов блока 18 вычисления вероятностей.

Вычислитель 39 вероятности состоит из блока 41 управления и вычислителя 42 (см. фиг.5). По спаренной группе входов вычислителя 39 вероятности в блок 41 управления поступают коды номеров элементов разрешения в координатах дальность доплеровская частота, в которых должны находиться цели. На второй вход блока 41 управления через четвертый вход вычислителя 39 вероятности поступают импульсы с генератора 40 тактовых импульсов (см. фиг.4), частота следования которых соответствует частоте поступления спектральных отсчетов. На пятый вход вычислителя 42 через второй вход вычислителя 39 вероятности поступают спектральные отсчеты с N выходов блока 5 селекции (см. фиг.1). В вычислителе 42 осуществляется запись и хранение в течение такта работы информации в ячейках памяти, каждая из которых соответствует элементу разрешения в координатах дальность доплеровская частота. Управление записью информации в вычислитель 42 осуществляется по сигналам, поступающим через третью группу входов вычислителя 39 вероятности на четвертую группу входов вычислителя 42. На третий вход блока 41 управления через пятый вход вычислителя 39 вероятности поступают импульсы, обнуляющие цифровые элементы блока 41 управления в начале каждого такта работы. С второго и третьего выходов блока 41 управления на соответствующие входы вычислителя 42 поступают сигналы считывания информации последовательно со всех ячеек памяти. С первого выхода блока 41 управления на соответствующий вход вычислителя 42 поступает бинарный сигнал, причем амплитуда его равна единице в случае, когда в ячейке памяти, с которой в данный момент считывается информация, должна находиться цель в соответствии с вычисленным эталоном.

Алгоритм вычисления апостериорной вероятности реализован в вычислителе 42 следующим образом (см. фиг.6).

На пятую группу входов вычислителя 42 сигнал в виде спектральных отсчетов с N элементов разрешения по дальности поступает на группу входов блока 43 первых линий задержки, состоящего из N параллельно соединенных линий задержки, время задержки в которых равно времени обработки информации в блоке 16 привязки координат. Блок 44 первых элементов совпадения состоит из N параллельно соединенных элементов совпадения, на один вход каждого из которых поступает сигнал в виде спектральных отсчетов с соответствующего элемента разрешения по дальности, а на другой управляющий сигнал. Значения управляющих сигналов формируются на N выходах первого дешифратора 32 (см. фиг.2) и уровень их равен логической "1" на r из N выходов. Эти сигналы разрешают прохождение спектральных отсчетов через r из N элементов совпадения блока 44. Блок 45 памяти состоит из l x r ячеек памяти, где l количество спектральных отсчетов в анализируемом доплеровском диапазоне частот. Таким образом, в блок 45 памяти осуществляется запись информации c l x r элементов разрешения, в которых находится ГВЦ. Затем осуществляется ее считывание по сигналам, поступающим на второй и третий входы блока 45 памяти через первый и второй входы вычислителя 42 соответственно. В результате считывания на выходе блока 45 памяти формируется бинарный сигнал, уровень которого равен логической "1" в том случае, если в элементе разрешения пространства, соответствующем ячейке памяти, из которой в настоящий момент считывается информация, была обнаружена цель. Второй 46, третий 47, четвертый 48 и пятый 49 элементы совпадения управления сигналами с выхода блока 45 памяти, а также с третьего входа вычислителя 42 непосредственно и через первый 52 и второй 53 элементы НЕ. Первый 50 и второй 51 запоминающие блоки представляют собой задатчики постоянных величин Рпо и Рлт соответственно. Код значения Рпо поступает на третий вход второго элемента 46 совпадения непосредственно, а на третий вход третьего элемента 47 совпадения через первый вычитающий блок 54, в котором осуществляется операция 1 Рпо. Аналогично код значения Рлт поступает на третий вход пятого элемента 49 совпадения непосредственно, а на третий вход четвертого элемента 48 совпадения через второй вычитающий блок 55, где выполняется операция 1 Рлт. В результате в зависимости от комбинации значений сигналов на выходе блока 45 памяти и на третьем входе вычислителя 42, на первом входе четвертого умножителя 57 формируются коды значений Рпо, 1 Рпо, Рлт, 1 Рлт. Полученное значение через вторую линию 58 задержки, время задержки которой равно периоду считывания информации из ячеек памяти блока 45 памяти, поступает на второй вход четвертого умножителя 57. После считывания информации со всех ячеек памяти код полученного значения апостериорной вероятности данного вычислителя 42 поступает на первую группу входов решающего блока 19 (см. фиг.1). На второй его вход поступают синхроимпульсы с четвертого выхода синхронизатора 15, определяющие начало каждого такта работы решающего блока 19.

Пример реализации решающего блока 19 представлен на фиг.13 и работает следующим образом.

Синхроимпульс, поступающий на второй вход решающего блока 19 обнуляет четвертый счетчик 103 и первый запоминающий блок 96, а также через первую линию 101 задержки запускает первый генератор 102 тактовых импульсов. Время задержки определяется временем вычисления значений апостериорных вероятностей в блоке 18 (см. фиг.4). Код с выхода первого счетчика 103 поступает на управляющий вход мультиплексора 92, коммутируя на его выходе последовательно каждое из L ˙ M значений апостериорной вероятности. Эти значения сравниваются в первой схеме 100 сравнения с числом, записанным в первом запоминающем блоке 96. Если значение апостериорной вероятности больше этого числа, то на первый 93 и второй 94 элементы совпадения поступает сигнал логической единицы, разрешающий запись в первый 96 и второй 97 запоминающие блоки значения апостериорной вероятности и кода числа из первого счетчика 103 соответственно. После того, как первый счетчик 103 произведет подсчет L ˙ М импульсов, во втором запоминающем блоке 97 будет зафиксирован номер входа из первой группы входов решающего блока 19, по которому поступило максимальное значение апостериорной вероятности, а второй дешифратор 99 сформирует на своем выходе сигнал, разрешающий прохождение кода этого номера на вход первого дешифратора 98. Он формирует на группе выходов решающего блока 19 сигналы, обеспечивающие загорание на индикаторе 9 транспорантов о БП наблюдаемой ГВЦ и ее ракурсе.

Для оценки возможности распознавания БП ГВЦ с помощью указанных признаков производился расчет изображений в координатах дальность доплеровская частота для групповой цели, изображенной на фиг.9. Изображения для боевых порядков типа "пеленг", "кончики пальцев", "текущая четверка" представлены на фиг. 10-12 соответственно. Привязка осуществлялась к ближней по пеленгу цели (ей присвоен индекс 1); по горизонтальной оси системы координат откладывается разность расстояний истребитель цель, а по вертикальной относительный доплеровский сдвиг частоты.

П р и м е р. Пусть БП ГВЦ "кончики пальцев" (см. фиг.9).

Входными данными для вычислителя 38 эталона (см. фиг.7) являются коды углов пеленга ГВЦ в горизонтальной ϕА и угломестной ϕВ плоскостях, поступающие на первый и второй входы вычислителя 38 эталона соответственно, а также коды дальности D1, скорости Vr1, доплеровской частоты Fд1 цели, имеющей максимальный доплеровский сдвиг частоты, которые поступают соответственно на первый, четвертый и третий входы вычислителя 38 эталона.

Согласно фиг.9, доплеровский сдвиг частоты для второй, третьей и четвертой целей при БП 20о и принятом для простоты предположении ϕВ 0 будет определяться соответственно

F =

=  cos(ϕA+Δϕ2) (1)

cos(ϕA+Δϕ2) (1)

F =

=  cos(ϕA+Δϕ2+Δϕ3) (2)

cos(ϕA+Δϕ2+Δϕ3) (2)

F =

=  cos(ϕA+Δϕ2+Δϕ3+Δϕ4) (3) где Vr= Vи+Vц

cos(ϕA+Δϕ2+Δϕ3+Δϕ4) (3) где Vr= Vи+Vц (4)

(4)

Δϕ2=  (5)

(5)

Δϕ3=  (6)

(6)

Δϕ4=  (7)

(7)

В первом 62, втором 63 и третьем 64 вычислителях разности углов на основании измеренных значений дальности, скорости сближения, углов пеленга цели для одного из L возможных ракурсов ГВЦ осуществляется вычисление разности углов пеленга между первой целью и остальными целями в составе ГВЦ по алгоритмам (5), (6), (7) соответственно. Затем на основании вычисленных значений Δϕ2, Δϕ3, Δϕ4 в первом 59, втором 60 и третьем 61 вычислителях доплеровской частоты определяются значения Fд2, Fд3, Fд4 согласно формулам (1), (2), (3). Перед выполнением вычислений по выражениям (1), (2), (3) в каждом вычислителе доплеровской частоты осуществляется вычисление значения V по алгоритму

V  (8) В первом 65, втором 66 и третьем 67 вычитающих блоках для i 2, 3, 4 соответственно вычисляется относительный доплеровский сдвиг частоты

(8) В первом 65, втором 66 и третьем 67 вычитающих блоках для i 2, 3, 4 соответственно вычисляется относительный доплеровский сдвиг частоты

ΔFдi Fд1 Fдi, (9) где i номер цели.

В первом 68, втором 69 и третьем 70 масштабирующих усилителях для i 2, 3, 4 соответственно выполняется операция определения номера элемента разрешения по доплеровской частоте, в котором в соответствии с выбранным эталоном должен присутствовать сигнал цели по формуле

n = sup

= sup (10) где операция Sup[ означает округление до большего целого. Одновременно в первом 74, втором 75 и третьем 76 вычислителях относительной дальности вычисляются значения ΔD2, ΔD3, ΔD4 соответственно по алгоритмам

(10) где операция Sup[ означает округление до большего целого. Одновременно в первом 74, втором 75 и третьем 76 вычислителях относительной дальности вычисляются значения ΔD2, ΔD3, ΔD4 соответственно по алгоритмам

ΔD2 [AC] cos (70 + ϕц + ϕa) (11)

ΔD3 [CN] cos (70 + ϕц + ϕa + Δϕ2) (12)

ΔD4 [CN] cos (70 +

+ϕц + ϕa + Δϕ2 + Δϕ3) (13) Затем в четвертом 71, пятом 72 и шестом 73 масштабирующих усилителях для i 2, 3, 4 соответственно определяются номера элементов разрешения по дальности, в которых должны находиться цели.

n = sup

= sup (14) Выходы блоков 68, 69 и 70, а также блоков 71, 72 и 73 объединены в группы выходов и являются спаренной группой выходов вычислителя 38 эталонов. Здесь формируются коды номеров элементов разрешения по дальности и доплеровской частоте, в которых должны находиться цели при соответствии наблюдаемого БП ГВЦ данному эталону.

(14) Выходы блоков 68, 69 и 70, а также блоков 71, 72 и 73 объединены в группы выходов и являются спаренной группой выходов вычислителя 38 эталонов. Здесь формируются коды номеров элементов разрешения по дальности и доплеровской частоте, в которых должны находиться цели при соответствии наблюдаемого БП ГВЦ данному эталону.

Для данного примера БП ГВЦ блок 41 управления работает следующим образом (см. фиг. 8). Через третий вход блока 41 управления на первые входы первого 88 и второго 89 счетчиков в начале каждого такта работы поступают импульсы обнуления. На вторые входы этих счетчиков поступают импульсы через второй вход блока 41 управления с выхода генератора 40 тактовых импульсов (см. фиг. 4), причем на второй вход первого 88 счетчика импульсы поступают через делитель 90 частоты с коэффициентом деления r. В результате на выходах счетчиков 88 и 89 формируются коды, осуществляющие управление через первый 86 и второй 87 дешифраторы считыванием информации с блока 45 памяти (см. фиг.6). Сигналы управления считыванием поступают на второй и третий выходы блока 41 управления. Одновременно сигнал с выхода первого 88 счетчика поступает на вторые входы первой 77, второй 78 и третьей 79 схем сравнения, где происходит сравнение кода числа с кодами эталонных номеров элементов разрешения по доплеровской частоте, поступающих через первую группу спаренных групп входов блока 41 управления на первые входы указанных схем сравнения для второй, третьей и четвертой цели соответственно. В результате на выходе схемы сравнения формируется сигнал с уровнем логической единицы в момент равенства кодов числа и эталонного номера и с уровнем логического нуля во всех остальных случаях. Четвертая 80, пятая 81 и шестая 82 схемы сравнения работают аналогично с той лишь разницей, что на их первые входы поступают коды эталонных номеров элементов разрешения по дальности через вторую группу входов спаренной группы входов блока 41 управления. На первые входы первого 83, второго 84 и третьего 85 элементов И поступают сигналы с выходов соответственно первой 77, второй 78 и третьей 79 схем сравнения, а на вторые входы сигналы с выходов соответственно четвертой 80, пятой 81 и шестой 82 схем сравнения. Выходы первого 83, второго 84 и третьего 85 элементов И соединены с соответствующими входами первого элемента ИЛИ 91, выход которого является первым выходом блока 41 управления. При соответствии кодов числа на выходах первого 88 и второго 89 счетчиков кодам номеров эталонных элементов разрешения в соответствующих схемах сравнения на их выходах формируются сигналы с уровнем логической единицы, которые через соответствующий элемент И и элемент ИЛИ 91 в виде уровня логической единицы поступает на вход блока 41 управления.

Таким образом, предлагаемое техническое решение позволяет расширить функциональные возможности ИД РЛС за счет распознавания БП ГВЦ и определения ее ракурса.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБРАБОТКИ СИГНАЛОВ РАДИОЛОКАЦИОННОЙ СТАНЦИИ БОКОВОГО ОБЗОРА | 1998 |

|

RU2124738C1 |

| ИМПУЛЬСНО-ДОПЛЕРОВСКАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1997 |

|

RU2109306C1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ НАЗЕМНЫХ ЦЕЛЕЙ В ТРЕХКАНАЛЬНОЙ ЦИФРОВОЙ РСА | 1998 |

|

RU2205423C2 |

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ С ПЕРЕМЕННОЙ СТРУКТУРОЙ | 1998 |

|

RU2130635C1 |

| АССОЦИАТИВНЫЙ ВЫЧИСЛИТЕЛЬ СМЕЩЕНИЯ ЦЕНТРА ТЕКУЩЕГО ИЗОБРАЖЕНИЯ ОТ ЦЕНТРА ЭТАЛОННОГО | 1991 |

|

RU2029358C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ ДЛИТЕЛЬНОСТИ | 1992 |

|

RU2020735C1 |

| Устройство для измерения динамических характеристик | 1983 |

|

SU1168902A1 |

| РАСХОДОМЕР ТОПЛИВА | 1990 |

|

RU2035699C1 |

| ТОПЛИВОМЕР | 1991 |

|

RU2019794C1 |

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ С ПЕРЕМЕННОЙ СТРУКТУРОЙ | 1998 |

|

RU2132079C1 |

Изобретение относится к радиолокации. Устройство содержит антенну 1, антенный переключатель 2, смесители 3, 11, предварительный усилитель частоты 4, блок 5 селекции, селекторы 6 дальности, блоки 7 частотной селекции, блоки 8 цифровой обработки, индикатор 9, усилитель 10 мощности, генератор 12 высокой частоты, кварцевый гетеродин 13, модулятор 14, синхронизатор 15, блок 16 привязки координат, блок 17 формирования эталонов, блок 18 вычисления вероятностей, решающий блок 19, что позволяет расширить функциональные возможности путем распознавания боевого порядка групповой воздушной цели и определения ее ракурса. 5 з.п. ф-лы, 13 ил.

| Дудник П.И | |||

| и Чересов Ю.И | |||

| Авиационные радиолокационные устройства, М.: ВВИА им.проф | |||

| Н.Е.Жуковского, 1986, с.247, рис.8.15. |

Авторы

Даты

1995-06-19—Публикация

1990-07-26—Подача