Изобретение относится к приборостроению и может быть использовано при построении долговременных запоминающих устройств на подвижном носителе.

Известны способы записи-воспроизведения (контроля аппарата магнитной записи), включающие запись на движущийся магнитный носитель кодовой последовательности, воспроизведение ее с магнитного носителя, суммирование простробированных воспроизведенных импульсов и формирование сигнала ошибки.

Однако эти способы не обеспечивают достаточной точности при записи-воспроизведении реальной цифровой информации.

Известны также способы записи-воспроизведения цифровой информации с использованием корректирующих кодов, которые образуются добавлением некоторого количества дополнительных корректирующих разрядов к информационным разрядам, промежуточного запоминания информации, формирования информационных разрядов выходного кода с автоматическим обнаружением и исправлением определенного количества ошибок.

Недостатком этих способов является ограниченная точность и значительная сложность реализации.

Наиболее близким по технической сущности и достигаемому эффекту является способ записи-воспроизведения цифровой информации по частям от нескольких источников с контрольными разрядами на четность для каждой из ее частей, при которой производят промежуточное запоминание воспроизведенной информации и контроль ее по частям, а при обнаружении ошибки в контролируемой части производят ее замену.

Недостатком известного способа является низкая точность (достоверность), обусловленная тем, что осуществляется косвенный контроль достоверности информации по количеству единиц в ней. Например, в случае пропадания двух единиц в информации (что может иметь место на практике) зафиксируется правильный результат.

Наиболее близким по технической сущности и достигаемому эффекту устройством для реализации предлагаемого способа является устройство записи-воспроизведения цифровой информации, содержащее накопитель на подвижном носителе, блок записи и воспроизведения цифровой информации, сопряженный с накопителем, блок буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде, первый, второй, третий, четвертый, пятый и шестой элементы И, первый элемент ИЛИ, первая и вторая шины информационных входов которого подключены соответственно к информационным выходам четвертого шестого элементов И.

Недостатком известного устройства записи-воспроизведения цифровой информации является также низкая точность (достоверность), обусловленная тем, что в нем осуществляется косвенный контроль достоверности информации по количеству единиц в ней.

Кроме того, реализация известного устройства приводит к значительному увеличению объема памяти накопителя (носителя) за счет записи дублирующей информации и дополнительных разрядов.

Целью изобретения является повышение точности воспроизведения.

Реализация изобретения позволяет значительно уменьшить объем накопителя (носителя).

Поставленная цель достигается тем, что 5 согласно способу записи-воспроизведения цифровой информации, заключающемуся в записи по частям цифровой информации, промежуточном запоминании воспроизводимой части цифровой информации, конт0 роле ее по частям и замене дефектной части при обнаружении ошибки, введены новые операции, заключающиеся в том, что запись массивов частей цифровой информации на носитель производят одновременно с их за5 поминанием и поочередно с промежуточным воспроизведением, в процессе которого при промежуточном запоминании контроль осуществляют путем поразрядного сравнения с одноименной запомненной

0 частью в процессе записи на носитель, при несовпадении запомненную часть информации маркируют адресом контролируемой информации с носителя и дополнительно запоминают полученную информацию, ис5 пользуя ее для замены в соответствии с адресом дефектной части в процессе окончательного воспроизведения информации с носителя, осуществляя это воспроизведение одновременно с запоминанием

0 исходной цифровой информации.

Устройство для реализации способа записи-воспроизведения цифровой информации содержит накопитель на подвижном носителе, блок записи и воспроизведения

5 цифровой информации, сопряженный с накопителем, блок буферной памяти с преобразователями кода с шинами выходов . цифровой информации в последовательном и параллельном коде, первый, второй, тре0 тий, четвертый, пятый и шестой элементы И, первый элемент ИЛ И, первая и вторая шины информационных входов которого подключены соответственно к информационным выходам четвертого и шестого элементов И.

5 Введение в устройство первого, второго и третьего блоков памяти, реверсивного счетчика, компаратора данных цифровой информации, адресного компаратора, блока управления, первого и второго регистров

0 адреса, регистра памяти, седьмого, восьмого, девятого, десятого и одиннадцатого элементов И, второго элемента ИЛИ, первого триггера, второго и третьего триггеров, селектора сигналов, формирователя импуль5 сов, формирователя синхроимпульсов, блока управления приводом, шины входной информации, шины выходной информации в последовательном коде, шины выходной информации в параллельном коде способствует достижению поставленной цели.

При этом эффективность достижения цели изобретения повышается при реализации блока управления на основе микро- ЭВМ, а также реализации блоков памяти как образцовых с ограниченным объемом.

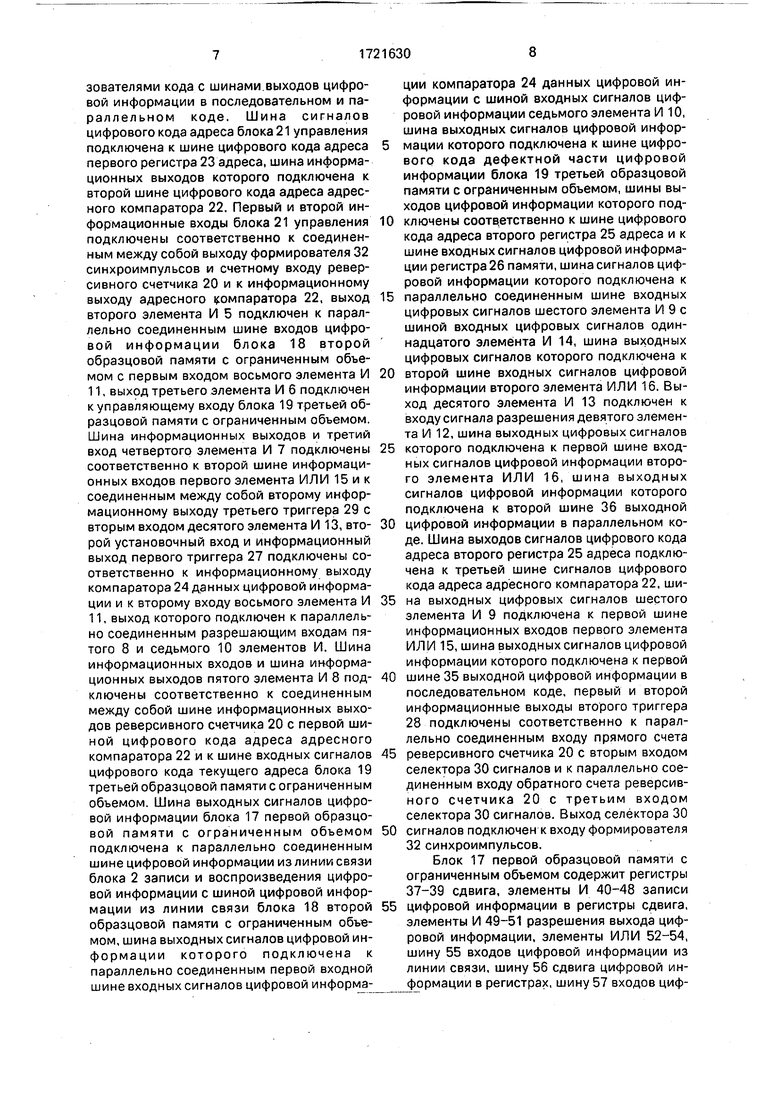

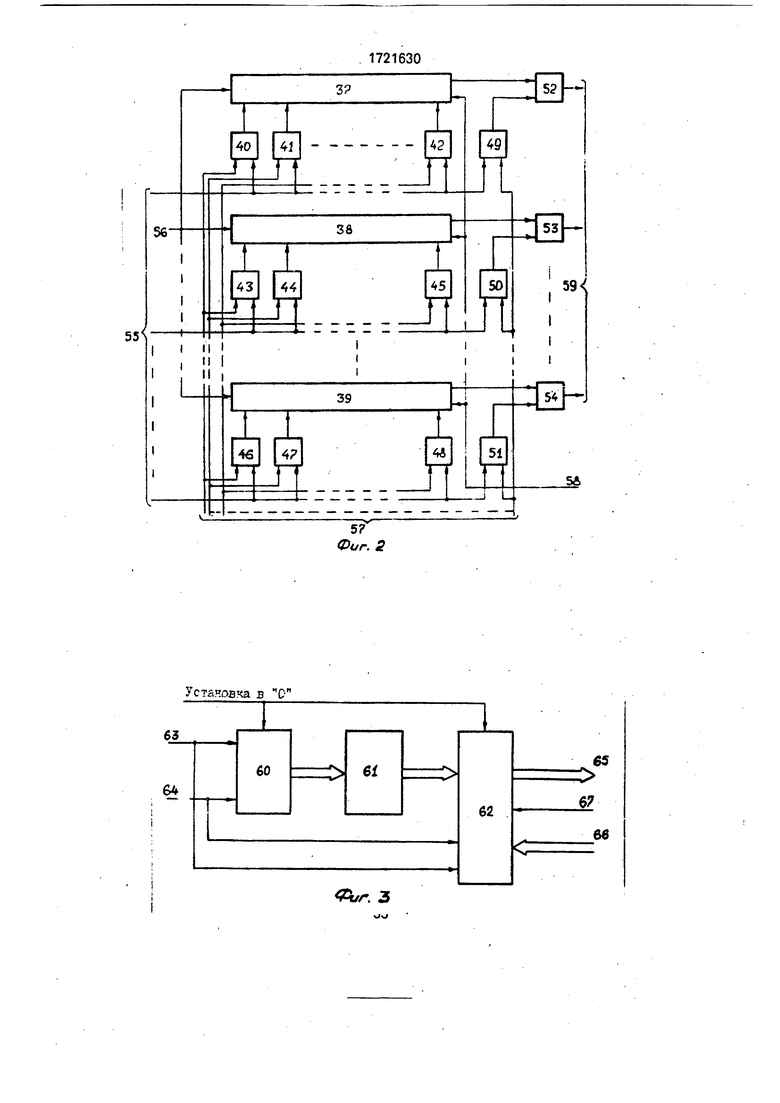

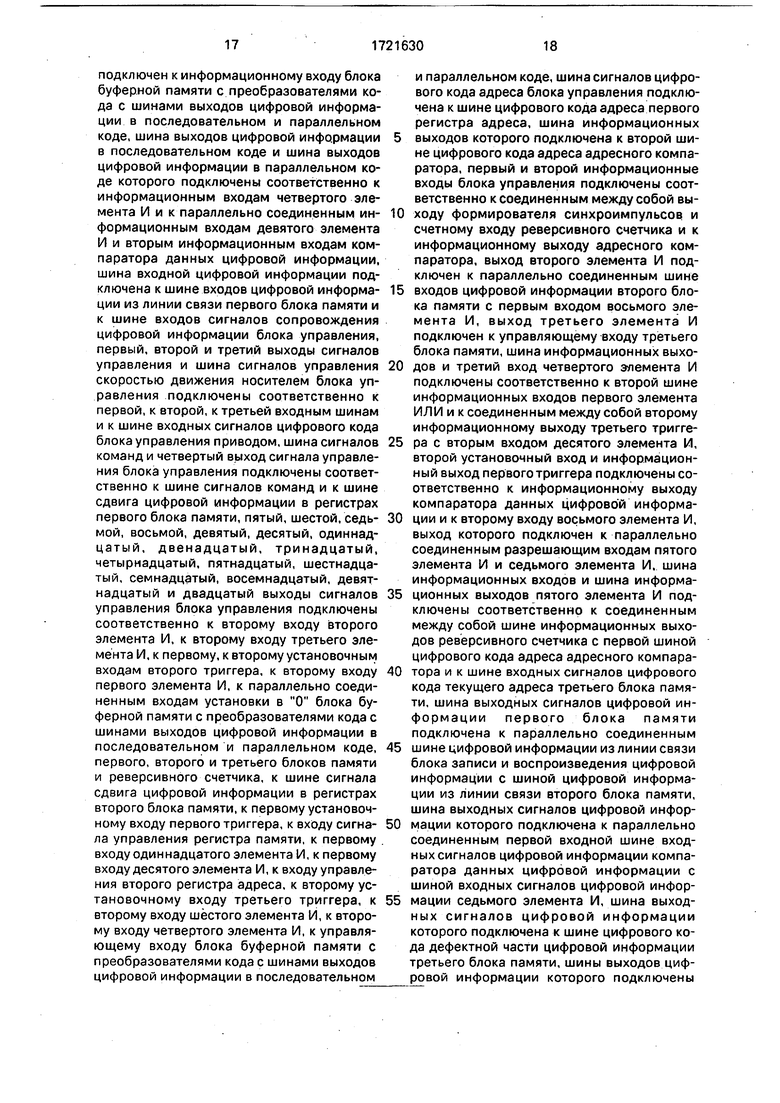

На фиг. 1 приведена структурная схема устройства записи-воспроизведения цифровой информации, реализующего предлагаемый способ; на фиг. 2 - структурная схема блоков первой и второй образцовой памяти с ограниченным объемом; на фиг. 3 - структурная схема блока третьей образцовой памяти с ограниченным объемом; на фиг. 4 - структурная схема блока управления; на фиг. 5 - структурная схема селектора сигналов; на фиг, 6 - структурная схема блока управления приводом.

Устройство записи-воспроизведения цифровой информации (фиг. 1) содержит накопитель 1 на подвижном носителе, блок 2 записи и воспроизведения цифровой информации (сопряженный с накопителем 1 на подвижном носителе), блок 3 буферной памяти с преобразователями кода с шинами выходов цифровой информации в последо- вательном и параллельном коде, первый 4, второй 5, третий 6, четвертый 7, пятый 8, шестой 9, седьмой 10, восьмой 11, девятый 12, десятый 13 и одиннадцатый 14 элементы И, первый 15 и второй 16 элементы ИЛИ, блоки первой 17, второй 18, третьей 19 образцовой памяти с ограниченным объемом, реверсивный счетчик 20, блок 21 управления, адресный компаратор 22, первый регистр 23 адреса, компаратор 24 данных цифровой информации, второй регистр 25 адреса, регистр 26 памяти, первый 27, второй 28 и третий 29 триггеры, селектор 30 сигналов, формирователь 31 импульсов, формирователь 32 синхроимпульсов, блок 33 управления приводом, шину 34 входной цифровой информации, шину 35 выходной цифровой информации в последовательном коде и шину 36 выходной цифровой информации в параллельном коде.

Выходы и входы накопителя 1 на подвижном носителе подключены и сопряжены к соответствующим входам и выходам блока 2 записи и воспроизведения, первый, второй,третий и четвертый выходы которо- го подключены соответственно к первому входу второго элемента И 5, к первому входу третьего элемента И 6, к первой входной шине селектора 30 сигналов и к входу формирователя 31 импульсов, выход которого подключен к первому входу первого элемента И 4, выход которого подключен к информационному входу блока 3 буферной памяти с преобразователями кода, с шинами выходов цифровой информации в последовательном и параллельном коде, шина выходов цифровой информации в последовательном коде и шина выходов цифровой информации в параллельном коде которого подключены соответственно к информационным входам четвертого элемента И 7 и к параллельно соединенным информационным входам девятого элемента И 12 и вторым информационным входам компаратора 24 данных цифровой информации. Шина 34 входной цифровой информации подключена к шине входов цифровой информации из линии связи блока 17 первой образцовой памяти с ограниченным объемом и к шине входов сигналов сопровождения цифровой информации блока 21 управления. Первый, второй и третий выходы сигналов управления и шина сигналов цифрового кода управления скоростью движения носителя блока 21 управления подключены соответственно к первой, второй, третьей входным шинам и к шине входных сигналов цифрового кода блока 33 управления приводом. Шина сигналов команд и четвертый выход сигнала управления блока 21 управления подключены соответственно к шине сигналов команд и к шине сдвига цифровой информации в регистрах блока 17 первой образцовой памяти с ограниченным объемом/Пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый,двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый и двадцатый выходы сигналов управления блока 21 управления подключены соответственно к второму входу второго элемента И 5, к второму входу третьего элемента И 6, к первому, к второму установочным входам второго триггера 28, к второму входу первого элемента И 4, к параллельно соединенным входам установки в О блока 3 буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде, блоков первой 17, второй 18 и третьей 19 образцовой памяти с ограниченными объемами и реверсивного счетчика 20, к шине сигнала сдвига цифровой информации в регистрах блока 18 второй образцовой памяти с ограниченным объемом, к первому установочному входу первого триггера 27, к выходу сигнала управления регистра 26 памяти, к первому входу одиннадцатого элемента И 14, к первому входу десятого элемента И 13, к входу управления второго регистра 25 адреса, к второму установочному входу третьего триггера 29, к второму входу шестого элемента И 9, к второму входу четвертого элемента И 7, к управляющему входу блока 3 буферной памяти с преобразователями кода с шинами.выходов цифровой информации в последовательном и параллельном коде. Шина сигналов цифрового кода адреса блока 21 управления подключена к шине цифрового кода адреса первого регистра 23 адреса, шина информационных выходов которого подключена к второй шине цифрового кода адреса адресного компаратора 22. Первый и второй информационные входы блока 21 управления подключены соответственно к соединенным между собой выходу формирователя 32 синхроимпульсов и счетному входу реверсивного счетчика 20 и к информационному выходу адресного компаратора 22, выход второго элемента И 5 подключен к параллельно соединенным шине входов цифровой информации блока 18 второй образцовой памяти с ограниченным объемом с первым входом восьмого элемента И 11, выход третьего элемента И 6 подключен к управляющему входу блока 19 третьей образцовой памяти с ограниченным объемом. Шина информационных выходов и третий вход четвертого элемента И 7 подключены соответственно к второй шине информационных входов первого элемента ИЛИ 15 и к соединенным между собой второму информационному выходу третьего триггера 29 с вторым входом десятого элемента И 13, второй установочный вход и информационный выход первого триггера 27 подключены соответственно к информационному выходу компаратора 24 данных цифровой информации и к второму входу восьмого элемента И 11, выход которого подключен к параллельно соединенным разрешающим входам пятого 8 и седьмого 10 элементов И. Шина информационных входов и шина информационных выходов пятого элемента И 8 подключены соответственно к соединенным между собой шине информационных выходов реверсивного счетчика 20 с первой шиной цифрового кода адреса адресного компаратора 22 и к шине входных сигналов цифрового кода текущего адреса блока 19 третьей образцовой памяти с ограниченным объемом. Шина выходных сигналов цифровой информации блока 17 первой образцовой памяти с ограниченным объемом подключена к параллельно соединенным шине цифровой информации из линии связи блока 2 записи и воспроизведения цифровой информации с шиной цифровой информации из линии связи блока 18 второй образцовой памяти с ограниченным объемом, шина выходных сигналов цифровой информации которого подключена к параллельно соединенным первой входной шине входных сигналов цифровой информации компаратора 24 данных цифровой информации с шиной входных сигналов цифровой информации седьмого элемента И 10, шина выходных сигналов цифровой инфор- 5 мации которого подключена к шине цифрового кода дефектной части цифровой информации блока 19 третьей образцовой памяти с ограниченным объемом, шины выходов цифровой информации которого под0 ключены соответственно к шине цифрового кода адреса второго регистра 25 адреса и к шине входных сигналов цифровой информации регистра 26 памяти, шина сигналов цифровой информации которого подключена к

5 параллельно соединенным шине входных цифровых сигналов шестого элемента И 9 с шиной входных цифровых сигналов одиннадцатого элемента И 14, шина выходных цифровых сигналов которого подключена к

0 второй шине входных сигналов цифровой информации второго элемента ИЛИ 16. Выход десятого элемента И 13 подключен к входу сигнала разрешения девятого элемента И 12, шина выходных цифровых сигналов

5 которого подключена к первой шине входных сигналов цифровой информации второго элемента ИЛИ 16, шина выходных сигналов цифровой информации которого подключена к второй шине 36 выходной

0 цифровой информации в параллельном коде. Шина выходов сигналов цифрового кода адреса второго регистра 25 адреса подключена к третьей шине сигналов цифрового кода адреса адресного компаратора 22, ши5 на выходных цифровых сигналов шестого элемента И 9 подключена к первой шине информационных входов первого элемента ИЛИ 15, шина выходных сигналов цифровой информации которого подключена к первой

0 шине 35 выходной цифровой информации в последовательном коде, первый и второй информационные выходы второго триггера 28 подключены соответственно к параллельно соединенным входу прямого счета

5 реверсивного счетчика 20 с вторым входом селектора 30 сигналов и к параллельно соединенным входу обратного счета реверсивного счетчика 20 с третьим входом селектора 30 сигналов. Выход селектора 30

0 сигналов подключен к входу формирователя 32 синхроимпульсов.

Блок 17 первой образцовой памяти с ограниченным объемом содержит регистры 37-39 сдвига, элементы И 40-48 записи

5 цифровой информации в регистры сдвига, элементы И 49-51 разрешения выхода цифровой информации, элементы ИЛИ 52-54, шину 55 входов цифровой информации из линии связи, шину 56 сдвига цифровой информации в регистрах, шину 57 входов цифровой информации с блока управления, шину 58 установки в О регистров сдвига и шину 59 выходных сигналов цифровой информации. Входная цифровая информация из линии связи подается на один из входов элементов И 40-48 и 49-51. а сигналы сопровождения - в блок 21 управления. Последний анализирует полученную информацию и выдает разрешающие сигналы на другие входы тех элементов И 40-48, которые связаны с первой свободной ячейкой памяти (на триггерах регистров сдвига). Например, если свободна только последняя ячейка, то разрешающие сигналы с блока 21 управления подаются на элементы И 40, 43 и 46. Если свободны все ячейки и осуществляется режим контроля записанной на носитель информации (режим считывания), то разрешающие сигналы подаются на входы элементов И 42, 45 и 48. При этом входная информация записывается в первую свободную ячейку памяти. Если свободны все ячейки и осуществляется режим записи информации на носитель, то разрешающие сигналы подаются на входы элементов И 49-51. При этом входная информация проходит транзитом на выход устройства через элемент ИЛИ 53. В режиме записи осуществляется считывание записанной в блоке памяти информации путем подачи сигналов на шину 56 сдвига информации, запомненной в регистрах памяти. С подачей каждого сигнала на шину 56 осуществляется сдвиг на один разряд информации в регистрах памяти и выдача информации на выход через элемент ИЛИ 53 из старших разрядов регистров сдвига.

Блок 18 второй образцовой памяти с ограниченным объемом аналогичен по своей структуре и принципу работы блоку 17 первой образцовой памяти с ограниченным объемом. Отличие заключается лишь в том, что выдача информации из данного блока памяти осуществляется по принципу стековой памяти. При этом цифровая информация, записанная последней, выдается первой. Соответствующее управление осуществляется с блока 21 управления.

Блок 19 третьей образцовой памяти с ограниченным объемом содержит реверсивный счетчик 60, дешифратор 61 адреса, матрицу 62 элементов памяти, шины записи 63 и считывания 64, шины выходных 65 и входных 66 сигналов, шину 67 сигналов управления. Специфической особенностью данного блока памяти является то, что формирование адреса осуществляется в самом блоке, а не задается извне. В режиме записи информации входной сигнал записи с шины 63 подается на прямой вход реверсивного счетчика 60, увеличивая его содержимое на единицу. Одновременно сигнал записи подается на вход установки режима записи в матрице 62 элементов памяти, При этом

адрес с выхода реверсивного счетчика 60 дешифрируется с помощью дешифратора 61 и действующая на шине 66 входная информация записывается в матрицу 62 по адресу, задаваемому с реверсивного счетчика 60. В

0 режиме считывания информации входной сигнал считывания с шины 64 подается на обратный вход реверсивного счетчика 60, уменьшая его содержимое на единицу. Одновременно сигнал считывания подается на

5 вход установки режима считывания в матрице 62 элементов памяти. При этом с выхода реверсивного счетчика 60 информация дешифрируется с помощью дешифратора 61 и по заданному адресу считывается из матрицы

0 62 элементов памяти на выходную шину 65. Блок 21 управления содержит микро- ЭВМ 67, шинный формирователь 68, регистр 69, дешифратор 70, шины информации 71 и управления 72, шины 73 и

5 74 установки, входную информационную шину 75 регистра, шину 76 подачи сигналов на входы дешифратора, шины 77-79 подачи сигналов на входы регистра и шины 80-82 выходной информации дешифратора.

0 Блок 21 управления работает следующим образом.

В блоке реализуется программное управление. Программа заложена в постоянном запоминающем устройстве (ПЗУ),

5 входящем в состав микроЭВМ 67. Шинный формирователь 68 обеспечивает двухсторонний обмен информацией между микро- ЭВМ 67, регистром 69 и дешифратором 70. Выходная информация вырабатывается на

0 выходах дешифратора 70, связанных с выходными шинами 80-82. В режиме приема информации микроЭВМ 67 вырабатывает на шине 72 сигналы управления, отпирающие шинный формирователь 68 и регистр

5 69, а также сигнал записи, устанавливающий шинный формирователь 68 в режим передачи информации от регистра 69 к микроЭВМ 67. В режиме приема информации сигналы с шины 75 передаются через шин0 ный формирователь 68 на информационную шину 7.1 и далее в микроЭВМ 67. МикроЭВМ 67 анализирует полученную информацию и в зависимости от результата анализа вырабатывает соответствующие выходные сиг5 налы. В режиме выдачи информации микроЭВМ 67 вырабатывает на шине 72 сигналы управления, отпирающие шинный формирователь 68 и дешифратор 70, а также сигнал чтения, устанавливающий шинный формирователь 68 в режим передачи информации от микроЭВМ 67 к дешифратору 70. В режиме выдачи информации сигналы с информационной шины 71 передаются через шинный формирователь 68 на шину 76, связанную с входами дешифратора 70. При этом на соответствующем выходе дешифратора 70 вырабатывается сигнал, адэкватный информации, действующей на его входах. Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый и двадцатый выходы сигналов управления, выходы шины сигналов цифрового кода управления скоростью движения носителя, выходы шины цифровой информации и команд и выходы шины сигналов цифрового кода адреса блока 21 управления подключены соответственно к выходным шинам 80-82 (в общем случае с шин) блока 21 управления. Первый и второй информационные входы шины сигналов сопровождения блока 21 управления подключены соответственно к входным шинам 77-79 (в общем случае р шин) блока 21 управления.

Селектор 30 сигналов содержит первую 87, вторую 88 и третью 89 входные шины, элемент НЕ 83, первый 84 и второй 85 элементы И, элемент ИЛИ 86 и выходную шину 90, причем первая входная шина 87 подключена к первому входу первого элемента И 84 и к входу элемента НЕ 83, выход которого подключен к первому входу второго элемента И 85, вторая входная шина 88 подключена к второму входу первого элемента И 84, выход которого подключен к первому входу элемента ИЛИ 86, третья входная шина 89 подключена к второму входу второго элемента И 85, выход которого подключен к второму входу элемента ИЛИ 86, выход которого подключен к выходной шине 90.

Блок 33 управления приводом содержит входные шины 102-104 управляющих сигналов, входные шины 105-107 сигналов цифрового кода (в общем случае m шин разрядов цифрового кода), элемент ИЛИ 91, триггер 94, первый 92 и второй 93 элементы И, цифроаналоговый преобразователь 95, первый 96 и второй 97 коммутируемые стабилизаторы напряжения, первый 98 и второй 99 усилитель, первый 100 и второй 101 электродвигатели, причем шина 102 сигнала управления подключена к первому входу триггера 94, шина 103 сигнала управления подключена к первому входу элемента ИЛИ 91 и к второму входу первого элемента И 92, шина 104 сигнала управления подключена к второму входу элемента ИЛИ 91 и к второму

входу второго элемента И 93, входные шины 105-107 - к первому, второму и к третьему (в общем случае к m-му) информационным входам цифроаналогового преобразователя 5 95. Выход элемента ИЛИ 91 подключен к второму входу триггера 94, выход которого подключен к первым входам первого 92 и второго 93 элементов И. Выход первого элемента И 92 подключен к управляющему вхо0 ду первого коммутируемого стабилизатора 96 напряжения, выход которого подключен к шине питания первого усилителя 98. Выход второго элемента И 93 подключен к управляющему входу второго коммутируемого

5 стабилизатора 97 напряжения, выход которого подключен к шине питания второго усилителя 99. Выход цифроаналогового преобразователя 95 подключен к входам первого 98 и второго 99 усилителей, а первый

0 электродвигатель 100 прямой перемотки магнитной ленты носителя и второй электродвигатель 101 обратной перемотки магнитной ленты носителя подключены соответственно к выходам первого усилите5 ля 98 и к выходам второго усилителя 99.

Блок 3 буферной памяти с преобразователями кода реализуется на основе регистра сдвига. Цифровая информация с носителя запоминается в нем и при необходимости

0 выдачи в последовательном коде сдвигается при подаче соответствующих сигналов с блока 21 управления. При выдаче цифровой информации в параллельном коде сдвиг не производится. Цифровые сигналы в парал5 лельном и последовательном коде поступают на выход блока соответственно через шину выходов сигналов в параллельном коде и через шину выходов сигналов в последовательном коде.

0 Адресный компаратор 22 и компаратор 24 данных цифровой информации реализуется на основе двух регистров памяти и двух групп элементов И, подключенных соответственно к единичным и нулевым выходам

5 триггеров регистров памяти, а выходами - к входам элементов ИЛИ.

Устройство записи-воспроизведения цифровой информации работает следующим образом.

0 Предварительно сигналом установки в О, поступающим с десятого выхода блока 21 управления, производят подготовку к работе блока 3 буферной памяти с преобразователями кода, реверсивного счетчика 20 и

5 блоков первой 17, второй 18 и третьей 19 образцовой памяти с ограниченным объемом.

Режим периодического чередования записи и воспроизведения задается сигналами соответственно с первого, второго и

третьего выходов блока 21 управления, подаваемыми на шины 102-104 сигналов управления блока 33 управления приводом. При этом также с выходной шины сигналов цифрового кода блока 21 управления посту- лают на шины 105-107 блока 33 управления приводом соответствующие сигналы цифрового кода управления скоростью движения носителя, а с седьмого и восьмого выходов блока 21 управления поступают на первый и второй установочные входы второго триггера 28 и соответственно на входы прямого и обратного счета реверсивного счетчика 20 и на вторую 88 и третью 89 входные шины селектора сигналов, соответствующие уста- новленному режиму, сигналы управления. Входная цифровая информация с сигналами сопровождения из линии связи с входной шины 34 подается на вход блока 17 первой образцовой памяти с ограниченным объемом. При этом сигналы сопровождения подаются на входную шину блока 21 управления. В памяти блока управления в каждый данный момент вырабатывается запись входной цифровой информации. Если ни од- на ячейка в памяти блока 17 не заполнена, то входная цифровая информация (в режиме воспроизведения) записывается в первую ячейку, следующая - во вторую и так далее, а в режиме записи проходит на выход блока 17. В начальный момент работы устройства осуществляется режим записи. При этом входная цифровая информация проходит с входной шины 34 через блок 17 первой образцовой памяти транзитом (поскольку ни одна ячейка в памяти блока 17 не заполнена) на вход блока 2 записи и воспроизведения, откуда осуществляется запись ее на накопитель 1, и на вход блока 18 второй образцовой памяти с ограниченным объе- мом, где производится запись текущей цифровой информации в режиме записи устройства. Одновременно в этом режиме осуществляется подсчет реверсивным счетчиком 20 синхроимпульсов, поступающих на его счетный вход с выхода блока 2 записи и воспроизведения. При этом на информационных выходах реверсивного счетчика 20 воспроизводится текущий адрес части цифровой информации, записываемой в на ко- питель 1 на движущемся носителе.

Таким образом, в режиме записи осуществляется запись входной цифровой информации на носитель и одновременно эта же информация записывается в блок 18 второй образцовой памяти с ограниченным объемом. Режим записи осуществляется до момента достижения равенства кода адреса с реверсивного счетчика 20 коду адреса, выставленного с блока 21 управления в первом

регистре 23 адреса. При совпадении цифровых кодов адресов с выходов реверсивного счетчика 20 и регистра 23 адреса на выходе адресного компаратора 22 вырабатывается сигнал, подаваемый на второй информационный вход блока 21 управления.

При этом блок 21 управления вырабатывает соответствующий сигнал реверса, подаваемый на соответствующую шину сигнала управления блока 33 управления приводом, в результате чего начинает осуществляться режим воспроизведения. Наряду с этим с блока 21 управления выставляется в первом регистре 23 адреса код адреса, до которого осуществляется режим воспроизведения. В данном режиме входная цифровая информация записывается в блок 17 первой образцовой памяти с ограниченным объемом, а информация, записанная в накопитель 1 на подвижном носителе, считывается, осуществляется промежуточное запоминание ее частей в блоке 3 буферной памяти с преобразователями кода и с помощью компаратора 24 данных цифровой информации - поразрядное сравнение с идентичной информацией, считываемой из блока 18 второй образцовой памяти с ограниченным объемом. При несовпадении на выходе элемента И 10 выра- батывается сигнал, по которому несовпавшая информация из блока 18 второй образцовой памяти с ограниченным объемом записывается в блок 19 третьей образцовой памяти вместе с текущим адресом (через элемент И 8), зафиксированным в данный момент на реверсивном счетчике 20. Режим воспроизведения осуществляется до момента совпадения кода с информационных выходов реверсивного счетчика 20 с кодом, выставленным с блока 21 управления. При этом на выходе адресного компаратора 22 вырабатывается сигнал, подаваемый через блок 21 управления на блок 33 управления приводом. Кроме того, блок 21 управления выставляет код адреса. При этом блок 33 управления приводом осуществляет реверс и форсированный режим перемотки магнитной ленты накопителя 1 до момента совпадения кода с реверсивного счетчика 20 и кода, выставленного с блока 21 управления. При этом по сигналу с адресного компаратора 22 блок 21 управления вырабатывает сигнал на блок 33 управления приводом, по которому прекращается форсированный режим перемотки магнитной ленты накопителя 1 и начинается следующий цикл нормальной записи входной цифровой информации в накопитель 1 на подвижном носителе. При этом блок 21 управления выставляет адрес, до которого

должен осуществляться данный режим записи. В момент достижения равенства кода адреса с реверсивного счетчика 20 и кода адреса, выставленного с блока 21 управления, на выходе адресного компаратора 22 вырабатывается сигнал, подаваемый на блок 21 управления. Далее процесс идет аналогично описанному, но входная цифровая информация записывается в накопитель 1 и блок 18 второй образцовой памяти.

При окончательном воспроизведении записанной в накопителе 1 на подвижном носителе информации описанным способом с блока 21 управления на блок 33 управления приводом подается соответствующий сигнал управления, выставляется конечный адрес считывания и подаются соответствующие сигналы управления на реверсивный счетчик 20, селектор 30 сигнала и на блоки первой 17, второй 18 и третьей 19 образцовой памяти с ограниченным объемом. При этом реверсивный счетчик 20 должен считать в обратном направлении, первая 17 и вторая 18 образцовые памяти блоков отключаются, а блок 19 третьей образцовой памяти работает в режиме считывания записанной в нее цифровой информации. При этом, если при считывании отсутствует совпадение адресной информации с реверсивного счетчика 20 и из блока 19 третьей образцовой памяти, то цифровая информация проходит с накопителя 1 на подвижном носителе через блок 2 записи и воспроизведения и блок 3 буферной памяти с преобразователями кода соответственно через четвертый элемент И 7 и первый элемент ИЛИ 15 на выходную шину 35 устройства в последовательном коде, а через девятый элемент И 12 и второй элемент ИЛИ 16 на выходную шину 36 устройства в параллельном коде.

При совпадении же упомянутой адресной информации на выходные шины 35 и 36 устройства цифровая информация проходит из блока 19 третьей образцовой памяти с ограниченным объемом через регистр 26 памяти и соответственно через шестой элемент И 9 и первый элемент ИЛИ 15 в последовательном коде, а через одиннадцатый элемент И 14 и второй элемент ИЛИ 16 - в параллельном коде.

Формула изобретения 1. Способ записи-воспроизведения цифровой информации, заключающийся в записи по частям цифровой информации, промежуточном запоминании воспроизводимой части цифровой информации, контроле ее по частям и замене дефектной части при обнаружении ошибки, отличающийс я тем, что, с целью повышения точности записи-воспроизведения, запись массивов частей цифровой информации на носитель производят одновременно с их запоминанием и поочередно с промежуточным воспроизведением, в процессе которого при промежуточном запоминании контроль осуществляют путем поразрядного сравнения с одноименной запомненной частью в про0 цессе записи на носитель, при несовпадении запомненную часть информации маркируют адресом контролируемой информации с .носителя и дополнительно запоминают полученную информацию,

5 используя ее для замены в соответствии с адресом дефектной части в процессе окончательного воспроизведения информации с носителя, осуществляя это воспроизведение одновременно с запоминанием исход0 ной цифровой информации.

2. Устройство для записи-воспроизведения цифровой информации, содержащее накопитель на подвижном носителе, блок записи и воспроизведения цифровой ин5 формации, сопряженный с накопителем, блок буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде, первый, второй, третий, четвертый, пя0 тый и шестой элементы И, первый элемент ИЛИ, первая и вторая шины информационных входов которого подключены соответст- венно к информационным выходам четвертого элемента И и к информацион5 ным выходам шестого элемента И, о т л и- чэющееся тем, что, с целью повышения точности записи воспроизведения, в него введены первый, второй и третий блоки памяти, реверсивный счетчик, компаратор

0 данных цифровой информации, адресный компаратор, блок управления, первый регистр адреса, второй регистр адреса, регистр памяти, седьмой, восьмой, девятый, десятый и одиннадцатый элементы И, вто5 рой элемент ИЛИ, первый, второй и третий триггеры, селектор сигналов, формирователь импульсов, формирователь синхроимпульсов, блок управления приводом, шина входной цифровой информации, шина вы0 ходной цифровой информации в последовательном коде и шина выходной цифровой информации в параллельном коде, причем первый, второй, третий и четвертый выходы блока записи и воспроизведения подключе5 ны соответственно к первому входу второго элемента И, к первому входу третьего элемента И, к первой входной шине селектора сигналов и к входу формирователя импульсов, выход которого подключен к первому входу первого элемента И, выход которого

подключен к информационному входу блока буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде, шина выходов цифровой информации в последовательном коде и шина выходов цифровой информации в параллельном коде которого подключены соответственно к информационным входам четвертого элемента И и к параллельно соединенным информационным входам девятого элемента И и вторым информационным входам компаратора данных цифровой информации, шина входной цифровой информации подключена к шине входов цифровой информации из линии связи первого блока памяти и к шине входов сигналов сопровождения цифровой информации блока управления, первый, второй и третий выходы сигналов управления и шина сигналов управления скоростью движения носителем блока управления подключены соответственно к первой, к второй, к третьей входным шинам и к шине входных сигналов цифрового кода блока управления приводом, шина сигналов команд и четвертый выход сигнала управления блока управления подключены соответственно к шине сигналов команд и к шине сдвига цифровой информации в регистрах первого блока памяти, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый и двадцатый выходы сигналов управления блока управления подключены соответственно к второму входу второго элемента И, к второму входу третьего элемента И. к первому, к второму установочным входам второго триггера, к второму входу первого элемента И, к параллельно соединенным входам установки в О блока буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде, первого, второго и третьего блоков памяти и реверсивного счетчика, к шине сигнала сдвига цифровой информации в регистрах второго блока памяти, к первому установочному входу первого триггера, к входу сигнала управления регистра памяти, к первому входу одиннадцатого элемента И, к первому входу десятого элемента И, к входу управления второго регистра адреса, к второму установочному входу третьего триггера, к второму входу шестого элемента И, к второму входу четвертого элемента И, к управляющему входу блока буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном

и параллельном коде, шина сигналов цифрового кода адреса блока управления подключена к шине цифрового кода адреса первого регистра адреса, шина информационных

выходов которого подключена к второй шине цифрового кода адреса адресного компаратора, первый и второй информационные входы блока управления подключены соответственно к соединенным между собой вы0 ходу формирователя синхроимпульсов и счетному входу реверсивного счетчика и к информационному выходу адресного компаратора, выход второго элемента И подключен к параллельно соединенным шине

5 входов цифровой информации второго блока памяти с первым входом восьмого элемента И, выход третьего элемента И подключен к управляющему входу третьего блока памяти, шина информационных выхо0 дов и третий вход четвертого элемента И подключены соответственно к второй шине информационных входов первого элемента ИЛИ и к соединенным между собой второму информационному выходу третьего тригге5 ра с вторым входом десятого элемента И, второй установочный вход и информационный выход первого триггера подключены соответственно к информационному выходу компаратора данных цифровой информа0 ции и к второму входу восьмого элемента И, выход которого подключен к параллельно соединенным разрешающим входам пятого элемента И и седьмого элемента И, шина информационных входов и шина информа5 ционных выходов пятого элемента И подключены соответственно к соединенным между собой шине информационных выходов реверсивного счетчика с первой шиной цифрового кода адреса адресного компара0 тора и к шине входных сигналов цифрового кода текущего адреса третьего блока памяти, шина выходных сигналов цифровой информации первого блока памяти подключена к параллельно соединенным

5 шине цифровой информации из линии связи блока записи и воспроизведения цифровой информации с шиной цифровой информации из линии связи второго блока памяти, шина выходных сигналов цифровой инфор0 мации которого подключена к параллельно соединенным первой входной шине входных сигналов цифровой информации компаратора данных цифровой информации с шиной входных сигналов цифровой инфор5 мации седьмого элемента И, шина выходных сигналов цифровой информации которого подключена к шине цифрового кода дефектной части цифровой информации третьего блока памяти, шины выходов цифровой информации которого подключены

19

соответственно к шине цифрового кода адреса второго регистра адреса и к шине входных сигналов цифровой информации регистра памяти, шина сигналов цифровой информации которого подключена к параллельно соединенным шине входных цифровых сигналов шестого элемента И с шиной входных цифровых сигналов одиннадцатого элемента И, шина выходных цифровых сигналов которого подключена к второй шине входных сигналов цифровой информации второго элемента ИЛИ, выход десятого элемента И подключен к входу сигнала разрешения девятого элемента И, шина выходных цифровых сигналов которого подключена к первой шине входных сигналов цифровой информации второго элемента ИЛИ, шина выходных сигналов цифровой информации которого подключена к второй шине выходной цифровой информации в параллельном

1721630

20

коде, шина выходов сигналов цифрового кода адреса второго регистра адреса подключена к третьей шине сигналов цифрового кода адреса адресного компаратора, шина выходных цифровых сигналов шестого элемента И подключена к первой шине информационных входов первого элемента ИЛИ, шина выходных сигналов цифровой информации которого подключена к первой шине выходной цифровой информации в последовательном коде, первый и второй информа- ционные выходы второго триггера подключены соответственно к параллельно соединенным входу прямого счета реверсивного счетчика с вторым входом селектора сигналов и к параллельно соединенным входу обратного счета реверсивного счетчика с третьим входом селектора сигналов, выход селектора сигналов подключен к входу формирователя синхроимпульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2039382C1 |

| Устройство для поиска зон информации на магнитном носителе | 1989 |

|

SU1644217A1 |

| Устройство для поиска зон информации на магнитном носителе | 1989 |

|

SU1712961A1 |

| Устройство для поиска зон информации на магнитном носителе | 1990 |

|

SU1780107A1 |

| Устройство цифровой магнитной записи и воспроизведения | 1981 |

|

SU1030844A1 |

| Устройство магнитной записи и воспроизведения | 1980 |

|

SU902057A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

Изобретение относится к технике накопления цифровой информации и может быть использовано в аппаратуре записи, хранения и воспроизведения цифровой информации. Целью изобретения является повышение точности записи-воспроизведения цифровой информации. Поставленная цель достигается тем, что в предлагаемом способе записи-воспроизведения цифровой информации, заключающемся в записи по частям цифровой информации, промежуточном запоминании воспроизводимой части цифровой информации, контроле ее по частям и замене дефектной части при обнаружении ошибки, запись массивов частей цифровой информации на носитель производят одновременно с их запоминанием и поочередно с промежуточным воспроизведением, в процессе которого при промежуточном запоминании контроль осуществляют путем поразрядного сравнения с одноименной запомненной частью в процессе записи на носитель. При несовпадении запомненную часть информации маркируют адресом контролируемой информации с носителя и дополнительно запоминают полученную информацию, используя ее для замены в соответствии с адресом дефектной части в процессе окончательного воспроизведения информации с носителя, осуществляя это восроизведение одновременного с запоминанием исходной цифровой информации. 2 с. п. ф-лы, 6 ил. k/ 1C

Фиг.1

39

57 Фиг. 2

Установка в О

«w

Ц

5А

3

С

2

4

&&

Ј-Э

f02

75

77 Ъ

69

76

:

60

61

70

с

А2

ФигЛ

64

1

45

Ф/г. 5

i03

104 I f05

i06

JO

| Способ контроля аппарата магнитной записи и устройство для его осуществления | 1985 |

|

SU1324065A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Коган Б | |||

| М | |||

| и др | |||

| Запоминающие устройства большой емкости | |||

| - М,: Энергия, 1968, с | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Патент США N 3569934 | |||

| кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Способ записи и воспроизведения цифровой информации | 1981 |

|

SU1001166A1 |

Авторы

Даты

1992-03-23—Публикация

1990-01-09—Подача