Изобретение относится к вычислительной технике и может найти применение при создании центральных процессоров, например, для формирования и считывания адреса следующей микрокоманды.

Целью изобретения является повышение быстродействия устройства.

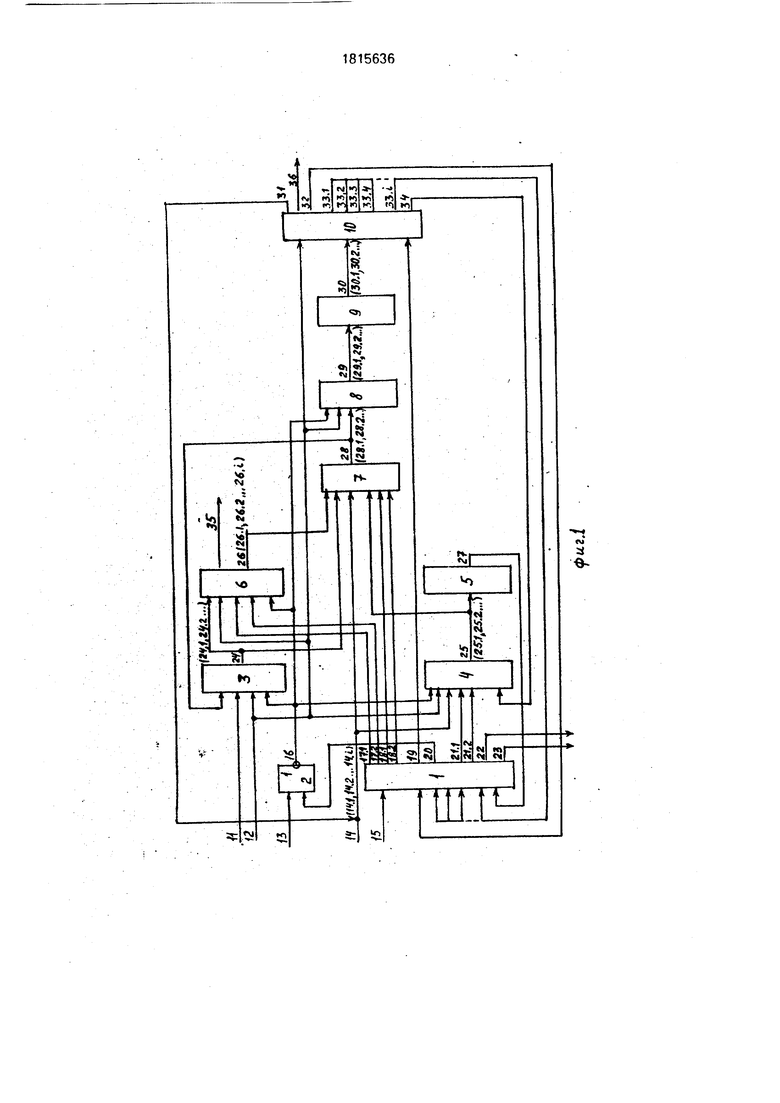

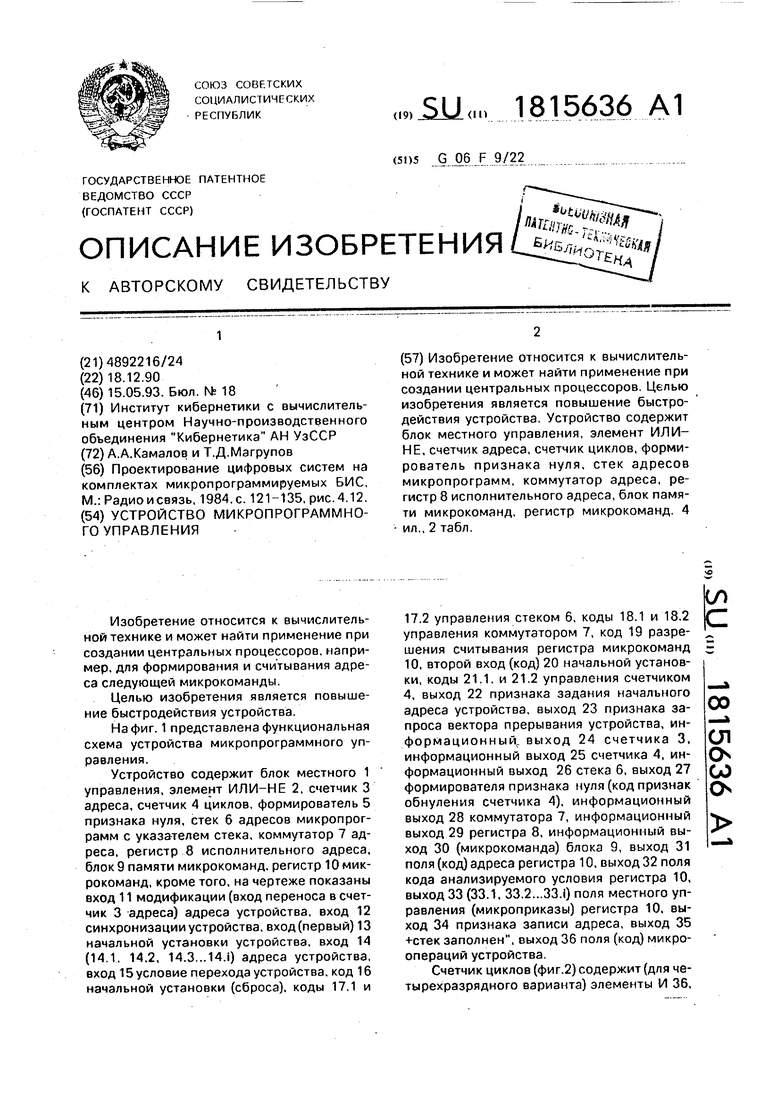

На фиг. 1 представлена функциональная схема устройства микропрограммного управления.

Устройство содержит блок местного 1 управления, элемент ИЛИ-НЕ 2, счетчик 3 адреса, счетчик 4 циклов, формирователь 5 признака нуля, стек 6 адресов микропрограмм с указателем стека, коммутатор 7 адреса, регистр 8 исполнительного адреса, блок 9 памяти микрокоманд, регистр 10 микрокоманд, кроме того, на чертеже показаны вход 11 модификации (вход переноса в счетчик 3 адреса) адреса устройства, вход 12 синхронизации устройства, вход (первый) 13 начальной установки устройства, вход 14 (14.1. 14.2, 14.3...14.1) адреса устройства, вход 15 условие перехода устройства, код 16 начальной установки (сброса), коды 17.1 и

17.2 управления стеком 6, коды 18.1 и 18.2 управления коммутатором 7, код 19 разрешения считывания регистра микрокоманд 10, второй вход (код) 20 начальной установки, коды 21.1. и 21.2 управления счетчиком 4, выход 22 признака задания начального адреса устройства, выход 23 признака запроса вектора прерывания устройства, ин- формационныйс выход 24 счетчика 3, информационный выход 25 счетчика 4, информационный выход 26 стека 6, выход 27 формирователя признака нуля (код признак обнуления счетчика 4), информационный выход 28 коммутатора 7, информационный выход 29 регистра 8, информационный выход 30 (микрокоманда) блока 9, выход 31 поля (код) адреса регистра 10, выход 32 поля кода анализируемого условия регистра 10, выход 33 (33.1, 33.2...33.0 поля местного управления (микроприказы) регистра 10. выход 34 признака записи адреса, выход 35 +стек заполнен, выход 36 поля (код) микроопераций устройства.

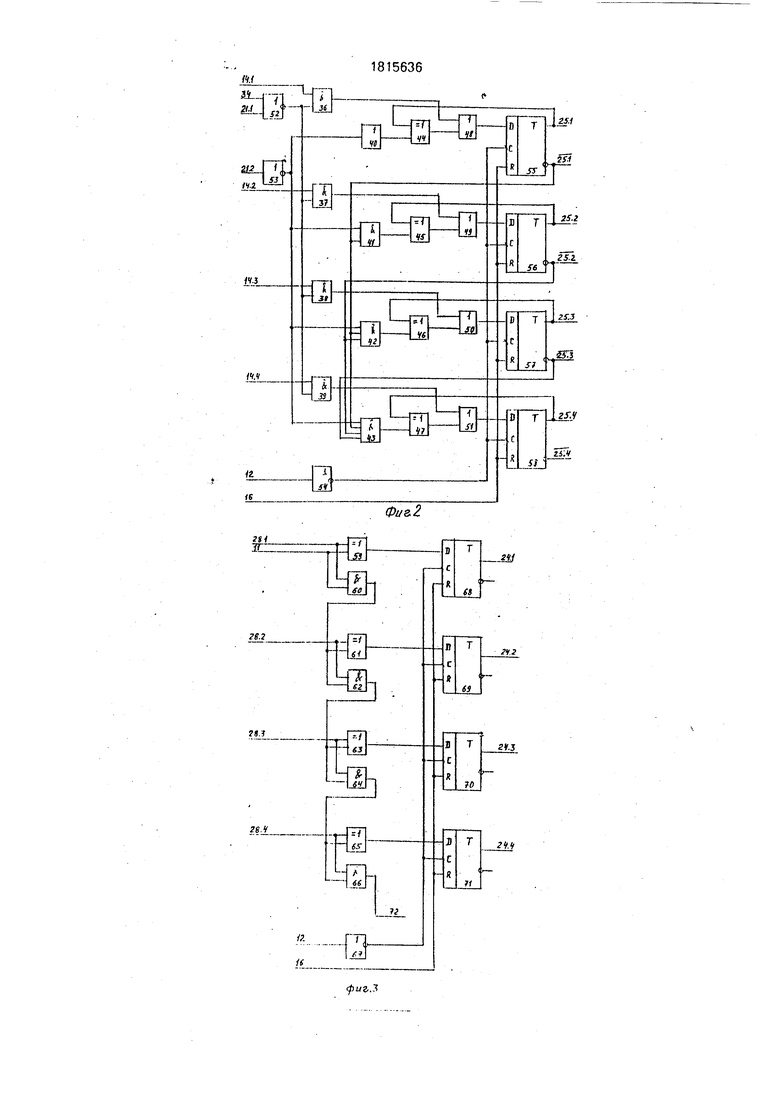

Счетчик циклов (фиг.2) содержит (для четырехразрядного варианта) элементы И 36,

ел

с

оо

ел о

00

о

37, 38, 39, 41, 42, 43, элементы исключающие ИЛИ 44, 45, 46, 47, элементы ИЛИ 40, 48,49,50, 51, триггера 55, 56,57,58, элементы ИЛИ-НЕ 52, 53, 54, входы данных 14.1, 14.2, 14.3, 14,4, входы 21.1 и 34 признака записи адреса в счетчик, вход признака считывания адреса 21.2, вход синхронизации 12, вход начальной установки 16, прямые выходы триггеров 25.1, 25.2.25..4.06- ратные выходы триггеров, 25.1, 25.2, 25.3 и 25.4.

Счетчик адреса (фиг.З) содержит (для четырехразрядного варианта) элементы исключающие ИЛИ 59, 61, 63, 65, элементы И 60, 62, 64, 66, D-триггера 68, 69, 70, 71 (68 - младший разряд, 71 - старший разряд), информационные входы 28.1, 28.2, 28.3, 28.4, вход переноса 11, (модификации адреса), выход переноса 72, синхровход 12, вход начальной установки 16,информационные выходы счетчика адреса 24.1, 24.2, 24.3, 24.4.

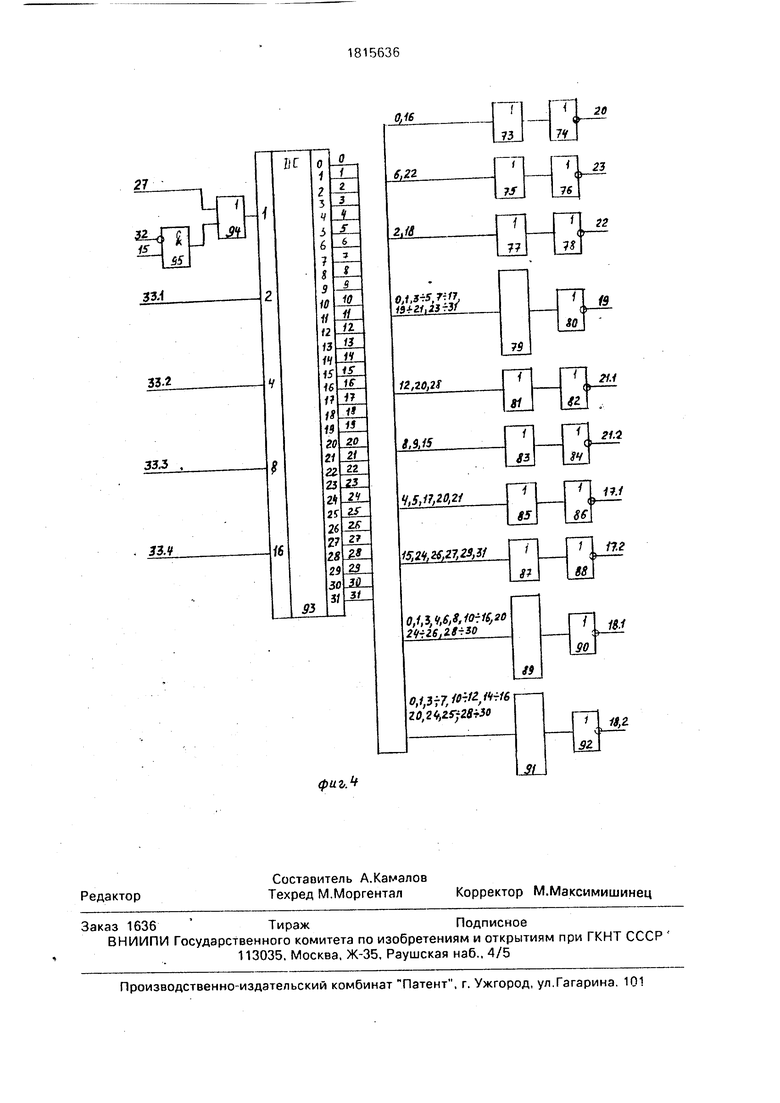

Блок местного управления (фиг.4) для четырехразрядного кода микрокоманды содержит элементы ИЛИ 73, 75, 77, 81, 83, 85, 87, 94, группы элементов ИЛИ 79, 89, 91, элемент И 95, элементы ИЛИ-НЕ 74, 76, 78, 80,82,84,86,88,90,92, дешифратор 93. вход (код) 27 признака обнуления счетчика 4. вход 32 кода анализируемого условия, вход (код) 15условие перехода устройства, входы (коды) 33.1, 33.2. 33.3, 33.4 поля местного управления (микроприказы), выход (код) 20 начальной установки, выходы (коды) 32-1.1.и 21.2 управления счетчиком 4, выход (код) 22 признак задания начального адреса, выход (код) 23 признак запроса вектора прерывания, выход (код) 19 разрешения считывания регистра микрокоманд 10, выходы (коды) 17.1 и 17.2 управления стеком 6. выходы (коды) 18.1 и 18.2 управления коммутатором 7.

Регистр 8 исполнительного адреса построен как типовой регистр.

Нумерация элементов, внешних входов и выходов счетчика циклов, счетчика адреса и блока местного управления проделана с учетом нумераций блоков, входов и выходов устройства микропрограммного управления (см.фиг. 1, фиг,2, фиг.З, фиг.4 совместно).

Устройство работает следующим образом.

Каждая микрокоманда, хранящаяся в блоке 9 памяти микрокоманд содержит адресную и управляющую часть. Адресная часть микрокоманды содержит код 31 адреса следующей микрокоманды. Управляющая часть микрокоманды содержит кодовую последовательность 33.1, 33,2, 33.1...33.1 микроприказа, которые выдаются при выполнении текущей микрокоманды в виде кодовой комбинации, код 32 анализируемого условия, код 34 признака записи адреса в счетчик 4 циклов и код 36 управления микроопераций.

Работу устройства можно условно разделить на два этапа и средства: первый (основной) этап и средства - формирование адреса следующей микрокоманды, второй этап и средства - хранение исполнительного адреса, хранение и считывание микрокоманды.

Рассмотрим этап формирования адреса следующей микрокоманды. Адрес формируется из двух источников: внутренних и

5 внешних.

Внутренними источниками являются: регистр 10 микрокоманд, счетчик 3 адреса, счетчик 4 циклов, стек 6 адресов микропрограмм. Внешними источниками могут быть

0 дешифратор начального адреса и дешифратор векторов прерывания.

Рассмотрим назначение средств формирования адреса следующей микрокоманды.

5Блок местного управления построен как логическая матрица. Блок 1 местного управления (для четырехразрядного кода микрокоманды) при кодовой комбинации 33.1, 33,2, 33.3 и 33.4 микроприказов, кода 15,

0 кода 27 и кода 32 вырабатывает одновременно управляющие коды: коды 17.1, 17.2 управления стеком 6, коды 18.1 и 18.2 управления коммутатором 7, коды 21.1 и 21.2 управления счетчиком 4, код 20 начальной

5 установки и один из трех кодов: 19 (разрешения считывания регистра 10), 23 (признак запроса вектора прерывания), 22 (признак задания начального адреса).

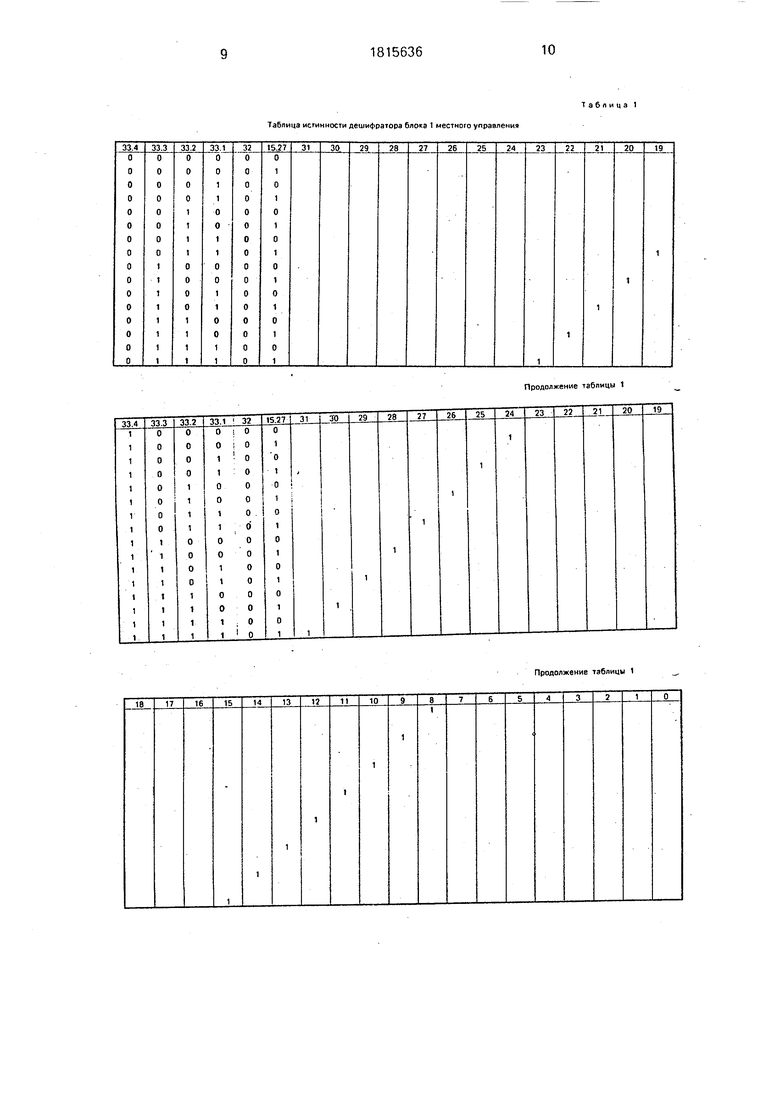

Ниже приводятся табл.1 и 2 истинности

0 дешифратора блока местного управления и данного блока местного управления для.случая четырехразрядного кода микрокоманды.

Счетчик циклов работает в следующих

5 режимах: режим записи данных (записываемыми данными могут быть адреса или количество циклов) на вход 21.1 или 34 подается сигнал О, на вход 21.2. подается сигнал 1. Через элементы И 36, 37, 38, 39

0 и ИЛИ 48, 49, 50, 51 входные данные записываются в триггера 55, 56, 57, 58 при положительном фронте синхросигнала.

Режим обратного счета (счетчик работает как вычитающий): на вход 21.1 (или 34)

5 подается сигнал 1. На вход 21.2 подается сигнал О. На выходах элементов И 36, 37, 38, 39 устанавливается сигнал О. При этом на выходе элемента ИЛИ 40 устанавливается 1, а на выходах элементов И 41. 42, 43 устанавливается конъюнкция сигналов с обратных выходов триггеров 55, 56, 57. Из-за того, что прямые выходы триггеров 55, 56, 57. 58 соединены с первыми входами элементов исключающие ИЛИ 44, 45. 46, 47 и выходы элемента ИЛИ 40, элементов И 41, 42, 43 соединены с вторыми входами элементов исключающее ИЛИ 44, 45. 46, 47 просуммированные по mod 2 значение сигналов через элементы ИЛИ 48, 49. 50, 51 поступает на D-входы триггеров 55, 56, 57, 58 и записывается на положительном фронте синхросигнала 12. Режим хранения: на вход 21.1. (или 34) и 21.2 подается сигнал Г. На выходе элементов И 36, 37, 38, 39, 41, 42, 43 и элемента ИЛИ 40 значение сигнала О. Через элементы исключающие ИЛИ 44, 45, 46, 47 (суммирование по mod 2) и ИЛИ 48, 49, 50,51 сигналы из прямых выходов триггеров 55, 56, 57, 58 поступают на D-входы триггеров 55, 56. 57. 58 и обеспечивается таким образом хранение информации, ранее записанной в триггерах 55,56, 57. 58.

Формирователь 5 признака нуля вырабатывается код 27 признака обнуления (положительный сигнал) только в том случае, когда код 25 равен нулю (т.е. содержимое счетчика 4 равно нулю).

Счетчик адреса работает следующим образом.

Режим увеличения адреса (данных) на 1. При этом режиме код 11 переноса должен быть 1. Тогда в зависимости от входных данных (кодов) 28.1, 28.2, 28.3 и 28.4 на выходе элементов исключающие ИЛИ 59, 61, 63, 65 устанавливаются коды, увеличенные на 1 и следовательно по D-входу триггера 68. 69, 70, 71 также устанавливается при положительном фронте синхросигнала 12 соответствующее состояние. На выходе 72 переноса код 1 устанавливается только в том случае когда на входах 28.1, 28.2, 28.3. 28.4 и 11 установлено состояние 1.

Режим хранения данных. При этом режиме код 11 переноса должен быть равен О, тогда при положительном фронте синхросигнала 12 в триггерах 68, 69, 70, 71 записываются коды 28.1, 28.2, 28.3, 28.4 без изменений.

Стек 6 адресов микропрограмм - память с указателем стека. Стек 6 предназначен для хранения адреса возврата при выполнении микропрограмм и работает по принципу - последний записан - первый прочитан. Стеком 6 обеспечивается запись, хранение и считывание кода 24 адреса, сформированного в счетчике 3. При записи информации указатель стека увеличивается на единицу, при считывании уменьшается на единицу. Глубина вложенности микропрограмм зависит от разрядности указателя стека. При заполнении последней ячейки стека формируется код 35 стек заполнен. Запись и считывание информации (т.е. кода 24 и кода 26) в стеке 6 происходит по наличию кода 12 (положительный фронт синхросигнала).

Коммутатор 7 адреса обеспечивает выбор из четырех поступивших на его входы

0 кодов адресов: код 14 адреса (либо из регистра 10 микрокоманд либо из внешних источников), код 24 адреса (сформированный, в счетчике 3), код 25 адреса (сформированный в счетчике 4) и код 26 адреса (сформи5 рованный в стеке 6). Код 28 поступает в счетчик 3 адреса и в регистр 8 исполнительного адреса.

Рассмотрим второй этап и средства хранения исполнительного адреса, хранения и

0 считывания микрокоманды.

Регистр 8 исполнительного адреса обеспечивает хранение кода 28 адреса и передачу кода 29 исполнительного адреса в блок 9 памяти микрокоманд. Блок 9 памяти

5 микрокоманд построен так, что он дешифрирует код 29 исполнительного адреса и передает микрокоманду 30, хранимое в памяти блока 9 в регистр 1, микрокоманд. Регистр 10 микрокоманд обеспечивает

0 запись, хранение и выдачу микрокоманды (соответствующих кодов 31. 32, 33.1, 33.2, 33.3, 33.4,34 и 36) для формирования адреса следующей микрокоманды и выполнения микроопераций,

5 Необходимо отметить формирование нулевого адреса, то есть адреса микрокоманды, находящейся по нулевому адресу в блоке 9 памяти микрокоманд. Нулевой адрес формируется двумя способами: входом

0 (первый) 13 начальной установки устройства (отрицательный сигнал) и вторым входом (кодом) 20 начальной установки (отрицательный сигнал). Код 20 формируется (отрицательный сигнал) блоком 1 местного

5 управления если на его входе комбинация 33,1. 33.2, ЗЗ.З...ЗЗ-i имеет нулевое значение, т.е. 0,0...0. Таким образом, при наличии одного из двух кодов 13 или 20 (отрицательны сигнал) элемент ИЛИ-НЕ 2 вырабатыва0 ет код 16 (положительный сигнал) который обнуляет счетчик 3, стека 6, счетчик 4, регистр 8 и следовательно код 29 исполнительного адреса обеспечивает считывание микрокоманды по нулевому адресу блока 9

5 памяти микрокоманд.

Использование данного устройства дает возможность формировать адрес следующей микрокоманды из внешних и внутренних источников адреса; осуществить аппаратный сброс и следовательно,

считывание микрокоманды, находящейся в нулевом адресе блока памяти микрокоманды; хранение исполнительного адреса; запись, хранение и последовательную выборку микрокоманды по исполнительному адресу; совмещения операций по формированию адреса и, считывания микрокоманд различных этапов.

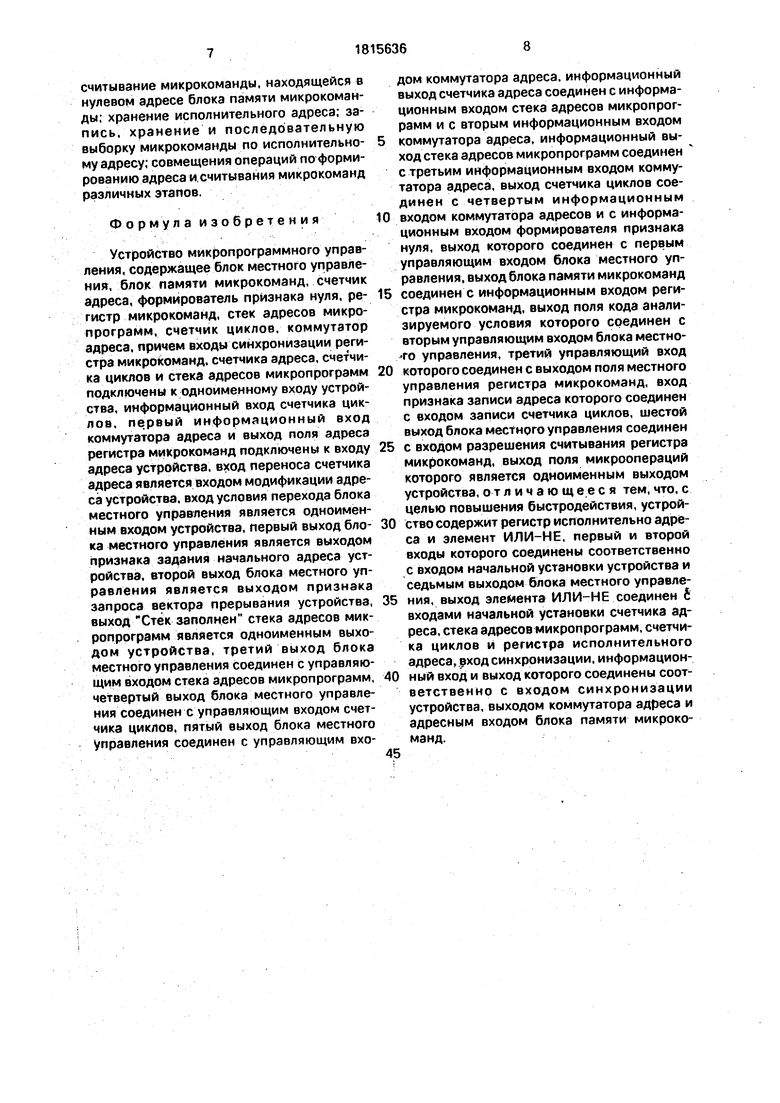

Формула изобретения

Устройство микропрограммного управления, содержащее блок местного управления, блок памяти микрокоманд, счетчик адреса, формирователь признака нуля, регистр микрокоманд, стек адресов микропрограмм, счетчик циклов, коммутатор адреса, причем входы синхронизации регистра микрокоманд, счетчика адреса, счетчика циклов и стека адресов микропрограмм подключены к одноименному входу устройства, информационный вход счетчика циклов, первый информационный вход коммутатора адреса и выход поля адреса регистра микрокоманд подключены к входу адреса устройства, вход переноса счетчика адреса является входом модификации адреса устройства, вход условия перехода блока местного управления является одноименным входом устройства, первый выход блока местного управления является выходом признака задания начального адреса устройства, второй выход блока местного управления является выходом признака запроса вектора прерывания устройства, выход Стек заполнен стека адресов микропрограмм является одноименным выходом устройства, третий выход блока местного управления соединен с управляющим входом стека адресов микропрограмм, четвертый выход блока местного управления соединен с управляющим входом счетчика циклов, пятый выход блока местного управления соединен с управляющим входом коммутатора адреса, информационный выход счетчика адреса соединен с информационным входом стека адресов микропрограмм и с вторым информационным входом

коммутатора адреса, информационный выход стека адресов микропрограмм соединен с третьим информационным входом коммутатора адреса, выход счетчика циклов соединен с четвертым информационным

входом коммутатора адресов и с информационным входом формирователя признака нуля, выход которого соединен с первым управляющим входом блока местного управления, выход блока памяти микрокоманд

соединен с информационным входом регистра микрокоманд, выход поля кода анализируемого условия которого соединен с вторым управляющим входом блока местного управления, третий управляющий вход

которого соединен с выходом поля местного управления регистра микрокоманд, вход признака записи адреса которого соединен С входом записи счетчика циклов, шестой выход блока местного управления соединен

с входом разрешения считывания регистра микрокоманд, выход поля микроопераций которого является одноименным выходом устройства, отличающееся тем, что, с целью повышения быстродействия, устройство содержит регистр исполнительно адреса и элемент ИЛИ-НЕ, первый и второй входы которого соединены соответственно с входом начальной установки устройства и седьмым выходом блока местного упрэвления, выход элемента ИЛИ-НЕ соединен Ј входами начальной установки счетчика адреса, стека адресов микропрограмм, счетчика циклов и регистра исполнительного адреса, вход синхронизации, информационный вход и выход которого соединены соот- ветственно с входом синхронизации устройства, выходом коммутатора адреса и адресным входом блока памяти микрокоманд.

Таблица истинности дешифратора блока 1 местного управления

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

Изобретение относится к вычислительной технике и может найти применение при создании центральных процессоров. Целью изобретения является повышение быстродействия устройства. Устройство содержит блок местного управления, элемент ИЛИ- НЕ, счетчик адреса, счетчик циклов, формирователь признака нуля, стек адресов микропрограмм, коммутатор адреса, регистр 8 исполнительного адреса, блок памяти микрокоманд, регистр микрокоманд. 4 ил., 2 табл.

Продолжение таблицы 1

Таблица истинности блока 1 местного управления

Продолжение таблицы 1

ТэБлица2

Продолжение таблицы 2

| Проектирование цифровых систем на комплектах микропрограммируемых БИС, М.: Радио исвязь, 1984 | |||

| с | |||

| Ребристый каток | 1922 |

|

SU121A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-05-15—Публикация

1990-12-18—Подача