«у

(Л

01

со

4 4

СО

« бпдп

ИвчвЛ КМ Т

9ut.i

мультиплексоры, блок 3 умножения, арифметико-логический блок 4 мантисс, первый 5 и второй 6 буферные регистры, блок 8 коррек1щи частного, узел 9 поиска левой единиц., блок 10 сдвига.

блок 11 приближенного деления, блок 12 приближенного вычисле1шя корня, арифметический блок 13 порядков, блок 14 микропрограммного управления с соответствуюпсими связями. 18 шт.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046396C1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении процессоров с плавающей запятой. Целью изобретения является расширение области применения за счет выполнения операции вычисления обратной величины квадратного корня и использования шинной структуры. Устройство для обработки данных содержит блок 1 регистров общего назначения, первый 2 и второй 7 мультиплексоры, блок 3 умножения, арифметико-логический блок 4 мантисс, первый 5 и второй 6 буферные регистры, блок 8 коррекции частного, узел 9 поиска левой единицы, блок 10 сдвига, блок 11 приближенного деления, блок 12 приближенного вычислений корня, арифметический блок 13 пордяков, блок 14 микропрограммного управления с соответствующими связями. 18 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических процессоров с плавающей запятой.

Целью изобретения является расши- рение области применения за счет выполнения операции вычисления обратной величины квадратного корня и использования ншнной структуры.

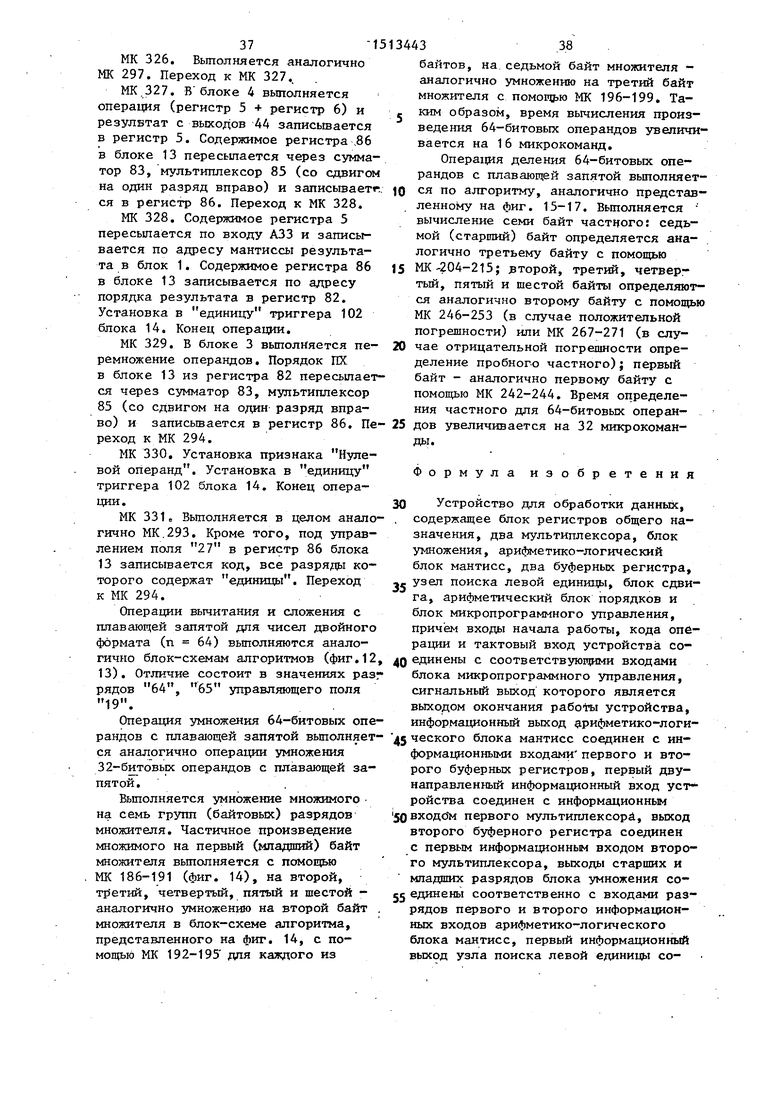

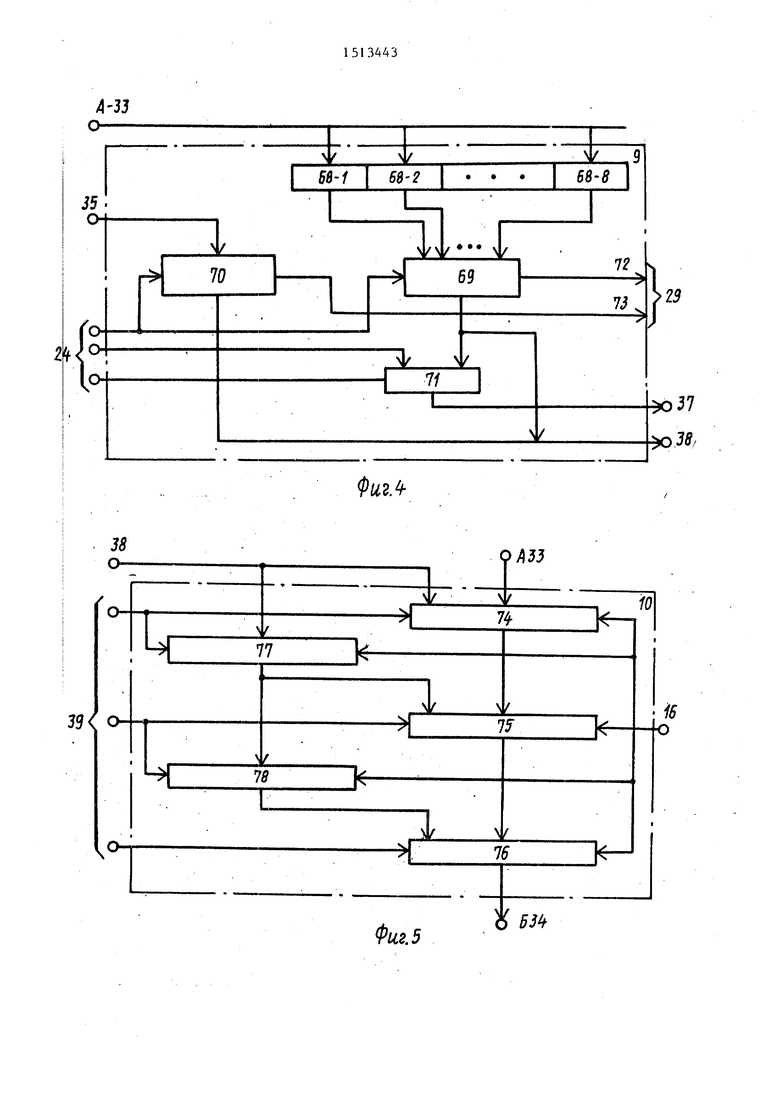

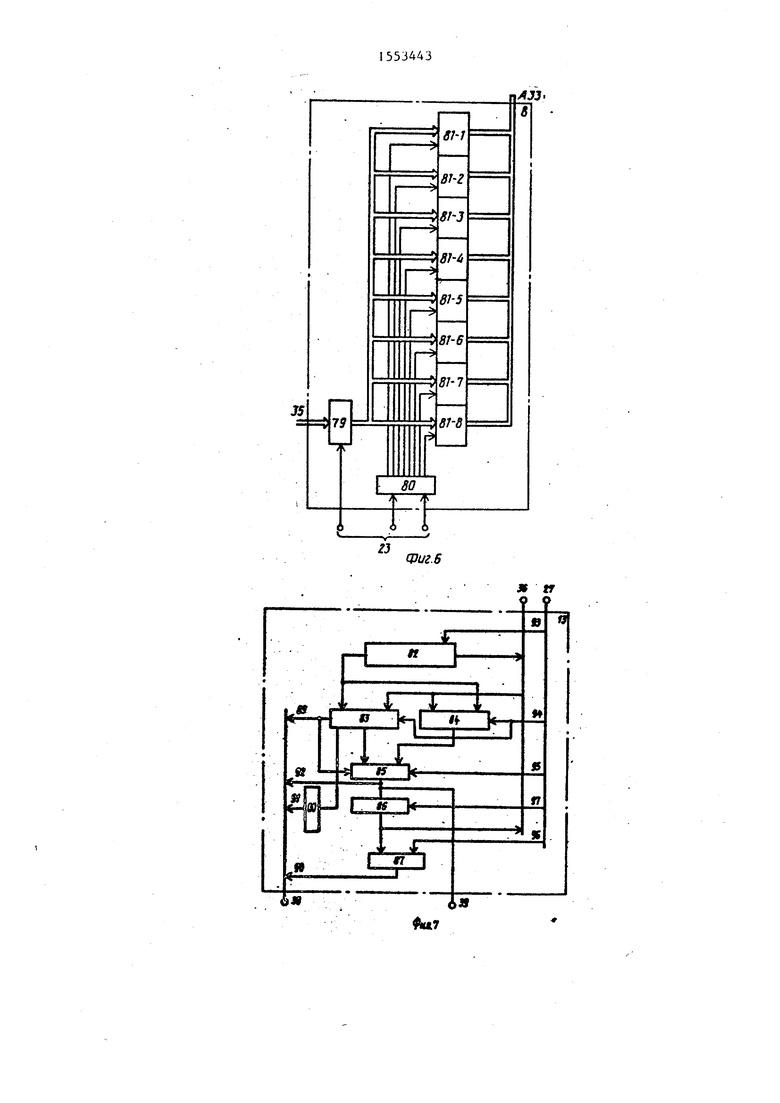

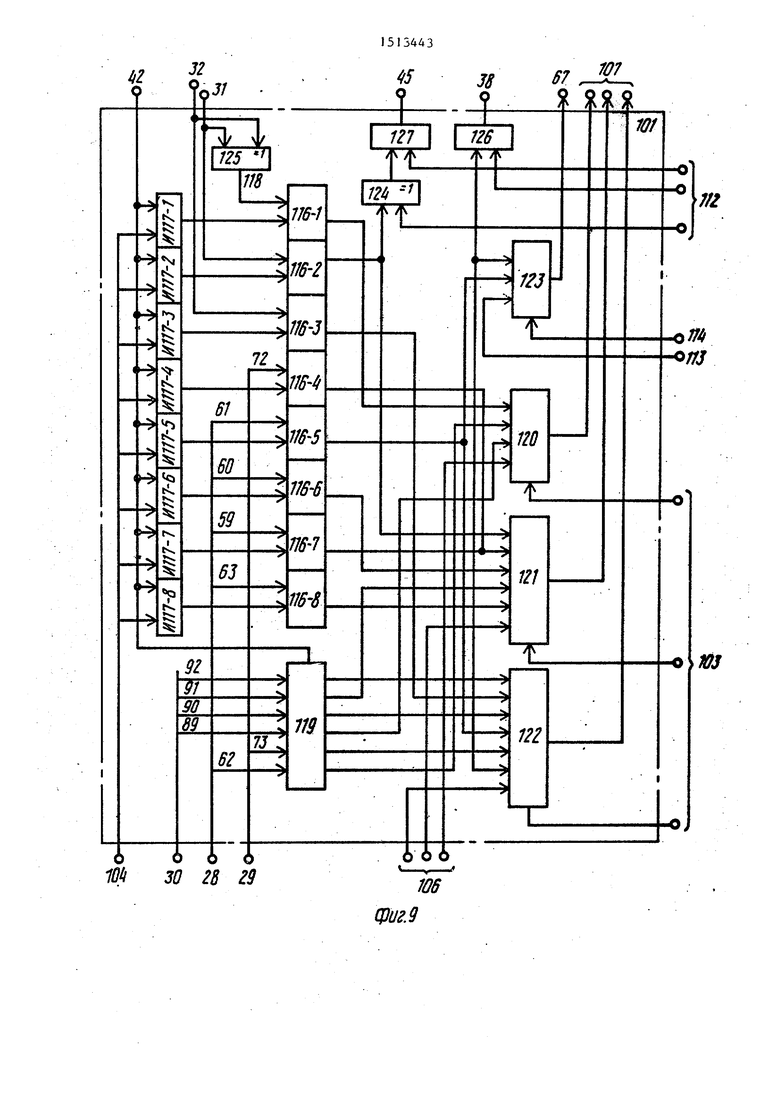

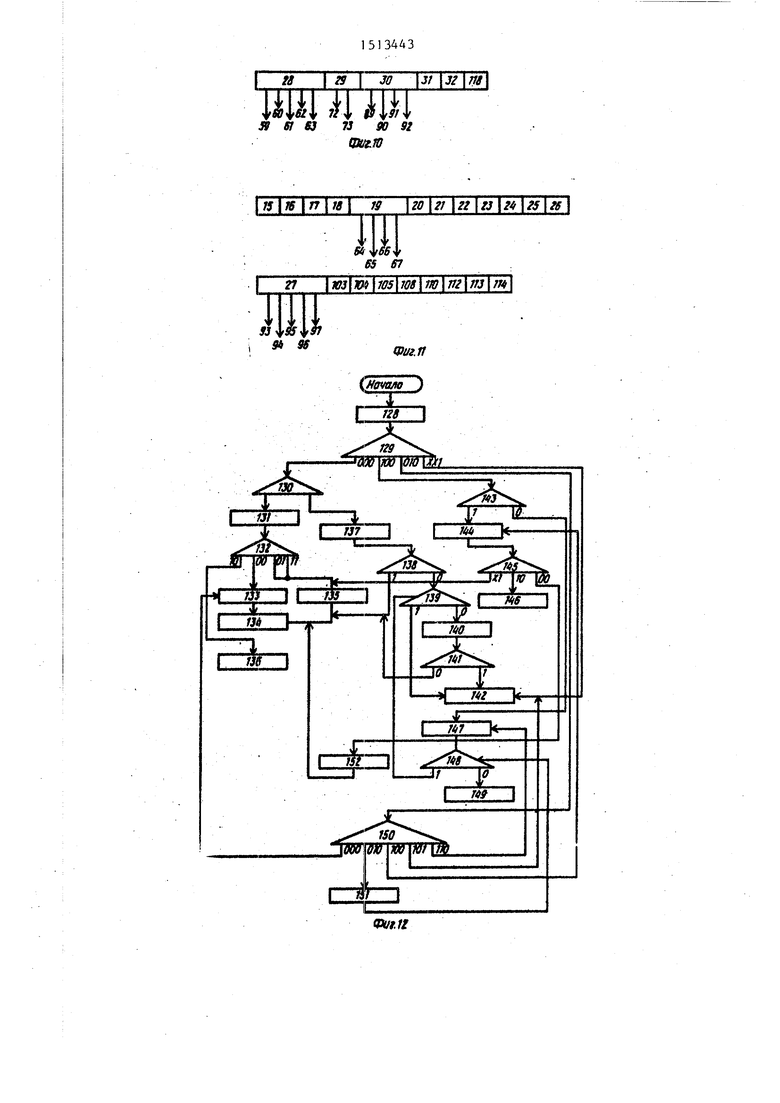

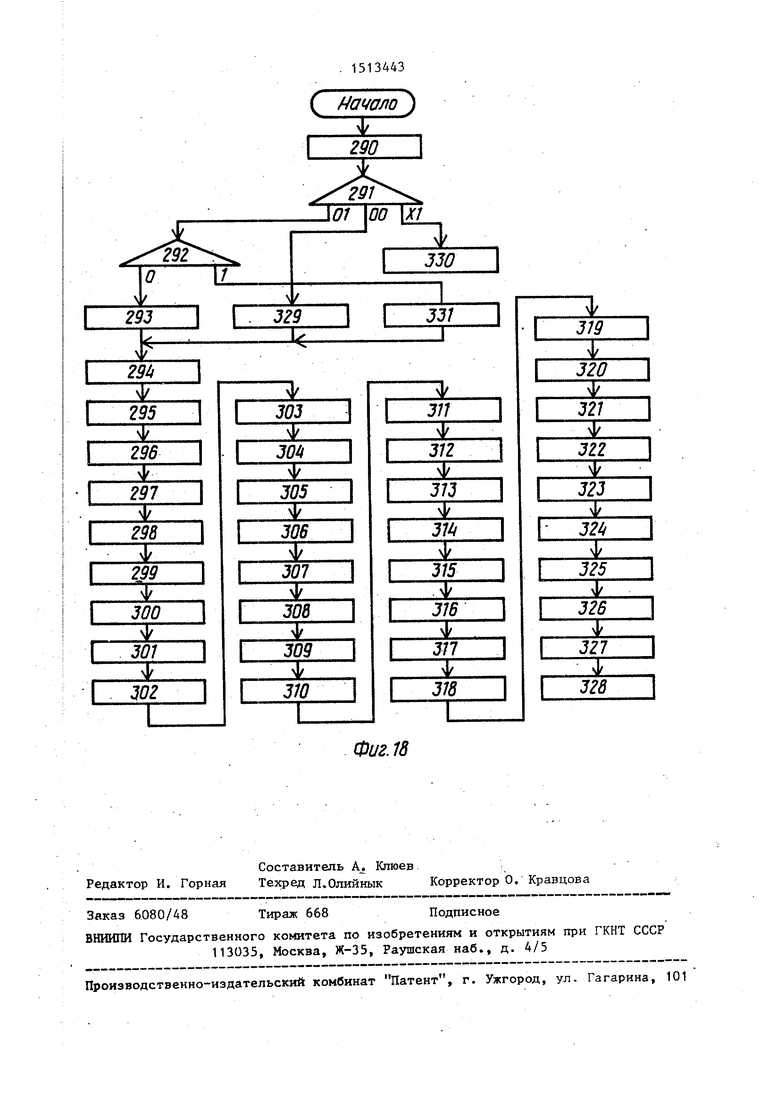

На фиг. 1 представлена схема уст- ройства для обработки данных; на фиг. 2,- схема блока умножения; на фиг. 3 - схема арифметико-логического блока мантисс; на фиг. 4 - схем узла поиска левой единиц ; на фиг.5- схема блока сдвига; на фиг« 6 - схема блока коррекции частного; на фиг. 7 - схема арифметического блока порядков; на фиг. 8 - схема блока микропрограммного управления; на фиг. 9 - схема узла регистрации состояния; на фиг. 10 - структура слова .состояния; на фиг. 11 - структура микрокоманды; на фиг. 12 - диаграмма алгоритма операции вычитания; на фиг. 13 - диаграмма апгори-тма операции сложения; на фиг. 14 - диаграмма алгоритма операции у ножения; на фиг. 15-17 диаграмма алгоритма операции деления ; на фиг. 18 - диаграм- ма алгоритма -операции вычисле1дая об- ратной величины корня.

Устройство для обработки данных (фиг, 1) содержит блок 1 регистров общего назначения, первый мультиплек сор 2, блок 3 умножения, арифметико- логический блок 4 мантисс, первый 5 и второй 6 буферные регистры, второй мультиплексор 7, блок 8 коррекции частного,- узел 9 поиска левой еди- ницы, блок 10 сдвига, блок 11 приближенного деления, блок 12 приближенного вычисления корня, арифметически блок 13 порядков, блок.14 микропрограммного управления, с первого по тринадцатый управляющие выходы 15-27 соответственно блока 14 микропрограммного управления, с первого по пятый входы 28-32 условий блока 14 микропрограммного управления соответственно, первый А 33 и второй Б 34 двунаправленные информационные входы устройства, выход 35 мультиплексора 2, первый 36 и второй 37 информационные выходы узла 9 поиска левой единицы, первый информационный вход 38 блока 10 сдвига, вход 39 задания величины сдвига блока 10 сдвига, вход 40 начала работы устройства, вход 41 кода операции устройства, тактовый вход 42 устройства, выход 43 окончания работы устройства, информа1щонный вькод 44 ариф1 1етико-логического блока 4 мантисс, информационный выход 45 блока 14 микропрограммного управления .

Структурные схемы блоков и узлов на фиг, 2-9 приведены ддя случая операндов двух форматов - 32 (24 разряда мантисса, 8 разрядов порядок и 64 (56 разрядов мантисса, 8 разрядов порядок) разряда.

Блок 1 регистров общего -назначе-- ния предназначен для записи, хранения и считывания информации (побайтно или кратно байту) по двум двунаправленным .входам АЗЗ и Б34.

Мультиплексор 2 имеет трехстабиль ные выходы. Блок 3 умножения (фиг.2) содержит з множители (46-1)446-7), входы первых сомножителей которых соединены с входом 34 устройства, а входы вторых сомножителей - с выходом 35 мультиплексора 2, выходы стар пгих и младших разрядов умножителей (46-1)-(46-7) являются соответствующими выходами блока 3 умножения, а вход разрелпения соединен с выходом 18 блока 14 микропрограммного управления .

Арифметико-логический блок 4 мантисс (фиг.3) для разрядности 64 содержит четыре сумматора-вычитателя 47-50, элементы Ш1И 51-53, демульти- .гшексор 54, мультиплексор 55, элемен ИЛИ 56, выходы 57 сравнения операндов сумматоров-вычитателей, элемент ИЛИ 58, группу сигнальных выходов

арифметико-логического блока А ман- тисе, состоящую из выходов переноса 59, старшего разряда 60, разряда округления 61, равенства нулю 62 старших шестнадцати разрядов выхода 44 и равенства операндов 63, группу входов задания режима арифметико-логического блока 4 мантисс, состоящую из входов точности 64 (одинарная/ двойнал), формата 65 (плавающая/фиксированная запятая), вида операции 66 и переноса 67, причем входы двадцати четырех старпшх разрядов ин- форматщонных входов 33 и 34 подключены соответственно к первым и вторым информационным входам сумматора-вьти- тателя 50, следующие восемь (по-стар- шинству) входов разрядов информационных входов 33 и 34 соединены соответственно с первыми и вторыми информационными входами сумматора-вычитате- ля 49, младшие восемь входов разрядов информационных входов 33 и 34 подключены соответственно к первым и вторым |информационным входам сумматора-вы- читателя 47, остальные входы разрядов информационных входов 33 и 34 соединены соответственно с первыми и вторь ми информационными входами сумматора- вычитателя 48, выходы переноса сумма- торов-вычитателей 47, 48 и 49 подключены к первым входам элементов ИЛИ 51 52 и 53 соответственно, вторые входы которых соединены соответственно с первым, вторым и третьим выходами де- мультиплексора 54 четвертый выход которого подключен к .входу переноса сумматора-вычитателя 47, выходы элементов ИЛИ 51, 52 и 53 соединены с входами переносов соответственно сумма торов-вычитателей 50, 49 и 48, выходы 57 сравнения операндов подключены к входам элемента ИЛИ 58, выходы сумматоров-вычитателей 47-50 соединены с информационным выходом 44 блока 4, старпше шестнадцать выходов разрядов которого подключены к входам элемента или 56, входы 64-67 грзшпы блока- 4 подключены соответственно к управляющим входам демультиплексо- ра 54, мультиплексора 55, сумматоров- вычитателей 47-50 и к информационно- му входу демультиплексора 54,

Буфер ные регистры 5 и 6 имеют вход сигнала записи и тристабильные выходы.

Мультиплексор 7 имеет два информационных входа и тристабильный выход

0

5

0

5

0

5

0

5

0

и вьтолняет сдвиг на 8 бит влево или передачу информации без сдвига.

Узел 9 поиска левой единицы (фиг.4) содержит восемь элементов ИЛИ (68-1)- (), два приоритетных шифратора 69 и 70 и мультиплексор 71, первый - восьмой входы байтов информационного входа 33 устройства подключены к входам соответственно первого - восьмого элемента ИЛИ (68-1)-(68-8), выходы которых соединены с информационными входами первого приоритетного шифратора 69, чьи выходьт подключены к четвертому, пятому и mecTONry (старшим) выходам разрядов выхода 36 узла 9 и к первому информационному входу -мультиплексора 71, Отправляющий и второй информационный входы которого, входы разрешения приоритетных шифраторов 69 и 70 соединены соответственно с входами разрядов входа задания режима узла 9, выход 37 которого соединен с выходами мультиплексора 71, сиг- нальные выходы приоритетных шифраторов 69 и 70 являются соответственно выходами 72 и 73 разрядов сигнального выхода узла 9 (налгтчие сигнала на выходах 72 и 73 соответствует отсутствию единичного бите.) , информационные выходы второго приоритетного шифратора 70 подключены к трем младшим выходам разрядов выхода 36 узла 9, а информационные входы шифратора 70 соединены с выходом 35 мультиплексора 2 .

Блок 10 сдвига (фиг. 5) предназначен для выполнения логических сдвигов влево и вправо на 0-63 бита и содержит пять сдвигателей 74-78. Первый сдвигатель 74 реализует сдвиг на О, 1, 2, 3 бита вправо, второй сдвигатель .75 - на О, 4, 8, 12 бит вправо, третий сдвигатель 76 - на О, 16, 32, 48 бит впр-аво. Входы 38 и 33 являются соответственно первым и ВТОРЫМ информационными входами, выход третьего сдвигателя 76 - выходом блока 10 сдвига, вход 38 подключен к информационному входу четвертого сдвигателя 77, а входы трех младших разрядов входа 38 соединены с дополнительными входами разрядов первого сдвигателя 74. выходы разрядов последнего соединены с входами разрядов второго сдвигателя 75, дополнительные входы разрядов которого подключены к двенадцати ьшадишм выходам

азрядов четвертого сдвигателя 77 ыходы разрядов пятого сдвигателя 78, ыходы разрядов второго сдвигателя 5 подключены к входам разрядов третьго сдвигателя 76, сорок восемь доолнительных входов разрядов котороо соединены с выходами разрядов пяого сдвигателя 78,

В случае вьтолнения правого сдвига JQ его реализация осуществляется на пером 74j втором 75 и третьем 76 сдвига- телях. Операнд поступает на ин|3эорма- ционный вход первого сдвигателя 74. Сигнал с выхода 16 поступает на входы 15 управления третьим состоянием четвертого 77 и пятого 78 сдвигателей и запрещает передачу через них информации на дополнительные входы разрядов второго 75 и третьего 76 сдвигателей. 20

Сдвиг влево вьтолняется через сдвиг вправоэ число сдвигов вправо является дополнением до 64 числа сдвигов влево. Операнд поступает на вход 38, а по входу 33 поступает нулевое значе- 25 ние. Сигнал с выхода 16 поступает на входы управления третьим состоянием четвертого 77 и пятого 78 сдвигателей и разрешает передачу через них инфор- матщи на дополнительные входы разря- 30 дов соответственно второго 75 и третьего 76 сдвигателей. Входы младших двух разрядов числа сдвигов (вход 39) подключены к входам управления с числом сдвигов первого 74 и четвертого 77 сдвигателей, входы следующих.двух разрядов числа сдвигов соединены с входами управления числом сдвигов второго .75 и пятого 78 сдвигателей, входы старших двух разрядов числа jg сдвигов подключены к управляющим входам чи сла сдвигов третьего сдвигателя 76

Блок 11 приближенного деление может реализовать любой быстрый метод ,,- приближенного деления, например табличный. К адресным входам таблиц под- , кгаочаются входы групп старших разрядов делимого и делителя, а на выходе блока под управлением сигнала с выхода 25 устанавливается значение прибли женного частного.

БЛОК 12 приближенного вычислегогя корня может реализовать любой быстрый метод определения приближенного значения корня квадратного (ипи обратной величины корня), например табличный метод. К адресным входам таблиц подключается вход группы старших разрядов

35

50

0

5 0 g

,-

5

0

операнда, а на выходах устанавливается под управлением сигнала с выхода 26 приближенное значение корня квадратного (или обратной величины корня).

Блок 8 коррекции частного (фиг, 6) содержит реверсивный двоичный счетчик 79 с запоминанием, выходы которого подключены к входам демультиплексора, образованного дешифратором 80 и восемью шинными формирователями (81-1) (81-8), выходы дешифратора 80 подключены к управляющим входам соответству- юшрих формирователей 81, информационные входы которых соединены с выходами счетчика 79, а выходы являются соответствующими выходами разрядов блока 8, счетный вход счетчика 79, вход разрешения и информационный вход, дешифратора 80 являются входами соответ- ствзпощих разрядов входа задания релси- ма блока 8,

Арифметический блок 13 порядков (фиг. 7) содержит регистр 82 общего назначения, сумматоры-вычитатели 83 и 84, и мультиплексор 85, регистр 86 порядка, схему 87 сравнения с -константой, элемент ИЛИ 88, выходы 89-92 раз™ рядов сигнального выхода арифметического блока 13 порядков, входы 93-97 разрядов входа задания режима арифме- , тического блока 13 порядков, причем вход 94 соединен с управляющими входами сумматоров-вычитателей 83 и 84, выход переноса сумматора-вычитателя 83 соединен с первым управляющим вхо- док мультиплексора 85 и является выходом 89 блока 13, вькод регистра 86 и вход 96 блока 13 соединены соответственно с информационным входом и входом разрешения схемы 87 сравнения с константой, выход младшего разряда и второй зтт:равл.яющий вход мультиплексора 85 соединены соответственно с выходом 92 и входом 95 блока 13, первый информационный выход регистров 82 общего назначения соединен с первым информахщонным входом первого сумматора-вычитате ля 83 и вторым информационным входом второго с т-шатора-вычи- тателя 84, информационный вход блока 13 соединен с вторым информационным входом - выходом регистров 82 общего назначения, с вторым информационным входом сумматора-вычитателя 83, с первым информахщонным входом сг. мматора- вычитателя 84 и выходом регистра 86 порядков, выход результата сумматора- вычитателя 83 соединен прямо и со

5

10

20

25

сдвигом вправо на один разряд соответственно с первьш и вторым информационными входами мультиплексора 85, выход которого соединен с информационным входом регистра 86 порядков, выход результата сумматора-вычитателя 84 соединен с третьим информационным входом мультиплексора 85, выходы равенства разрядов двух операндов первого сумматора-вычитателя 83 подключены к входам элемента ИЛИ 88, выход которого соединен с выходом 91 блока 13, выход мультиплексора 85 подключен к информационному выходу блока 13,|5 вход задания режима регистра 86 порядков соединен с входом 97 блока 13, выход схемы 87 сравнения с константой вляется выходом 90 блока 13.

Блок 14 микропрограммного управле- ния (фиг 8) содержит регистр 98 адреса микрокоманд, узел 99 памяти микрокоманд, регистр 100 микрокоманд, узел 101 регистрации состояния, триггер 102, выходы 103-105 соответственно первого, второго управляющих полей и окончания работы регистра 100 микрокоманд, выход 106 трех младших разрядов регистра 98 адреса микрокоманд, выход 107 узла 101 регистрации состояния, выход 108 адреса перехода узла 99 памяти микрокоманд, информационный вход 109 регистра 100 микрокоманд, выход 110 управления узла 99 памяти микрокоманд, регистр 111 команд, выходы 112-114 соответственно микроприказов переноса и полярности знака, третьего управляющего поля регистра 100 микрокоманд, узел 115 памяти комавд, причем вход 41 кода операции устройства подключен к информационным входам регистра 111, зшравляющий вход которого вместе с входом сброса триггера.102 соединен с входом 40 устройства. Выход регистра 111 соединен с входом узла . 115 памяти команд, выход которого подключен к первому информационному входу регистра 98, второй информационный вход которого соединен с выходом 108 узла 99, и управляющий вход подключен к выходу 110 узла 99, выходы старших разрядов и выходы трех младших разрядов регистра 98 соединены соответственно с входами старших разрядов узла 99 и

30

35

40

50

101, вход с соответ

регистров 98, 100 и узла 28-32 бпока 14 соединены вующими входами узла 101.

Узел 101 регистрации состояния (фиг. 9) содержит восемь триггеров (116-1)-(116-8), восемь элементов (117-1)-(117-8), выход 118, регист

119,четыре мультиплексора 120-123 элементы ИСКПЮЧАМ01ЕЕ ИЛИ 124 и 125 два формирователя шин 126 и 127, п чем первые входы элементов И 117 п ключены к соответствз ющим разрядам выходов 104 регистра 100, а вторые - к тактовому входу 42 устро ства, выходы элементов И 117 соеди ны с тактовыми входами соответству ющих триггеров 116, информационные входы которых подключены к входам

31 и 32, выходам 72, 61, 60, 59 и и к выходу 118 элемента 125, выход триггера 116-1 соединен с четверты информационным входом Мультиплексо

120,выход триггера 116-2 - с инфо мационным входом мультиплексора 12 и первым входом элемента 124, выхо третьего триггера 116-3 - с шестым информационным входом мультиплексо 122, выход триггера 116-4 - с пяты информационным входом мультиплексо ра 121, выход триггера 116-5 - с ч вертым и вторым информационными вх дами мультиплексоров 122 и 123 соо ветственно, выход триггера 116-6 с четвертым информационным входом мультиплексора 121, выход триггера 116-7 - с вторым и третьим информа ционными входами мультиплексоров 1 и 123 соответственно, а также с ин мационным входом формирователя 126 выход триггера 116-8 соединен с вт ;рым информационным входом мультиплек ;сора 121, вь1ходы62, 73, 89, 90, 91 и 92 подключены соответственно к п вому, второму, третьему, четвертом пятому и шестому информационным вх дам регистра 119, тактовый вход ко рого соединен с тактовым входом 42 устройства, первый выход (выход пе вого разряда) регистра 119 подключ к третьему информационному входу м типлексора 120, второй выход - к треть ему информационному входу мультиплек ра 122, третий выход - к второму и

входом узла 101, выходы 107 узла 101 со-/ формационному входу мультиплексора

единены с входами трех младших разряде узла 99, выход которого соединен входом 109 регистра 100, вход 42 устройства соединен с тактовыми входами

120, четвертый выход - к пятому инф мационному входу мультиплексора 12 пятый выход - к третьему информацио ному входу мультиплексора 121, а ше

5

10

0

5

5

.

30

5

0

0

101, входы с соответст-

регистров 98, 100 и узла 28-32 бпока 14 соединены вующими входами узла 101.

Узел 101 регистрации состояния (фиг. 9) содержит восемь триггеров (116-1)-(116-8), восемь элементов И (117-1)-(117-8), выход 118, регистр

119,четыре мультиплексора 120-123, элементы ИСКПЮЧАМ01ЕЕ ИЛИ 124 и 125, два формирователя шин 126 и 127, причем первые входы элементов И 117 подключены к соответствз ющим разрядам выходов 104 регистра 100, а вторые - к тактовому входу 42 устройства, выходы элементов И 117 соединены с тактовыми входами соответству - ющих триггеров 116, информационные входы которых подключены к входам

31 и 32, выходам 72, 61, 60, 59 и 63 и к выходу 118 элемента 125, выход триггера 116-1 соединен с четвертым информационным входом Мультиплексора

120,выход триггера 116-2 - с информационным входом мультиплексора 121 и первым входом элемента 124, выход третьего триггера 116-3 - с шестым информационным входом мультиплексора 122, выход триггера 116-4 - с пятым информационным входом мультиплексора 121, выход триггера 116-5 - с четвертым и вторым информационными входами мультиплексоров 122 и 123 соответственно, выход триггера 116-6 с четвертым информационным входом мультиплексора 121, выход триггера 116-7 - с вторым и третьим информационными входами мультиплексоров 122 и 123 соответственно, а также с информационным входом формирователя 126, выход триггера 116-8 соединен с вто- ;рым информационным входом мультиплек- ;сора 121, вь1ходы62, 73, 89, 90, 91 и 92 подключены соответственно к первому, второму, третьему, четвертому, пятому и шестому информационным входам регистра 119, тактовый вход которого соединен с тактовым входом 42 устройства, первый выход (выход первого разряда) регистра 119 подключен к третьему информационному входу мультиплексора 120, второй выход - к третьему информационному входу мультиплексора 122, третий выход - к второму информационному входу мультиплексора

120, четвертый выход - к пятому информационному входу мультиплексора 122, пятый выход - к третьему информационному входу мультиплексора 121, а шее-.

1513443 2

ой выход - к седьмому информационно-поля 27 с признаками: 93 - управ- му входу мультиплексора 122, первыеление регистром 82; 94 - управление информационные входы мультиплексоровсумматорами-вычитателями 83 и 84; 120-122 соединены с выходами разрядов 95 - управление мультиплексором 85; выхода 106, а их управляюище входы - управление схемой 87; 97 - .с выходами разрядов выхода 103, выходыуправление регистром 86; поля мультиплексоров 120-122 подключены куправления мультиплексорами 120, 121 выходам 107, первый информационныйи 122; поля 104 - поля маски элемен- вход мультиплексора 123 соединен с вы1|дтов И 117; поля 105 микроприказа ходом 113, заправляющие входы соедине-работы устройства; поля 108 - поля ны с выходом 114, а выход подключенадреса следующей микрокоманды; поля к входу 67, вторые входы элементов 110 - поля управления регистром 98; 124, формирователей 126 и 127 соедине-поля 112 - поля управления элемен- ны с выходами соответствующих разрядов sтами 124, 126 и 127; поля 113 - сиг- выхода 112, выход элемента 124 подклю-нала входа переноса для блока 4; по- чен к первому в:{оду формирователя шинля 114 - поля управления мульти- 127, выход которого соединен с инфор-плексором 123.

мациониым выходом 4.5 блока 14, выход Все операнды для любой операции

формирователя шин 126 подключен к вхо-20хранятся в регистрах общего назначеду 38 блока 10 сдвига.ния: знаки и мантиссы в блоке, порядСлово-состояние (фиг. 10) содержитки в регистре 82 блока 13. следующие признаки полей, формируемьте Устройство (фиг. 1) работает слена соответствующих входах.дующим образом.

Для поля 59 - выход пере- 25 На вход 41 устройства поступает

носа; 60 выход старшего разряда;код операции, который под управлени 61 - выход разряда округления; сигнала на входе 40 (сигнал на вхопризнак нулевого старшего слова; 40 одновременно сбрасьгоает тригпризнак равенства мантисс.гер 102) заносится в регистр 111 коДля поля 72 - признак нуле.- оманд. Код операции на выходах этого

вого операнда; 73 - признак нулево-регистра определяет адрес узла 115,

го байта.содержимое соответствуклцей ячейки памяти которого является начальным адреДля поля 89 - выход парено-сом микропрограммы. Адрес начальной

са; 90 - признак сравнения; 91 - .микрокоманды под управлением тактового

признак равенства порядков; 92 сигнала с входа 42 и сигнала с выхомладший разряд результата. да 110 записьгоается в регистр 98. Три

Для одноразрядных полей: 31 -младших разряда с выходов регистра 98

знак.первого операнда; 32 - знакпостзшают через мультиплексоры 120,

второго операнда; 118 - результат Q121 и 122 соответственно на адресные

сложения по модулю два знаков операн-входы младших разрядов узла 99 памяти

дов. микрокоманд, на старшие с1дресные вхоМикрокоманда (фиг. 11) состоит изды которого поступает код старших раз- следующих полей: поля 15 управления-рядов регистра 98. Спустя время, опре- мультиплексором 2; поля .16 управле- д«деляемое временем чтения узла 99, на ния блоком 10; поля 17 управления вторые информационные входы регистра блоком 1; поля 18 управления бло-98 поступает адрес следующей микроко- . ком 3; поля 19 с признаками: 64 -манды с выхода 108 узла 99, Под управ- точность операнда (одинарная/двойная);лением сигнала с выхода 107 поле уп- 65 - формат операнда (фиксирован- JQ равляющих сигналов с выходов узла 99 ный/плавающий); 66 - управление сум-записьтается в регистр 100 микроко- маторами-вьшитателями 47-50; 67 -манд, а адрес следующей микрокоманды - вход переноса; поля 20 управленияв регистр 98. Управляющие сигналы с регистром 5; поля 21 управления выхода регистра 100 осуществляют мас- регистром 6; поля 22 управления «кирование через элементы записи при- мультиплексором 7; поля 23 управ-знаков условий входов 31, 32 и 118 ления блоком 8; поля 24 управленияв триггеры 116. Остальные признаки узлом 9; поля 25 управления блокомусловий в каждом такте записьшаются 11j поля 26 управления блоком 12;в регистр 119. Выходы последнего и

триггеров 116 подключены к информационным входам мультиплексоров 120- 122, управляющие входы которых, определяемые выходами 103 регистра 100, позволяют осуществлять ветвление в микропрограмме по трем признакам условий одновременно. Микрокоманда, соответствующая окончанию микропрограммы, с помощью сигнала с выхода t05 устанавливает триггер 102 в единичное состояние, при этом выход 43 сигнализирует об окончании работы текущей микропрограммы и готовности вьтолнить следую1цую команду.

Устройство в процессе вьтолнения различных арифметических операций работает следующим образом.

Микропрограмма операции вычитания представлена на фиг. 12 и содержит микрокоманды (МК) 128-152.

МК 128. Из регистров считьшаются мантиссы операндов X и Y соответственно на входы АЗЗ и Б34. Янаки 31 первого X и 32 второго Y операндов и результат 118 сложения по модулю два знаков на элементе 125 под управлением разрешающих сигналов 104 через элементы И 117 фиксируются в соответствующих триггерах 116 узла 101 блока 14. В блоке 13 признак 89 управляет выбором информационного входа мультиплексора 85 и под управлением микроприказа 97 поля 27 результат с выходов мультиплексора 85 запи- сьшается в регистр 86. Результат с выходов мультиплексора 85 поступает также на первые входы схемы 87, где

МК 132. Под управлением поля 93

сравнивается с константой и формируется признак больше 90, который фикси-дд из регистра 82 считьшается константа, руется в соответствующем триггере 116 равная единице, которая с выхода мультиплексора 85 поступает с выходов 39 блока 13 на входы числа сдвигов блока 10. Под .отравлением поля 20 со- 45 держимое буферного регистра 5 поступает по входу АЗЗ на -информационные входы блока 10, где выполняется сдвиг вправо (под управлением поля 16), и результат с выходов блока 10 по вхо- нием микроприказов полей 20 и 21, jg ду Б34 записьшается в блок 1 по адре- В соответствующих триггерах 116 фикси- су результирующей мантиссы. Анализ руются признаки 59 переноса, 60

узла 101 блока 14. В случае равенства порядков элемент ИЛИ 88 формирует признак 91, который фиксируется, в соответствующем триггере 116. В блоке 4 (под управлением микроприказов поля 19) вычисляется разность операндов (X - Y) , которая записьгоается в буферные регистры 5 и 6 под управлепризнаков 59 и если 00, то переход к МК 133; если 10, то переход к МК 136; если 11, то переход к МК 135.

значения старшего значащего разряда . и 63 равенства операндов. Переход к-МК 129.

МК 129. Анализ сформированных пре- даздущей микрокомандой условий 89, 91 и если 000, то переход к МК 130; если 100, то переход к МК

143; если 010, то переход к МК 150; если ХХ1, то переход к Ж 142 (X - iбезразли шое состояние).

МК 130, Из блока считьгоается на вход АЗЗ операнд Y. В блоке 10 выполняется сдвиг операнда Y вправо |на число разрядов, определяемых со- держи 1ым регистра 86, которое с выходов 36 регистра 86 через сумматор 83 и мультиплексор 85 поступает с вы- . ходов 39 блока 13 в блок 10 на входы числа сдвигов. Результат сдвинутого операнда Y по входу Б34 записьшается под, управлением поля 17 в один из регистров группы регистров блока 1. Вьтолняется анализ признака если О, то переход к МК 137; если 1, то .переход к МК 131.

МК 131. Мантисса операнда X и де- нормализованная мантисса операнда Y Считаются (под управлением поля 17) из блока 1 по входам АЗЗ и Б34 соответственно и поступают на входы блока 4. Результат суммы с выходов блока 4 (под управлением поля 19) записьшается в регистр 5 (под управлением поля 20). Порядок операнда X (под управлением поля 93) поступает из регистра 82 на сумматоры 83 и 84 блока 13, где увеличивается на единицу (под управлением поля 94), результат записьшается через мультиплексор 85 в регистр 86 (под управлением поля 97). Признаки переноса 59 блока 4 и 89 блока 13 фиксируются в соответствующих триггерах 116 узла 101 блока 14 Переход к МК 132„

МК 132. Под управлением поля 93

из регистра 82 считьшается константа, равная единице, которая с выхода мультиплексора 85 поступает с выходов 39 блока 13 на входы числа сдвигов блока 10. Под .отравлением поля 20 со- держимое буферного регистра 5 поступает по входу АЗЗ на -информационные входы блока 10, где выполняется сдвиг вправо (под управлением поля 16), и результат с выходов блока 10 по вхо- ду Б34 записьшается в блок 1 по адре- су результирующей мантиссы. Анализ

дд из регистра 82 считьшается константа, равная единице, которая с выхода муль типлексора 85 поступает с выходов 39 блока 13 на входы числа сдвигов блока 10. Под .отравлением поля 20 со- 45 держимое буферного регистра 5 поступает по входу АЗЗ на -информационные входы блока 10, где выполняется сдвиг вправо (под управлением поля 16), и результат с выходов блока 10 по вхо jg ду Б34 записьшается в блок 1 по адре- су результирующей мантиссы. Анализ

55

признаков 59 и если 00, то переход к МК 133; если 10, то переход к МК 136; если 11, то переход к МК 135.

МК 133. Под управлением поля 20 содержимое буферного регистра 5 по входу АЗЗ записывается в блок 1 (под управлением поля 17) по адресу результирукядей мантиссы. Под управлением поля 93 порядок операнда X запи- сьгеается по адресу результирующего порядка в регистр 82 блока 13. Переход к МК 134.

МК 134. Под управлением поля 112 с выхода 45 формирователя 127 узла 101 блока 14 значение знака операнда X по соответствунлцим разрядам входа АЗЗ записьтается в разряды знака регистра результата блока 1 (под управлением поля 17). Установ ка триггера 102 блока 14 в единицу. Конец операции.

МК 135. В блок 1 (под управлением поля 17) ив регистр,8 блока 13 (под управлением поля 93) по адресам результирующей мантиссы и результирующего порядка записываются единицы во всех разрядах, т.е. записывается максимальное значение результата. Переход к МК 134.

МК 136. Выполняется аналогично МК 134. Дополнительно осуществляется запись порядка операнда X в регистр 82 блока 13 по адресу результирующего порядка (под управлением поля 93).

МК 137. Под з равлением поля 17 из блока 1 считываются на входы АЗЗ и Б34 соответственно мантисса операнда X. и денормализованная мантисса операнда Y. В блоке 4 (под управлением поля 19) вьтолняется операция вычитания мантисс операнда X и денор- мализованной мантиссы Y, результат под управлением полей 20 и 211 записьтается в буферные регистры 5 и 6. Признак 60 d выходов 28 блока

45

4 фиксируется в соответствующем триг- дл ем поля 27 содержимое регистра 86 гере 116 узла 101 блока 14. Под управлением, поля 93 в блоке 13 порядок операвда X записьшается по адресу результирующего порядка в регистр 82. Переход к МК 138.

МК 138. Под управлением поля 20 содержимое регистра 5 по входу АЗЗ поступает на первые информационные входы узла 9, где под управлением поля 24 формируется на выходах 36 j двоичньй код номера левого ненулевого разряда. В блоке 13 этот код записывается в одном из регистров 82, и в сумматоре 84 (под управлением ;поля 94) вычисляется дополнение до „

64, результат через мультиплексор

85 записьгоается в регистр 86. Признак .

72 с выходов 29 узла 9 фиксируется

в регистре 119 узла 101 блока 14. Вызаписывается по адресу порядйа резул тата в регистр 82. Вьтолняется анали признака если О, то переход к МК 134; если 1, то переход к МК 142. МК 142. Под управлением поля 17 в блок 1 и в регистр 82 блока 13 (по управлением поля 27) по адресу результата записьшаются мантисса, знак и порядок результата, равные нулевом значению. Установка в единицу триг гера 102 блока 14, Конец операхщи.

МК 143 о Выполняется аналогично МК 130о Отличие состоит в том, что на вход АЗЗ из блока 1 считьшается мантисса первого операнда X. Вьтолняется анализ признака если О то переход к МК 147; если 1, то пере ход к МК 144о

полняется анализ условия 60, зафиксированного в МК 137: если О, то переход к МК 139; если 1, то переход к МК 134.

,МК 139. Под управлением поля 21 содержимое буферного регистра 6 с выходов поступает на информационные входы 38 сдвигателя 77 и дополнительные входы сдвигателя 74 блока 10. На ин- форма1щонные входы сдвигателя 74, соединенные с выходом АЗЗ, не поступает информация (что соответствует нулевому операнду). На входы 39 блока 10 с выходов мультиплесора 85 блока 13 поступает код числа сдвигов вправо. Под управлением поля 16 в блоке 10 выполняется операция сдвига вправо на число разрядов, которое является дополнением до 64 числа сдвигов влево, и результат по входу Б34 запи- сьшается (под управлением поля 17) в блок 1 по адресу результирующей мантиссы. Выполняется анализ призна- ка 72, сформированного в МК 138: если О, то переход к МК 140; если 1, то переход к МК 142.

МК 140. В блоке 113 под управлением поля 27 считываются из регистра 82 результирумций порядок и двоичный код левого ненулевого разряда мантиссы результата на соответствующие входы сумматора-вычитателя 83, разность с выходов последнего записьшается в регистр 86. Признак 89 переноса сумматора 83 фиксируется в соответствующем триггере 116 узла 101 блока 14. Переход к МК 141.

МК 141. В блоке 13 под управлени

ем поля 27 содержимое регистра 86

записывается по адресу порядйа результата в регистр 82. Вьтолняется анализ признака если О, то переход к МК 134; если 1, то переход к МК 142. МК 142. Под управлением поля 17 в блок 1 и в регистр 82 блока 13 (под управлением поля 27) по адресу результата записьшаются мантисса, знак и порядок результата, равные нулевому значению. Установка в единицу триггера 102 блока 14, Конец операхщи.

МК 143 о Выполняется аналогично МК 130о Отличие состоит в том, что на вход АЗЗ из блока 1 считьшается мантисса первого операнда X. Вьтолняется анализ признака если О, то переход к МК 147; если 1, то переход к МК 144о

17

МК 144. Вьшолняется аналогично МК 131. Отличие состоит э том, что на вход АЗЗ из блока 1 считывается мантисса вторичного операнда Y, а на входы сумматоров-вычитателей 83 и 84 из регистра 82 блока 13 считьшает- ся порядок второго операнда Y. Переход к МК 145.

МК 145. Вьтолняется аналогично МК 132. Анализ признаков 59 и 89 сформированных в МК 144: если 00, то переход к МК 152; если 10, то переход к МК 146; если 11, то переход к МК 135.

МК 146. Выполняется аналогично МК 136, Отличие состоит в том, что по адресу порядка результата в регист 82 блока 13 записьгоается порялок второго операнда Y

МК 147. Под управлением поля 17 из блока 1 на входы АЗЗ и Б34 считываются мантисса второго операнда Y и денормализованная мантисса операнда X соответственно. Под управлением поля 19 в блоке 4 вычисляется разность этих кодов и результат записывается в буферные регистры 5 и 6 (под управлением полей 20 и 21). Переход к МК 148.

МК 148. Вьтолняется аналогично МК 138о Анализ признака 60, полученного в МК 147: если О, то переход к МК 149; если 1, то переход к МК-139

МК 149. Под управлением поля 112 инверсное значение знака операнда X с выхода 45 формирователя шин 127 уя- ла 101 блока 14 по входу АЗЗ записывается в разряды знака результата регистра блока 1 (под з равлением поля 17). Установка в единицу триггера 102 блока 14. Конец операции,

МК 150 Под управлением поля 17 мантисса первого операнда X записывается по адресу мантиссы результа.та в блок 1, Под управлением поля 27 порядок первого операнда X записывается по адресу порядка результата в -регистр 82 блока 13, Вьтолняется анализ признаков 118, 89 и 63, сформированных в МК 128: если 000, то переход к МК 133; ясли 100, то переход к МК 144; если 110, то переход к МК 147; если 010, то переход к МК 151; если 101, то переход к МК 142„

МК 151 о Под управлением поля 17 из блока 1 на шины АЗЗ и Б34 считываются мантиссы второго Y и первого X

-

1513443 8

операндов соответственно. Под упрдвл - нием поля 19 в блоке 4 вычисляется

разность мантисс к результат записывается в буферные регистры 5 и 6 (под управлением полей 20 и 21), Переход к МК 148 о

МК 152, Под управлением поля 20 содержимое регистра 5 по входу АЗЗ записьгоается по адресу мантиссы результата в блок 1 о Под управлением поля 27 порядок второго операнда Y записывается по адресу порядка результата в регистр 82 блока 13, Перехода к МК 134.

5

0

5

0

5

. Микропрограмма операции сложения представлена на фиг, 13,и содержит микрокоманды 153-185.

0 МК 153о Вьтолняется аналогично МК 128о Переход к МК 154.

МК 154. Вьтолняется аналогично МК 129. Анализ признаков 89, 91 и 90. сформированных в МК 153: ес- 5 ли 000, то переход к МК 155; если 100, то переход к МК 168; если 010, то переход к МК 176; если ХХ1, то переход к МК 167. ,

МК 155. Вьтолняется аналогично 0 МК 130. Анализ признака 118, сформированного в МК 153: если О, то переход к МК 156; если 1, то переход к МК 162 о

МК 156. Вьтолняется аналогично МК 131, Переход к МК 157,

МК 157,, Вьтолняется аналогично МК 132о Анализ признаков 59 и 89, сформированных в МК 156: если 00, то переход к МК 158; если 10, то переход к МК 161; если XI, то переход к МК 160,

МК 158. Вьтолняется аналогично МК 133. Переход к МК 159.

МК 159. Вьтолняется аналогично МК 134. Конец операции.

МК 160. Вьтолняетсй аналогично МК 135, Переход к МК 159.

МК 161, Выполняется аналогично МК 136,, Конец операции,

МК 162 Вьтолняется аналогично МК 137,, Переход к МК 163.

МК 163о Вьтолняется аналогично МК. 138о Анализ признака 60, сформированного в МК 162: если О, то переход к МК 164; если 1, то переход к МК 159,

МК 164, Вьтолняется аналогично МК 139, Анализ признака 72, сформированного в МК 163: если О, то пере19

ход к МК 165; если 1, то переход МК 167.

МК 165 о Вьшолняется аналогично МК lAOo Переход к МК 166.

МК 166. Вьтолняется аналогично МК 141. Анализ признака 89, сформированного в МК 165: если О, то переход к МК 159; если 1, то переход к МК 167о

МК 167. Выполняется аналогично МК 142о Конец операциио

МК 168о Выполняется аналогично МК 143. Анализ признака 118, сформированного в МК 153: если О, то переход к МК 169; если 1, то переход к МК 173„

МК 169 о Вьтолняется аналогично МК 144. Переход к МК 170.

МК 170о Вьтолняется аналогично МК 145, Анализ признаков 59 и 89, сформированных в МК 169: если 00, то переход к МК 172; если 10, то переход к МК 171; если Х1, то переход к МК 159с

МК 171. Вьшолняется аналогично МК 146. Конец операции.

МК 172. Вьтолняется аналогично МК 152. Конец операции.

МК 173. Под управлением поля 17 из блока 1 на входы АЗЗ и Б34 счи- тьшаются мантисса второго операнда Y и денормализованная мантисса операнда X соответственно. Под управлением поля 19 в блоке 4 вычисляется разность и результат записьшается в буферные регистры 5 и 6 (под управлением микроприказов полей 20 и 21). Переход к МК 174.

МК 174, Вьтолняется аналогично МК 148о Анализ признака 60, сформированного в МК 173: если О, то переход к МК 164; если 1, то переход к МК .175о

МК 175. Выполняется аналогично МК 149 Конец операции.

МК 176о Под управлением поля 27 порядок первого операнда X записьта- ется по адресу порядка результата в регистр 82 блокд 13. Анализ признаков 118, 89 и 63, с4юрмиро- ванных в МК 153: если ОХХ, то переход к МК 177; если 100, то переход к МК 179; если 101, то переход к

управлением поля блоке 4 вычисляется сумма мантисс и результат записывается в регистр 5 (под управле- нием микроприказов поля 20). Под управлением поля 27 порядок операнда X в блоке 13 увеличивается на

10

15

20

25

единицу и записьшается в регистр 86, Переход к МК 178.i

МК 178. Вьтолняется аналогично МК 132. Анализ признака 89, сформированного в МК 177: если О, то переход к МК 158; если 1, то переход к МК 160.

МК 179о Вьтолняется в целом аналогично МК 133 за исключением того, что переход к следующей МК осуществляется по анализу признака 60. сформированного в МК 153: если О, то переход к МК 163; если 1, то переход к МК 159.

МК 180о Под управлением поля 17 из блока 1 на входы АЗЗ и Б34 считываются мантиссы второго Y и первого X операндов соответственно. Под управлением поля 19 в блоке 4 вычисля- ется разность мантисс и результат записьшается в буферные регистры 5 и 6 (под управлением полей 20 и 21). 30 Переход к МК 181.

МК 181, Под управлением микроприказов поля 20 содержимое буферного регистра 5 передается на вход АЗЗ и затем записьшается по адресу мантиссы результата в блок 1 под yupas- лением поля 17.. Вьтолняется анализ признака 60, сформированного в Щ 180: если О, то переход к МК 182; если 1, то переход к МК 175.

МК 182. Вьтолняется в целом аналогично МК 128 за исключением того, что анализ признака 60 не выполняет ся и осуществляется переход к МК 183.

МК 183. Вьтолняется аналогично МК 139. Переход к МК 184.

МК 184о Выполняется аналогично МК 140. Переход к МК 185.

МК 185 о Вьшолняется аналогично МК 141. Анализ признака 89, сфор- 50 мированного в МК 184: если О, то переход к МК 175; если 1, то переход к МК 167„

Блок-схема вьшолнения операции умножения чисел с плавающей запятой

35

45

МК 172; если 110, то переход к МК 180. 55 одинарной точности (п 32) представМК 177. Под управлением поля 17 из блока 1 на входы АЗЗ и Б34 соответственно считьшаются мантиссы первого X и второго Y операндов. Под

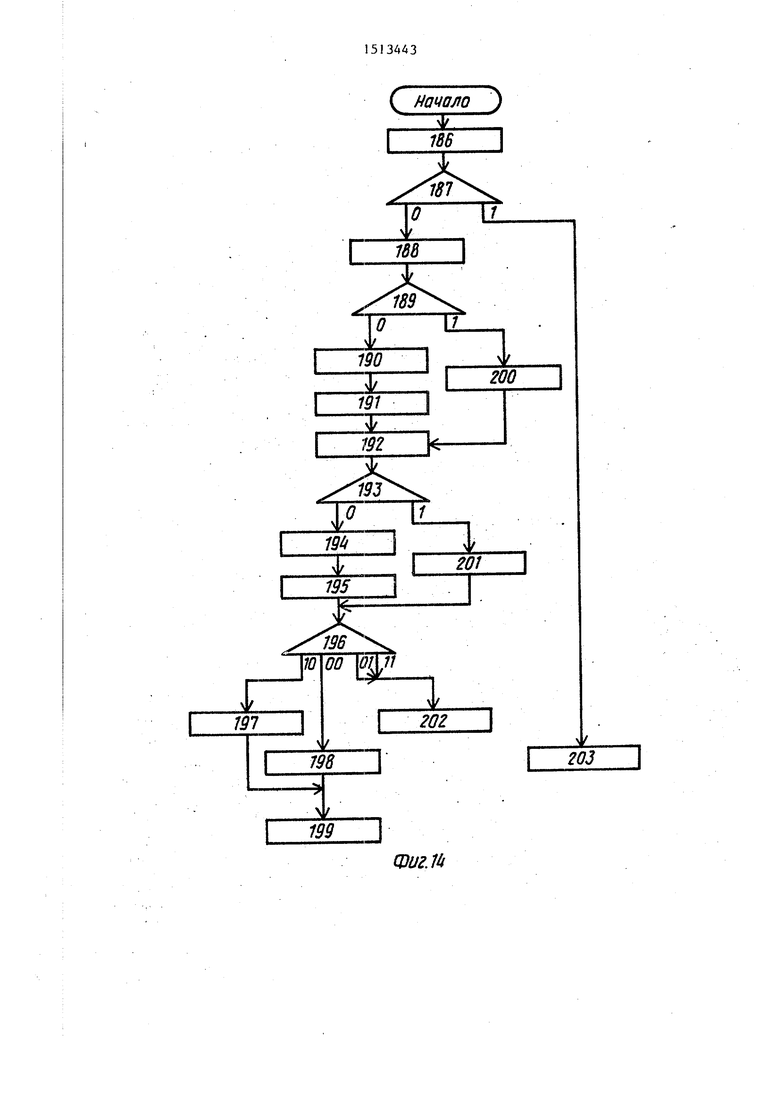

лена на фиг. 14 и содержит микрокоманды МК 186-203.

МК 186. Из блока 1 под управлением поля 17 на входы АЗЗ и Б34 считы,

51344320

управлением поля блоке 4 вычисляется сумма мантисс и результат записывается в регистр 5 (под управле- нием микроприказов поля 20). Под управлением поля 27 порядок операнда X в блоке 13 увеличивается на

10

15

20

25

единицу и записьшается в регистр 86, Переход к МК 178.i

МК 178. Вьтолняется аналогично МК 132. Анализ признака 89, сформированного в МК 177: если О, то переход к МК 158; если 1, то переход к МК 160.

МК 179о Вьтолняется в целом аналогично МК 133 за исключением того, что переход к следующей МК осуществляется по анализу признака 60. сформированного в МК 153: если О, то переход к МК 163; если 1, то переход к МК 159.

МК 180о Под управлением поля 17 из блока 1 на входы АЗЗ и Б34 считываются мантиссы второго Y и первого X операндов соответственно. Под управлением поля 19 в блоке 4 вычисля- . ется разность мантисс и результат записьшается в буферные регистры 5 и 6 (под управлением полей 20 и 21). 30 Переход к МК 181.

МК 181, Под управлением микроприказов поля 20 содержимое буферного регистра 5 передается на вход АЗЗ и затем записьшается по адресу мантиссы результата в блок 1 под yupas- лением поля 17.. Вьтолняется анализ признака 60, сформированного в Щ 180: если О, то переход к МК 182; если 1, то переход к МК 175.

МК 182. Вьтолняется в целом аналогично МК 128 за исключением того, что анализ признака 60 не выполняется и осуществляется переход к МК 183.

МК 183. Вьтолняется аналогично МК 139. Переход к МК 184.

МК 184о Выполняется аналогично МК 140. Переход к МК 185.

МК 185 о Вьшолняется аналогично МК 141. Анализ признака 89, сфор- 50 мированного в МК 184: если О, то переход к МК 175; если 1, то переход к МК 167„

Блок-схема вьшолнения операции умножения чисел с плавающей запятой

35

45

одинарной точности (п 32) представ

лена на фиг. 14 и содержит микрокоманды МК 186-203.

МК 186. Из блока 1 под управлением поля 17 на входы АЗЗ и Б34 считываются мантиссы-операндов Y и X соответственно. Мантисса операнда X записывается с входов множимого в блок 3 под управлением поля 18. . На входы 35 мультиплексора 2 (под управлением микроприказов полей 15 и 24) передается младший (третий) байт мантиссы операнда Y, поступает на входы множителя блока 3 и под управлением поля 18 записывается в блок Зо Под управлением поля 27 и блока 13 из регистра 82 считьтают- ся порядки операндов X и Y и в сумматорах 83 и 84 вычисляется сумма порядков. Результат с выходов мультиплексора 85 записывается в регистр 86 Выход 89 переноса сумматора 83 фиксируется в соответствующем триггере

15 семь разрядоз вправо. Сдвинутый р зультат с выходов блока 10 заноси по входу Б34 через блок 4 в регис Одновременно с эт им в блоке 3 под управлением поля 18 выполняется

116 узла 101 блока 14. В другом триг- 20 перемножение. Вьшолняется анализ

гере 116 фиксируется результат 118 сложения по модулю два знаков 31 первого X и 32 второго Y операндов В блоке 3 вьтолняется умножениео Переход к МК 187.

МК 187о Под управлением поля 18 с выходов блока 3 на входы АЗЗ и Б34 считьшаются соответственно слово старших и слово младших разрядов произведений, вычисленных в соответ- ствукщих умножителях 46 блока 3. Эти два слова поступают на входы блока 4, где под управлением поля 19 вычисляется их сумма, т.е. произведение мантиссы операнда X на младший байт мантиссы операнда Y. Результат с выходов блока 4 записьшается в регистр В под управлением прля 20. Выполняется анализ признака 89. сформированного в МК 186: если О, то переход к МК 188; если 1, то переход кМК203..

МК 188. Под управлением поля 17 из блока 1 на вход АЗЗ считьгоается мантисса второго операнда Y. Под управлением микроприказов полей 24 и 15 второй байт мантиссы Y передается через мультиплексор 2 на его выходы и записьгоается с входов множите- ля в блок 3 (под управлением поля 18)о Выполняется перемножение в блоке 3. Одновременно с этим в узле 9 под управлением поля 24 на выходе 73 приоритетного шифратора 70 формируется признак нулевого байта и фиксируется в соответствующем разряде регистра 119 узла 101 блока 14. Под управлением поля 27 в блоке 13 содержимое регистра 86 записьтается

25

30

признака 73, сформированного в

МК 188: если О, то переход к МК 1

если 1, то переход к МК 200..

МК 190.Выполняется в целом ана но МК 187 за исключением того,что выполняется анализ признака 89,а зультат с выходов 44 блока 4 запи вается в регистр 6. Переход к Ж

МК 191 . Под у правлением по ля 18 в ке 4 выполняется суммирование содер мого регистров 5 и 6(под управлен Микроприкаэов полей 20, Результат с выходов 44 блока 4 по равлением поля 20 записьшается гистр 5 г Переход к МК 192. МК 192. Выполняется в целом а гично МК 188. Отличие состоит в что по входам множителя в блок 3 письшается с выхода 35 мультипле ра 2 старпмй байт операнда Y, счи ваемый по входу АЗЗ из блока 1 ме того, в блоке 13 пересылка сод жимого регистра 86 в регистр 82 осуществляется. Переход к МК 193

МК 193, Вьтолняется аналогично Анализ признака 73, сформированн в МК 192: если О,то переход к МК если 1,то переход к МК 201.

МК 194 о & 1п лняется аналогично 5о МК 190. Переход к МК 195.

МК 195о Под управлением полей 20, 21 и 22 содержимое буфе ,ных регистров 5 и 6 поступает на ;входы ЛЗЗ и Б34 соответственно. С мощью управляющего поля 19 в бл ;4 вьтолняется сложение. V Под управлением поля 27 в бл ке 13 вьтолняется уменьшение на ницу порядка результата и запись

35

40

45

55

в регистр 82 по адресу порядка результата Переход к МК 189.

МК 189. Из регистра 82 читается кон- станта (восемь - число сдвигов нЭ байт) и через сумматор 83 и мультиплексор 85 передается на выходы 39 блока 13. Под управлением поля 20 содержимое буферного регистра 5 по

входу АЗЗ поступает на вторые информационные входы блока 10, где под управлением микроприказов поля 16 и кода на его входах 39 вьшолняется сдвиг частичного произведения на восемь разрядоз вправо. Сдвинутый результат с выходов блока 10 заносится по входу Б34 через блок 4 в регистр. Одновременно с эт им в блоке 3 под управлением поля 18 выполняется

перемножение. Вьшолняется анализ

5

0

признака 73, сформированного в

МК 188: если О, то переход к МК 190;

если 1, то переход к МК 200..

МК 190.Выполняется в целом аналогично МК 187 за исключением того,что не выполняется анализ признака 89,а результат с выходов 44 блока 4 записывается в регистр 6. Переход к Ж 191.

МК 191 . Под у правлением по ля 18 в блоке 4 выполняется суммирование содержимого регистров 5 и 6(под управлением Микроприкаэов полей 20,) . Результат с выходов 44 блока 4 под управлением поля 20 записьшается в регистр 5 г Переход к МК 192. МК 192. Выполняется в целом анало- гично МК 188. Отличие состоит в том, что по входам множителя в блок 3 записьшается с выхода 35 мультиплексора 2 старпмй байт операнда Y, считываемый по входу АЗЗ из блока 1 Кроме того, в блоке 13 пересылка содержимого регистра 86 в регистр 82 не осуществляется. Переход к МК 193, ,

МК 193, Вьтолняется аналогично МК 189. Анализ признака 73, сформированного в МК 192: если О,то переход к МК 194: если 1,то переход к МК 201.

МК 194 о & 1п лняется аналогично о МК 190. Переход к МК 195.

МК 195о Под управлением полей 20, 21 и 22 содержимое буфер- ,ных регистров 5 и 6 поступает на ;входы ЛЗЗ и Б34 соответственно. С помощью управляющего поля 19 в блоке ;4 вьтолняется сложение. V Под управлением поля 27 в бло- ке 13 вьтолняется уменьшение на единицу порядка результата и запись его

5

0

5

5

в регистр 86. Признаки 60, 61 и признак 89 выхода переноса сумматора 83 фиксируются в соответствую ющих триггерах 116 узла 101 блока 14. Переход к МК 196. .

,МК 196о Под управлением поля 21 содержимое регистра 6 подается на первые информационные входы 38 блока 10, в котором под управлением поля 16 вьтолняется сдвиг на один разряд влевоо Результат с выходов 10 по входу Б34 через блок 4 записьшается в. регистр 6. Вьтолняется анализ признаков 60 и 89, сформированных в МК 195: если 00, то переход к МК 198; если 10, то переход к МК 197; если XI, то переход к МК 202.

МК 197о Под управлением поля 20 содержимое регистра 5 по входу АЗЗ постзшает на первые входы блока 4, на вход 67 переноса которого поступает с выхода мультиплексора 123 узла 101 блока 14.значение признака 61. сформированного в МК 195. Результат с выхода блока 4 записывается под управлением поля 20 в регистр 5. .Переход к МК 199о

МК 198 о Под управлением поля 21 Ьодержимое регистра 6 по входу Б34 постзшает на вторые входы блока 4, на вход 67 переноса которого поступает с выхода мультиплексора 123 узла 101 блока 14 значение признака 61, сформированного в МК 195. Результат с выхода блока 4 записывается -под управлением поля 20 в регистр 5. Под управлением поля 27 в блоке 13 содержимое регистра 86 записывается по адресу порядка результата в регистр 82.. Переход к МК 199.

МК 199, Под управлением поля содержх-шое регистра 5 пересылается по входу АЗЗ через блок 10 (со сдви гом на восемь разрядов вправо) на. вход Б34 и затем записьшается с помощью управляющего поля 17 по адресу мантиссы результата в блок 1 Установка в ё диницу триггера 102 блока 14. Конец операции.

МК 200. Под управлением поля 20 содержимое регистра 5 по входу АЗЗ пересылается через блок 10 (со сдвигом на восемь разрядов вправо) на вход Б34, затем через блок 4 пересылается на входы регистра 5 и записывается в него. Переход к МК 192.

МК 201. Вьтолняется аналогично МК 200. Отличие состоит в том, что

с выходов блока 4 результат, кроме регистра 5., записьшается в регистр 6 (под управлением поля 21). Признаки. 60 и 61 фиксируются в соответствующих триггерах 116 узла 101 блока 14. Под управлением поля 27 порядок результата в блоке 13 уменьшается на единицу,а результат записьшается

в регистр 86. Переход к МК 196.

МК 202. Под управлением полей 17 и 27 по адресам мантиссы и порядка результата соответственно в блок 1 и регистр 82 блока 13 записываются нулевые значения операндов. Устанавливается триггер 102 блока 14 в единицу. Конец операции.

МК 203. Под управлением полей 17 и 27 по адресам мантиссы и порядка

результата соответственно в блоке 1 и регистре 82 блока 13 записьюаются значения единиц во всех разрядах. Установка триггера 102 блока 14 в единицу. Конец операции.

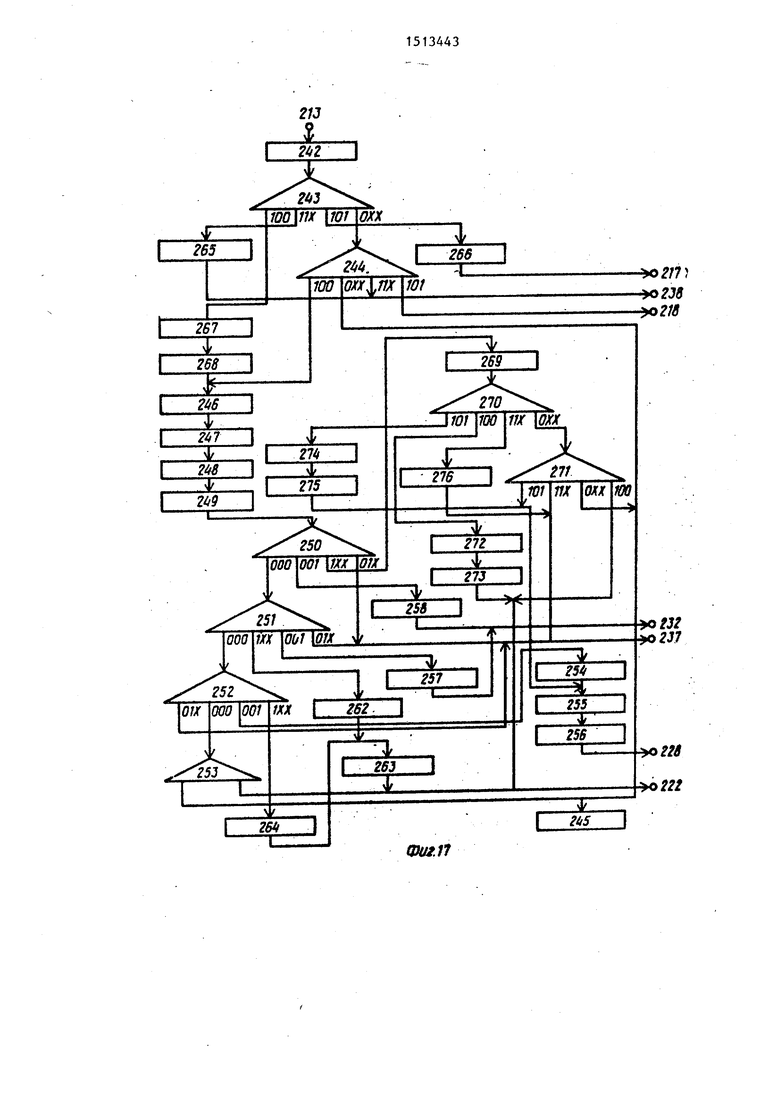

Блок-схема алгоритма деления чисел одинарной точности представлена на фиг, 15-17 и содержит микрокоманды МК 204-289.

МК 204о Под управлением поля 17

из блока на входы АЗЗ и Б34 считьша- ются соответственно мантиссы операндов X и YO Мантисса операнда Y с выхода Б34 поступает на входы множимого и записывается в блок 3, а также поступает на вторые информационные входы блока 4. Под управлением поля 19 в блоке 4 вьтолняется вычисление разности мантисс, в соответствующих триггерах 116 узла блока 14 фикснруются признаки 59 переноса и 63 сравнения. Группы старших разрядов операнда X и операнда Y поступают на входы блока 11, под управлением поля 25 в этом блоке 11 вьгчисляется пробное частное (восемь разрядов) и затем записывается (под управлением поля 23) в блок 8 и с входов множителя записьгоается (под управлением поля 18) в блок 3, Под управлением поля 27 в блоке 13 вычисляется разность порядка (ПХ-ПУ) и результат записьшается в регистр 86. В соот- ветствзпощих триггерах 116 узла 101 блока 14 фиксируются признаки 89

и 118 Переход к МК 205.

МК 205 Под управлением поля .18 b блоке 3 вьтолняется перемножение мантиссы делителя Y на пробное частное. Под управлением поля 17 из

блока 1 на вход АЗЗ считьшается мантисса Y, которая через блок 10 (под упр.авлением поля 16) со сдвигом на восемь разрядов вправо (с помощью уп-: равлякядих входов 39) передается на вход Б34 и затем записьшается по первому адресу одного из регистров блока 1 . С выходов 29 узла 9 в соответствующем триггере 116 узла 101 блока Q 14 фиксируется признак 72 - нулевой операнд. Выполняется анализ признаков 63, 59 и 89, сформированных в МК 204: если ХОО, то переход к МК 206; если Х01, то переход к МК 209j 15 если 010, то переход к МК 211; если 110, то переход к МК 282; если 011, то переход к МК 284; если 111, то переход к МК 285.

Щ 206о Под управлением поля 17. 20 из блока 1 на вход АЗЗ считьшается мантисса, операнда X, пересыпается через блок 10 со сдвигом на один разряд вправо (под управлением кода на входах 39) и по входу Б34 записывается 25 по второму адресу в блок 1. Выполняет ся анализ признака 72,, сформированного в МК 205; если О, то переход к МК 289; если 1, то переход к НК 207.

МК 207. Под управлением поля 27 jg в блоке 13 содержимое регистра 86 увеличивается на единицу и в соответствующем триггере 116 узла 101 блока 14 фиксируется признак 89.. Под управлением поля 17 из блока 1 на входы АЗЗ и Б34 считывак тся соответственно содержимое регистра с вторым адресом и мацтисса делителя Y. Старпие разряды входов АЗЗ и Б34 поступают на входы блока 11, с выходов дя которого (под управлением поля 25) робное частное пересылается и под управлением поля 23 записьтается блок 8, а также в качестве множитея в блок За Переход к МК 208, :,

МК 208о Под управлением поля 18 блоке 3 вьтолняется. перемножение сомножителей Под управлением поля 17 содержимое регистра блока 1 с BTOpbiM адресом записьгоается по jg адресу операндао Выполняется анализ ризнака 89, сформированного в (К 207: если О, то переход к МК 211; еСпи 1, то переход к МК 287.

МК 209 о Вьтолняется аналогично К 207. Переход к МК 210.

МК 210. Вьшолняется аналогично К 208 и, кроме того, анализируется ризнак 89, сформированный в МК

35

55

Q 5

0 5

g я ,

g

5

5

209: если О, то переход к МК 211; если 1, то переход к МК 284.

МК 211. Под управлением поля 18 с выходов блока 3 старшие разряды произведения поступают на первые информационные входы блока 4,а младшие разряды - на вторые информационные входы блока.,4, где под управлением поля 19 вьтолняется их сложение Результат с выходов 44 блока 4 записывается в регистр 6 (под управлением поля 21). Под управлением поля блоке 13 содержимое регистра 86 записывается по адресу порядка результатов в регистр 82. Вьтолняется анализ признака 72, сформированного в МК 205: если О, то переход к МК 212; если 1, то переход к МК 289.

МК 212. Под управлением поля 17 из блока 1 на вход АЗЗ считывается мантисса X. Под управлением поля 19 в блоке 4 вычисляется разность между 1антиссой X и содержимым регистра 6. Результат с выходов 44 блока 4 записы- вается в регистры .5 и 6. В соответствую ющих триггерах узла 101 блока 14 фик- (сируются признаки 59, 63 и 62. -Переход к МК 213.

МК 213. Под управлением поля 17 считьгаается содержимое регистра с первым адресом блока 1 на вход Б34. На вход АЗЗ считьгоается содержимое регистра 5 и записывается по адресу ре- гистра с вторым адресом в блок 1. Под управлением поля 19 в блоке 4 вьтолняется операция вычитания и результат с вы5сода 44 записьшается в регистс 5. t Фиксирую тся Ъризнаки 63 и 62. Вьтолняется анализ признаков 59, 63 и 62, сформированных в МК 212: если 000, то переход к МК 214: если 001, то переход к МК 241; если 01Х, то переход к МА 238; если 1ХХ, то переход к МК 242.

МК 214. Под управлением поля 23 в блоке 8 вьшолняется увеличение на единицу пробного частного. Из бло-у ка 1 на вход Б34 считывается содержимое регистра с первым адресом. На вход АЗЗ считъшается содержимое регистр 5 oi вьтолняется его запись по третьему адресу в блок 1. Под управлением поля блоке 4 осуществляется вычитание и результат с выхода 44 записывается в регис.тр 5. Фиксируются признаки 59, 63 и 62. Вьтолняется анализ признаков 59, 63 и 62, сформированных в МК 213: если 000, то переход.

;К МК 215; если 001, то переход к МК ;240;.если OIXj to переход к МК 238; если 1ХХ, то переход к МК 259. ; МК 215. Под управлением поля 23 IB блоке 8 выполняется увеличение на |; единицу пробного частного. Из блока 11 на вход Б34 считьшается содержимое регистра с первым адресом. На вход АЗЗ считьшается содержимое регистра 5 Под управлением поля 19 в блоке 4 ; вьтолняется вычитание и результат с выходов 44 записывается в регистр 6. Фиксируется признак 59. Вьтолняется анализ признаков 59, 63 и 62, сформированных в МК 214; если 000, то переход к МК 216; если 001, то переход к МК 217; если 01X, то переход к МК 238; если 1ХХ,- то: переход к МК 261.

МК 216о Содержимое блока 8 пересылается по входу АЗЗ и затем записывается в старший байт мантиссы результата в блок 1. Содержимое регистра 6 через мультиплексор 7 (со сдвигом на восемьсразрядов влево) пересыпается I по входу Б34 и затем записьюается в |.регистр 6, Вьтолняется анализ признака 59, сформированного в МК 215; если О, то переход к МК 245; если 1, то переход к МК 246.

МК 217. Вьшолняется в целом аналогично МК 216. Переход к МК 218 без анализа условий.

МК 218. В блок 8 записьгоается ну- левое значение. Содержимое регистра 6 через мультиплексор 7 (со сдвигом на восемь разрядов влево) и через -блок 4 записывается в регистр 5. Переход к МК 219.

i

МК 219. На вход АЗЗ поступает содержимое регистра 5, а на вход Б34 из блока 1 считьтается мантисса У.В блоке 4 вьтолняется вычитание и результат записьшается в регистр 5. Фикси руются признаки 59, 63 и 62. Переход к МК 220.

МК 220. Под управлением поля 23 в блоке 8 вьтолняется увеличение на едгашцу счетчика 79« Под управлением поля 19 в блоке 4 вьтолняется вычитание-мантиссы У из содержимого регистра 5, и результат с выходов 44

10

231; если 01X, то переход к МК 237; если 1ХХ, то переход к МК 230.

МК 221. Под управлением поля 23 содержимое блока 8 пересыпается по входу АЗЗ и затем записьшается во второй по старшинству байт мантиссы результата в блок 1. Вьтолняется анализ признака 59. сформированного,в МК 220: если О, то переход к МК 245;

15

20

30

если 1, то переход к МК 222.

МК 222. Старшие разряды содержимого регистра 5 по входу АЗЗ поступают на первые информационные входы блока 11, на его вторые информационные входы постзшают по входу Б34 старшие разряды мантиссы Y из блока 1. Из блока 11 считывается пробное частное, записьтается в блок 8 и с входов множителя в блок 3. Переход к МК 223.

МК 223 о Выполняется аналогично МК 210. Безусловньй переход к МК 224.

МК 224. Слово старших и слово младших разрядов (составленные из произ- 25 ведений различных умножителей 46) с выходов блока 3 по входам АЗЗ и Б34 соответственно поступают на входы блока 4. В блоке 4 вьтолняется сложение и результат с выходов 44 записьшается в регистр 6. Переход к МК 225.

МК 225о В блоке 4 вьтолняется вычитание содержимого регистра 6 из со- деряшмого регистра 5 и результат записьшается в регистры 5 и 6, Фиксируются признаки 59, 63 и 62. Переход к МК 226.

МК 226. Выполняется аналогично МК 213„ Анализ признаков 59, 63 и 62, сформированных в МК 225: если 000, то переход к МК 227; если 001, то переход к МК 239; если 01X, то переход к МК 239; если 1ХХ, то переход к МК 278.

МК 227. Выполняется аналогично . 45 МК 214. Анализ признаков 59, 63, и 62, сформированных в МК 226: если 000, то переход к МК 228; если 001, то переход к МК 239; если 01Х, то переход к МК 239; если 1ХХ, то 50 переход к МК 277.

МК 228. Вьтолняется аналогично Ж 215о Анализ признаков 59, 63 и 62, сформированных в МК 227: ес35

40

ли 000, то переход к МК 229; если 001, записьшается в регистр 5. Фиксируется 55 то переход к МК 239; если ОIX, то признак 59. Вьтолняется анализ при- переход к МК 239; если 1ХХ, то перезнаков 59.. 63 и 62, сформирован- ход к МК 277,

1ШХ в МК 219: если 000, то переход МК 229с Под управлением поля 23 к МК 221; если 001, то переход к МК содержимое блока 8 пересылается по

0

231; если 01X, то переход к МК 237; если 1ХХ, то переход к МК 230.

МК 221. Под управлением поля 23 содержимое блока 8 пересыпается по входу АЗЗ и затем записьшается во второй по старшинству байт мантиссы результата в блок 1. Вьтолняется анализ признака 59. сформированного,в МК 220: если О, то переход к МК 245;

5

0

0

если 1, то переход к МК 222.

МК 222. Старшие разряды содержимого регистра 5 по входу АЗЗ поступают на первые информационные входы блока 11, на его вторые информационные входы постзшают по входу Б34 старшие разряды мантиссы Y из блока 1. Из блока 11 считывается пробное частное, записьтается в блок 8 и с входов множителя в блок 3. Переход к МК 223.

МК 223 о Выполняется аналогично МК 210. Безусловньй переход к МК 224.

МК 224. Слово старших и слово младших разрядов (составленные из произ- 5 ведений различных умножителей 46) с выходов блока 3 по входам АЗЗ и Б34 соответственно поступают на входы блока 4. В блоке 4 вьтолняется сложение и результат с выходов 44 записьшается в регистр 6. Переход к МК 225.

МК 225о В блоке 4 вьтолняется вычитание содержимого регистра 6 из со- деряшмого регистра 5 и результат записьшается в регистры 5 и 6, Фиксируются признаки 59, 63 и 62. Переход к МК 226.

МК 226. Выполняется аналогично МК 213„ Анализ признаков 59, 63 и 62, сформированных в МК 225: если 000, то переход к МК 227; если 001, то переход к МК 239; если 01X, то переход к МК 239; если 1ХХ, то переход к МК 278.

МК 227. Выполняется аналогично . 45 МК 214. Анализ признаков 59, 63, и 62, сформированных в МК 226: если 000, то переход к МК 228; если 001, то переход к МК 239; если 01Х, то переход к МК 239; если 1ХХ, то 50 переход к МК 277.

МК 228. Вьтолняется аналогично Ж 215о Анализ признаков 59, 63 и 62, сформированных в МК 227: ес5

0

ли 000, то переход к МК 229; если 001, 55 то переход к МК 239; если ОIX, то переход к МК 239; если 1ХХ, то переход к МК 277,

входу АЗЗ и затем записьтается в младший байт мантиссы результата в блок 1 Выполняется анализ признака 59, cфb мированного в МК 228: если О, то переход к МК 245; если 1, то переход к МК 288.

МК 230. По входу АЗЗ в блок 1 по адресу второго байта мантиссы результата под управлением поля 17 зaпиcь вается нулевой операнд. Содержимое регистра с вторым адресом из блока 1 пересылается по входу В34 через блок 4 и записьюается в регистр 5. Переход к МК 222.

МК 231 о Выполняется аналогично Ж

МК 232. Вьтолняется аналогично МК

МК 233о Вьтолняется аналогично МК

МК 234, Выполняется аналогично МК

МК 235 Выполняется аналогично МК 229.

МК 236. Под управлением поля 17 по адресу младшего байта мантиссы результата в блок записьтается нулевое значение. Установка триггера 102 блока 14 в единицу. Конец опе- рациио

МК 237 о Содержимое блока 8 по входу АЗЗ записьшается по адресу второ- го байта мантиссы результата в блок 1 Установка триггера 102 блока 14 в .единицу. Конец операции.

МК 238. Содержимое блока 8 пересылается по входу АЗЗ и затем записы- вается по адресу третьего (старшего) байта мантиссы результата в блок 1. Установка триггера.102 блока 14: в единицу. Конец операции.

. МК 239 о Содержимое блока 8 пере- сьшается по входу АЗЗ и затем записьшается по адресу младацего байта мантиссы результата в блок 1. Установка триггера 102 блока 14 в единицу Конец операции.

МК 240о Под здгравлением поля 17 из блока 1 считьшается содержимое регистра с третьим адресом, пересылается по входу АЗЗ через блок 4 и затем

0

5

0

я

.

Q

5

записьгоается в регистр 6. Переход к МК 217.

МК 241. Под управлением поля 17 из блока 1 считывается содержимое регистра с вторым адресом, пересылается по входу АЗЗ через блок 4 и затем запнсьшается в регистр 6. Переход к Ж 217.

МК 242о Содержимое счетчика 79 блока 8 уменьшается на единицу. На входы АЗЗ и Б34 из блока 1 считыва- . ется содержимое регистров с первым и вторым адресами соответственно. В блоке 4 выполйяется сложение и результат суммы с выходов 44 записывается в пегистры 5 и 6. Фиксируются признаки 59, 63 и 62. Переход к МК 243.

Ж 243 о Содержимое счетчика 79 блока 8 уменьшается на единицу. На вход АЗЗ из блока 1 считывается содержимое регистра по первому адресу, а в регистр по второму адресу в блок 1 пересылается по входу Б34 и записывается содержимое регистра 6. В блоке 4 Вьтолняется сложение и результат суммы с выходов 44 записьшается в регистр 6. Фиксируются признаки 59, 63 и 62. Вьтолняется «нагшз признаков 59, 63 и 62, сформированных в Ж 242: если ОХХ, то переход к МК 244; если 100, то переход к Ж 267; если 101, то переход к МК 266; если 11Х, то переход к МК 265.

МК 244. Выполняется аналогично МК 217. Анализ признаков 59, 63 и 62, сформированных в МК 243; если ОХХ, то переход к МК 245; если 100, то переход к МК 246; если 101, то переход к МК 218; если 11Х, то переход к МК 238,

МК 245. -Устанавливаются признак Ошибка и триггер 102 блока 14. Конец операции.

Ж 246. Выполняется аналогично МК 222. Переход к Ж 247.

МК 247. Вьтолняется аналогично Ж 223. Переход к Ж 248.

МК 248. Вьтолняется аналогично , .Ж 224. Переход к МК 249. ,

Ж 249. Вьшолняется аналогично Ж 225. Переход к Ж 250.

МК 250. Выполняется аналогично МК 226. Анализ признаков 59, 63 . и 62, сформированных в Ж 249: ес- ди 000, то переход к МК 251; если 001, то переход к МК 258; если 01Х,

3115

то переход к МК 237; если 1ХХ, то переход к МК 269.

МК 251. Выполняется аналогично МК 227. Анализ признаков 59, 63 и 62, сформированных в МК 250: если 000, то переход к МК 252; если 001, то переход к МК 257; если 01Х, то переход к МК 237; если 1ХХ, то переход к МК 262.

МК 252. Выполняется аналогично МК 228. Анализ признаков 59, 63 и 62, сформированных в МК 251: если 000, то переход к МК 253; если 001, то переход к МК 254; если 01Х, то переход к МК 237; если 1ХХ, то переход к МК 264.

МК 253. Выполняется в целом аналогично МК 216. Отличив состоит в том, что содержимое блока 8 пересьтается по входу АЗЗ и затем записывается по адресу второго байта мантиссы результата в блок 1. Выполняется анализ признака 59, сформированного в МК 252: если О, то переход к МК 245; если 1, то переход к МК 222с

МК 255. Выполняется аналогично МК 232. Переход к МК 256.

МК 254. Выполняется аналогично МК 231„ Переход к МК 255.

МК 256. Выполняется аналогично МК,233. Переход к МК 228.

МК 257. Содержимое блока пересылается по входу АЗЗ и затем записы- вается в блок 1 по адресу .второго байта мантиссы результата. Содержимое регистра по третьему адресу из блока 1 пересылается по входу Б34 и через блок 4 и затем записывается в регистр 6. Переход к МК 232.

МК 258. Вьшолняется в целом аналогично МК 257. Отличие состоит всчи-втотом, что на вход Б34 из блока 1

тывается содержимое регистра по втот рому адресу. Переход к МК 232.

МК 259. Уменьшение содержимого счетчика 79 блока 8 на единицу. Из блока 1 -считывается содержимое регистра по второму адресу на вход Б34 и через блок 4 записьшается в регистр 6. Переход к МК 260.

МК 260. Выполняется аналогично Ж 216. Переход к Ж 246.

МК 261. Выполняется в целом аналогично МК 259. Отличие состоит в том, что на вход Б34 из блока 1 считывается содержимое регистра по третьему адресуо Переход к МК 260.

3

32

, МК 262. Вьтолняется аналогично МК 259. Переход к МК 263.

МК 263. Выполняется аналогично МК 253. Переход к МК 222.

МК 264. Выполняется аналогично МК 261. Переход JC МК 263.

МК 265. Содержимое счетчика 79 блока 8 увеличивается на единицу. Переход к МК 238.

МК 266. Содержимое счетчика 79 блока 8 увеличивается на единицу. Из блока 1 считывается на вход АЗЗ содержимое регистра по третьему адресу, которое через блок 4 записывается в регистр 6. Переход к МК 217.

МК 267. Вьтолняется аналогично МК 266. Переход к МК 268.

МК 268. Вьтолняется аналогично МК 216. Переход к МК 246.

МК 269. Вьтолняется аналогично МК 242. Переход к МК 270.

МК 270. Вьтолняется аналогично МК 243. Анализ признаков 59, 63 и 62, сформированных в МК 269: если ОХХ, то переход к МК 271; если 100, то переход к МК 272; если 101, то переход к МК 274; если 11Х, то переход к МК 276.

МК 271. Вьшолняется в целом аналогично МК 244. Отличие состоит в том, что содержимое блока 8 пересылается по входу АЗЗ и записывается в блок 1 по адресу второго байта мантиссы результата. Вьтолняется анализ призна

ков 59, 63

н 62, сформированных в МК 270: если ОХХ, то переход к МК 245; если 100, то переход к МК 222; если 101, то переход к МК 255; если 11Х, то переход к МК 237.

МК 272. Вьтолняется аналогично МК 266. Переход к МК 273.

МК 273. Выполняется аналогично МК 263. Перехо д к МК 222.

МК 274. Выполняется аналогично МК 266. Переход к МК 275.

МК 275. Выполняется аналогично МК 263. Переход к МК 255.

МК 276. Вьтолняется аналогично МК 265. Переход к МК 237.

МК 277. Содепжимое счетчика 79

блока 8 уменьшается Переход к МК 239.

на единицу .

МК 278. Выполняется аналогично МК 242. Переход к МК 279.

МК 279. Вьтолняется аналогично МК 243. Анализ признака 59, сформированного в МК 278: если О, то

переход к МК 280; если 1, то переход к МК 281. .

МК 280. Вьтолняется аналогично МК 271. Анализ признака 59, сформированного в МК 279: если О, то переход к МК 245; если 1, то переход к МК 239.

МК 281. Вьтолняется аналогично МК 265. Переход к МК 239.

МК 382. В блоке 13 содержимое регистра 86 увеличивается на единицу. В блок 1 по адресу старшего байта мантиссы результата записывается константа (10 000 000). Переход к МК 283.

МК 283. Содержимое регистра 86 записывается по адресу порядка результата в регистр 82 блока 13. В блок 1 по адресу двух младших байтов мантис- сы результата записьгоаются нулевые операции. Триггер 102 блока 14 устанавливается в единицу. Конец опера- ции.

; МК 284. В регистр 82 блока 13 по адресу порядка результата записывается

нулевой операнд. В блоке 1 по адресу мантиссы результата записывается нулевой операнд. Установка триггера 102 блока 14 в единицу. Конец операции.

МК 285. В блоке 13 содержимое регистра 86 увеличивается на единицу. Фиксируется признак 89 переноса. В блок 1 по адресу старшего байта ман тиссы результата записывается конс-т станта (10 000 000).. Переход к МК 286 МК 286. Выполняется в целом аналогично МК 280. Отличие состоит в том, что не Вьтолняется установка в единицу триггера 102 блока 14. Конец операции. Анализ признака 89, сформированного в МК 285: если О, то переход к МК 288; если 1, то переход к МК 284.

МК 287. В регистр 82 блока 13 по адресу порядка результата записывается значение, все разряды которого равны единице. По адресу мантиссы результата в блок 1 записьшается значение, все разряды которого равны

единице. Установка в

единицу

триггера 102 блока 14. ции.

МК 288. Установка в триггера 102 блока 14. ции.

единицу

МК 289. Установка в триггера Деление на нуль и триггера 102 блока 14. Конец операции.

Блок-схема алгоритма вычисления функции 1 / УХ для одинарной точности формата с плавающей запятой представлена на фиг. 18 и содержит микрокоманды МК 290-331.

. МК 290. Под управлением поля 17 из блока 1 с входа Б34 с штывается мантисса операнда X, труппа старших разрядов которого поступает на информационные входы блока 12. Значение пробного корня (восемь бит) из блока 12 постз. пает на входы множителя блока 3. Порядок ПХ операнда X в блоке 13 читается из регистра 82 и записывается в регистр 86. Фиксируются признак 92 (значение младшего разряда порядка) и знак 32 операнда. Переход к МК 291.

МК 291. В блоке 13 содержимое регистра 86 увеличив 1ется на ед11Ницу

5

30

35

40

и фиксируется признак 89. Из блока 1 на вх:од Б34 считывается мантисса операнда X и с входов множимого записывается в блок 3. Вьшолняется анализ признаков 92 и 32, сформированных в МК 290: если 00, то переход к МК 328; если 10, то переход к МК 292; если XI, то переход к МК 329.

МК 292. Из блока 1 на вход АЗЗ считывается мантисса X, пересылается через блок 10 (со сдвигом на один разряд вправо) на вход Б34 и записывается по первому адресу в регистры блока 1 и с входов множимого в блок 3, а также поступает на информационные входы блока 12. Значение пробного корня с выходов блока 12 поступает на входы множителя блока 3. ВьтоЛ ie няется анализ признака 89, сформированного в МК 291: если О, то переход к МК 293; если 1, то переход к МК331.

МК 293. В «локе 3 выполняется перемножение операндов. Содержимое регистра с первым адресом записывается в блок 1 по адресу мантиссы операнда X. Переход к МК 294.

МК 294. Коды старших и младших разрядов блока 3 поступают соответственно на первые и вторые входы блока 4. В последнем Вьтолняется сложение, и результат с выходов 44 записывается в регистр 6. Переход к МК 295..

50

55

МК 295. Содержимое регистра 6 поступает на входы множителя, множимого и записывается в блок 3. Переход к МК 296.

МК 296. В блоке 3 вьтолняется пе- 1 емножение операндов. Переход к МК 297.

МК 297, Вьшолняется в целом аналогично МК 294. Отличие состоит в том, что результат с выходов 44 блока 4 записывается в регистр 5. Переход к МК 298.

МК 298. В блойе выполняется операция (регистр 5-1) и результат с выходов 44 записывается в регистр 5. Переход к МК 299.

МК 299. Содержимое регистра 5 пересылается на вход АЗЗ и через блок -. Ю (со сдвигом на один разряд вправо) на вход Б34 и затем через блок 4 записывается в регистр 6, Переход к МК 300.

МК 300. в блоке 4 выполняется one- рация (1 - регистр 6) и результат с выходов 44 записывается в регистр 6. Переход к МК 301.

МК 301, Содержимое регистра 6 передается по входу Б3.4 и с входов мно- жимого записывается в блок 3. Переход к МК 302.

МК 302. Вьтолняется перемножение операндов в блок 3. Из узла 101 блока 14 содержимое триггера 116-2 под управлением поля 112 через элементы 124, 127 с выхода 45 передается по входу АЗЗ и записьтается в знаковые разряды блока 1. Переход к МК 303

МК 303. Вьшолняется аналогично МК 297. Переход к МК 304.

МК 304, Из блока 1 на вход Б34 считывается мантисса операнда X и записьшается с входов множимого в блок 3. Содержимое регистра 5 передается по входу АЗЗ и записывается в регистр с первым адресом регистров блока 1, а второй по старпшнству байт этого числа-передается через мультн плексор 2 на входы множителя и записывается в блок 3. Переход к МК305

МК 305. Вьшолняется аналогично МК 302. Переход к МК 306.

МК 306. Вьшолняется аналогично МК 296. Переход к МК 307.

МК 307. Старший байт содержимого регистра с первым адресом регистров блока 1 с входа АЗЗ через мультиплексор 2 поступает на входы множителя

0

5

0

5

о

и записывается в блок 3. Переход к МК 308. .

МК 308. В блоке 3 вьшолняется перемножение операндов. Содержимое регистра 5 по входу АЗЗ и через блок 10 (со сдвигом на восемь разрядов вправо) передается на вход Б34 и затем с него через блок 4 записывается в регистр 6. Переход К МК 309.

МК 309 Вьшолняется аналогично Ж 303. Переход к МК 310.

МК 310. В блоке 4 выполняется операция (р егистр 5 + регистр 6) ) и 5 .результат с выходов 44 записьшается в регистр 6о Переход к МК 311.

МК 311. Содержимое регистра 6 пе- 1ресьтается по входу Б34 и записьгоает- ся с входов множимого в блок 3. Второй по старшинству байт содержимого регистра, с первым адресом считьшает- ся из блока 1 на вход, АЗЗ и через мультиплексор 2 записьшается с входов 35 множителя в блок 3. Переход к МК 312.

МК 312. Вьшолняется аналогично МК 296. Переход к МК 313.

МК 31Зо Вьшолняется аналогично MIC297. Переход к МК 314.

МК 314. Второй по старшинству байт содержимого регистра считывается из блока 1 на вход АЗЗ и через мультиплексор 2 записывается с входов -35 множителя в блок 3. Переход к МК 315.

МК 315. Вьшолняется аналогично Ж 308. Переход к МК 316.

МК 316. Вьшолняется аналогично Ж 297. Переход к МК 317.

МК 317. В блоке 4 выполняется операция (регистр 5 + регистр 6) и результат с выходов 44 записьшается в регистр 5. Переход к МК 318.

МК 318. Вьшолняется аналогично МК 298. Переход к МК 319.

МК 319, Вьшолняется аналогично МК 299. Переход к МК 320.

МК 320.Вьшолняется аналогично Ж 300, Переход к МК 321.

МК 321 о Вьшолняе тся аналогично Ж 311„ Переход к МК 322,

МК 322. Вьшолняется аналогично МК 296. Переход к МК 323.

МК 323. Бьшолняется аналогично Ж 297, Переход к МК 324,

МК 324, Выполняется аналогично. Ж 307. Переход к МК 325,

МК 325. Вьшолняется аналогично ж; 308, Переход к МК 326,

45

50

55

МК 326. Вьтолняется аналогично Ж 297. Переход к МК 327..

МК.327. В блоке 4 вьтолняется операция (регистр 5 + регистр 6) и резулвтат с выходов 44 записьшается в регистр 5. Содержимое регистра ,86 в блоке 13 пересыпается через сумматор 83, мультиплексор 85 (со сдвигом на один разряд вправо) и записываетг ся в регистр 86. Переход к МК 328.

МК 328. Содержимое регистра 5 пересыпается по входу АЗЗ и записывается по адресу мантиссы результата в блок 1. Содержимое регистра 86 в блоке 13 записывается по адресу порядка результата в регистр 82.

пе-

Установка в единицу триггера 102 блока 14. Конец операции.

МК 329. В блоке 3 вьтолняется ремножение операндов. Порядок ПХ в блоке 13 из регистра 82 пересыпается через сзл 1матор 83, мультиплексор 85 (со сдвигом на один разряд впрапе-

во) и записьшается в регистр 86. Пе- 25 дов увеличивается на 32 микрокоман- реход к МК 294.ды.

МК 330. Установка признака Нулевой операнд. Установка в единицу триггера 102 блока 14. Конец операции.

МК 331е Вьтолняется в целом аналогично МК.293. Кроме того, под управлением поля 27 в регистр 86 блока 13 записывается код, торого содержат единицы к МК 294.

Операции вычитания и сложения с плавающей запятой для чисел двойного формата (п 64) вьтолняются аналоФормула изобретени

30

все разряды ко- Переход