Изобретение относится к вычислительной технике, в частности к устройствам для управления очередностью обслуживания в условиях поступления множества запросов на обслуживание, и может быть использовано при построении различных устройств автоматики и информационно-измерительной техники.

Известно устройство для обработки прерываний, содержащее два триггера, элемент И, а также групповой регистр прерываний, регистр маски, регистр вектора прерывания, группу элементов И-НЕ, элемент И-НЕ и элемент задержки с обусловленными связями между элементами схемы [1]

Недостатками известного устройства являются сложность и невысокое быстродействие из-за применения элементов задержки.

Известно также устройство приоритета, содержащее элемент И, группу элементов ИЛИ, два регистра, группу элементов ИЛИ и элемент задержки с обусловленными связями между элементами схемы [2]

Недостатками этого устройства являются сложность и невысокое быстродействие.

Наиболее близким по технической сущности к предлагаемому изобретению является многоканальное устройство для обработки запросов, содержащее дешифратор, группу элементов И, группу триггеров и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, а также элемент задержки, два элемента И, группу элементов НЕ, вторую группу элементов И, элемент ИЛИ и триггер с обусловленными связями между элементами схемы [3]

К недостаткам прототипа относятся его сложность и невысокое быстродействие из-за применения элемента задержки и счетчика.

Цель изобретения повышение быстродействия и упрощение устройства.

Поставленная цель достигается тем, что в известное многоканальное устройство для обработки запросов, содержащее дешифратор, группу элементов И, группу триггеров и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, введены два элемента ИЛИ-НЕ, причем i-e (i 1,n, где n количество каналов) входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первого элемента ИЛИ-НЕ, дешифратора и первый вход i-го элемента И группы соединены с прямым выходом i-го триггера, тактовый вход которого соединен с i-м входом запроса устройства, вход сброса которого соединен с (n + 1)-м входом дешифратора, (n + 2)-й вход которого соединен с выходом второго элемента ИЛИ-НЕ, первый вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторыми входами элементов И группы, выходы которых являются выходами разрешения устройства, информационные входы группы триггеров соединены с выходом первого элемента ИЛИ-НЕ и вторым входом второго элемента ИЛИ-НЕ, вход сброса i-го триггера соединен с i-м выходом дешифратора, а также тем, что дешифратор содержит последовательно соединенные первую дизъюнктивную, конъюнктивную и вторую дизъюнктивную программируемые логические матрицы, первые n входов дешифратора являются входами первой дизъюнктивной программируемой логической матрицы, (n + 1)-й вход является первым входом второй дизъюнктивной программируемой логической матрицы, (n + 2)-й вход является первым входом конъюнктивной программируемой логической матрицы, а выходы дешифратора являются выходами второй дизъюнктивной программируемой матрицы.

Наличие перечисленных отличительных признаков свидетельствует о том, что изобретение соответствует критерию "новизна".

Заявитель не обнаружил в исследованной патентной и научно-технической литературе многоканальное устройство для обработки запросов с указанной совокупностью отличительных признаков, которые при реализации изобретения обеспечивают достижение положительного эффекта, т.е. предлагаемое техническое решение соответствует критерию "существенные отличия".

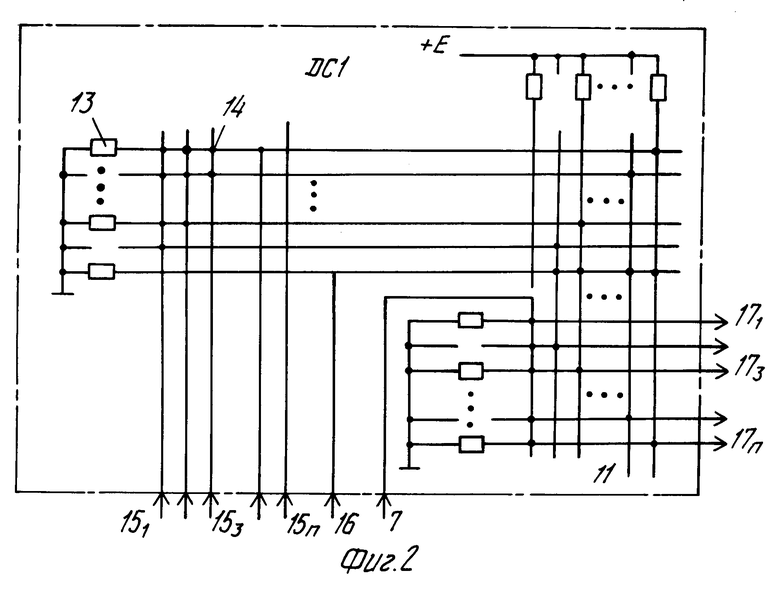

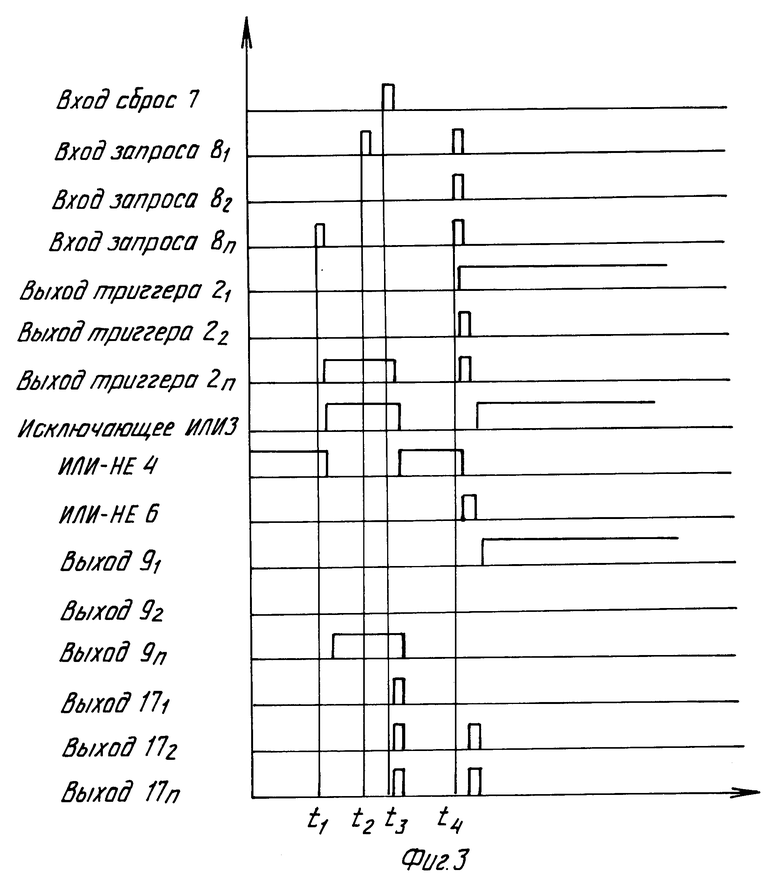

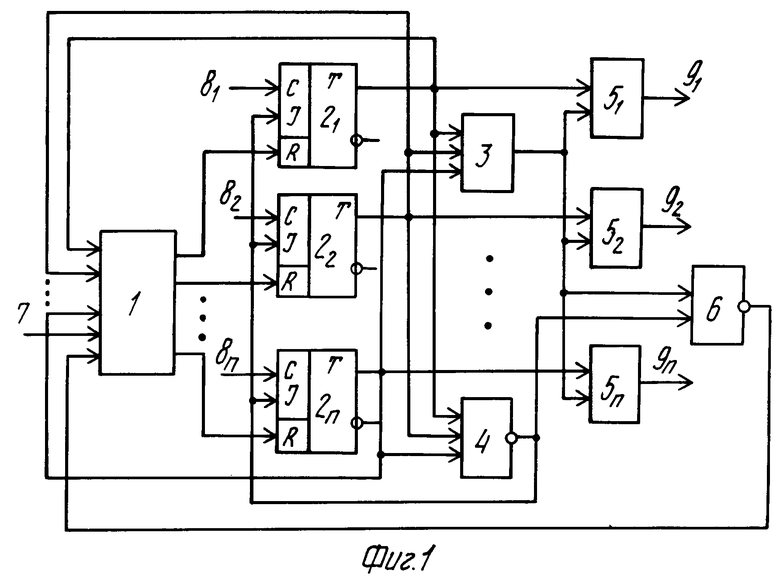

На фиг. 1 представлена структурная схема многоканального устройства для обработки запросов; на фиг. 2 принципиальная схема дешифратора; на фиг. 3 временная диаграмма работы устройства.

Многоканальное устройство для обработки запросов (фиг. 1) содержит дешифратор 1, группу из n триггеров 2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, первый элемент ИЛИ-НЕ 4, группу из n элементов И 5, второй элемент ИЛИ-НЕ 6, вход сброса 7, n входов запроса 8 и n выходов разрешения 9.

Дешифратор 1 (фиг. 1) содержит первую 10 и вторую 11 дизъюнктивные программируемые логические матрицы, конъюнктивную 12 программируемую логическую матрицу, каждая из которых содержит группу нагрузочных резисторов 13 и группу диодов 14 условно показанные в виде точки). В дизъюнктивной программируемой логической матрице аноды диодов 14 соединяются со входами матрицы, а катоды с выходами матрицы и с одним из выводов соответствующего нагрузочного резистора 13, другой вывод которого соединен с общей шиной устройства. В конъюнктивной программируемой логической матрице катоды диодов 14 соединяются с входами матрицы, а аноды с выходами матрицы и с одним из выводов соответствующего нагрузочного резистора 13, другой вывод которого соединен с выводом источника питания Е устройства. Кроме того, дешифратор содержит группу из n входов 15, (n + 1)-й вход 7, (n + 2)-й вход 16 и группу из n выходов 17. Рассматриваемые матрицы являются типовыми логическими элементами и могут быть выполнены на микросхемах К556РТ1 или К712РВ1.

Остальные элементы устройства могут быть реализованы на микросхемах широкого применения серии К155.

Первая 10 дизъюнктивная логическая матрица должна быть запрограммирована так, чтобы на ее i-м выходе выполнялась логическая функция:

yi=  xj-1, y1=0 где Хj сигнал на входе 15 дешифратора 1.

xj-1, y1=0 где Хj сигнал на входе 15 дешифратора 1.

Конъюнктивная 12 логическая матрица должна быть запрограммирована так, чтобы на ее К-м выходе выполнялась логическая функция:

Vk= a yi, v=1 где а сигнал на входе 16 дешифратора 1 (k 2,).

yi, v=1 где а сигнал на входе 16 дешифратора 1 (k 2,).

Вторая 11 дизъюнктивная логическая матрица должна быть запрограммирована так, чтобы на ее К-м выходе выполнялась логическая функция:

Zk= V Z1=b где b сигнал на входе 7 дешифратора 1.

Z1=b где b сигнал на входе 7 дешифратора 1.

Устройство работает следующим образом.

Каналы имеют относительный приоритет между собой, соответствующий номеру канала, т.е. первый канал имеет наивысший приоритет на обслуживание по отношению к остальным каналам.

В исходном состоянии при отсутствии запросных сигналов от абонентов на обслуживание на запросных входах 8 устройства имеются сигналы логического нуля (низкий уровень напряжения). Если все триггеры 2 устройства сброшены в нуль, то на выходе первого 4 элемента ИЛИ-НЕ имеется сигнал логической "1" (высокий уровень напряжения), а на остальных выходах элементов устройства имеются сигналы логического "0". При подаче, например, только на запросный вход 8n n-го канала единичного импульса (сигнал запроса) в момент времени t1 (см. фиг. 3) на прямом выходе триггера 2n устанавливается также на выходах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 и выходе 9n элемента И 5n, а на выходе первого 4 элемента ИЛИ-НЕ устанавливается сигнал логического нуля, который поступает на информационные входы всех триггеров. Поэтому при поступлении, например, на запросный вход 81 первого канала единичного импульса в момент времени t2 (см. фиг. 3) состояние первого 21 триггера не изменяется и устройство обслуживает запрос только n-го канала. По окончании обслуживания на вход сброса 7 устройства в момент времени t3 подается единичный импульс и на всех выходах 17 второй дизъюнктивной программируемой логической матрицы 11 дешифратора 1 формируются единичные импульсы, которые поступают на входы сброса всех триггеров 2, устанавливая их в нуль. При этом сигналы логического нуля последовательно появляются на выходах триггера 2n, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 и выходе 9n n-го элемента И 5n, а на выходе первого элемента ИЛИ-НЕ 4 устанавливается сигнал логической "1". Далее, если в момент времени t4 (см. фиг. 3) на входах запроса первого 81; второго 82 и n-го 8n каналов одновременно появляются единичные импульсы, так как триггеры 2 идентичны, то первый 21, второй 22 и n-й 2n триггеры одновременно устанавливаются в единичное состояние, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 удерживается сигнал логического "0", а на выходах первого 4 и второго 6 элементов ИЛИ-НЕ устанавливаются соответственно нулевой и единичный логические сигналы.

Сигнал логической "1" с выхода второго 6 элемента ИЛИ-НЕ поступает на (n + 2)-й вход 16 дешифратора 1, а именно: на первый вход конъюнктивной логической матрицы 12, поэтому на выходах втором 172 и n-м 17n второй 11 дизъюнктивной логической матрицы появляются сигналы логической "1", по которым триггеры второй 22 и n-й 2n сбрасываются в нуль, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 устанавливается сигнал логической "1", а на выходе второго 6 элемента ИЛИ-НЕ устанавливается сигнал логического "0", который также устанавливается на выходах 17 дешифратора 1. Таким образом, устройство обслуживает запрос наиболее приоритетного канала, т.е. первого, и на его выходе 91 удерживается сигнал логической "1". Для изменения относительного приоритета каналов необходимо перепрограммировать логические матрицы 10-12 в соответствии с заданными приоритетами.

Таким образом, устройство обслуживает запрос, пришедший по времени первым, а при поступлении нескольких запросов одновременно обслуживается запрос, имеющий наивысший приоритет.

Преимуществами предлагаемого устройства по сравнению с прототипом являются упрощение устройства, снижение стоимости и повышение его быстродействия, так как используется 2 (n + 2)-элементов вместо 4 (n + 2) элементов, т. е. в два раза уменьшается количество используемых элементов и исключается использование счетчика и элемента задержки. Кроме того, повышается надежность устройства в целом, так как уменьшается количество используемых элементов и связей между ними без снижения функциональных возможностей устройства.

Предлагаемое устройство реализовано в виде макета и прошло проверку. Его предлагается использовать при реализации высокопроизводительных вычислительных систем.

Применение программируемых логических матриц обеспечивает также возможность программного изменения относительных приоритетов каналов между собой, не изменяя связей между элементами схемы устройства, путем перепрограммирования логических матриц, что также существенно расширяет функциональные возможности устройства, по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2005 |

|

RU2287179C1 |

| Устройство для исследования графов | 1985 |

|

SU1305720A1 |

| УСТРОЙСТВО КОНТРОЛЯ МЕСТОПОЛОЖЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 1992 |

|

RU2042922C1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1999 |

|

RU2152072C1 |

| Устройство ассоциативного распознавания образов | 1985 |

|

SU1330644A1 |

| Ассоциативная однородная обучаемая среда для распознавания объектов | 1983 |

|

SU1149287A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2589317C1 |

| Устройство для программного управления положением объекта | 1984 |

|

SU1193642A1 |

| Многорежимное устройство приоритета | 1990 |

|

SU1805469A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1993 |

|

RU2087939C1 |

Изобретение относится к вычислительной технике, в частности к устройствам для управления очередностью обслуживания в условиях поступления множества запросов на обслуживание, и может быть использовано при построении различных устройств автоматики и информационно-измерительной техники. Цель изобретения повышение быстродействия и упрощение устройства. Многоканальное устройство для обработки запросов содержит дешифратор 1, группу из n триггеров 2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, два элемента ИЛИ НЕ 4, 6, группу из n элементов И 5. 1 з.п. ф-лы, 3 ил.

| Многоканальное устройство для обработки запросов | 1984 |

|

SU1201838A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-08-27—Публикация

1991-07-22—Подача