Изобретение относится к вычислительной технике и может быть использовано при разработке узлов и устройств высокопроизводительных вычислительных систем.

Целью изобретения является повышение быстродействия путем обеспечения суммирования с одновременным округлением.

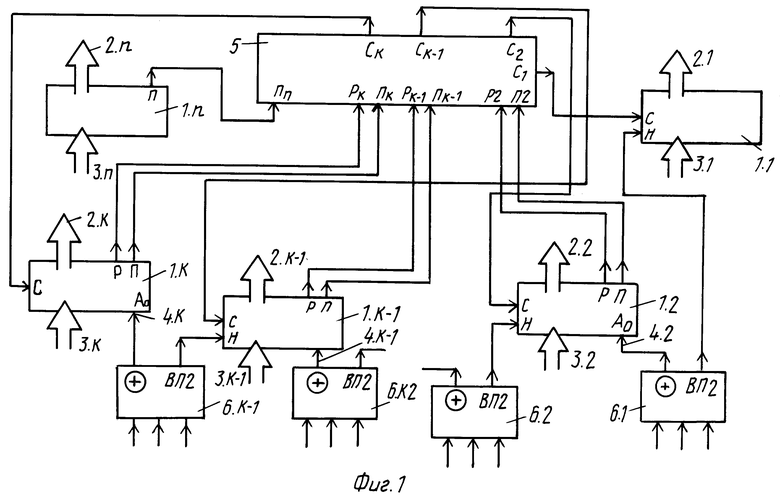

На фиг. 1 приведена схема устройства; на фиг.2 и 3 примеры реализации сумматоров 1-1п; на фиг.4 и 5 примеры реализации сумматора 1.1.

Устройство суммирования с округлением содержит n сумматоров 1.1.1.n, выходы 2,1.2.n, суммы которых являются соответствующими выходами устройства, а входы 3.1.3.n, кроме входов 4.2.4.К старших разрядов со второго по К-й сумматор соответствующими входами устройства, и блок 5 анализа переносов, входы переполнения (П2.Пn по фиг.1) и распространения (Р2.Рn-1), которого соединены с соответствующими выходами П и Р сумматоров, входы переноса С которых соединены с соответствующими выходами С1.Сn-1 блока 5. В устройство дополнительно введены К-1 суммирующих элемента 6.1.6.К-1, выходы суммы которых соответственно соединены с входом 4.2.4.К старшего разряда сумматоров 1.2.1.К, а выходы переноса соответственно соединены с дополнительным входом М младшего разряда сумматоров 1.1.1.К-1, входы элементов 6.1.6.К-1 являются дополнительными входами устройства.

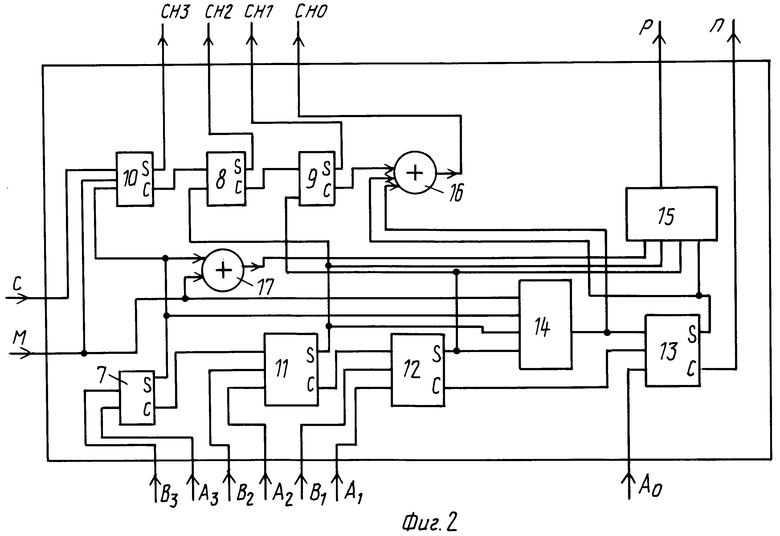

На фиг.2 показана первая возможная реализация сумматоров 1.2.1.К-1. Сумматор содержит полусумматоры 7, 8 и 9 и полные одноразрядные сумматоры 10, 11, 12 и 13, элементы, И 14 и 15, элементы 16, 17 и ИСКЛЮЧАЮЩЕЕ ИЛИ. Входы полусумматора 7 соединены с входами младших разрядов обоих операндов А3 и В3, его выход переноса С соединен с входом сумматора 11, с остальными входами которого соединены входы второго разряда обоих операндов А2 и В2 из отрезка суммирования, выход С сумматора 11 соединен с входом сумматора 12, остальные входы которого соединены с входами третьего разряда операндов А1 и В1 из отрезка суммирования, выход С сумматора 12 соединен с входом сумматора 13, на остальные входы которого поданы сигналы с входа старшего разряда АО и выхода вентиля 14, на входы которого поданы сигналы с выходов полусумматора 7, сумматоров 11 и 12 и входа М дополнительного входа младших разрядов. Сигнал с выхода С сумматора 13 подан на выход П, а выход Р соединен с выходом элемента 15, входы которого соединены с выходами суммы сумматоров 11, 12, 13 и выходом вентиля 17, входы которого соединены с выходом суммы полусумматора 7 и входом М. Выход элемента 16 соединен с выходом СМО старшего разряда суммы, его входы соответственно соединены с выходом суммы сумматора 13, выходом элемента 14 и выходом переноса С полусумматора 9, выход суммы которого соединен с выходом СМ1 второго разряда суммы, его входы соответственно соединены с выходом суммы сумматора 12 и выходом С полусумматора 8, выход суммы которого соединен с выходом СМ2 третьего разряда суммы, а его входы соответственно соединены с выходом суммы сумматора 11 и выходом С сумматора 10, выход суммы которого соединен с выходом СМ3 младшего разряда суммы, его входы соответственно соединены с входами М и С и выходом суммы полусумматора 7.

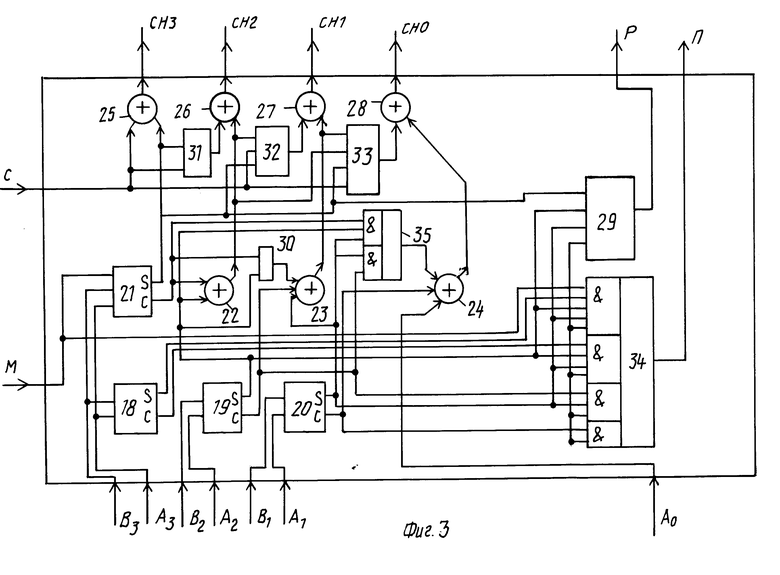

Пример конкретной реализации сумматоров 1.2.1.К-1 (фиг.3) содержит полусумматоры 18, 19 и 20, одноразрядный сумматор 21, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 22-28, элементы И 29-33, элемент 2-3-4-5 И 4 ИЛИ 34 и элемент 2-3 И 2 ИЛИ 35. Входы полусумматоров 18, 19 и 20 соответственно соединены с входами А3 и В3, А2 и В2, А1 и В1 битов соответственно четвертого (младшего), третьего и второго разрядов отрезка суммирования. Входы сумматора 21 соединены с входами М, А3 и В3, входы группы 2И элемента 34 соединены с входом АО и выходом С полусумматора 20. Входы группы 3И элемента 34 соединены выходом суммы полусумматора 20, выходом С полусумматора 19 и входом АО. Входы группы 4И элемента 34 соединены с выходами суммы полусумматоров 19 и 20, выходом С полусумматора 18 и входом АО. Входы группы 5И элемента 34 соединены с выходами суммы полусумматоров 18, 19, 20 и входами АО и М. Выход элемента 34 соединен с выходом П. Входы элемента 29 соединены с выходами суммы полусумматоров 19 и 20 и сумматора 21 и с входом АО. Выход элемента 29 соединен с выходом Р. Входы элемента 22 соединены с выходом С сумматора 21 и выходом суммы полусумматора 19, входы элемента 30 соединены соответственно с входами элемента 22, входы элемента 23 соответственно соединены с выходом суммы полусумматора 20, выходом С переноса полусумматора 19 и выходом элемента 30. Входы группы 3И элемента 35 соединены с выходом С сумматора 21, выходом суммы полусумматора 19 и выходом суммы полусумматора 20. Входы группы 2И элемента 35 соединены с выходом суммы полусумматора 20, выходом переноса полусумматора 19. Входы элемента 24 соединены с выходом С полусумматора 20, выходом элемента 35 и входом АО. Входы элемента 25 соединены с входом С и выходом суммы сумматора 21, с которыми также соединены входы элемента 31, выход которого соединен с первым входом элемента 26, второй вход которого соединен с выходом элемента 22 и входом элемента 32, остальные входы которого соответственно соединены с входами элемента 31. Выход элемента 32 соединен с входом элемента 27, другой вход которого соединен с выходом элемента 23 и входом элемента 33, остальные входы которого соответственно соединены с входами элемента 32. Выход элемента 33 соединен с входом элемента 28, другой вход которого соединен с выходом элемента 24. Выходы элементов 25-28 соответствено соединены с выходами СМ3, СМ2, СМ1 и СМО.

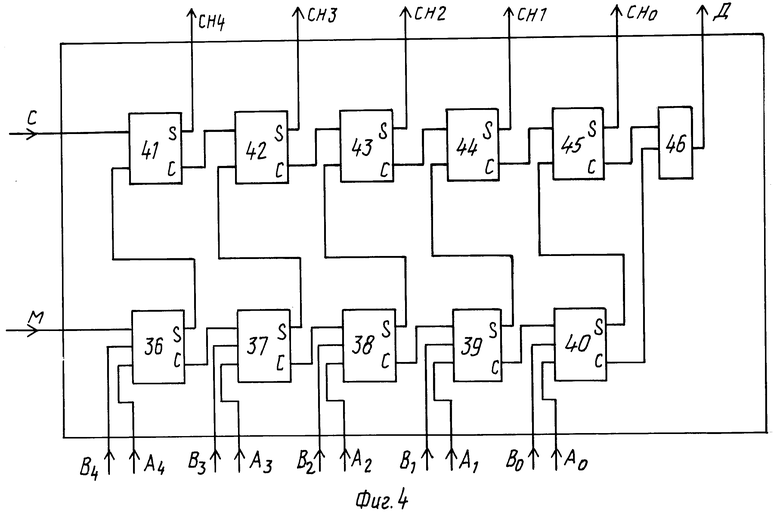

Первый пример конкретной реализации сумматора 1.1 (фиг.4) содержит одноразрядные сумматоры 36-40, полусумматоры 41-45, элемент ИЛИ 46. Входы сумматора 40 соединены с входами АО и ВО и выходом переноса сумматора 39, входы которого соединены с входами А1 и В1 и выходом переноса сумматора 38, входы которого соединены с входами А2 и В2 и выходом переноса сумматора 37, входы которого соединены с входами А3 и В3 и выходом переноса сумматора 36, входы которого соединены с входами А4, В4 и М. Выход элемента 46 соединен с выходом Д дополнительным выходом (переполнения) суммы при суммировании двух операндов, а его входы соединены с выходами переноса сумматора 40 и полусумматора 45, выход суммы которого соединен с выходом СМО, а его входы соединены с выходом суммы сумматора 40 и выходом переноса полусумматора 44, выход суммы которого соединен с выходом СМ1, а его входы соединены с выходом суммы сумматора 39 и выходом переноса полусумматора 43, выход суммы которого соединен с выходом СМ2, а его входы соединены с выходом суммы сумматора 38 и выходом переноса полусумматора 42, выход суммы которого соединен с выходом СМ3, а его входы соединены с выходом суммы сумматора 37 и выходом переноса полусумматора 41, выход суммы которого соединен с выходом СМ4, а его входы соединены с выходом суммы сумматора 36 и входом С.

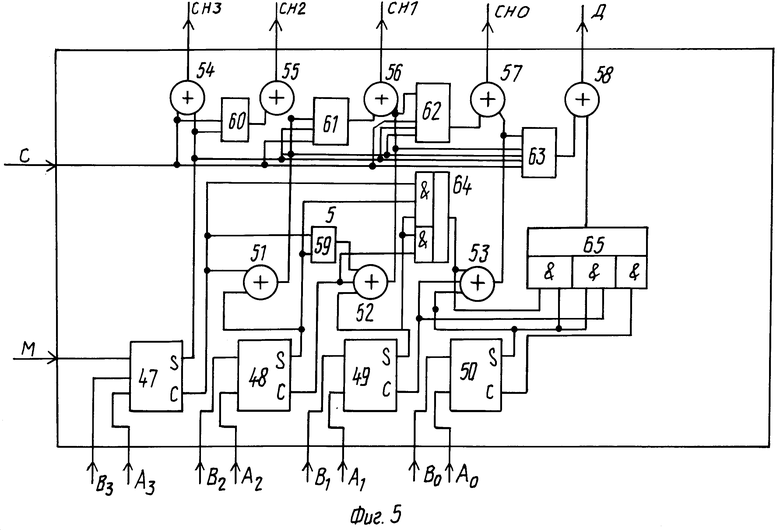

Вторая возможная реализация сумматора 1.1 (фиг.5) содержит сумматор 47, полусумматоры 48, 49 и 50, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 51,58, элементы И 59,63 и элементы 2-3И 2 ИЛИ 64 и 2-2-1И-3ИЛИ 65. Входы сумматора 47 соединены с входами М, А3 и В3. Входы полусумматора 48 соединены с входами А2 и В2. Входы полусумматоров 49, 50 соединены соответственно с входами А1 и В1, АО и ВО. Входы элемента 51 соединены с выходом переноса сумматора 47 и выходом суммы полусумматора 48. Входы элемента 52 соединены с выходами переноса и суммы соответственно полусумматоров 48 и 49 и выходом элемента 59, входы которого соответственно соединены с входами элемента 51. Входы элемента 53 соединены с входами переноса и суммы соответственно полусумматоров 49 и 50 и выходом элемента 64, входы группы 3И которого соединены с выходом переноса сумматора 47 и выходами суммы полусумматоров 48 и 49, а входы его группы 2И соединены с выходами переноса и суммы соответственно полусумматоров 48 и 49. Входы элемента 54 соединены с выходом суммы сумматора 47 и входом С. Входы элемента 55 соединены с выходом элемента 51 и выходом элемента 60, входы которого соответственно соединены с входами элемента 54. Входы элемента 56 соединены с выходами элемента 52 и элемента 61, входы которого соответственно соединены с выходом элемента 51 и входами элемента 60. Входы элемента 57 соединены с выходами элементов 53 и 62, входы последнего из которых соответственно соединены с выходом элемента 52 и входами элемента 61. Входы элемента 58 соединены с выходом элементов 65 и 63, входы последнего из которых соответственно соединены с выходом элемента 53 и входами элемента 62. Выходы элементов 54-57 соединены с выходами соответственно СМ3, СМ2, СМ1 и СМ0. Выход элемента 58 соединен с выходом Д переполнения суммы, также относящимся к выходам суммы.

Входящий в состав устройства сумматор 1.1 работает следующим образом.

Его задача сводится к тому, чтобы сложить старший отрезок суммирования (т.е. старшие разряды обоих операндов) и 2 бита младших разрядов, поступающие на входы М и С. На его выходах суммы формируется результат этого сложения. Для большей ясности рассмотрим работу обоих реализаций сумматора 1.1 (фиг. 6 и 7). Сумматор 1.1 не вырабатывает никаких битов, влияющих на быстродействие всех остальных блоков, входящих в состав устройства (таких, как сигналов Р и П). В сумматоре 1.1 (фиг.4) одноразрядные сумматоры 36,40 осуществляют сложение отрезка суммирования с битом на входе М с последовательным переносом. Полусумматоры 41,45 осуществляют сложение полученной промежуточной суммы с битом на входе С также с последовательным переносом. Элемент 46 служит для получения бита переполнения суммы, который может возникнуть как на стадии суммирования бита со входа М и битов из отрезка суммирования, так и при прибавлении к ним бита с входа С.

В сумматоре 1.1 (фиг.5) одноразрядный сумматор 47 и полусумматоры осуществляют частичное суммирование битов отрезка суммирования и бита на входе М. Затем элементы 51, 52 и 53 и 59 и элементы 64 и 65 из результата частичного суммирования получают окончательную сумму битов отрезка суммирования с битом на входе М. Элементы 54,58, 60,63 осуществляют суммирование предыдущего результата с битом на входе С. Указанная реализация (фиг.4 и 5) предполагает, что сумма операндов без округления не превышает 1.11.1, 01.1 (точкой отделен бит переполнения Д, а после запятой идет разряд округления).

Задача сумматоров 1.2. 1. К заключается в том, чтобы на первом этапе проанализировать биты, поступающие на их входы (в т.ч. на вход АО старшего разряда) и вход М, сформировать сигналы Р и П и отправить их для обработки в блок 5. После этого они формируют сумму битов отрезка суммирования и бита на входе М, с которой на последнем этапе осуществляют суммирования бита, приходящего на вход М.

В сумматоре (фиг.2) одноразрядные сумматоры 11, 12 и 13, полусумматор 7 и элементы 14, 15 и 17 осуществляют формирование суммы битов отрезка суммирования и формирование сигналов Р и П. Элемент 17 необходим для правильного формирования сигналов Р с учетом сигнала на входе М. Элемент 14 необходим для исключения снижения быстродействия и может быть выполнен монтажными средствами; эмиттерное объединение в ЭСЛ или применение многоэмиттерного транзистора в ТТЛ-схемотехниках. Одноразрядный сумматор 10 и полусумматоры 8 и 9 вместе с элементом 16 осуществляют сложение суммы битов отрезка суммирования с битами на входах М и С.

В сумматоре (фиг.3) полусумматоры 18, 19 и 20 осуществляют частичное суммирование битов из отрезков суммирования, по результатам которого элемент 34 с учетом сигнала на входе М вырабатывает бит П. Одноразрядный сумматор 21 суммирует биты младшего разряда отрезка суммирования и бит со входа М, результат этого суммирования используется для правильного формирования бита Р, осуществляемого на элементе 29, который удобно выполнить монтажными средствами. Элементы 22, 23, 24 и 30 и элемент 35 осуществляют совместно с сумматором 21 суммирование отрезка суммирования с битом на входе М, а элементы 25, 26, 27, 28, 31, 32 и 33 осуществляют прибавление к этой сумме бита на входе С. Элементы 31, 32 и 33 для повышения быстродействия также целесообразно выполнить монтажными средствами. При этом сумматоры 1.1.1 могут иметь не только четырехразрядную длину, которая была выбрана исключительно из иллюстративных целей.

Сумматоры 1. К.1.n осуществляют суммирование битов в отрезках суммирования, по результатам чего они формируют биты Р и П, направляя их для дальнейшего анализа на блок 5, сигнал переноса С от которого они затем прибавляют к сумме битов отрезка суммирования. На выходах суммы формируется результат последнего суммирования.

Реализация этих сумматоров очевидна с учетом вышеописанных реализаций, хорошо известна и поэтому здесь не приводится.

Все входы элементов 6.1.6.К-1 равноправны, на выходе суммы формируется результат этой функции от входных битов, а выход переноса 2 находится в "1", если два или три бита на входах находятся в "1", в противном случае в "0". Как уже отмечалось, в качестве этих элементов могут использоваться одноразрядные сумматоры, что позволяет трактовать результат работы этих элементов как суммирование.

Предлагаемое устройство работает следующим образом (фиг.1). Пусть на входы сумматоров, кроме входов АО сумматоров 1.2.1.К, поданы соответствующие биты операндов, 2 старших бита соответствующих отрезков суммирования подаются на входы элементов 6.1.6.К-1. На третий вход одного из этих элементов подается сигнал округления, на третьи входы остальных элементов подается логический "0". Поскольку элементы 6 осуществляют фактически суммирование поданных битов, эта операция не влияет на правильность результата. После этого сумматоры 1.2.1.n суммируют биты на входах М, АО и других входах (кроме, разумеется, входа С) и формируют сигналы П и Р, которые поступают на соответствующие входы блока 5, вырабатывающего соответствующие сигналы С1.С.n-1, которые в свою очередь поступают на соответствующие входы С сумматоров 1.1. 1. n-1. Сумматоры же согласно своему алгоритму суммируют бит С с суммой от сложения отрезка суммирования и бита на входе М. Выходы сумматоров являются соответствующими выходами устройства.

Как уже отмечалось выше, для каждого сумматора в отношении его битов П и Р справедливо то, что они не равны 1 одновременно. Это обеспечивает правильность функционирования предлагаемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНВЕЙЕРНЫЙ АРИФМЕТИЧЕСКИЙ УМНОЖИТЕЛЬ | 2013 |

|

RU2546072C1 |

| Параллельный сумматор | 2016 |

|

RU2635247C1 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018923C1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке узлов и устройств высокопроизводительных вычислительных систем. Цель изобретения - повышение быстродействия за счет обеспечения суммирования с одновременным округлением. Устройство суммирования с округлением содержит n сумматоров 1.1.1.n, выходы 2.1.2.n сумм которых являются соответствующими выходами устройства, а входы 3.1.3.n, кроме входов 4.2.4.K старших разрядов с второго по K-й сумматоров - соответствующими входами устройства, и блок 5 анализа переносов, входы переполнения и распространения которого соединены с соответствующими выходами П и Р сумматоров, входы переноса С которых соединены с соответствующими выходами C1...Cn-1 блока 5. В устройство дополнительно введены K-1 суммирующих элементов 6.1.6.K-1, выходы суммы которых соответственно соединены с входом 4.2.4.K старшего разряда сумматоров 1.2.1.K, а выходы переноса 2 с дополнительным входом М младшего разряда сумматоров 1.1.1.K-1. Входы элементов 6.1.6.K-1 являются дополнительными входами устройства. Введение дополнительных элементов 6.1.6.K-1 позволяет избежать ситуации П-Р-1 для любого отрезка суммирования при наличии сигнала округления, и позволяет производить операции суммирования и округления одновременно. 5 ил.

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, содержащее n сумматоров и блок анализа переносов, входы младших разрядов первого и второго операндов устройства соединены с первым и вторым информационными входами соответствующих разрядов устройства, выходы суммы сумматоров являются выходами результата устройства, i-й вход переполнения и распространения переносов (где i 2, 3. K < n) блока анализа переносов соединен с соответствующим одноименным выходом i-го сумматора, вход переноса (i 1)-го сумматора соединен с соответствующим выходом переноса блока анализа переносов, отличающееся тем, что, с целью повышения быстродействия за счет выполнения суммирования с округлением, устройство содержит (K 1) суммирующих элементов, причем выход суммы (i - 1)-го суммирующего элемента соединен с входом старшего разряда первого операнда i-го сумматора, выход переноса (i 1)-го суммирующего элемента соединен с дополнительным входом младшего разряда (i 1)-го сумматора, первый и второй информационные входы (i 1)-го суммирующего элемента являются входами соответствующих разрядов первого и второго информационных входов устройства, входы переноса K суммирующих элементов являются входами соответствующих переносов устройства.

| Питце У., Шенк К., Патент США N 3925652, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Полупроводниковая схемотехника, М., Мир, 1983, с | |||

| Приспособление, обнаруживающее покушение открыть замок | 1910 |

|

SU332A1 |

Авторы

Даты

1995-09-10—Публикация

1990-12-19—Подача