Изобретение относится к вычислительной технике, в частности к устройствам обработки массивов информации, и может быть использовано при построении как универсальных ЭВМ, так и специализированных вычислительных машин, ориентированных на исполнение в микроэлектронной интегральной технологии.

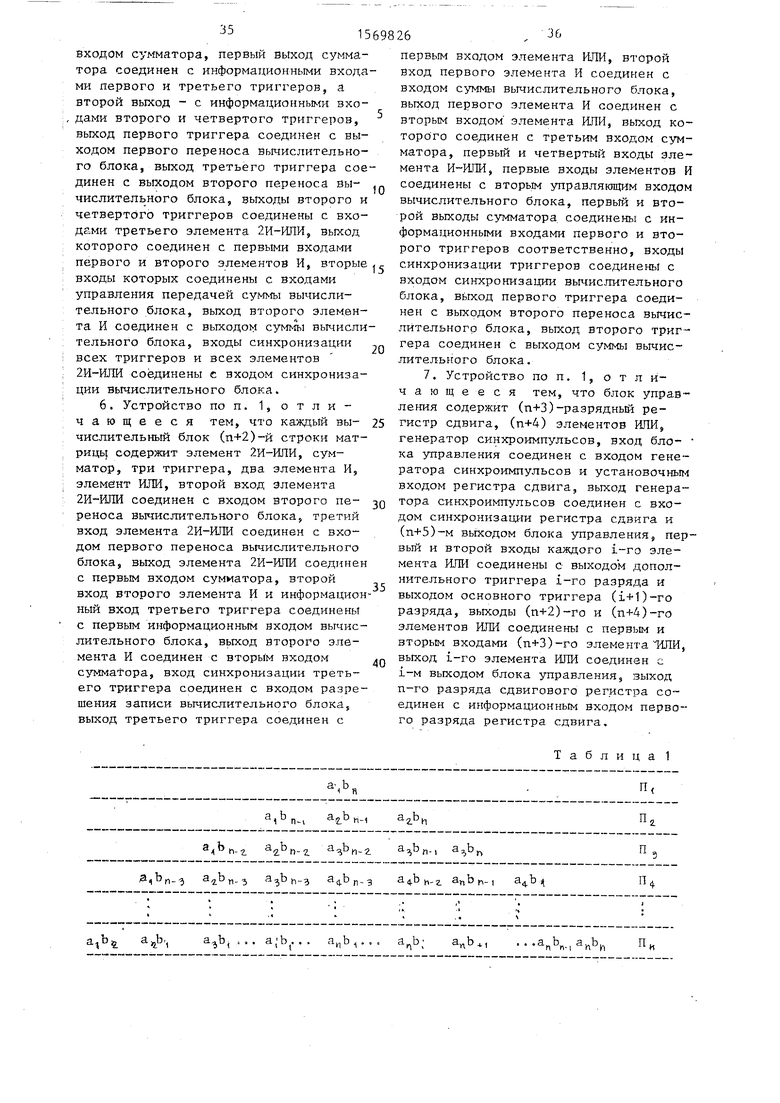

На фиг. 1а,б представлена структурная схема устройства; на фиг. 2 - 6 - функциональные схемы вычислительных блоков, на основе которых формируется вычислительная матрица устройстваj на фиг. 7 - функциональная схема блока управления„

Структурная схема устройства представлена на фиг. 1.

Устройство содержит матрицу 1 вычислительных блоков и блок 2 управления. Матрица 1 вычислительных блоков содержит п информационных входов 3 i() и один информационный выход 4. Матрица состоит из п+2 строк, каждая из первых п+1 строк состоит из п+2 вычислительных блоков. Число входов определяется количеством пар сомножителей, результат считывается с информационного выхода 4.

Управление устройством осуществляется по управляютему 5.

На фиг, 2 представпрна ф гнкцио- нальная схема вычисгшгетьного блока первого типа, из которого формируются первые п строк магрицп 1, начиная с второго по п-и сгоибоп.

ГО

ЈЛ

Клок содержит элемент 2И-ИЛИ 6„ cyvrMJTop 7, триггеры 8 и 98 элемент ИЛИ 103 элементы И 11 и 12, триггеры 13 и 14, элементы 2И-ИЛИ 15 и 16, -.ггнекш И 17 и 8Э триггеры 19 и 20 и элемент 2И-ИЛИ 21.

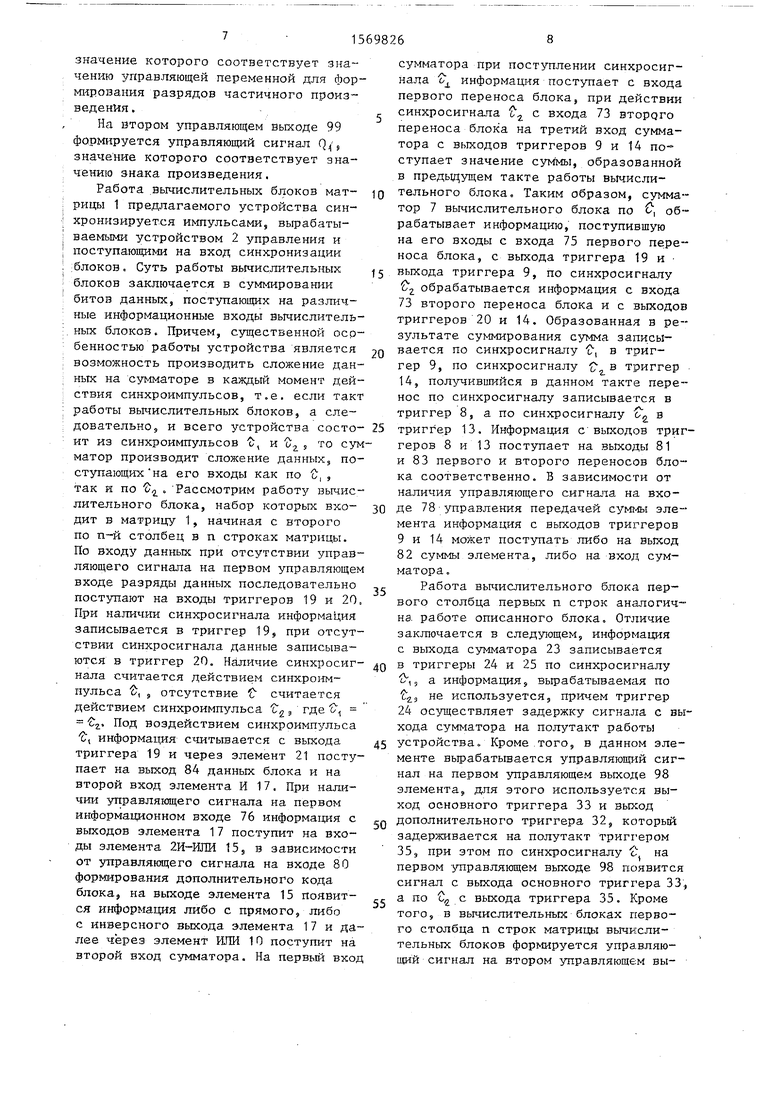

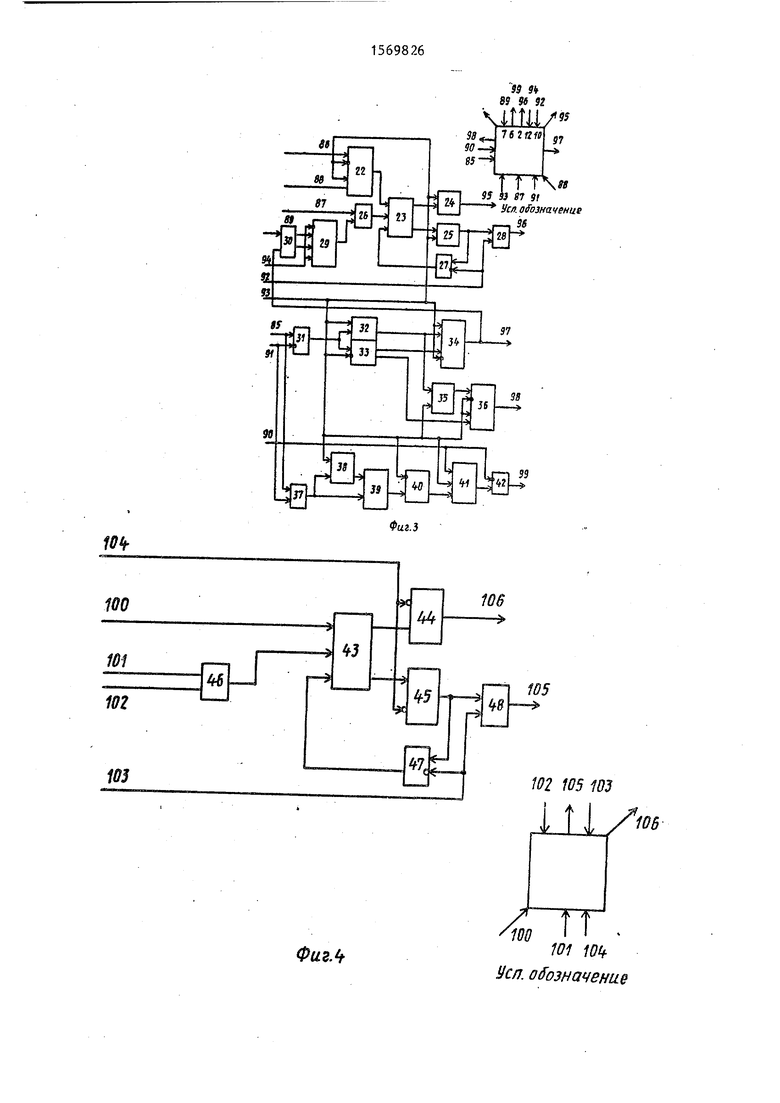

На фиг с 3 представлена функцио-- :альная схема вычислительного блока второго тишц предназначенного для Аормиоования первого столбца первых п строк, Блок содержит элемент 2И-ИЛИ 22; сумматор 23, триггеры 24 и 25s элемент ИЛИ 26S элементы И 27 и 28„ элемент 2И-ИЖ 29, элементы И 30 и 31 триггеры 32 и 33,, элемента 2И--ИЛИ 3, триггер 35з элемент 2И-ИЛИ 363 элемент И 37, триггер 38, полусумматор 39, триггеры 40 и 41s элемент И 47,

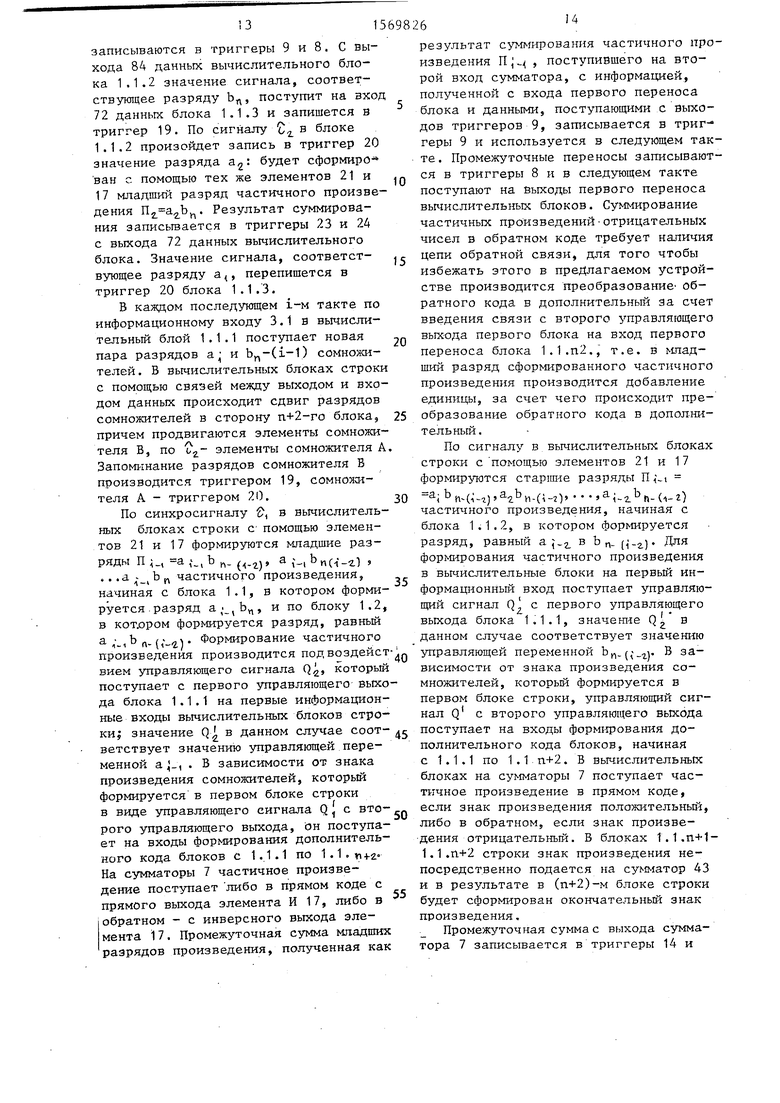

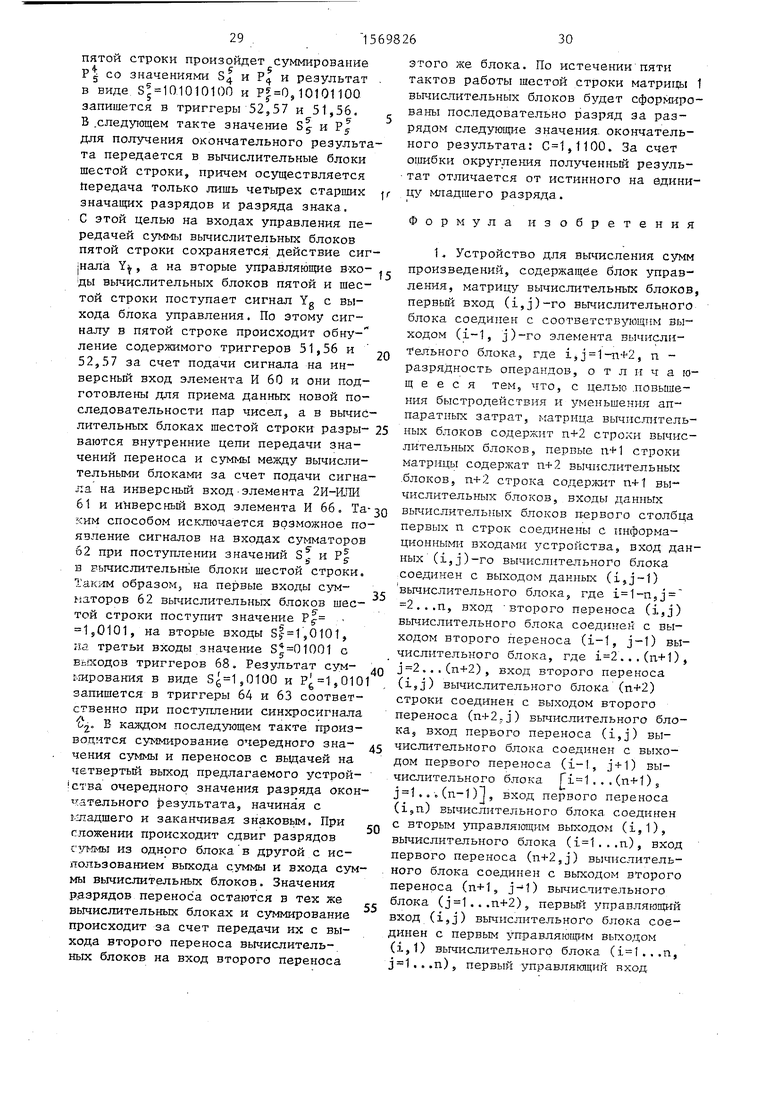

1 а фит „ 4 представлена функциональ ная схема вычислительного блока третьего типа, из которого формируются (п |)-й и Оо+2)-й столбцы первых п стоок матршфь Блок содержит сумма-тор 43, два триггера 44 и 45., эле чгент ИЛИ 46S два элемента И 47 и 48,

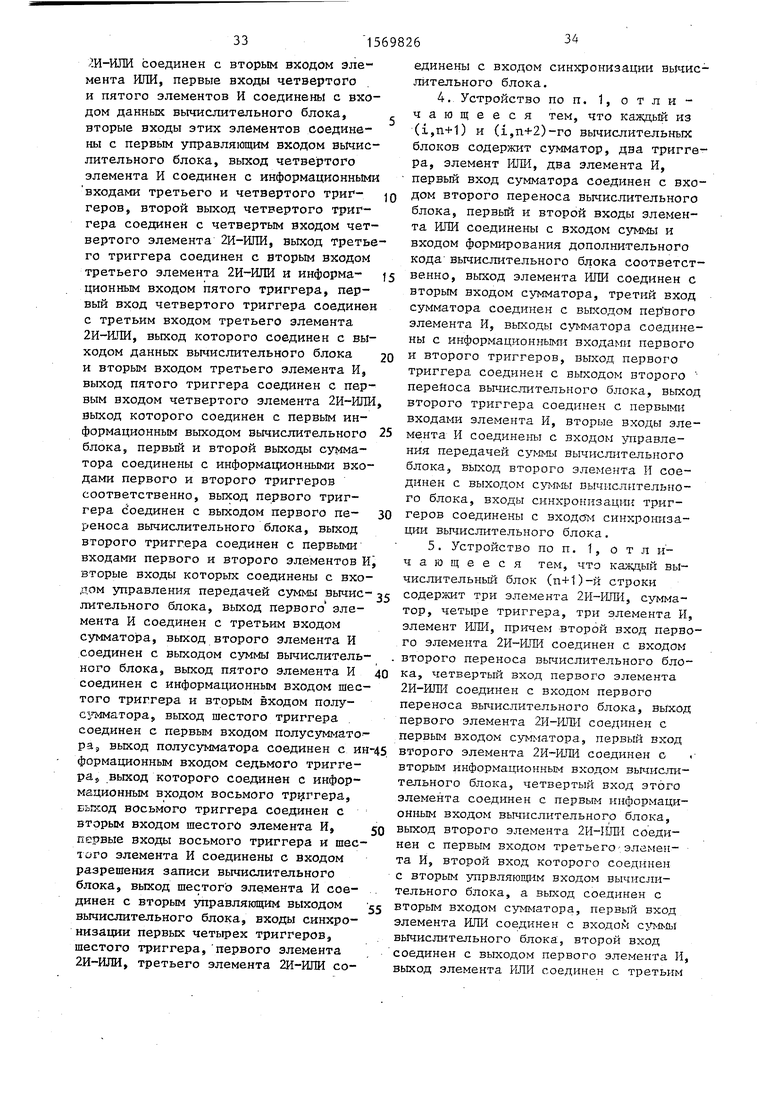

На фиг„ 5 представлена фунциональ- няя о-ема вычислительного блока четвертого типа5 предназначенного для формирования (п+1)й строки матрицы 1 (блоки I о 1 . (n-M)-i.(ти-2) „(rvt 1) „ Блок содержит элемент 2И-ИЛИ 499 сумматор 50, триггеры 5i и 52Э элемент ИЛИ 539 элементы И 54 и 55s триггеры 56 и 57S элементы 2И-ИЛМ 58 н 59, элемент ИбО

На фит, 6 представлена функциональ ная схема вычислительного блока для сЬзрМ Оования (п+2)-й строки матрицы. Блок содержит элемент 2И-ИЛИ 61, сум- матоо 625 триггеры 63 и 64s элемент ИЛИ 65 элементы И 66 и 67, триггер 68 ,

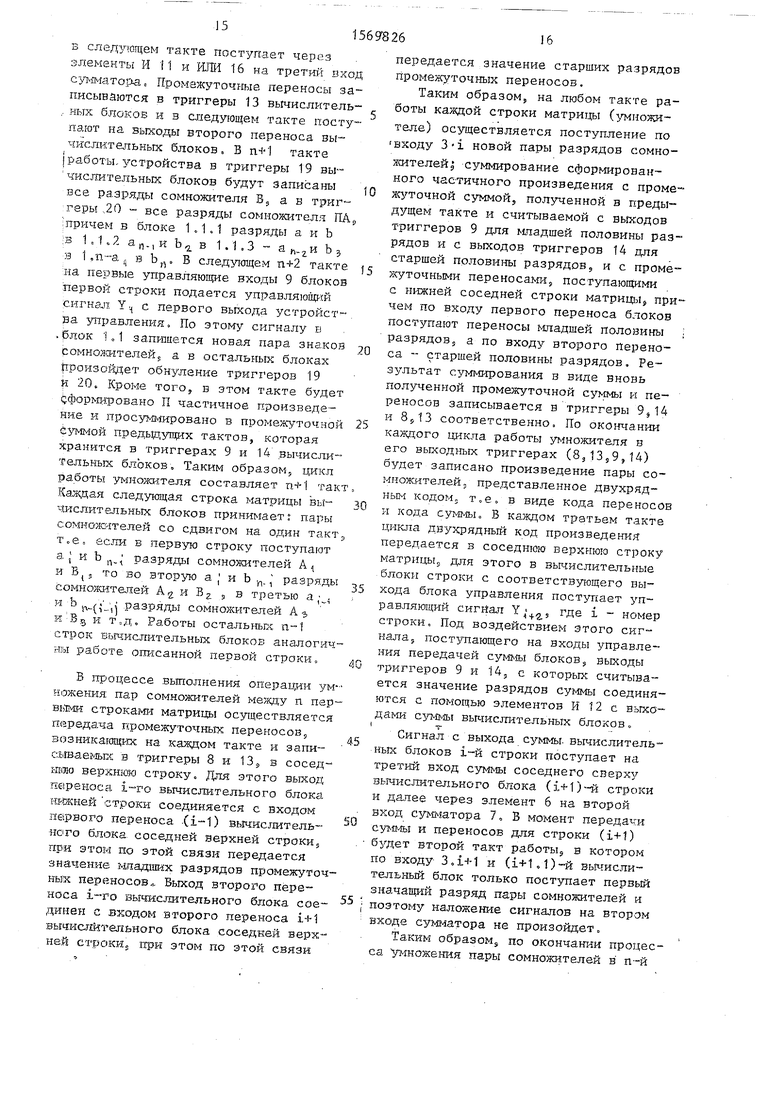

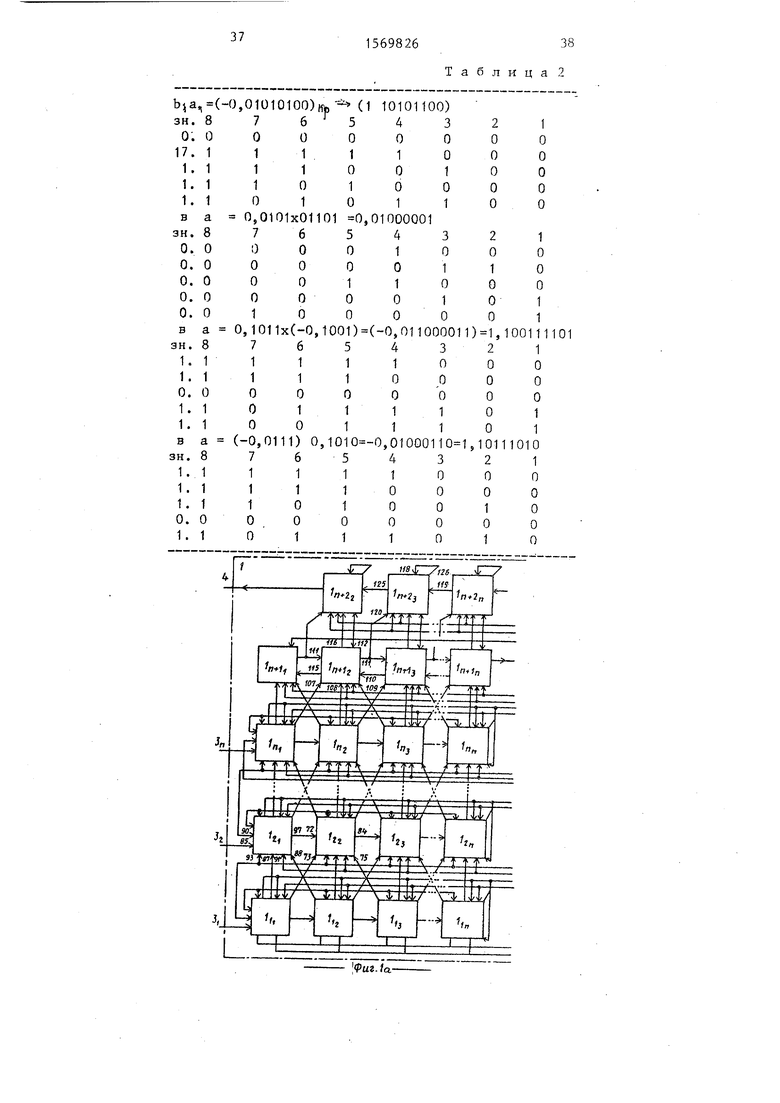

На фиг о 7 представлена функциональная скема блока 2 управления, который содержит генератор 69 синхроимпуль- сов, (п- г-З)-разрядный сдвиговый регистр 70з состоящий из двойных M-S трчтг егов, п-(4 элемента ИЛИ 71 i (i i--n+4 )

Вычислительные блоки содержат следующие входы/выходы,

Вычислительный блок первого типа (фиг„2) содержит вход 72 данных, вход 73 второго переноса, вход 74 суммы вход 75 первого переносаs информационный 76 к управляющий 77 входы, вход

78управления передачей суммы, вход

79синхронизации, вход 80 формирования дополнительного- кода, выход 81

первого переноса, выход 82 суммы, выход 83 второго переноса, выход 84 данных ,

Вычислительный блок второго типа (фиг.З) содержит вход 85 данных, вход 86 второго переноса, вход 87 суммы, вход 88 первого переноса, информационный вход 89, вход 90 разрешения записи, управляющий вход 91, вход 92 управления передачей суммы, вход 93 синхронизации,, вход 94 формирования дополнительного кода, выход 95 первого переноса, выход 96 суммы, выход 97 данных, первый управляющий выход 98„ второй управляющий выход 99.

Вычислительный блок третьего типа (фиг. 4) содержит вход 100 перекоса, вход 101 суммы, вход 102 формирования дополнительного кодаа вход 103 управления передачей суммы, вход 104 синхронизации, выход 105 суммы, выход 106 переноса.

Вычислительный блок четвертого типа (фиг,5) содержит вход 107 второго переноса, вход 108 суммы, вход 109 первого переноса, первый 110 и второй 111 информационные входыэ управляющий вход 112, вход 113 управления передачей суммы, вход 114 синхронизации,, выход 115 первого переноса, выход 116 суммы, выход 117 второго переноса о

Вычислительный блок (фиг, 6) содержит вход 118 второго переноса, вход 119 суммы, вход 120 первого переноса, информационный вход 121, управляющий вход 122, вход 123 разрешения записи, вход 124 синхронизации, выход 125 суммыэ выход 126 переноса,

Для удобства чтения схем приведена сводная таблица входов/выходов:

Входы вычислительных элементов матрицы по своему функциональному назначению разделены на 12 типов, а именно: входы 72 и 85 данных9° входы 75, 88Р109 и 120 первого переноса входы 73,865100,107 и 118 второго переноса, входы 74S87S101,108 и 119 суммы первые информационные входы 76, 89,110 и 121; второй информационный вход 111| вторые управляющие входы 112 и 12Я; входы 90 и 123 разрешения записи| первые управляющие входь 77 и 91| входы 78, и 113 управления передачей суммы| входы 80,94 и 102 формирования дополнительного ксда| входы 79,935104,114 и 124 синхронизации,

51

Выходы вычислительных элементов также подразделяются по функциональному назначению: выходы 81,95 и 115 первого переноса; выходы 83,106,117 и 126 второго переноса; выходы 82,96 105,116 и 125 суммы; выходы 84 и 97 данных; первый управляющий выход 98; второй управляющий выход 99.

Устройство функционирует следующи образом.

По входам 72 и 85 данных на каждо такте работы устройства в вычислителные блоки первых п строк производитс перезапись разрядов сомножителей с в хода данных соседнего слева вычислительного блока. Входы 75,88 и 109 первого переноса (i,j)-ro вычислительного элемента в строках матрицы с 1-й по (п+1)-й предназначены для приема переноса, возникающего на выходе первого переноса в (i-1, j + 1) вычислительном блоке при сложении младших разрядов данных при действии синхроимпульса Ј, . В (п+2)-й строке по входу 120 первого переноса осуществляется прием разрядов переноса из (п+1)й строки при наличии управляющего сигнала на входе 122.

Входы 73,86,100,107 (i,j) второго переноса вычислительного блока в строчках с 1-й по (п+1)-ю матрицы предназначены для приема переноса, возникающего при сложении старших рязрядов данных с выхода второго пе- рлноса в (i-1, j-1) вычислительном

блоке при действии синхроимпульса Ј2, В (п+2)-й строке на вход 118 второго переноса поступает сигнал переноса с выхода второго переноса своего же вычислительного блока.

Входы 74,87,101 и 108 суммы (i,j) вычислительных блоков в (п+1) строках матрицы предназначены для приема разряда суммы, возникающего на выходе суммы (i-1,j) вычислительного блока при наличии управляющего сигнала на входе управления передачи суммы. В (п+2)-й строке на этот вход 119 суммы поступает значение суммы с соседнего справа вычислительного блока.

Первые информационные входы 76 и 89 (i,j) вычислительного блока, где , , предназначены для приема сигнала с первого управляющего выхода (1,1) вычислительного блока к формирования соответствующего разряда частичного произведения. В (п-Н)-й и (п+2)-м столбцах матрицы на этот

10

вход

15

20

25

02 поступает сигнал для формирования дополнительного кода, в (п+1)-и строке матрицы на первый информационный вход 110 поступает сигнал переноса с соседнего справа вычислительного блока, в (п+2)-й строке матрицы на первый информационный вход 121 поступает значение суммы с (п+1)-и строки матрицы при наличии управляющего сигнала на входе 122.

Второй информационный вход 111 в вычислительных блоках (п+1)-и строки матрицы предназначен для приема сигнала переноса с выхода 117 второго переноса соседнего слева вычислительного блока. На управляющие входы 112 и 122 вычислительных блоков (п+1) и (п+2) строк поступает сигаал с выходов устройства управления. При поступлении сигнала на вход 112 в вычислительных блоках (п+1)-й строки запрещается прием информации по 110 и 111 входам, в вычислительных блоках (п+2)-и строки происходит запрещение приема информации по входам 118 и 1-19 разрешения приема информации по входам 120 и 121.

Вход 90 разрешения записи в вычис30 лительных блоках первого столбца в п первых строках предназначен для управления записи информации в триггер 41, в вычислительных блоках (п+2)-и строки при наличии сигнала на этом входе 123 происходит запись информации с входа 121 в триггер 68.

Первые управляющие входы 177 и 91 в вычислительных блоках первых 1г строках предназначены для запрещения пе4Q редачи информации между вычислительными блоками, при наличии на них управляющего сигнала с выходов устройства управления.

При наличии управляющего сигнала на входах 78,92S103 и 113 производит ся передача значения разрядов суммы в верхний соседний вычислительный блок. На вход синхронизации всех вычислительных блоков подаются синхроимпульсы для синхронизации работы вычислительных блоков.

При наличии сигнала на входах 80 и 94 формирования дополнительного кода производится преобразование прямого кода разрядов частичного произведения в дополнительный код.

На первом управляющем входе 98 вычислительных блоков первого столбца формируется управляющий сигнал Q,

35

5

0

5

значение которого соответствует значению управляющей переменной для формирования разрядов частичного произведения .

На втором управляющем выходе 99 формируется управляющий сигнал Q,, , значение которого соответствует значению знака произведения.

Работа вычислительных блоков матрицы 1 предлагаемого устройства синхронизируется импульсами, вырабатываемыми устройством 2 управления и поступающими на вход синхронизации блоков. Суть работы вычислительных блоков заключается в суммировании битов данных, поступающих на различные информационные входы вычислительных блоков. Причем, существенной особенностью работы устройства является возможность производить сложение данных на сумматоре в каждый момент действия синхроимпульсов, т.е. если такт работы вычислительных блоков, а следовательно, и всего устройства состоит из синхроимпульсов Ј, и Јг j то сумматор производит сложение данных, поступающих на его входы как по С, , так и по Ј4 Рассмотрим работу вычислительного блока, набор которых входит в матрицу 1, начиная с второго по п-и столбец в п. строках матрицы. По входу данных при отсутствии управляющего сигнала на первом управляющем входе разряды данных последовательно поступают на входы триггеров 19 и 20. При наличии синхросигнала информация записывается в триггер 19, при отсутствии синхросигнала данные записываются в триггер 20. Наличие синхросигнала считается действием синхроимпульса Ј, s отсутствие Ј считается действием синхроимпульса Ј2, где Сг, Под воздействием синхроимпульса Ј, информация считывается с выхода триггера 19 и через элемент 21 поступает на выход 84 данных блока и на второй вход элемента И 17. При наличии управляющего сигнала на первом информационном входе 76 информация с выходов элемента 17 поступит на входы элемента 2И-ИПИ 15, в зависимости от управляющего сигнала на входе 80 формирования дополнительного кода блока на выходе элемента 15 появится информация либо с прямого, либо с инверсного выхода элемента 17 и далее через элемент ИЛИ 10 поступит на второй вход сумматора. На первый вход

5

0

5

0

5

0

45

50

55

сумматора при поступлении синхросигнала информация поступает с входа первого переноса блока, при действии синхросигнала с входа 73 второго переноса блока на третий вход сумматора с выходов триггеров 9 и 14 поступает значение суммы, образованной в предыдущем такте работы вычислительного блока. Таким образом, сумма-тор 7 вычислительного блока по Ј, обрабатывает информацию, поступившую на его входы с входа 75 первого переноса блока, с выхода триггера 19 и выхода триггера 9, по синхросигналу обрабатывается информация с входа 73 второго переноса блока и с выходов триггеров 20 и 14. Образованная в результате суммирования сумма записывается по синхросигналу Ј, в триггер 9, по синхросигналу в триггер 14, получившийся в данном такте перенос по синхросигналу записывается в триггер 8, а по синхросигналу в триггер 13. Информация с выходов триггеров 8 и 13 поступает на выходы 81 и 83 первого и второго переносов блока соответственно. В зависимости от наличия управляющего сигнала на входе 78 управления передачей суммы элемента информация с выходов триггеров 9 и 14 может поступать либо на выход 82 суммы элемента, либо на вход сумматора.

Работа вычислительного блока первого столбца первых п строк аналогична работе описанного блока. Отличие заключается в следующем, информация с выхода сумматора 23 записывается в триггеры 24 и 25 по синхросигналу С,з а информация, вырабатываемая по Ј2Э не используется, причем триггер 24 осуществляет задержку сигнала с выхода сумматора на полутакт работы устройства. Кроме того, в данном элементе вырабатывается управляющий сигнал на первом управляющем выходе 98 элемента, для этого используется выход основного триггера 33 и выход дополнительного триггера 32, который задерживается на полутакт триггером 35, при этом по синхросигналу Ј на первом управляющем выходе 98 появится сигнал с выхода основного триггера 33, а по С2 с выхода триггера 35. Кроме того, в вычислительных блоках первого столбца п строк матрицы вычислительных блоков формируется управляющий сигнал на втором управляющем выходе 99 блока, который равен сумме по mod 2 битов данных, поступивших в блок по входу 85 данных при наличии управляющего сигнала на первом управляющем входе 91. Информация, поступившая в блок по синхросигналу и , задерживается триггером 38 на полутакт и на входе полусумматора 39 сов- .падает по времени с информацией, поступившей по синхросигналу «/2 , и далее, сложившись, записывается в триггер 40 и затем при наличии управляющего сигнала на входе 90 разрешения

значением, записанным в триггере 68, при этом сумма и перенос поступают соответственно в триггеры 64 и 63. При отсутствии управляющего сигнала сумматор 62 принимает информацию с входа 118 второго переноса и входа 119 суммы блока.

В матрице вычислительных блоков первые п строк вычислительных блоков формируют п умножителей, осуществляющих умножение поступающих сомножителей произвольного знака. Сомножители поступают в умножители с информацион

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство вычисления сумм произведений | 1990 |

|

SU1718216A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для умножения | 1987 |

|

SU1481744A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

Изобретение относится к вычислительной технике и может использоваться для создания высокопроизводительных специализированных и универсальных ЭВМ. Цель изобретения - повышение быстродействия и уменьшение аппаратных затрат. Для достижения поставленной цели в устройстве, представляющем собой регулярную матрицу вычислительных блоков, вычислительные блоки выполнены разнотипными (всего пять типов). Операции над данными и переносами разнесены во времени и соответствуют длительности и паузе синхронизирующего импульса. Пары чисел поступают последовательными кодами. Повышение быстродействия достигается за счет разнесения во времени и пространстве обработки данных и переносов, конвейеризации этих процессов при выполнении векторной операции. 8 ил.

записи записывается в триггер 41. Бы- jj ных входов 3 последовательным кодом числительные блоки (п+1) и (п+2)-го разряд за разрядом в каждом такте ра- столбцов суммируют по синхросигналу боты устройства. Под тактом работы Отданные, поступающие в блок по входу 100 второго переноса, входу 101

устройства .понимается сдвиг числа на один разряд. Количество пар сомножисуммы и входу 102 формирования дополнительного кода с суммой, образованной в предыдущем такте. Образованные в данном такте перенос и сумма в следующем такте появляются на выходе 106 второго переноса блока, и в зависимости от значения управляющего сигнала на входе 103 управления передачей суммы блока, либо на выходе 105 суммы, либо вновь поступает на вход сумматора 43.

Вычислительные блоки (п+1)-и строки матрицы по синхросигналу Ј, суммирует сигналы, поступающие с входа i 109 первого переноса и информационно- гс входа со значением суммы предыдущего такта, которое хранится в триггере 52. Полученные по синхросигналу в данном такте перенос и сумма записываются в триггерах 51 и 52 соответственно. Ш. синхросигналу о2 сумматор 50 складывает сигналы, поступающие с входа 107 второго переноса и второго информационного входа 111 блока со значением суммы предыдущего

такта, которое хранится в триггере 57. д5 строк таблицы частичных произведений. Полученные перенос и сумма эаписы- В (п+1)-и строке матрицы вьтчисли- ваются в триггеры 55 и 57 соответственно. Наличие управляющего сигнала на втором управляющем входе 112 запрещает подачу сигналов с первого и

тельных элементов производится суммирование данных, которые поступают на каждом такте работы устройства из 50 строки матрицы.

второго информационных входов 110 и 1 1 блока на сумматор.

Вычислительные блоки (п+2)-й строки работают по синхросигналу, причем при наличии управляющего сигнала на втором управляющем входе 122 сумматор 62 суммирует данные, поступающие с входа 120 первого переноса и первого информационного входа 121 блока со

ных входов 3 последовательным кодом разряд за разрядом в каждом такте ра- боты устройства. Под тактом работы

устройства .понимается сдвиг числа на один разряд. Количество пар сомножи

телей определяется числом информационных входов в матрицу вычислительных ,блоков. Каждый умножитель реализует алгоритм согласно табл.1, которая приводится для случая п-разрядных сомножителей:

,а4аэ. . .а у, и ВНэ Ь,.. ,ЬП.

Суммирование строк таблицы позволяет получить результат умножения чисел А и В. Управляющими переменными для левой половины таблицы является последовательность значений разрядов сомножителя В, начиная с младшего разряда bh для верхней строки и кончая разрядом Ь{ для нижней строки. Для правой половины таблицы управляющими переменными являются значения разрядов сомножителя А - от старшего разряда а4 до младшего ап . Таким сгбразом, при подаче в устройство двух сомножи- телей последовательным кодом, причем один из сомножителей старшими разрядами вперед, а второй - младшими, можно совместить введение чисел с операцией формирования и суммирования

строк таблицы частичных произведений. В (п+1)-и строке матрицы вьтчисли-

тельных элементов производится суммирование данных, которые поступают на каждом такте работы устройства из строки матрицы.

Последняя (п+2)-я строка матрицы преобразует двухрядный код, поступающий в нее из (п+1)-и строки в окончательный результат, представляющий со- бой сумму парных проичведений сомножителей. Работа матрицы вычислительных элементов состой г и следующем: по информационном . 1 в первую строку матрицы в HI ном такте по И1569826

значения знаков первой пары

пр ря ра 19

сомножителей: ,, b,| b .Ј . о ,b

,аи и

где п - разрядность сомножителей, последовательно друг за другом: по Ј, знак Ь& одного сомножителя, по €г знак а0 - второго. Под воздействием управляющего сигнала Yf,длительность которого равна С, + Јг, они поступают в первый вычислительный элемент первой строки. Знак одного из сомножителей задерживается триггером 38 на время действия синхросигнала Ј для того., чтобы на входы полусумматора 39 знаки поступили одновременно. Значение суммы знаков, которое соответствует значению знака произведения сомножителей, записывается в триггер 40 и затем перепишется при наличии управляющего сигнала в триггер 41 . Таким образом, на шестом выходе вычислительного элемента 1.1.1 на третьем такте работы устройства будет сформирован управляющий сигнал Q , соответствующий знаку произведения,

На втором такте работы устройства по информационному входу 3.1 в вычислительный блок 1.1.1 поступают старший разряд a i одного из сомножителей и младший разряд bh сомножителя Bs которые записываются: bп - в основной триггер 32 по сигналу Ј, и а - в основной триггер 33 по сигналу Ј2 соответственно. В следующем такте по сигналу Ј, происходит перезапись значения разряда b n с выхода триггера 32 в триггер 35а кроме того, значение его поступит на вход элемента И 30 и на выход 9 7 данных блока 1.1.1 для записи в триггер 19 соседнего вычислительного блока 1.1.2. С выхода триггера 33 значение разряда а( записывается в дополнительный триггер, поступает первый управляющий сигнал на выход 98 вычислительного блока для формирования управляющего сигнала Q . Значение сигнала Q (г поступает на первый информационный вход 89 элемента и на выходе элемента И 30 формируется

первое частичное произведение ,50 и 17, а также управляющего сигнала О,

В зависимости от значения управляющего сигнала Q(, которое соответствует знаку произведения, сформированное частичное произведение поступит на вход сумматора 23 либо в прямом, .либо в обратном коде. С выхода сумматора сигналы, соответствующие сумме и переносу записываются в триггере 25 я 24 По этому сигналу в триггер 32

поступающего на первый информационный вход блока, будет сформирован следующий старший разряд частичного произведения П atb у,,., . В зависимости от 55. значения управляющего сигнала QJ на входе 80 формирования дополнительного кода блока, прямой или обратный код этого разряда подается на сумматор 7 и далее полученная сумма и перенос

производится запись следующего разряда b А, сомножителя В, а значение разряда b n переписывается в триггер 19 блока 1.1.2.

В этом такте по синхросигналу Ј2 значение разряда а4 с выхода триггера 33 поступает на вход элемента И 30 и выход 97 данных блока; сигнал с выхода триггера 35, соответствующий значению разряда b п. , поступает на первый управляющий выход 98 блока в далее,, на первый информационный вход 89. Вследствие этого на выходе элемен5 та 39 сформируется частичное произведение Ьиа,. Однако запоминание результата суммирования не производится, так как он дублирует действия, выполненные по сигналу с, . В резуль0 тате выполнения данного такта в триггеры 32 и 33 вычислительного блока 1.1 будут записаны значения разрядов Ьп,и а1 в триггеры 24 и 25 будут записаны значения переноса и суммы от

5 сложения частичного произведения Щ со значением, записанным в предыдущем такте в триггер 25 и сигналом, поступившим -по входу 88 первого переноса блока 1.1. В триггеры 19 и 20 вычис0 лительного блока 1,, 2 будут записаны значения разрядов bn,a,.

В четвертом такте по сигналу в вычислительном блоке 1.1.1 будут произведены следующие действия: в триггер 32 запишется значение разряда , с помощью элементов 34 и 30 сформируется разряд частичного произведения h, и просуммируется с предыдущим частичным произведением ,п, записанным в триггеры 25 s сформируется управляющий сигнал Q, равный значению разряда ()4 сомножителя А . При действии сигнала с значение управляющего сигнала 0 будет соответствовать значению разряда Ъ ц-i сомножителя В. В вычислительном блоке 1.1.2 при действии сигнала произойдет запись в триггер 19 значения разряда b й,. Кроме того9 с помощью элементов 21

S

поступающего на первый информационный вход блока, будет сформирован следующий старший разряд частичного произведения П atb у,,., . В зависимости от 55. значения управляющего сигнала QJ на входе 80 формирования дополнительного кода блока, прямой или обратный код этого разряда подается на сумматор 7 и далее полученная сумма и перенос

131

записываются в триггеры 9 и 8. С выхода 84 данных вычислительного блока 1.1.2 значение сигнала, соответствующее разряду bn, поступит на вхо 72 данных блока 1.1.3 и запишется в триггер 19. По сигналу Јг в блоке 1.1.2 произойдет запись в триггер 20 значение разряда а2: будет сформиро- ван с помощью тех же элементов 21 и 17 младший разряд частичного произведения . Результат суммирования записывается в триггеры 23 и 24 с выхода 72 данных вычислительного блока. Значение сигнала, соответствующее разряду а(, перепишется в триггер 20 блока 1.1.3.

В каждом последующем i-м такте по информационному входу 3.1 в вычислительный блой 1,1.1 поступает новая пара разрядов а и bn-(i-1) сомножителей . В вычислительных блоках строк с помощью связей между выходом и входом данных происходит сдвиг разрядов сомножителей в сторону п+2-го блока,

причем продвигаются элементы сомножителя В, по Јг- элементы сомножителя А.

Запоминание разрядов сомножителя В производится триггером 19, сомножителя А - триггером 21).

По синхросигналу Ј, в вычислительных блоках строки с помощью элементов 21 и 17 формируются младшие разряды П ;, а {, Ъ и. (ч.г), а -, Ъп , .. .а л-(Ь п частичного произведения, начиная с блока 1.1, в котором формируется разряд a;(bn, и по блоку 1.2, в котором формируется разряд, равный а n- (,-г) Формирование частичного произведения производится под воздействием управляющего сигнала Q, который поступает с первого управляющего выхода блока 1.1.1 на первые информационные входы вычислительных блоков стро

ки| значение Q в данном случае соот-45 поступает на входы формирования до- ветствует значению управляющей пере- полнительного кода блоков, начиная менной а, . В зависимости от знака произведения сомножителей, который формируется в первом блоке строки

в виде управляющего сигнала Q| с вто- - если знак произведения положительный, рого управляющего выхода, он поступа- либо в обратном, если знак произве- ет на входы формирования дополнительного кода блоков с 1.1.1 по 1.1, «4.2 На сумматоры 7 частичное произведение поступает либо в прямом коде с прямого выхода элемента И 17, либо в обратном - с инверсного выхода элемента 17, Промежуточная сумма младших разрядов произведения, полученная как

с 1.1.1 по 1.1 п+2. В вычислительных блоках на сумматоры 7 поступает частичное произведение в прямом коде,

дения отрицательный. В блоках 1.1.п+1 1.1.п+2 строки знак произведения непосредственно подается на сумматор 43 и в результате в (п+2)-м блоке строки будет сформирован окончательный знак произведения,

Промежуточная сумма с выхода сумматора 7 записывается в триггеры 14 и

14

0

0

0

результат суммирования частичного произведения , поступившего на второй вход сумматора, с информацией, полученной с входа первого переноса блока и данными, поступающими с выходов триггеров 9, записывается в триг-° геры 9 и используется в следующем такте. Промежуточные переносы записываются в триггеры 8 и в следующем такте поступают на выходы первого переноса вычислительных блоков. Суммирование частичных произведений отрицательных чисел в обратном коде требует наличия

с цепи обратной связи, для того чтобы избежать этого в предлагаемом устройстве производится преобразование обратного кода в дополнительный за счет введения связи с второго управляющего выхода первого блока на вход первого переноса блока 1.1.п2., т.е. в младший разряд сформированного частичного произведения производится добавление единицы, за счет чего происходит пре5 образование обратного кода в дополнительный.

По сигналу в вычислительных блоках строки с помощью элементов 21 и 17 формируются старшие разряды П t

а b tbtf-i) агъn-(i-т- V аi-zb n- (i-г) частичного произведения, начиная с

блока 1.1.2, в котором формируется разряд, равный а в b п (, -г). Для формирования частичного произведения в вычислительные блоки на первый информационный вход поступает управляющий сигнал Q. с первого управляющего выхода блока 1.1.1, значение Q в данном случае соответствует значению управляющей переменной Ъп.гу В зависимости от знака произведения сомножителей, который формируется в первом блоке строки, управляющий сигнал Q1 с второго управляющего выхода

поступает на входы формирования до- полнительного кода блоков, начиная

если знак произведения положительный, либо в обратном, если знак произве-

с 1.1.1 по 1.1 п+2. В вычислительных блоках на сумматоры 7 поступает частичное произведение в прямом коде,

если знак произведения положительный, либо в обратном, если знак произве-

дения отрицательный. В блоках 1.1.п+1 1.1.п+2 строки знак произведения непосредственно подается на сумматор 43 и в результате в (п+2)-м блоке строки будет сформирован окончательный знак произведения,

Промежуточная сумма с выхода сумматора 7 записывается в триггеры 14 и

Б следующем такте поступает чероз элементы И И и ИЛИ 16 на третий вход суммятооа. Промежуточные, переносы записываются в триггеры 13 вычислительных блоков и з следующем такте поступают на выходы второго переноса вычислительных: блоков. В п-Н такте

I работы устройства в триггеры 19 вычислительных блоков будут записаны все разряды сомножителя Bs а в триггеры 20 - все разряды сомножителя ПАР причем в блоке 1.1.1 разряды а и b з 1 К2ал.,иЬав 1 .1 .3 - а ц.ги b з в 1 ,п-э н в bn. В следующем тг+2 такте на управляющие входы 9 блоков первой строки подается управляющий сигнал YH с первого выхода устройства управления. По этому сигналу в

.блок 1,1 запишется новэ.я пара знаков сомножителей, а в остальных блоках произойдет обнуление триггеров 19 И 20. Кроме того, в этом такте будет формировано П частичное произведение к просуммировано в промежуточной суммой предыдущих тактов, которая хранится в триггерах 9 и 14 вычислительных блоков. Таким образом, цикл работы умножителя составляет т -1 такт Каждая следующая строка матрицы вы™ числительных блоков принимает: пары сомножителей со сдвигом на один такт, т.е. если в первую строку поступают а , и b пм разряды сомножителей А и 6( s то во вторую а , и b л., разряды сомножителей А2 и Вг э в третью а и bjw,-., Разряды сомножителей АЗ к В$ и т.д. Работы остальных п-1 строк вычислительных блоков аналогичны работе описанной первой строки,

В процессе выполнения операции ум чожекия пар сомножителей между п первыми строками матрицы осуществляется передача промежуточных переносов, зозпикающих на каждом такте и записываемых в триггеры 8 и 13, в сосед- шло верхнюю строку. Для этого выход переноса i-го вычислительного блока нижней строки соединяется с входом лервого переноса (i-1) вычислитель- него блока соседней верхней строки, при этом по этой связи передается значение младших разрядов промежуточных переносов Выход второго переноса 1-го вычислительного блока сое- динен с входом второго переноса i+1 вычислительного блока соседней верхней строки при этом по этой связи

передается значение старших разрядов промежуточных переносов.

Таким образом,, на любом такте работы каждой строки матрицы (умножителе) осуществляется поступление по входу З-i новой пары разрядов сомножителей Ј суммирование сформированного частичного произведения с промежуточной суммой, полученной в предыдущем такте и считываемой с выходов триггеров 9 для младшей половины разрядов и с выходов триггеров 14 для старшей половины разрядов, и с промежуточными переносами;, поступающими с нижней соседней строки матрицы причем по входу первого переноса блоков поступают переносы младшей половины разрядов; а по входу второго переноса - старшей половины разрядов. Результат суммирования в виде вновь полученной промежуточной суммы и переносов записывается в триггеры 9S 14 и 8513 соответственно. По окончании каждого цикла работы умножителя в его выходных триггерах (8,13,9,14) будет записано произведение пары сомножителей, представленное двухрядным кодом; т„е в виде кода переносо л кода суммы. В каждом третьем такте цикла двухрядный код произведения передается в соседнюю верхнюю строку матрицы,, для этого в вычислительные блоки строки с соответствующего выхода блока управления поступает управляющий сигнал Y, 5 гДе i номер строки. Под воздействием этого сиг- нала, поступающего на входы управления передачей суммы блоков, выходы триггеров 9 и 14, с которых считывается значение разрядов суммы соединяются с помощью элементов И 12 с ВэГхо дами суммы вычислительных блоков „

Сигнал с выхода суммы вычислительных блоков i-й строки поступает на третий вход суммы соседнего сверху вычислительного блока (х+1)-й строки и далее через элемент 6 на второй вход сумматора 7, В момент передали суммы и переносов для строки (i+t) будет второй такт работь в котором по входу 3.1-М и Ц-И.О-й вычислительный блок только поступает первый значащий разряд пары сомножителей и i поэтому наложение сигналов на втором входе сумматора не произойдет.

Таким o6pa3OMs по окончании процеса умножения пары сомножителей в п-и

строке матрицы 1 в нее поступают результаты операции умножения предыду- щих пар сомножителей из нижней строки По мере освобождения строк матрицы в нее может поступать новая последовательность пар чисел.

В (п-М)-й строке матрицы вычислительных блоков производится суммирование переносов, возникающих на каж- дом такте работы n-й строки матрицы, поступающих с выхода первого переноса для младшей половины разрядов и с выхода второго переноса, для старшей половины разрядов, выходов блоков на входы первого и второго переносов блоков (п+1)-й строки. В процессе работы возникающие переносы в вычислительных блоках п+1 строки передаются между элементами для каждой половины разрядов с выхода первого переноса на первый информационный вход соседнего слева вычислительного блока и с выхода второго переноса на второй информационный вход соседнего справа вычислительного блока для старшей половины разрядов. Значение разрядов промежуточной суммы в виде двухразрядного кода записывается в триггеры 51 и 52 для младших разрядов и триггеры 56 и 57 для старших разрядов. Цикл работы вычислительных блоков (п-Н)-й строки составляет также п+1 такт. Результат умножения пары сомножителей из л-й строки матрицы 1 поступает на входы суммы вычислительных блоков , (п+1)-и строки. Для этого, на входы управления передачей суммы вычислительных блоков (п+1)-й строки поступает управляющий сигнал Y п+3 кото- рый подключает выходы триггеров 52 и 57 на выходы суммы вычислительных блоков и в это время на входы суммы вычислительных блоков поступает код суммы с n-й строки матрицы. С выходов суммы вычислительных блоков разряды данных поступают в вычислительные блоки (п+2)-й строки. В следующем такте работы (п+1)-и строки матрицы старшие разряды сформированного в вы- числительных блоках двухрядного кода для преобразования в окончательный результат передаются в вычислительные блоки (п+2)-й строки. В вычислительных блоках (п+1) -й строки в момент передачи необходимо для установки в ноль триггеров 51 и 56 разорвать цепи распространения внутренних переносов. Для осуществления этих действий на

,.

JQ | 202530,5 о 5 Q

5

входе управления передачей суммы сохраняется сигнал Y по (т.е. длительность сигнала Ynt3 равна двум тактам), а на второй управляющий вход поступает сигнал Y , который отключает второй вход сумматора 50. Таким образом, второй и третий входы сумматоров 50 будут отключены от источников данных и, следовательно, не произойдет искажения разрядов числа, поступающего по входам первого и второго переносов вычислительного блока. Эти разряды чисел соответствуют переносам, возникающим при обработке новой пары сомножителей новой последо- вательности в n-й строке матрицы-.

Вычислительные блоки (п+2)-й строки матрицы 1 принимают двухрядный код, поступающий с (п+1)-и строки и за (п+1) так формируют окончательный n-разрядный результат операции суммирования пар произведений. Окончательный результат формируется на информационном выходе 4 устройства последовательно разряд за разрядом, начиная с младшего n-го разряда и кончая знаковым разрядом произведения. Разряды данных, поступающие с первого информационного входа вычислительного блока, записывающего в триггер 68 под воздействием управляющего сигнала Yn+z, поступающего на вход разрешения записи вычислительного блока с (п+2)-го выхода блока управления. Триггер 68 осуществляет задержку сиг-, нала на один такт работы устройства для временного согласования с информацией, которая поступает на вход первого переноса и первый информационный вход вычислительных блоков п+2 в следующем такте. Прием информации с (п+1)-и строки в (п+2)-ю осуществляется под воздействием управляющего сигнала Yn, поступающего на второй управляющий вход вычислительных блоков, при этом обрываются связи передачи значений суммы и переносов между вычислительными блоками и за счет этого происходит обнуление триггеров 63 и 64. Поступающая в данном такте информация с входа первого переноса и первого информационного входа складывается со значением разрядов числа, считываемого с выхода триггера 68, и полученные значения поразрядной суммы и переноса записываются соответственно в триггеры 64 и 63. Эти действия выполняются при воздействии синхроснгналз и2 В дальнейшем на каждом такте работы вычислительных блоке в (п+;) строки происходит суммирование записанных в триггерах 64 разрядов промежуточной суммы с разрядами промежуточных переносов, записанных в триггерах 63 со сдвигом разрядов полученной суммы в сторону младших разрядов, при этом на выход устройства 4 поступит вновь полученный разряд окончательного результата, В последнем (п+1)-м такте с выхода 4 будет считан знаковый разряд окончательного результата5 а на вход пер

зого переноса и первый информационный вход с (п-Н)-й строки поступит следующий двухрядный код.

Таким образом цикл работы каждой Строки матрицы 1 составляет п+ такт И в случае поступления на входы 3.i устройства последовательности пар сомножителей на выходы 4 устройства че р ез каждые п+1 так будет сформирован новый результат.

Работает предлагаемое устройство под воздействием сигналов, вырабатываемым блоком управления (фиг.8), При поступлении на управля ощий вход 5 устройства сигнала о начале работы про- исходит запуск генератора 69 синхроимпульсов и установка сдвигового регистра 70 в исходное состояние, кото-рое заключается в том, что в первом разряде устанавливается 1, а в остальных; Q. В дальнейшем под воздействием синхроимпульсовs вырабатываемых генератором 69, происходит сдвиг единичного состояния последовательно разряд за разрядом в сдвиговом регист ре. Количество разрядов сдвигового регистра 70 определяется количеством тактов работы предлагаемого устройства, в данном случае равном п+3, На выходах устройства управления появляются управляющие сигналы Y;, под воздействием которых осуществляется передача данных между строками матрицы вычислительных блоков и обнуление триггеров. Так, например, для обнуления содержимого триггеров второй строки на втором выходе появится сигнал Y во втором такте работы. Через такт с второй строки в третью происходит передача кодов суммы и перенос в третью строку матрицы, для этого с четвертого выхода во вторую строку на входы управления передачей суммы поступает сигнал Y4° Длительность каж

равна длительности о, + Јгн формирование помощью элементов ИЛИ

дого сигнала YJ

синхроимпульсов

их происходит с

элемента ИЛИ 71 поступают с выходов

дополнительного триггера и основного

триггера (i-M)-ro разряда. Длитель0

5

0

5

30 ( ность сигнала Y

гиз поступающего на

входы управления передачей суммы вычислительных блоков (п+1)-и строки матрицы, равна двум тактам работы устройства,, поэтому для формирования его используются выходы ш-2 и n-f-4 элементов ИЛИ, Запись информации триггер 69 вычислительных блоков (п+2)-й строки должна совпадать по времени с действием управляющего сигнала ,

Рассмотрим пример получения суммы произведений следущей последователь- 14 5 117, . ,6 13

ности 9

п( - --

Мб 16 16 16

)

и А Результаты операции

12)

6 Л Г5 131 Г11 , 9 -4 6х( ТбУ ЧТ6ХТ6 ШХ( Тб}

/ .

Чб} 169

Ь;а;

г, 7 N 10T 188 12

1( Тб)хТбГ 256 Тб В Двоичном

5

0

представлении щий вид;

,(0

i

операция имеет следую1

10х(-0,0110) + (0,0101)х х(0,:М01) + (0,1011)х(0,1ГЮ1) + (0,0111)х

x(0s 1010) (0,010101ОГИ-О, 01 00001- -0,01100011-0,01000110)0,10111100 -0,1011.

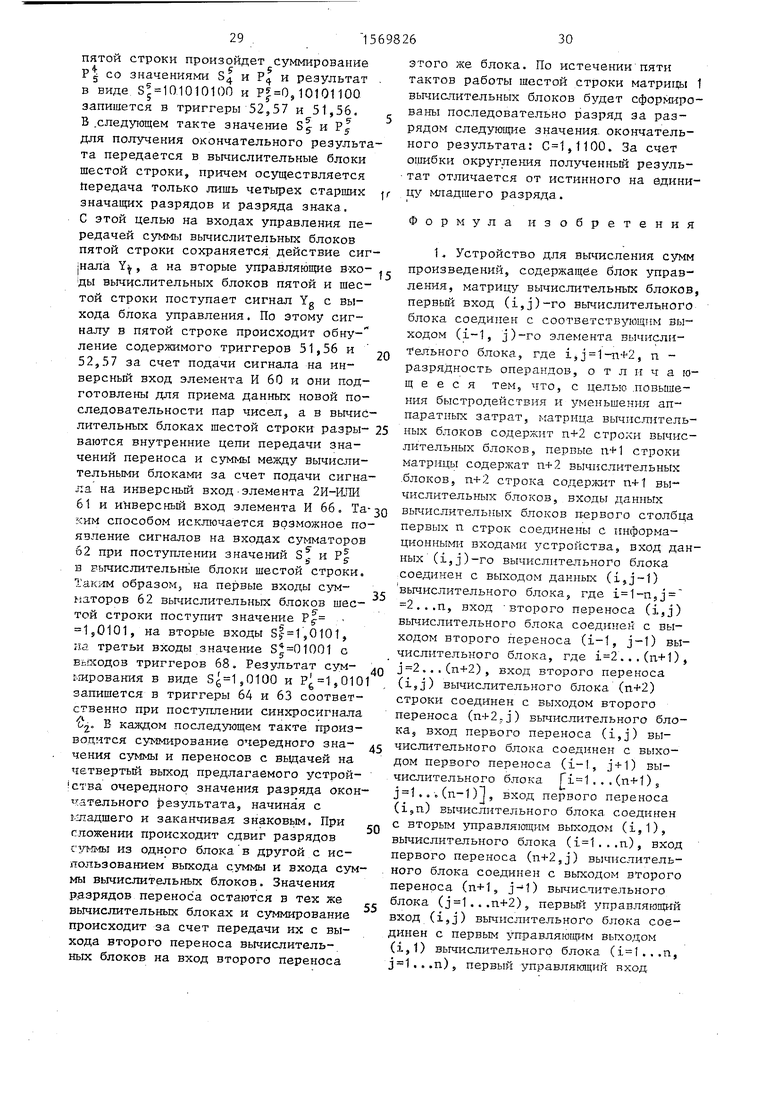

Частичные произведения для пар чисел представлены в табл. 2.

Согласно алгоритму работы устройства первоначально частичные произведения получаются в прямом коде, а далее s в зависимости от знака произве - дения9 преобразуются в дополнительный и далее производится их суммирование .

Суммирование полученных произведений дает следующий результат:

1,10101100

Os01000001

1,10011101

1,10111010

19ОЮ00100

Для выполнения данной операции матрица 1 вычислительных элементов должна содержать в первых пяти строчках

, вычислительных блоков, 6-я стро- вход схемы И 30 и на выход данных блока - 5 вычислительных блоков. Диапа- ка. На первые информационные входы

зон представления чисел выбирается из условия отсутствия переполнения при суммировании. На первом такте работы устройства в вычислительный блок 1.1 по входу данных последовательно поступают знаки а° 0 и первой

вычислительных блоков первой строки с 1.1.1 по К 1.4 поступит значение

управляющего сигнала 0- 1, на входы формирования дополнительного кода вычислительных блоков 1.1-1.6 поступит значение управляющей переменной 0 1. пары сомножителей, при этом на первый JQ Под воздействием этих переменных на управляющий вход поступает управляю- выходе элементов 2И-ИЛИ 15 будет сфор- щий сигнал Y с первого выхода бло- мировая обратный код младших четырех ка управления.. Под его воздействием разрядов частичного произведения: значение b ° поступает на вход триггера 1111 и далее, они поступают 38 при действии синхросигнала Ј, и осу- )5 На второй вход сумматора 7 и с выхода суммы результат записывается в триггере 9. Для преобразования обратного кода в дополнительный значение управляющего сигнала Q поступает на вход первого переноса вычислительного блока 1.1.4, за счет чего происходит прибавление единицы в младший разществляется задержка сигнала. По синхросигналу Јг поступает на вход полусумматора 39 значение а, а на другой вход с выхода триггера 38 значение Ь . С выхода суммы полусумматора 39 f) значение 1, соответствующее знаку результата операции умножения сомножителей А и В,-поступает на вход триг- ряд. По синхросигналу с выхода триггера 40 и по Јг записывается в него. гера 35 через элемент 2И-ИЛИ 36 на На втором такте работы устройства 25 первый управляющий выход вычислитель- прекращается действие управляющего Ного блока 1 .-1 .1 поступает значение сигнала и на вход данных вычислитель- , С выхода триггера 33 через эле- ного блока 1.1.1 поступает младший Мент 2И-ИЛИ 34 на выход данных блока разряд Ь.,0 сомножителя и записывает- и второй вход элемента И 30 поступает сд в триггер 32 по синхросигналу Ј, , Зо значение а)0. С помощью управляющих по синхросигналу Ъг поступает стар- символов Q , и Q формируются старшие ший разояд а сомножителя А и запи- разряды частичного произведения сывается в триггер 33. На вход раэре- П, 1.111 в вычислительных бло- шения записи вычислительного блока

l.i.1 поступает управляющий сигнал Y сд .сч с второго выхода блока управления и триггеры 14. по синхросигналу Ј, значения триггера 40 перепишется в триггер 41 . В этом же такте значение управляющего сигнала поступает на вход вычислительного блока 1.2.1. В вычислительный блок 1.2.1 по входу данных посту- пит знак второй пары сомножителей а°г

П 1.111 ках 1.1.2-1.1.6 и, пройдя через сумматор 7, записываются в

и Ь и равные соответственно а. и и после суммирования на полусумматоре 39 сумма равная О запишется в триггер 40. На третьем такте работы устройства на втором управляющем выходе вычислительного блока 1.1.1 будет сформирован управляющий сигнал Q1, равный 1. По синхросигналу С, на первый информационный выход вычислительного блока через элемент 36 с второго выхода триггера 33, который образован выходом основного i триггера, поступит значение управляющей переменной в виде сигнала 0, с выхода триггера 32 через схему 34 поступит значение на второй

45

;о

В результате в триггерах 9 будет записана поразрядная сумма,

1

равная S, 1,111111 10, в триггеры 8 и 13 будут записаны поразрядные переносы ,00000001. Значение Ь по С1 записывается в триггер 19 а а по Јг в триггер 20 вычислительного блока 1.1.2. На этом же такте по информационному входу 3.1 в вычислительный блок 1.1.1 записываются последовательно разряды в и в триггеры 32 и 33. В этом же такте в вычислительный блок 1.2.1 второй строки матрицы 1 в триггер 41 запишется значение знака произведения второй пары сомножителей, а в триггеры 32 и 33 поступят значения разряда сомножителя Ъ„ и разряда сомножителя а2. В вычислительный блок 3.1 третьей строки матрицы 1 по входу 3.3 поступят знаки и третьей пары( Сомножителей при действии управляющевычислительных блоков первой строки с 1.1.1 по К 1.4 поступит значение

ряд. По синхросигналу с выхода триггера 35 через элемент 2И-ИЛИ 36 на первый управляющий выход вычислитель- Ного блока 1 .-1 .1 поступает значение , С выхода триггера 33 через эле- Мент 2И-ИЛИ 34 на выход данных блока и второй вход элемента И 30 поступает значение а)0. С помощью управляющих символов Q , и Q формируются старшие разряды частичного произведения П, 1.111 в вычислительных бло-

сд .сч триггеры 14.

П 1.111 ках 1.1.2-1.1.6 и, пройдя через сумматор 7, записываются в

сд .сч триггеры 14.

5

В результате в триггерах 9 будет записана поразрядная сумма,

1

равная S, 1,111111 10, в триггеры 8 и 13 будут записаны поразрядные переносы ,00000001. Значение Ь по С1 записывается в триггер 19 а а по Јг в триггер 20 вычислительного блока 1.1.2. На этом же такте по информационному входу 3.1 в вычислительный блок 1.1.1 записываются последовательно разряды в и в триггеры 32 и 33. В этом же такте в вычислительный блок 1.2.1 второй строки матрицы 1 в триггер 41 запишется значение знака произведения второй пары сомножителей, а в триггеры 32 и 33 поступят значения разряда сомножителя Ъ„ и разряда сомножителя а2. В вычислительный блок 3.1 третьей строки матрицы 1 по входу 3.3 поступят знаки и третьей пары( Сомножителей при действии управляющеналов Q2 0 и будут сформированы старшие разряды П 080000 г и после суммирования со старшими раз рядами поразрядных переносов Р Р 0,0000 результат в виде ,,0000 и Р 0,0000 запишется в триггеры 14 и 13. В вычислительный блок 1.2,1 в

го сигнала Y3 с третьего выхода блока лу С под-действием управляющих сиг- управ тения и после суммирования ре- .зультат запишется в триггер 40, На четвертом такте работы в первой строке матрицы по синхросигналу на выходах схем 15 в вычислительных блоках 1 .1.1--1.1.4 будут сформированы млад-- lime разряды частичного произведения П ХгХХХХ0111 и поступят на вторые входы сумматоров 7. На третьи входы с выходов триггеров 9 через элемент И 11 поступят значения младших поразрядных сумм s Х,ХХХХ1110, После суммирования вновь образованная поразрядная сумма младших разрядов S2, Х9ХХХХ1000 запишется в триггер 9 вычислительных блоков 1.1.1-1.1.4, а в триггер 9 запишутся поразрядные

0

триггеры 32 и 33 запишется значение b3-Q и , в остальных вычислитель ных блоках произойдет сдвиг ранее записанных разрядов сомножителей. В вычислительный блок 1.3.1 третьей 5 строки в триггеры 32 и 33 запишутся разряды bt 1 и . В триггер 41 пе репишется значение знака результата с выхода триггера 40. В вычислительный блок 1,4.1 четвертой строки матпереносы ,ХХХХ0111. В триггер 32 рицы при действии управляющего сигна- вычислителъного блока 1.1.1 запишется ла Y. с четвертого выхода блока уп- эначение разряда Ь, а в остальных вычислительных блоках произойдет сдвиг ранее записанных в триггерах 19 разрядов сомножителей Ь, . По синхросчг- 5 на торе 39 результат

равления поступят знаки четвертой паи аЈ О

ры сомножителей

и после суммирования

К 1

на полусум- запишется

Налу i2 в вычислительных блоках 1.1.2 1.1.6 будут сформированы старшие разряды частичного произведения П 1 ,t 11 1 которые поступят на вторые входы сум - матора 7S а на третьи входы поступят значения старших разрядов поразрядных сумм ,111. Результат суммирования в виде поразрядной суммы S 0S0000 и оцоразрядных переносов ,1111 запишется соответственно в триггеры 13 м 14. В триггер 33 вычислительного блока 1.1,1 запишется значение разряда а3( 1, а в остальных вычислительных, блоках произойдет сдвиг ранее записанных в триггерах 20 разрядов со- множителя а „ В вычислительных блоках второй строки по синхросигналу под воздействием управляющих сигналов и будут сформированы младшие разряды частичного произведе- ния П1 Х0ХХХХ10000, которые поступают на вторые входы сумматоров 7 вычислительных блоков 1,2,1-1,2,4. На пер- ные входы сумматоров с выходов первого переноса вычислительных блоков I.1-1.4 через вход первого переноса блоков 152,,4 и элемент 2И-ИЛИ поступают значения поразрядных переносов младших (разрядов Р| Х,ХХХХ0010. После суммирования результат в виде

младших разрядов поразрядной суммы 8г.Х,ХХХХ1010 и поразрядных переносов Р ХЭХХХХОООО запишется в триггеры 9 :i 8 соответственно. По еинх-росигнаналов Q2 0 и будут сформированы старшие разряды П 080000 и после суммирования со старшими разрядами поразрядных переносов Р Р 0,0000 результат в виде ,,0000 и Р 0,0000 запишется в триггеры 14 и 13. В вычислительный блок 1.2,1 в

лу С под-действием управляющих сиг-

лу С под-действием управляющих сиг-

триггеры 32 и 33 запишется значение b3-Q и , в остальных вычислительных блоках произойдет сдвиг ранее записанных разрядов сомножителей. В вычислительный блок 1.3.1 третьей строки в триггеры 32 и 33 запишутся разряды bt 1 и . В триггер 41 перепишется значение знака результата с выхода триггера 40. В вычислительный блок 1,4.1 четвертой строки матрицы при действии управляющего сигна- ла Y. с четвертого выхода блока уп- на торе 39 результат

равления поступят знаки четвертой паи аЈ О

ры сомножителей

и после суммирования

К 1

на полусум- запишется

в триггер 40

- 5

0

5

На пятом такте работы устройства в вычислительных блоках первой строки будет сформировано частичное произведение П3 1,, 111 000115 которое поступает на вторые входы сумматоров 7Э на третий вход поступит значение разрядов суммы S2( с выходов триггеров 9 и 14 ,00001000, на первый вход сумматора 7 вычислительного блока 1.1.4 поступит единичное значение. Результат суммирования в виде вновь образованной суммы ,1101010 и- переносов P3 0S00000001 запишется в триггер 9}14 и 8,13 соответственно, В триггеры 32 и 33 запишутся разряды Ц 0 и сомножителей а и Ь( и произойдет сдвиг остальных ранее записанных разрядов. В вычислительных блоках второй строки будет сформировано частичное произведение П 05000001009 которое поступает на вторые входы сумматоров 7$ на третьи входы поступят разряды суммы S 0ЭOOQ01010, на первые входы поступят значения поразрядных переносов Р,2 1911101110 с выходов первого и второго переносов вычислительных блоков первой строки. Результат суммирования в виде S| 1511100000 и Р 0500001110 ; запишется в триггеры и 8,13. В триггеры 32 и 33 запишутся разряды Ь|-0 и .

В вычислительных блоках третьей строки сформируется частичное произведение ,11110111, которое лросум- мируется с единичным значением, по- ступающим на вход первого переноса вычислительного блока 1.3.4, Результат в виде суммы ,11101 10 и переносов 0,00000001 запишется в триггеры 9,14 и 8,13. В вычислительный блок 1.3.1 ю запишутся значения разрядов и . В вычислительный блок 1.4.1 четвертой строки поступят разряды Ъ

и а1 сомножителей b и а. На шестом

4 такте работы в вычислительных блоках

первой строки сформируется частичное произведение П 1, 11 001111, которое просуммируется с порязрядной суммой S3, и единичным значением, поступающим по входу первого переноса вычис- 2 лительного блока 1.1. в виде поразрядной суммы S,0,00100100 и поразрядных переносов Р,1,11001011 запишутся в триггеры 9,14 и 8,13. В этом же такте на первые управляющие входы 2 вычислительных блоков поступает управляющий сигнал с первого выхода блока управления, за счет чего происходит установка в О триггеров 19 и 20 л может происходить прием знаков новой нары сомножителей, В вычислительных блоках второй строки сформируется частичное произведение ,00110000, которое суммируется с предыдущей по-/ разрядной суммой ,11110000 и пе- 3 реносами, поступающими с вычислительных блоков первой строки Р3 t 1,00000010. Результат в виде вновь образованной суммы ,11010010 и переносов ,00100000 запишется в 4 триггеры 9,14 и 8,13. В вычислительный блок 1.2.1 запишутся значения разрядов Ь и аз, в остальных вычислительных блоках произойдет сдвиг дан- ых в соседние блоки. В вычислитель- 4 ных блоках третьей строки сформируется частичное произведение П| 1s11101111s которое просуммируется с предыдущей частичной суммой В Ш 10110 и переносами, поступающи-5 « к входам первого и второго перено- вычислительных блоков с нижней второй строки ,00011101.

Результат в виде вновь образованной поразрядной суммы ,00000100 5 и переносов .11111111 запишется в триггеры 9,14 и 8,13. В вычислительный блок 3.1 запишутся разряды и , в, остальных произойдет сдвиг

ранее записанных разрядов. В вычислительных блоках четвертой строки сформируется частичное произведение П 1,11110111, которое суммируется с переносами, поступающими с нижней третьей строки вычислительных блоков ,0000001 1 . Результат суммирования в виде поразрядной суммы 5 1,11110100 и переносов , 0000011 1 запишется в триггеры 9,14 и 8,13. В вычислительный блок 1.4.1 запишутся разряды Ъ3 и а2, . В следующем седьмом такте во второй строке вычислительных блоков сформируется последнее частичное произведение П 0,00000101s которое просуммируется с суммой S| и переносами Р, поступающими, из первой строки матрицы. Результат в виде суммы ,010000001 и переносов Р 1510010110 записывается в триггеры 9514 и 8,13. На первые управляющие входч блоков поступит управляющий сигнал Y2, за счет которого произойдет обнуление триггеров 19 и 20 в вычислительных элементах второй строки и они подготовлены для приема новой пары сомножителей. В вычислительных блоках третьей строки сформируется частичное „произведение ,11111111, которое просуммируется с S2 и Р| и результат в виде S3 1,101111010 и переносов ,01000101 запишется в триггерах 9,14 и 8,13. В вычислительный блок 3.1 поступают значения b и аЗ. В вычислительных блоках четвертой строки сформируется частичное произведение , 111 ОИ 11, которое просуммируется с S4 и Рч.

1

Вновь полученные сумма П4 1,111110100 и переносы Р4-1,1111111I1 запишутся в триггерах 9,14 и 8,13. В вычислительный блок 4.1 запишутся разряды Ъц. 1 и а 1 . В (п+1)-ю строку с выходов первого и второго переноса вычислительных блоков п строки поступят значения поразрядных переносов Р| и запишутся в триггеры 52 и 57. В восьмом такте на входы управления передачей суммы вычислительных блоков первой строки поступит управляющий сигнал Y с третьего выхода блока управения. Под воздействием этого сигнала выходы триггеров 9 и 14 вычислительных блоков первой строки, в которых ранится поразрядная сумма S,., будут одключены к выходам суммы вычислиельных блоков. За счет этого проиойдет передача S в вычнслитечь27

ные блоки второй строки, в которых просуммируются со значениями 5 и результат в виде ,1100101 и ,00000000 запишется в триггеры

14 и 8,13. В третьей строке сформируется частичное произведение П 1,10110100, которое просуммируется с S и П 2. и результат в виде 5 1,00100011 и ,10111100 записывается в триггеры 9,14 и 8,13. На первые управляющие входы вычислительных блоков поступит управляющий сигнал Y, за счет которого произойдет обнуление триггеров 19 и 20 в вычисли- тельных блоках третьей строки и они подготовлены для приема новой пары сомножителей. В вычислительных блоках четвертой строки сформируется частичное произведение ,11010001, кото-

рое просуммируется с S и П| и реч2ь

зультат в виде суммы ,10111110 и переносов ,11000001 запишется в соответствующие триггеры. В вычислительный блок 4.1 запишутся разряды Ь,0 и и произойдет сдвиг ранее записанных разрядов. С выходов первого и второго переноса вычислительных блоков четвертой строки значение IH

поступит на входы первого и второго переносов вычислительных блоков (п+1)-й строки, в которых произойдет суммирование с ранее записанным кодом и результат в виде 5| 1,11111000 и ,00000110 запишется в соответ- ствующие триггеры. При суммировании вычислительных блоках пятой строки внешние данные принимаются по входу первого и второго переноса вычислительных блоков, а внутренние переносы передаются для младших разрядов с выхода первого переноса на первый информационный вход, а для старших разрядов с выхода второго переноса н второй информационный вход. В девятом такте значения П и 5 поступят в вычислительные блоки третьей строки, причем для передачи 5 на входы управления передачей суммы вычислительных блоков второй строки подает

ся сигнал Y4 ка управления и

с четвертого выхода блог

S Ј просуммируются

В третьей строке П со значением и

результат в виде S| 1,01000110 и ,0010001 запишется в соответствующие триггеры. В вычислительных блоках четвертой строки сформируется

частичное произведение которое просуммируется

2628

1,01111001 и результат в виде ,001111000 и 4 1,1 111 11 111 запишется в соответствующие триггеры. На первые управляющие входы вычислительных блоков поступит управляющий сигнал Y, за счет чего произойдет обнуление триггеров 19 и 20. На входы вычислительных блоков пятой строки поступит значение Р и просуммируется со значением S2f и Р|.. Результат в виде ,01110110 и . 1,1000010000 запишется в соответствующие триггеры. В десятом такте на вход управления передачей суммы вычислительных блоков третьей строки

поступит управляющий сигнал Y, за счет чего осуществится передача значения Sj в вычислительные блоки четвертой строки. В вычислительных блоках четвертой строки произойдет

со значениями

ч ь з

суммирование Ј-

и И}, переданными по входам суммы, первого и второго переносов из третьей строки. Результат в виде 5 4 1,00111100 и ,01000010 запишется

в триггеры

Ч 9, 14 и

8,13. Значение

30

,5 40

45

50

55

1,

Р4 будет передано в пятую строку вычислительных блоков, где оно просуммируется с S3 и . Результат суммирования в виде ,10011000 и Р 0,101110110 запишется в соответствую- В

щие триггеры. В следующем такте в пятую строку осуществляется передача Л и PJ

SJJ и Р° для суммирования с результа

тами предыдущих действий. В связи с тем, что в пятой строке результат записан двухрядным кодом в виде Sg-u и Р&, а на вход вычислительных блоков пятой строки поступают значения 5 и Р| то одновременно осуществить суммирование всех данных невозможно, так как сумматоры имеют три входа. Поэтому в этом такте осуществляется передача S в шестую строку вычислительных блоков. С этой целью на входы разрешения записи вычислительных блоков шестой строки, подается управляющий сигнал Yg с шестого выхода блока управления, а на входы управления передачей суммы вычислительных блоков пятой строки подается управляющий сигнал Y7 с седьмого выхода блока управления. При этом, значение S с выходов второго переноса вычислительных блоков пятой строки поступит на первые информационные входы вычислительных блоков шестой строки и запишется в триггер 68. В вычислительных блоках

пятой строки произойдет суммирование Р со значениями S4 и Р4 и результат . в виде 85 101010100 и ,10101100 запишется в триггеры 52,57 и 51,56. В .следующем такте значение s| и Р| для получения окончательного результата передается в вычислительные блоки шестой строки, причем осуществляется передача только лишь четырех старших значащих разрядов и разряда знака. С этой целью на входах управления передачей суммы вычислительных блоков пятой строки сохраняется действие сиг- |Нала Y , а на вторые управляющие в-хо- | ды вычислительных блоков пятой и шестой строки поступает сигнал Yg с выхода блока управления. По этому сигналу в пятой строке происходит обну- ление содержимого триггеров 51,56 и 52,57 за счет подачи сигнала на инверсный вход элемента И 60 и они подготовлены для приема данных новой последовательности пар чисел, а в вычислительных блоках шестой строки разры- 2 ваются внутренние цепи передачи значений переноса и суммы между вычислительными блоками за счет подачи сигнала на инверсный вход-элемента 2И-ИЛИ

61и инверсный вход элемента И 66, Та-3 ким способом исключается возможное появление сигналов на входах сумматоров

62при поступлении значений sj и Р|

в вычислительные блоки шестой строки.

Таклм образом, на первые входы сумматоров 62 вычислительных блоков шестой строки поступит значение pf 1,0101, на вторые входы ,0101, на третьи входы значение S 01001 с ВЕ ХОДОВ триггеров 68. Результат сум- г-мрования в виде ,0100 и ,010 запишется в триггеры 64 и 63 соответственно при поступлении синхросигнала Јг. В каждом последующем такте производится суммирование очередного зна- чения суммы и переносов с выдачей на четвертый выход предлагаемого устрой- ства очередного значения разряда окон -зтельного результата, начиная с ютадшего и заканчивая знаковым. При сложении происходит сдвиг разрядов суммы из одного блока в другой с использованием выхода суммы и входа суммы вычислительных блоков. Значения разрядов переноса остаются в тех же вычислительных блоках и суммирование происходит за счет передачи их с выхода второго переноса вычислительных блоков на вход второго переноса

. |5 п 253035

Q 50

5

этого же блока. По истечении пяти тактов работы шестой строки матрицы 1 вычислительных блоков будет сформированы последовательно разряд за разрядом следующие значения окончательного результата: ,1100. За счет ошибки округления полученный результат отличается от истинного на единицу младшего разряда.

Формула изобретения

1 Устройство для вычисления сумм произведений, содержащее блок управления, матрицу вычислительных блоков, первый вход (i,j)-ro вычислительного блока соединен с соответствующим выходом (i-1, j)-ro элемента, вычислительного блока, где i,j 1-n+2, n - разрядность операндов, о т л и ч а ю- щ е е с я тем, что, с целью повышения быстродействия и уменьшения аппаратных затрат, матрица вычислительных блоков содержит п+2 строки вычислительных блоков, первые п+1 строки матрицы содержат п+2 вычислительных блоков, п+2 строка содержит п+1 вычислительных блоков, входы данных вычислительных блоков первого столбца первых n строк соединены с информационными входами устройства, вход данных (i,j)-ro вычислительного блока соединен с выходом данных (i,) вычислительного блока, где ,j 2...п, вход второго переноса (i,j) вычислительного блока соединен с выходом второго переноса (i-1, j-1) вычислительного блока, где ...(п+1), ...(n+2), вход второго переноса (i,j) вычислительного блока (п+2) строки соединен с выходом второго переноса (n+2.j) вычислительного блока, вход первого переноса (i,j) вычислительного блока соединен с выходом первого переноса (i-l, j+1) вычислительного блока ...(n+1), .,.(п-1)1, вход первого переноса (i,n) вычислительного блока соединен с вторым управляющим выходом (1,1), вычислительного блока (...п), вход первого переноса (n+2,j) вычислительного блока соединен с выходом второго переноса (п+1, j-О вычисчительного блока (...n+2), первый управляющий вход (i,j) вычислительного блока соединен с первым управляющим выходом (1,1) вычислительного блока (...п, ...n), первый управляющий вход

10

(n+1,j) вычислительного блока соединен с выходом первого переноса (п+1, j + 1) вычислительного блока (... -1), второй информационный вход (n+1,j) вычислительного блока соединен с выходом второго переноса (п+1, j-1) вычислительного блока, второй управляющий вход (n+1,j; n+2,j) вычислительного блока соединен с п+4 выходом блока управления (...n+2), вход разрешения записи (n+2,j) вычисительного блока соединен с п+2 выхоом блока управления (...п+2). пер- ый управляющий вход (i9j) вычисли- тельного блока соединен с i-м выходом блока управления (, ) и входом разрешения записи (1-1,1) вычислительного блока, вход управления передачей суммы (i,j) вычислительного блока соединен с (1+2)-м выходом блока управления (i 1. ..n+1, ...n+2), вход синхронизации (i,j) вычислительного блока соединен с п+5 выходом синхронизации блока управления ( ...n+2, ...n+2), вход формирования дополнительного кода (i,j) вычислительного блока соединен с вторым управляющим выходом (i,j) вычислительного блока (, j 1-n+2), выход суммы (п+2,2) вычислительного блока соединен с выходом матрицы вычислительных блоков.

20

25

30

35

40

50

элемента 2И-ИЛИ соединен с первым вхо-дд блока, выход первого элемента 2И-ИЛИ дом сумматора, первый вход элемента ИЛИ соединен с входом суммы вычислительного блока, выход элемента ИЛИ соединен с вторым входом сумматора, первый вход третьего элемента И соединен с первым информационным входом вычислительного блока, выходы третьего элемента И соединены с вторым и третьим входами второго элемента 2И-ИЛИ, первый и четвертый входы второго элемента 2И-ИЛИ соединены с входом формирования дополнительного кода блока, выход второго элемента 2И-ИЛИ соединен с вторым входом эле55

соединен с первым входом сумматора, первый вход элемента ИЛИ соединен с входом суммы вычислительного блока, выход элемента ИЛИ соединен с вторым входом сумматора, первый вход третьего элемента И соединен с первым информационным входом вычислительного блока, выходы третьего элемента И сое динены с вторым и третьим входами второго элемента 2И-ШШ, первый и четвертый входы второго элемента 2И-ИЛИ соединены с входом формирования дополнительного кода вычислительного блока, выход второго элемента

0

5

0

5

0

мента ИЛИ, первый вход четвертого элемента И соединен с входом данных вычислительного блока, второй вход соединен с первым управляющим входом вычислительного блока, выход соединен с информационными входами пятого и шестого триггеров, выходы которых соединены соответственно с первым и четвертым входами четвертого элемента 2И-ИЛИ, выход которого соединен с выходом данных вычислительного блока и вторым входом третьего элемента И, первый выход сумматора соединен с информационными входами первого и третьего триггеров, второй выход соединен с информационными входами второго и четвертого триггеров, выходы которых соединены с первым и четвертым входами третьего элемента 2И-ИЛИ соответственно, выход третьего элемента 2И-ИЛИ соединен с первыми входами первого и второго элемента И, вторые входы которых соединены с входом управления передачей суммы вычислительного блока, выход первого элемента И соединен с третьим входом сумматора, выход второго элемента И соединен с выходом суммы вычислительного блока, входы синхронизации всех триггеров, третьего и четвертого элементов 2И-ИЛИ соединены с входом синхронизации вычислительного блока.

блока, выход первого элемента 2И-ИЛИ

соединен с первым входом сумматора, первый вход элемента ИЛИ соединен с входом суммы вычислительного блока, выход элемента ИЛИ соединен с вторым входом сумматора, первый вход третьего элемента И соединен с первым информационным входом вычислительного блока, выходы третьего элемента И соединены с вторым и третьим входами второго элемента 2И-ШШ, первый и четвертый входы второго элемента 2И-ИЛИ соединены с входом формирования дополнительного кода вычислительного блока, выход второго элемента

И-ИЛИ соединен с вторым входом элемента ИЛИ, первые входы четвертого и пятого элементов И соединены с входом данных вычислительного блока, вторые входы этих элементов соединены с первым управляющим входом вычислительного блока, выход четвертого элемента И соединен с информационными входами третьего и четвертого триг- геров, второй выход четвертого триггера соединен с четвертым входом четвертого элемента 2И-ИЛИ, выход третьего триггера соединен с вторым входом третьего элемента 2И-ИЛИ и информа- ционным входом пятого триггера, первый вход четвертого триггера соединен с третьим входом третьего элемента 2И-ИЛИ, выход которого соединен с выходом данных вычислительного блока и вторым входом третьего элемента И, выход пятого триггера соединен с первым входом четвертого элемента 2И-ШШ выход которого соединен с первым информационным выходом вычислительного блока, первый и второй выходы сумматора соединены с информационными входами первого и второго триггеров соответственно, выход первого триггера соединен с выходом первого пе- еноса вычислительного блока, выход второго триггера соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с входом управления передачей суммы вычис- лительного блока, выход первого элемента И соединен с третьим входом сумматора, выход второго элемента И соединен с выходом суммы вычислительного блока, выход пятого элемента И соединен с информационным входом шестого триггера и вторым входом полусумматора, выход шестого триггера соединен с первым входом полусумматора, выход полусумматора соединен с информационным входом седьмого триггера j выход которого соединен с информационным входом восьмого триггера, выход восьмого триггера, соединен с вторым входом шестого элемента И, первые входы восьмого триггера и шестого элемента И соединены с входом разрешения записи вычислительного блока, выход шестого элемента И соединен с вторым управляющим выходом 5 вычислительного блока, входы синхронизации первых четырех триггеров, шестого триггера, первого элемента 2И-ИЛИ, третьего элемента 2И-ИЛИ соединены с входом синхронизации вычислительного блока.

с вторым упрвляющим входом вычислительного блока, а выход соединен с вторым входом сумматора, первый вход элемента ИЛИ соединен с входом суммы вычислительного блока, второй вход соединен с выходом первого элемента И, выход элемента ИЛИ соединен с третьим

35

входом сумматора, первый выход сумматора соединен с информационными входа ми первого и третьего триггеров, а второй выход - с информационными входами второго и четвертого триггеров, выход первого триггера соединен с выходом первого переноса вычислительного блока, выход третьего триггера соединен с выходом второго переноса вычислительного блока, выходы второго и четвертого триггеров соединены с входами третьего элемента 2И-ИЛИ, выход которого соединен с первыми входами

156

1

первого и второго элементов И, вторые синхронизации триггеров соединены с

входы которых соединены с входами управления передачей суммы вычислительного блока, выход второго элемента И соединен с выходом суммы вычислительного блока, входы синхронизации всех триггеров и всех элементов 2И-ИЛИ соединены с входом синхронизации вычислительного блока.

5

9826, Jf

первым входом элемента ИЛИ, второй вход первого элемента И соединен с входом суммы вычислительного блока, выход первого элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен с третьим входом сумматора, первый и четвертый входы элемента И-ИЛИ, первые входы элементов И соединены с вторым управляющим входом вычислительного блока, первый и второй выходы сумматора соединены с информационными входами первого и второго триггеров соответственно, входы

0

„

5

0

5

входом синхронизации вычислительного блока, выход первого триггера соединен с выходом второго переноса вычислительного блока, выход второго триггера соединен с выходом суммы вычислительного блока.

Таблица 2

1569826 f-71г 7

Фа

Усл. обозначение

Фиг.$

39 ft

89 36 П

чша/

/ IT //до I I

W / Усл. обозначение

101 109

w

m

ffg пг

56

«W

Составитель Ю.Фирстов Редактор В-.Бугренкова Техред М.Дидык Корректор М.Максимишинец

Заказ 1450

Тираж 565

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

ff«

ns «

- W

ff7

ОТ/

51112

m

w

-

7w ws

5J

j-I m

TrEK

nit Sea. обозначение

т

Подписное

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-07—Публикация

1988-10-02—Подача