первым разрядным входом шестого од поразрядного сумматора блока cyMMaторов, второй разрядный вход шестог одноразрядного сумматора блока cyi-f маторов соединен с выходом первого элемента ИЛИ блока анализа, входы элемента ИЛИ блока сумматоров соеди нены с выходам переноса шестого од-норазрядного с,гмматора блока сумма торов и выходом первого элемента И первой строки матри)цы, второй вход первого полусумматора блока сумма торов подключен к входу четвертого разряда третьего операнда устройств первый разрядный вход пятого одно разрядного сумматора блока сумматор подключен к выходу второго элемента ШШ блока анализа, выходы элемен. та ШМ и шестого одноразрядного сум матора блока сумматоров соединены с входами первого и второго разря дов первого трехразрядного двоичног сумматора кодопреобразователя, вы-ходы первого и второго элементов И кодопреобразователя соединены соот ветственно с первым и вторым входами первого элемента ИЛИ кодопреобразователя, выходы третьего и четве того элементов И кодопреобразователя подключены соответственно к перв му и второму входам второго элемента ИЛИ кодопреобразователя, выход первого элемента ШШ кодопреобразов .теля соединен с третьим входом втор го элемента ИЛИ кодопреобразователя выход второго элемента ШШ кодопреобразователя подключен к входу третьего разряда второго трехразрядног двоичного сумматора кодопреобразова теля, выходы разрядов второго трех- разрядного двоичного сумматора кодо преобразователя подключены к входам соответствующих разрядов третьего трехразрядного двоичного сумматора кодопреобразователя, выходы разрядов третьего трехразрядного двоичного сумматора кодопреобразователя подключены соответственно к выходам разрядов с пятого по седьмой результата устройства, выход суммы первог полусумматора блока сумматоров соединен с выходом восьмого разряда результата устройства, выход первого разряда второго трехразряд- него двоичного сумматора кодопреобразователя подключен к первым входам пятого и шестого элементов И кодопр образователя, выходы второго и третьего разрядов второго трехразрядно 13 го двоичного сумматора кодопреобразователя соединен с вторыми входами соответственно пятого и шестого элементов И кодопреобразователя, выходы пятого и шестого элементов И кодопреобразователя соединены соответственно с первым и вторым входами третьего элемента ИЛИ кодопреобразователя, о. тлич-ающееся тем, что, с целью повъпиения быстродействия, в блок анализа введены элементы И, НЕ и четыре элемента ИЛИ, в кодопреобразователь введены три элемента НЕ, девятый элемент И и пятый элемент ИЛИ, причем выход первого элемента И первой строки матрицы соединен с третьим входом первого и первым входом пятого элементов ИЛИ блока анализа, выход первого элемента И второй строки матрицы соединен с пердыми входами первого и второго элементов И и входом первого элемента НЕ блока анализа, выход второго элемента И первой строки матрицы соединен с третьим входом третьего и первым входом шестого элементов ИЛИ блока анализа, выход первого элемента И третьей строки матрицы соединен с вторым входом первого . и первым входом третьего элементов И и входом второго элемента НЕ блока анализа, выход четвертого элемента И третьей строки матрицы подключен к первому входу седьмого эле- . мента ИЛИ блока анализа, выход третьего элемента И первой строки матрицы подключен к вторым входам пятого и седьмого элементов ИЛИ блока анализа, третьи входы второго и четвертого элементов ИЛИ блока анализа соединены с выходом первого элемента И блока анализа, выход второго элемента И второй строки матрицы соединен с первым входом восьмого элемента ИЛИ блока анализа, вторые входы шестого и восьмого элементов ИЛИ блока анализа соединены с выходом третьего элемента И блока анализа, выход третьего элемента И третьей строки матрицы соединен с третьим входом шестого элемента ИЛИ блока анализа, четвертые входы четвертого и шестого элементов ШШ блока анализа соединены с выходом второго элемента И блока анализа, выходы первого и второго элементов НЕ блока анализа соединены с вторыми входами соответственно третьего и второго элементов И блока анализа.

выход четвертого элемента И второй строки матрицы соединен с третьим входом пятого элемента ИЛИ блока анализа, в блоке сумматоров выход переноса первого полусумматора соединен с входом переноса седьмого одноразрядного сумматора, выход переноса которого соединен с входом переноса восьмого одноразрядного сумматора, выход переноса которого соединен с входом переноса девятого .одноразрядного сумматора, выход переноса которого соединен с в переноса десятого .одноразрядного сумматора, выход переноса которого соединен с входом переноса шестого одноразрядного сумматора, вход переноса пятого одноразрядного сумматора соединен с выходом переноса второго полусумматора, первый разрядный вход десятого одноразрядного сумматора соединен с выходом суммы пятого одноразрядного сумматора, второй разрядный вход десятого одноразрядного сумматора соединен с выходом перенос четвертого одноразрядного сумматора, выход суммы которого соединен с первым разрядным входом девятого одноразрядного- сумматора, выходы суммы первого и второгоодноразрядных сумматоров соединены с первыми разрядными входами соответственно седьмого, и восьмого одноразрядных сумматоров , выход первого элемента И третьей строки матрицы соединен с вторым разрядным входом пятого одноразрядного сумматора блока сумматоров, выходы третьего и четвертого элементов ИЛИ блока анализа подключены соответственно к. входам второго полусумматора блока сумматоров, выход суммы Которого соединен с вторым раз рядным входом четвертого одноразрядного сумматора блока сумматоров, выход второго.элемента И второй строки матрищл соединен с вторым разрядным входом третьего одноразрядного cyi матора блока сумматоров, выходы шестого и седьмого элементов ИЛИ блока анализа соединены с вторыми разрядными входами соответственно второго t и первого одноразрядгалх сумматоров .блока сумматоров, вторые разрядные входы девятого, восьмого и седьнего одноразрядных сумматоров блока сумматоров подключены к входам соот ветственно первого, второго и третьего разрядов третьего операнда устройства, выходы пятого и восьмого

8513

элементов ИЛИ блока анализа соединены с входами переноса соответственно третьего и первого одноразрядных сумматоровблока сумматоров, в кодопреобразователе выход седьмого элемента И соединен с третьим входом первого элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ и входом первого элемента НЕ, выход которого подключен к первым входам третьего и четвертого элементов И, выходы которых соединены со.ответственно с входом второго разряда второго трехразрядного двоичного сумматора и входом второго элемента НЕ, выход которого подключен к первому входу восьмого элемента И, второй вход которого соединен с входом переноса первого трехразрядного двоичного сумматора и выходом третьего элемента ИЛИ, третий вход которого подключен к выходу переноса второго трехразрядно- го двоичного сумматора, выход пято- го элемента ИЛИ подключен к вторым входам третьего и четвертого элементов И, третьи входы которых соеди- . нены соответственно с выходом и вхо- дом третьего элемента НЕ, выход девятого элемента И подключен к входу , третьего элемента НЕ, второй вход четвертого элемента ИЛИ подключен к выходу четвертого элемента И, а . выход - к входу третьего разряда первого трехразрядного двоичного сумматора, выход переноса второго полусумматора блока сумматоров соединен с первыми входами первого и второго элементов И и пятого элемента ИЛИ кодопреобразователя, выход переноса четвертого одноразрядного сумматора блока сумматоров соединен с вторым входом первого элемента И, первым входом седьмого элемента И и вторым входом пятого элемента ИЛИ кодопреобразователя, выход переноса девятого одноразрядного сумматора блока сумматоров соединен с вторыми входами второго и седьмого элемен- ToiB И и третьим входом пятого элемента ИЛИ кодопреобразователя, выход суммы десятого одноразрядного сумматора блока сумматоров соединен с входом третьего разряда первого трехразрядного двоичного сумматора кодопреобразователя, выходы суммы девятого, восьмого и седьмого одноразрядных сумматоров блока сумматоров соединены соответственно с входами

первого, второго и третьего разрядов второго трехразрядного двоичного сумматора и входами девятого элемента И кодопреобразователя, выход восьмого элемента И кодопреобразователя соединен с входами второго и третьего разрядов третьего трехраз А

рядного двоичного сумматора кодопре-образователя, выход переноса и выхо ды разрядов первого трехразрядного двоичного сумматора соединены с вьпкодами разрядов с первого по четвертый результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство умножения двоично-десятичных цифр | 1982 |

|

SU1073771A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для подсчета числа двоичных единиц | 1980 |

|

SU966700A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018925C1 |

| Десятичный сумматор в избыточной системе счисления | 1985 |

|

SU1256015A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЦИФР, содержащее матрицу элементов И, блок анализа, блок сумматоров и кодопреобразователь, причем блок анализа содержит четыре элемента ИЛИ, блок сумматоров содержит одноразрядные сумматоры, полусумматоры и элемент ИЛИ, кодопреобразователь содержит три трехразрядных двоичных сумматора, восемь элементов И и четыре элемента ИЛИ, причем первые входы элементов И i-и строки матрицы (i J,...,4) соединены с входом 1-го разряда первого операнда устройства, вторые входы элементов И J-ro столбца матрицы (j 1,...,4) соединены с входом j-го разряда второго операнда устройства, первый и второй входы первого элемента ИЛИ блока анализа соединены с выходами первого элемента К второй строки матрицы и второго элемента И первой строки матрицы соответственно, первый и второй входы второго элемента ИЛИ блока анализа соединены с выходами второго элемента И второй строки матрицы и третьего элемента И первой строки матрицы соответственно, первый и второй входы третьего элемента ИЛИ блока анализа соединены с выхода- ми первого элемента И четвертой строки матрицы и второго элемента И третьей строки матрицы соответственно, первый, и второй входы четвертого элемента ИЛИ блока анализа соединены с выходами третьего элемента И второй строки матрицы и четвертого элемента. И первой строки матрицы соответственно, выход четвертого элемента И четвертой строки матрицы подключен к первому входу первого полусумматора блока сумматоров, выход третьего элемента И четвертой строки матрицы под(Л ключен к первому разрядному входу первого одноразрядного сумматора блока сумматоров, выход переноса первого одноразрядного сз мматора блока сумматоров подключен к входу переноса второго одноразрядного сумматора блока сумматоров, первый разQO 00 01 рядный вход второго одноразрядного сумматора блока сумматоров.подключен к выходу суммы третьего одноразрядного сумматора блока суммаСАЭ торов, первый разрядный вход третьего одноразрядного сумматора блока сумматоров подключен к выходу второго элемента И четвертой строки мат- . рицы, первый разрядный вход и вход переноса четвертого одноразрядного сумматора блока сумматоров соединены соответственно с выходами переноса третьего и второго одноразрядных сумматоров блока сумматоров-, выход переноса пятого одноразрядного сумматора блока сумматоров соединен с

1

Изобретение относится к вычисли

тельной технике, предназначено для умножения двоично десятичных цифр, представл,енных кодом , и прибавления десятичного переноса, и .может применяться в быстродействующих вычислителях.

Цель изобретения повьшение быстродействия .

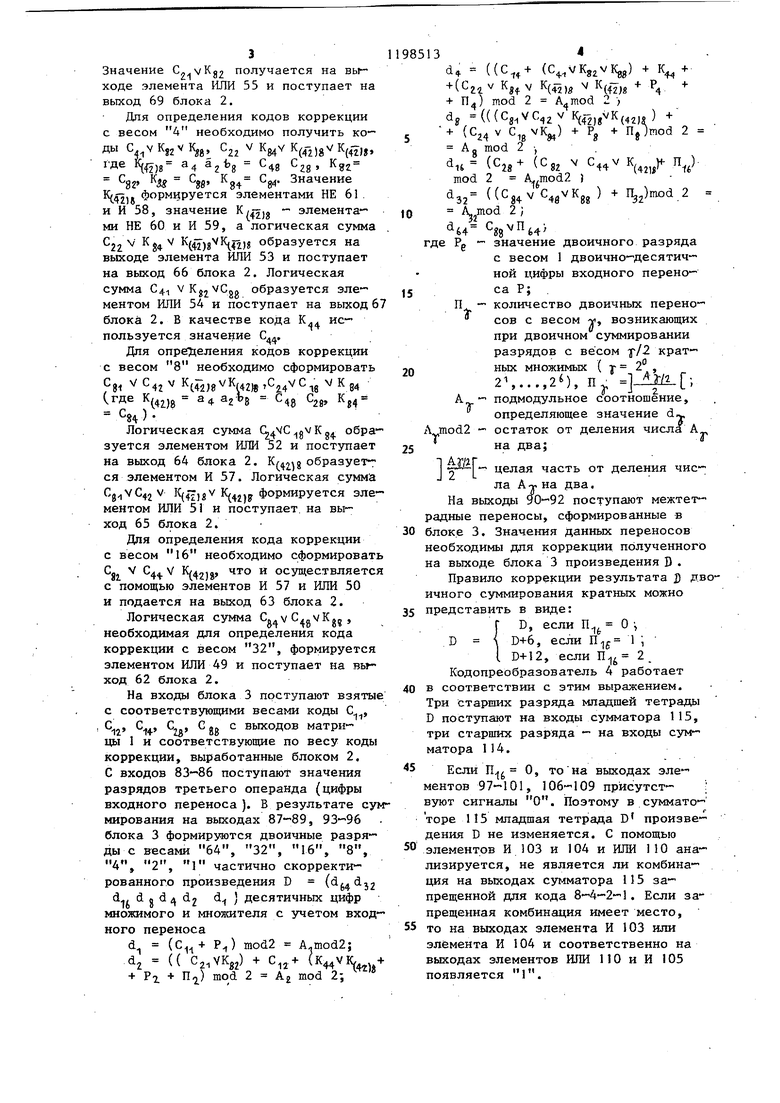

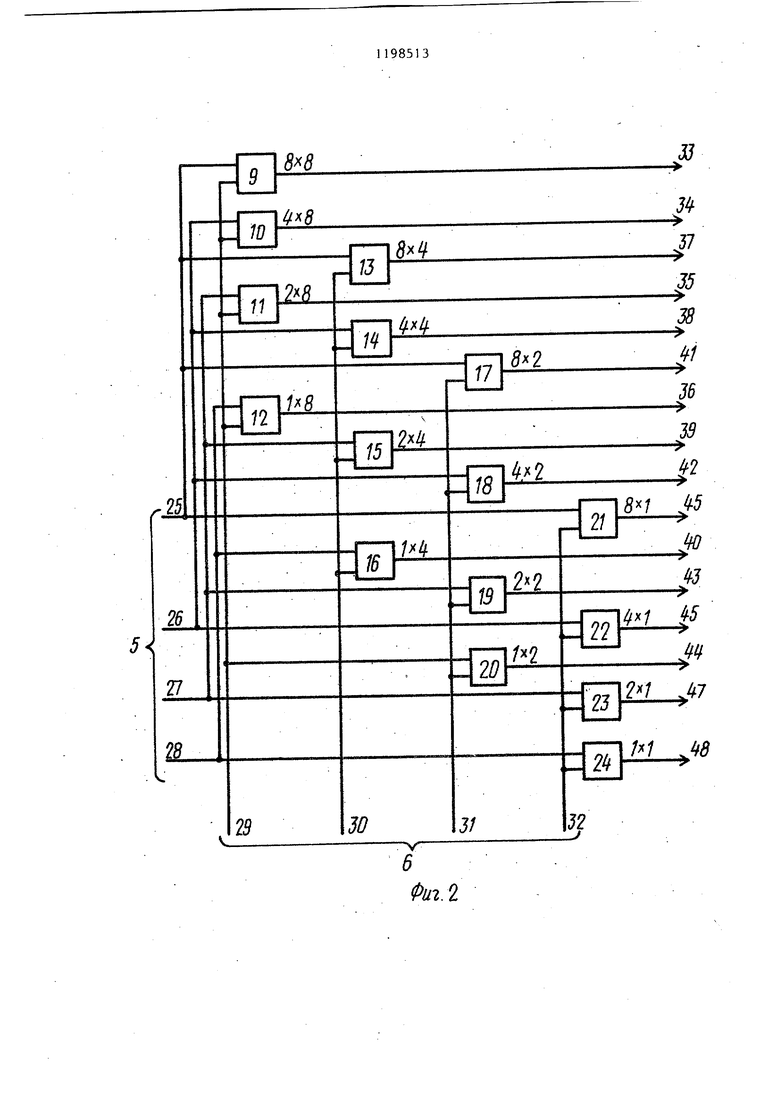

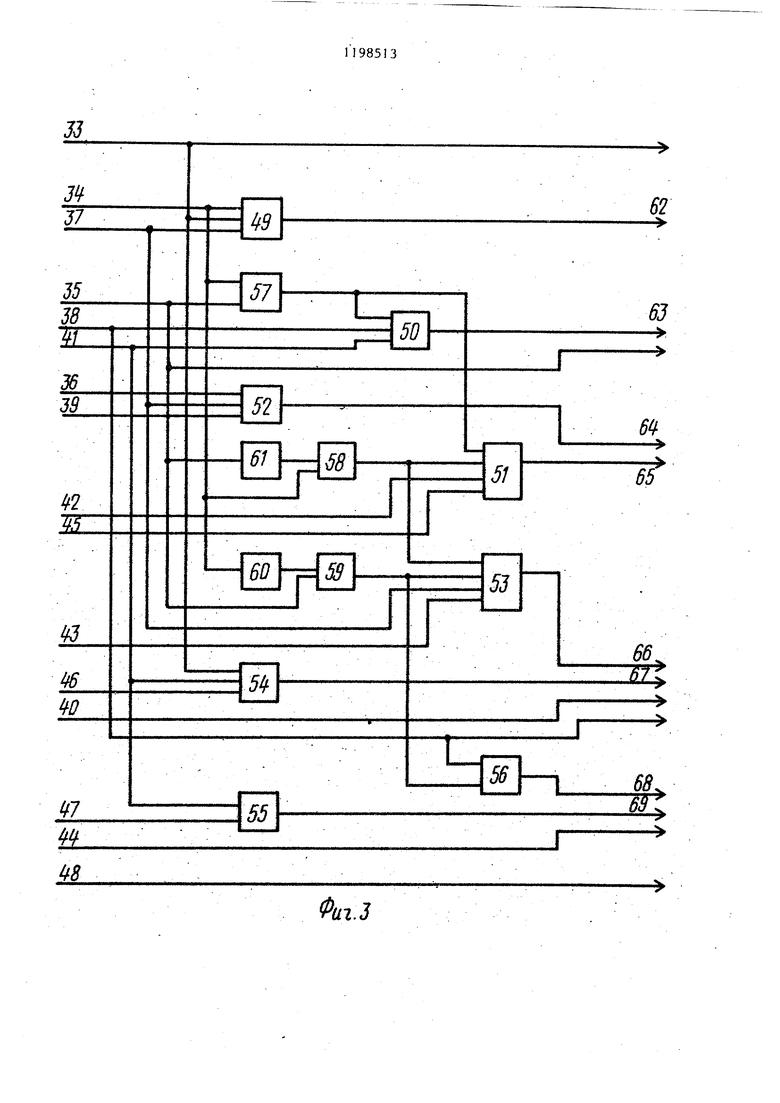

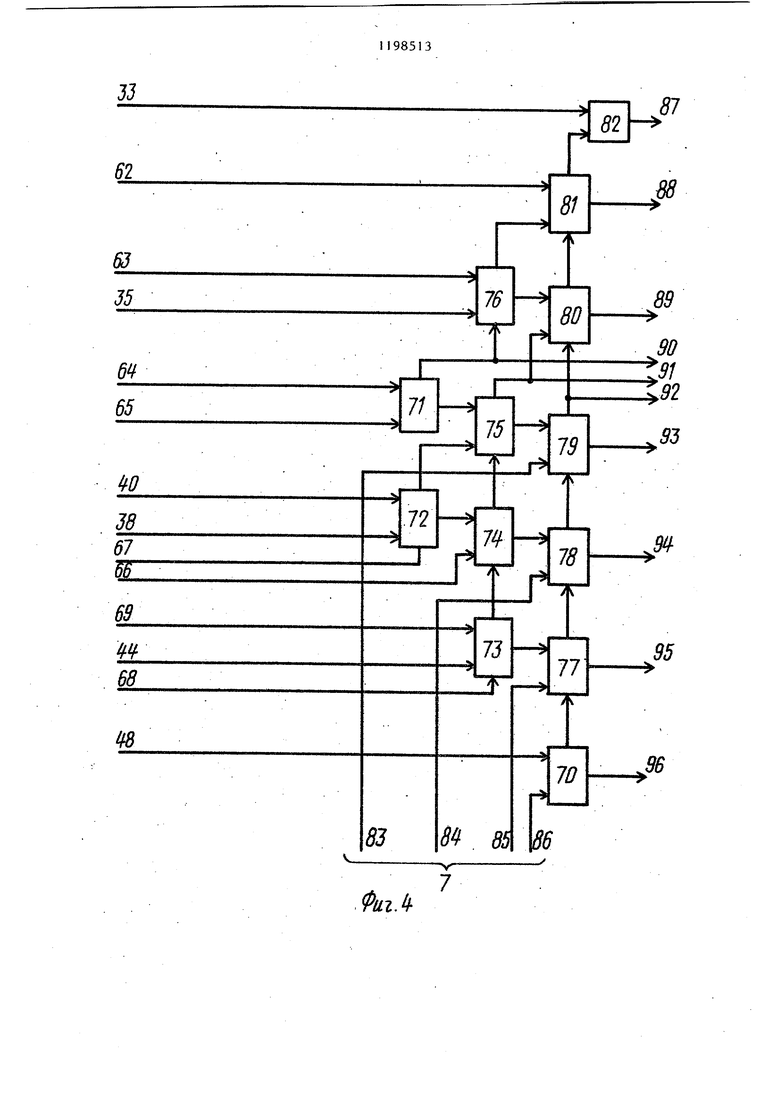

На фиг. I представлена структурная схема устройства; на фиг, 2 функциональная схема матрицы эле ментов И; на фиг. 3 функциональная схема блока анализа; на фиг. 4 функциональная схема блока сумматоров ; на фиг. 5 - функциональная схема кодопреобразователя.

Устройство (фиг. 1) содержит матрицу 1 элементов И, блок 2 анализа, блок 3 сумматоров, кодопреобразователь 4, входы 5 первого операнда, входы 6 второго операнда, входы 7 третьего операнда и выходы В результата.

Матрица 1 (фиг. 2) содержит элементы И 9-24, входы которых подключены к входам 25-28 разрядов первого операнда, входам 29-32 разрядов второго операнда, а выходы соединены с выходами 33-48 матрицы 1.

Блок 2 (фиг. 3) содержит элементы ИЛИ 49-56, И 57-59, НЕ 60 и 61, выходы которых соединены с выходами 62-69 блока 2.

Блок 3 (фиг. 4) содержит полусум маторы 70 и 71, одноразрядные сумматоры 72-81, элемент ИЛИ 82, входы которых соединены с выходами матрицы 1, блока 2 и входами 83-86 разрядов третьего операнда, а выходы соединены с выходами 87-96 блока 3.

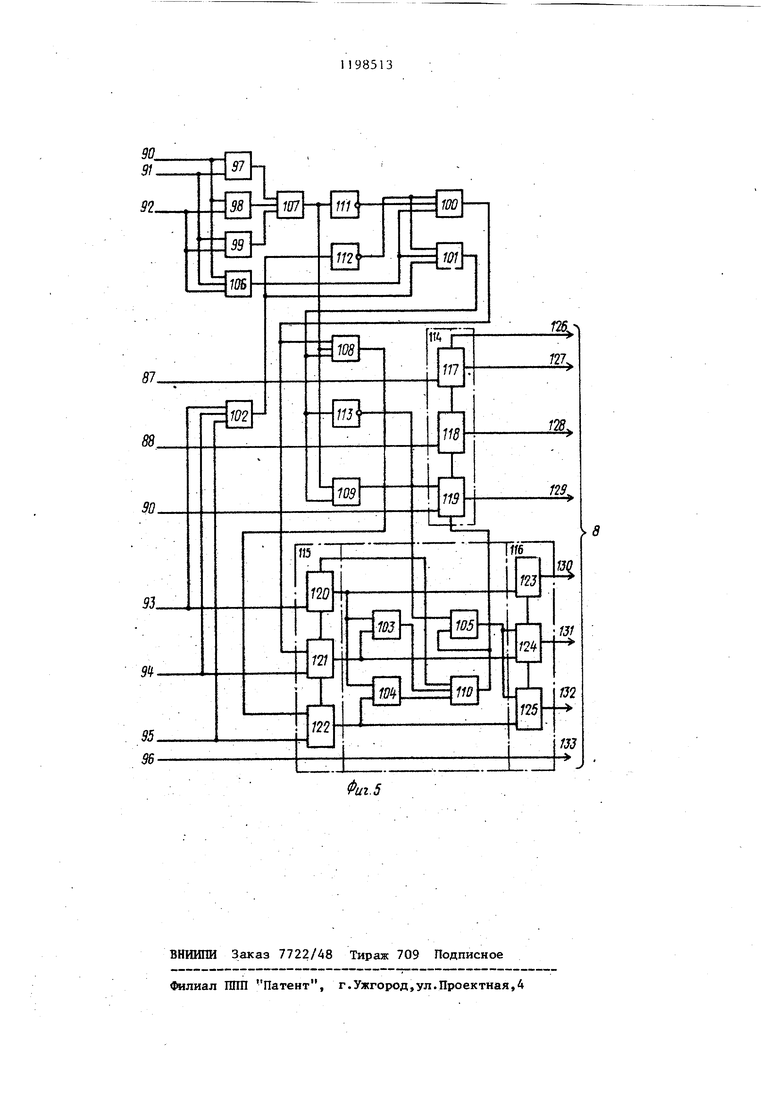

Кодопреобразователь 4 (фиг. 5) содержит элементы И 97-105, ИЛИ 106110, НЕ 111-113, трехразрядные двоичные сумматоры 114, 115 и 116. Сумматор 1Г4 содержит полусумматоры I17 и 118 и одноразрядный сумматор 119. Сумматор 115 содержит полусумматор 120, одноразрядный сумматор 121 и полусумматор 122. Сумматор 116 содержит полусумматор 123, одноразрядный сумматор 124 и полусумматор 125.

Выходы сумматоров 114 и 116 и полусумматора 70 соединены с выходами 126-133 разрядов результата.

Устройство работает следуюпщм образом.

На входы 5, 6 и 7 подаются значе- 5 ния трех, операндов (цифра множимого а, цифра множителя и цифра входного переноса Pg P,P2P ) в двоично десятичном коде 8-4-2-1. При этом срабатывают соот- 0 ветствующие элементы И 9-24 матрицы 1 и формируют соответствующие значения С у (1 1, 2, 4, 8 - значения весов разрядов входов 5; 1 1, 2, 4, 8 - значения весов разрядов вхо- 5 дов 6 .

Перед сложением, полученных в матрице 1 значений двоичных произведе-

НИИ в блоке 2 осуществляется формирование кодов неполной коррекции

0 кратных множимого. Формирование кодов коррекции выполняется частично исходя из возможности их учета на сумматорах блока 3, осуществляющих сложение двоичных частичных проиэ-

5 ведений. Окончательная коррекция кратных и результата, осуществляется в кодопреобразователе 4.

Для определения кодов коррекции

с весом 2 необходимо получить ко0 и К44УК ц, где K(|-,g

а

К

4« Ягз

Csi, К

вг

44 044. Значение К v формируется элементами НЕ 60, И 59, ИЛИ 56 и поступает на выход 68 блока 2. 3 Значение С..vKj2 получается на выходе элемента 1ШИ 55 и поступает на выход 69 блока 2. Дпя определения кодов коррекции с весом 4 необходимо получить ко ды с V % V K,g, С, V K(4-)gV К(-,„ Д %)8 а 4 48 28, Kgj Cg, % Cyg, Kg Cg4. Значение 41)8 Ф Р ЧРУЕтся элементами HE 61 . и И 58, значение K/,j элемента ми НЕ 60 и И 59, а логическая сумма 22 8 («))8 образуется на выходе элемента ИЛИ 53 и поступает на выход 66 блока 2. Логическая сумма C4i KgjVCgg образуется эле- ментом ИЛИ 54 и поступает на выход блока 2. В качестве кода К., используется значение С, Дпя определения кодов коррекции с весом 8 необходимо сформировать 81 С V ) К 84 (где .,jg а4 azbg , %) Логическая сумма обра зуется элементом ИЛИ 52 и поступает на выход 64 блока 2. образует- ся элементом И 57. Логическая сумма %2) эле ментом ИЛИ 51 и поступает, на выход 65 блока 2. Дпя определения кода коррекции с весом 16 необходимо сформироват С. V С V К/42)8 ° осуществляетс с помощью элементов И 57 и ИЛИ 50 и подается на выход 63 блока 2. Логическая сумма С, v Ci-vK.., от то о необходимая для определения кода коррекции с весом 32, формируется элементом ИЛИ 49 и поступает на вь ход 62 блока 2. На входы блока 3 поступают взяты с соответствующими весами коды С , 12 ф гг 88 выходов матрицы 1 и соответствующие по весу коды коррекции, выработанные блоком 2. С входов 83-86 поступают значения разрядов третьего операнда (цифры входного переноса ). В результате су мирования на выходах 87-89, 93-96 блока 3 формируются двоичные разряды с весами 64, 32, 16, 8, А, 2, 1 частично скорректированного произведения D ( d, d g d ( d2 d j десятичных цифр множимого и множителя с учетом вход ного переноса 1 1-1 ч A.mod2; d2 ({ C. п (4г)/ + РТ. + П) 2 Аг mod 2; 13 d ((С (C,VK,,vK,g) + ( K,v + n) mod 2 A mod 2 dj (((Cj, %1)(„,„) + + (C,, V ) + Pg + RgMod 2 Ag mod 4,1- «,, (C 44 K(a,/ mod 2 A,,mod2 ) ) + 2 32 ((,gVKg V° 2; где Pp значение двоичного разряда с весом 1 двоично-десятичной цифры входного переноса Р; . количество двоичных переносов с весом С возникающих при двоичном суммировании разрядов с весом f/2 кратных множимых ( т 2 , 01 2h П .Г; ,.. ., ;, 11 -, JJJ- ( I f J г подмодульное соотношение, определяющее значение d, остаток от деления числ А А mod2 на два; 1АШГ„ J 2 L целая часть от деления числа А -у на два. На выходы 90-92 поступают межтетрадные переносы, сформированные в блоке 3. Значения данных переносов необходимы для коррекции полученного на выходе блока 3 произведения D. Правило коррекции результата j) двоичного суммирования кратных можно представить в виде: Г D, если П О , D { D+6, если П-, 1 ; 1 D+12, если П 2 Кодопреобразователь 4 работает в соответствии с этим выражением. Три старших разряда младшей тетрады D поступают на входы сумматора 115, три старших разряда - на входы сумматора 114. Если П О, тона выходах элементов 97-101, 06-109 прйсутст- : взпот сигналы О. Поэтому в сумматоторе 115 младшая тетрада D произведения D не изменяется. С помощью элементов И 103 и 104 и ИЛИ ПО анализируется, не является ли комбинация на выходах сумматора 1I5 запрещенной для кода 8-4-2-1. Если запрещенная комбинация имеет место, то на выходах элемента И 103 или элемента И 104 и соответственно на выходах элементов ШШ 110 и И 105 появляется 1. с выхода элемента ИЛИ 110 I поступает на вход переноса сумматора 114, значение в котором, а значит значение старшей тетрады произведения D увеличивается на единицуС выхода элемента И 105 I поступает на входы сумматора 116, зна чение которого, а следовательно, мпадшая тетрада D, увеличивается на шесть. Если Il,j 1 {единица на одном из выходов 90-92 блока 3), то на выходах элементов И 97-99, ИЛИ 107 .присутствуют сигналы О, на выходах элементов ИЛИ 106 и НЕ 1I1 - I. С помощью элемента И 102 анализируется значение младшей тетрады D на код 1110 (14) или МП (15 Если мпадшая тетрада D отлична от данного значения, то на выходе элемента И 02 присутствует О, на выходе НЕ 112 - I. Поэтому срабатьшают элементы И 100, ИЛИ 108 и в сумматоре П5 к мпадшей тетраде D прибавляется код 6 (0110). С по мощью элементов И 103, 104, ИЛИ ПО полученная сумма ан.ализируется на запрещенную для кода 8-4-2-1 Kotfбина11Ию. При ее наличии или при появлении на Еыходе сумматора 115 еди ничного значения П 1 появляется на выходах элементов ИЛИ ПО, И 105 которая поступает на вход переноса сумматора П4, а младшая тетрада произведения, сформированная иа вых дах сумматора П 5, в сумматоре 116 увеличивается на 6, Если значение младшей тетрада D равно П10 (14) или ПП (15), то на выходе элемента И 102 появляется 1, на выходе НЕ П2 - О. Поэтому срабатывают элементы И 01, ИЛИ 108 и 109. На выходе элемента НЕ 113 появляется О. Это вызывает прибавление к произведению D, сформированному на выходах 87-89,

т

I

Фиг.1 136 93-96 блока 3, кода 0001 0010. Дан- i ное прибавление осуществляется в сумматорах 114 и 115. Перенос П , возникающий на выходе переноса сум- матора 115 и 120, проходит на выход элемента ИЛИ ПО, а отсюда на вход переноса сумматора 114. Поэтому старшая тетрада результата увеличивается на 1. . С выхода элемента НЕ 113 О поступает на вход элемента И 105, блокируя его работу. Поэтому в суьгматоре 116 младшая тетрада D, , сформированная на выходах сумматора 115, не изменяется. Если П . 2 (единицы на двух вь ходах из выходов 90-92 блока 3), то на выходах элементов ИЛИ 106 и 107 появляются сигналы I, на выходе элемента НЕ 111 - О, который блокирует работу элементов И 100 и 101. С выхода элемента ИЛИ 107 1 проходит через элементы ИЛИ 108 и 109. Поэтому в сумматорах 114 и 113 к произведению D прибавляется код коррекции 12 (0001 0010). Если при сложении в младшей тетраде результата появилась запрещенная комбинация или П на выходе переиоса сумматора 115 равен 1, то 1 появляется на выходе элементов ИЛИ ПО,И 105 Поэтому на вход переноса сзгммато- ра 114 поступает 1, а к младшей тетраде результата в cyi taTope 116 прибавляется 6. В результате указанных выше дей ствий на выходах 126-$33 фор в1руется произведение цифр множимого и (Сожителя (с учетом, входного переноса в коде 8-4-2 Г. Произведение представляет собой две двоично-десятичные цифры. Разряды с весами 8, 4, 2 и I младшей цифры появляются иа выходах 130-133 соответственно, разряды с весами 8, 4, 2 и 1 старшей цифры - соответственно на выходах 126-129.

Put г

Фаг.З

ФигЛ

| Патент США № 3890496, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство умножения двоично-десятичных цифр | 1982 |

|

SU1073771A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1983-06-27—Подача